# C29x CPU

# Reference Guide

Literature Number: SPRUIY2 NOVEMBER 2024

# **Table of Contents**

| About This Manual.  Related Documentation from Texas Instruments.  Glossary.  6 Support Resources.  6 Architecture Overview.  7. 1.1 Introduction to the CPU.  8. 13. C29x CPU System Architecture.  9 1.3 C29x CPU System Architecture.  12 Central Processing Unit (CPU).  12 Central Processing Unit (CPU).  12 C2T CPU Registers.  13 Lord System Architecture.  13 Interrupts.  2.3 Instruction Packing.  2.4 Stacks.  2.1 Stacks.  2.1 (PU Interrupts Architecture Block Diagram.  2.5 (PU Interrupts Architecture Block Diagram.  2.6 (PU Interrupt Control Registers.  3.1 (PU Interrupt Control Registers.  3.3 (PU Interrupt Control Registers.  3.4 (PU Interrupt Control Registers.  3.5 (Security.  3.6 Security.  3.7 (Pipeline.  3.7 (Pipeline.  3.8 (Pipeline.  3.9 (Pipeline. | Read This First                                  | 5  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----|

| Glossary   6   Support Resources   6   Architecture Overview   7   7   1.1 Introduction to the CPU   8   1.2 Data Type   8   8   1.3 C29x CPU System Architecture   9   1.4 Memory Map   9   1.4 Memory Map   9   1.4 Memory Map   9   1.4 Memory Map   1.5 C2 Central Processing Unit (CPU)   1.2 C2 Central Processing Unit (CPU)   1.2 C2 CPU Architecture   1.3 C2 CPU Registers   1.4   2.3 Instruction Packing   2.2 CPU Registers   1.4   2.3 Instruction Packing   2.3 Interrupts   2.4 Stacks   2.1   2.3 Interrupts Architecture Block Diagram   2.5   3.1 CPU Interrupts Architecture Block Diagram   2.5   3.1 CPU Interrupts Architecture Block Diagram   2.5   3.2 RESET, NMI, RTINT, and INT   2.7   3.3 Conditions Blocking Interrupts   3.5   1.4 CPU Interrupt Control Registers   3.5   Interrupt Nesting   3.4 CPU Interrupt Control Registers   3.5   Interrupt Nesting   3.4 Pipeline   3.5   3.6 Security   3.5   3.6 Security   3.5   4.1 Introduction   3.7   4.2 Decoupled Pipeline Phases   4.2 Decoupled Pipeline Phases   4.4   Pipeline Advancement and Stalls   4.4   Pipeline Advancement and Stalls   4.5 Pipeline Hazards and Protection Mechanisms   4.2   4.5 Pipeline Hazards and Protection Mechanisms   4.4   4.5 Pipeline Advancement and Stalls   4.5 Pipeline Hazards and Virles During Normal Operation   4.6   4.9 E1 Read Protection   4.7   4.1 WAWP Protection During Interrupt   4.9   5.1 Addressing Modes   5.3 Alignment and Pipeline Considerations   5.5 Alignment and Pipeline Considerations   5.6   5.3 Alignment and Pipeline Considerations   5.6   5.1 Addressing Modes   5.6   5.1 SU Overview   5.1   5.1 SU Overview   5.1   5.1 SU Overview   5.1   5.1 SU Overview   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5.1   5   | About This Manual                                | 5  |

| Support Resources       6         1 Architecture Overview       7         1.1 Introduction to the CPU       8         1.2 Data Type       8         1.3 C29x CPU System Architecture       9         1.4 Memory Map       11         2 Central Processing Unit (CPU)       12         2.1 C29x CPU Architecture       13         2.2 Central Processing       14         2.3 Instruction Packing       20         2.4 Stacks       21         3.1 CPU Interrupts Architecture Block Diagram       25         3.2 RESET, NMI, RTINT, and INT       27         3.2 Conditions Blocking Interrupts       30         3.4 CPU Interrupt Control Registers       31         3.5 Interrupt Resting       34         4.7 Pipeline       35         4.8 Decoupled Pipeline Phases       40         4.1 Introduction       38         4.2 Decoupled Pipeline Phases       41         4.3 Pipeline Hazards and Protection Mechanisms       42         4.5 Pipeline Hazards and Protection Mechanisms       42         4.6 Register Updates and Corresponding Pipeline Phases       44         4.7 Register Reads and Writes During Normal Operation       46         4.9 DZ Read Protection       46      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Related Documentation from Texas Instruments     | 5  |

| Support Resources       6         1 Architecture Overview       7         1.1 Introduction to the CPU       8         1.2 Data Type       8         1.3 C29x CPU System Architecture       9         1.4 Memory Map       11         2 Central Processing Unit (CPU)       12         2.1 C29x CPU Architecture       13         2.2 Central Processing       14         2.3 Instruction Packing       20         2.4 Stacks       21         3.1 CPU Interrupts Architecture Block Diagram       25         3.2 RESET, NMI, RTINT, and INT       27         3.2 Conditions Blocking Interrupts       30         3.4 CPU Interrupt Control Registers       31         3.5 Interrupt Resting       34         4.7 Pipeline       35         4.8 Decoupled Pipeline Phases       40         4.1 Introduction       38         4.2 Decoupled Pipeline Phases       41         4.3 Pipeline Hazards and Protection Mechanisms       42         4.5 Pipeline Hazards and Protection Mechanisms       42         4.6 Register Updates and Corresponding Pipeline Phases       44         4.7 Register Reads and Writes During Normal Operation       46         4.9 DZ Read Protection       46      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Glossary                                         | 6  |

| 1 Architecture Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                  |    |

| 1.1 Introduction to the CPU.       8         1.2 Data Type.       8         1.3 C29x CPU System Architecture.       9         1.4 Memory Map.       11         2 Central Processing Unit (CPU).       12         2.1 C29x CPU Architecture       13         2.2 CPU Registers.       14         2.3 Instruction Packing.       20         2.4 Stacks.       21         3.1 CPU Interrupts Architecture Block Diagram.       26         3.2 RESET, INMI, RTINT, and INT.       27         3.3 Conditions Blocking Interrupts.       30         3.4 CPU Interrupt Control Registers.       31         3.5 Interrupt Nesting.       34         4 Pipeline.       37         4.1 Introduction.       35         4.2 Decoupled Pipeline Phases.       40         4.2 Decoupled Pipeline Phases.       40         4.3 Dial Instruction Prefetch Buffers.       41         4.4 Pipeline.       37         4.5 Pipeline Hazards and Protection Mechanisms.       42         4.6 Register Updates and Protection Mechanisms.       42         4.7 Register Reads and Writes During Normal Operation.       46         4.8 D2 Read Protection.       46         4.9 E1 Read Protection.       46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                  |    |

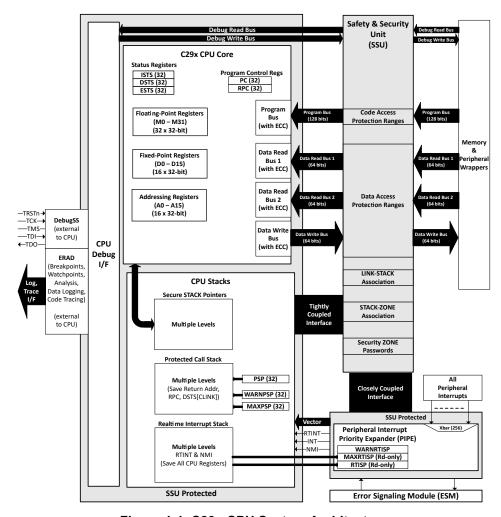

| 1.2 Data Type.       8         1.3 C29x CPU System Architecture.       9         1.4 Memory Map.       11         2 Central Processing Unit (CPU).       12         2.1 C29x CPU Architecture       13         2.2 CPU Registers.       14         2.3 Instruction Packing.       20         2.4 Stacks.       21         3 Interrupts.       25         3.1 CPU Interrupts Architecture Block Diagram.       26         3.2 RESET, NMI, RTINT, and INT.       27         3.3 COnditions Blocking Interrupts.       30         3.4 CPU Interrupt Control Registers.       31         3.5 Interrupt Nesting.       34         3.6 Security.       35         4 Pipeline.       37         4.1 Introduction.       38         4.2 Decoupled Pipeline Phases.       40         4.3 Dual Instruction Prefetch Buffers.       41         4.3 Dual Instruction Prefetch Buffers.       41         4.5 Pipeline Advancement and Stalls.       42         4.5 Pipeline Advancement and Stalls.       42         4.6 Register Updates and Corresponding Pipeline Phases.       44         4.7 Register Reads and Writes During Normal Operation.       46         4.8 D2 Read Protection.       47      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1.1 Introduction to the CPU                      | 8  |

| 1.3 C29x ČPU System Architecture       9         1.4 Memory Map       11         2 Central Processing Unit (CPU)       12         2.1 C29x CPU Architecture       13         2.2 CPU Registers       14         2.3 Instruction Packing       20         2.4 Stacks       21         3.1 CPU Interrupts       25         3.1 CPU Interrupt Architecture Block Diagram       26         3.2 RESET, NMI, RTINT, and INT       27         3.3 Conditions Blocking Interrupts       30         3.4 CPU Interrupt Control Registers       31         3.5 Interrupt Nesting       34         3.6 Security       35         4 Pipeline       37         4.1 Introduction       38         4.2 Decoupled Pipeline Phases       40         4.3 Dual Instruction Prefetch Buffers       40         4.4 Pipeline Advancement and Stalls       42         4.5 Pipeline Hazards and Protection Mechanisms       42         4.6 Register Updates and Corresponding Pipeline Phases       44         4.7 Register Reads and Writes During Normal Operation       44         4.8 D2 Read Protection       46         4.9 E1 Read Protection       46         4.9 E1 Read Protection       46 <td< td=""><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                  |    |

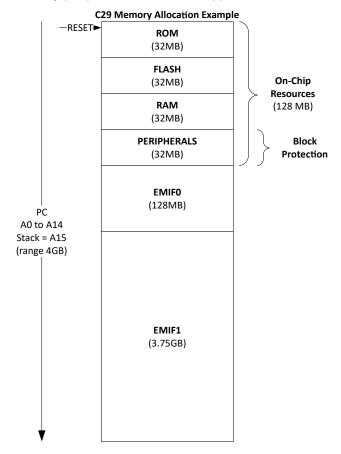

| 1.14 Memory Map       .11         2 Central Processing Unit (CPU)       .12         2.1 C29x CPU Architecture       .13         2.2 CPU Registers       .14         2.3 Instruction Packing       .20         2.4 Stacks       .21         3 Interrupts       .25         3.1 CPU Interrupts Architecture Block Diagram       .26         3.2 RESET, NMI, RTINT, and INT       .27         3.3 Conditions Blocking Interrupts       .30         3.4 CPU Interrupt Control Registers       .31         3.5 Interrupt Nesting       .34         3.6 Security       .35         4 Pipeline       .37         4.1 Introduction       .38         4.2 Decoupled Pipeline Phases       .40         4.3 Dual Instruction Prefetch Buffers       .40         4.3 Dual Instruction Prefetch Buffers       .40         4.4 Pipeline Advancement and Stalls       .41         4.5 Pipeline Hazards and Protection Mechanisms       .42         4.6 Register Updates and Corresponding Pipeline Phases       .44         4.7 Register Reads and Writes During Normal Operation       .44         4.8 D2 Read Protection       .46         4.9 E1 Read Protection       .47         4.10 WAW Protection During Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                  |    |

| 2 Central Processing Unit (CPU).       12         2.1 C29x CPU Architecture.       13         2.2 CPU Registers.       14         2.3 Instruction Packing.       20         2.4 Stacks.       21         3 Interrupts.       25         3.1 CPU Interrupts Architecture Block Diagram.       26         3.2 RESET, IMMI, RTINT, and INT.       27         3.3 Conditions Blocking Interrupts.       30         3.4 CPU Interrupt Control Registers.       31         3.5 Interrupt Nesting.       34         3.6 Security.       35         4 Pipeline.       37         4.1 Introduction.       38         4.2 Decoupled Pipeline Phases.       40         4.3 Dual Instruction Prefetch Buffers.       41         4.4 Pipeline Advancement and Stalls.       42         4.5 Pipeline Hazards and Protection Mechanisms.       42         4.6 Register Updates and Corresponding Pipeline Phases.       44         4.7 Register Updates and Corresponding Pipeline Phases.       44         4.7 Register Padas and Writes During Normal Operation.       44         4.8 D2 Read Protection.       46         4.9 E1 Read Protection.       47         4.10 WWW Protection       48         4.11 Protection During Inte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                  |    |

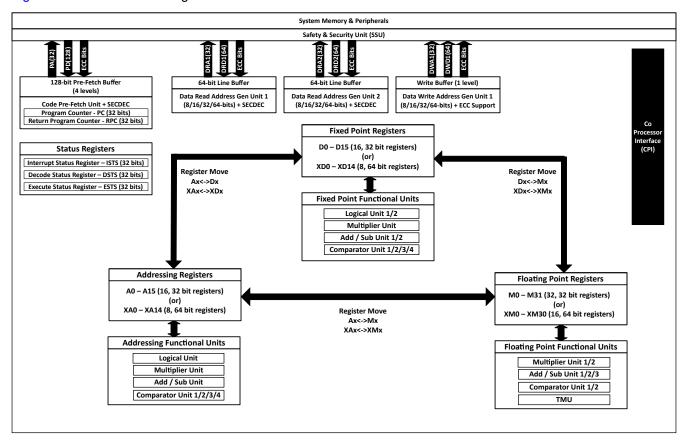

| 2.1 C29x CPU Architecture       13         2.2 CPU Registers       14         2.3 Instruction Packing       20         2.4 Stacks       21         3 Interrupts       25         3.1 CPU Interrupts Architecture Block Diagram       26         3.2 RESET, NMI, RTINT, and INT       27         3.3 Conditions Blocking Interrupts       30         3.4 CPU Interrupt Control Registers       31         3.5 Interrupt Nesting       34         3.6 Security       34         4 Pipeline       37         4.1 Introduction       38         4.2 Decoupled Pipeline Phases       40         4.3 Dual Instruction Prefetch Buffers       41         4.4 Pipeline Advancement and Stalls       42         4.5 Pipeline Hazards and Protection Mechanisms       42         4.6 Pegister Updates and Corresponding Pipeline Phases       44         4.7 Register Reads and Writes During Normal Operation       44         4.8 D2 Read Protection       46         4.9 E1 Read Protection       47         4.10 WAW Protection       48         4.11 Protection During Interrupt       49         5.1 Addressing Modes       50         5.1 Addressing Modes Overview       51         5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                  |    |

| 2.2 CPU Registers     14       2.3 Instruction Packing     20       2.4 Stacks     21       3 Interrupts     25       3.1 CPU Interrupts Architecture Block Diagram     26       3.2 RESET, NMI, RTINT, and INT     27       3.3 Conditions Blocking Interrupts     30       3.4 CPU Interrupt Control Registers     31       3.5 Interrupt Nesting     34       3.6 Security.     35       4 Pipeline     37       4.1 Introduction     38       4.2 Decoupled Pipeline Phases     40       4.3 Dual Instruction Prefetch Buffers     41       4.4 Pipeline Advancement and Stalls     42       4.5 Pipeline Hazards and Protection Mechanisms     42       4.6 Register Updates and Corresponding Pipeline Phases     44       4.7 Register Reads and Writes During Normal Operation     44       4.8 DZ Read Protection     46       4.9 E1 Read Protection     46       4.9 E1 Read Protection     47       4.10 WAW Protection     48       5.1 Addressing Modes     50       5.1 Addressing Modes Overview     51       5.2 Addressing Modes Considerations     52       5.2 Addressing Modes Solution     72       6.1 SN Overview     73       6.2 Links and Task Isolation     78       7.4 Tove                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                  |    |

| 2.3 Instruction Packing.       20         2.4 Stacks.       21         3 Interrupts.       25         3.1 CPU Interrupts Architecture Block Diagram.       26         3.2 RESET, NMI, RTINT, and INT.       27         3.3 Conditions Blocking Interrupts.       30         3.4 CPU Interrupt Control Registers.       31         3.5 Interrupt Nesting.       34         3.6 Security.       35         4 Pippeline       37         4.1 Introduction.       38         4.2 Decoupled Pipeline Phases.       40         4.3 Dual Instruction Prefetch Buffers.       40         4.4 Pipeline Advancement and Stalls.       41         4.5 Pipeline Hazards and Protection Mechanisms.       42         4.6 Register Updates and Corresponding Pipeline Phases.       44         4.7 Register Reads and Writes During Normal Operation.       44         4.8 D2 Read Protection.       46         4.9 E1 Read Protection.       46         4.9 E1 Read Protection.       47         4.10 WAW Protection.       48         4.11 Protection During Interrupt.       49         5 Addressing Modes.       50         5.1 Addressing Modes Soverview.       51         5.2 Addressing Mode Fields.       54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                  |    |

| 2.4 Stacks.       21         3 Interrupts       25         3.1 CPU Interrupts Architecture Block Diagram       26         3.2 RESET, NMI, RTINT, and INT.       27         3.3 Conditions Blocking Interrupts.       30         3.4 CPU Interrupt Control Registers.       31         3.5 Interrupt Nesting.       34         3.6 Security.       35         4 Pipeline.       37         4.1 Introduction.       38         4.2 Decoupled Pipeline Phases.       40         4.3 Dual Instruction Prefetch Buffers       41         4.4 Pipeline Advancement and Stalls.       42         4.5 Pipeline Hazards and Protection Mechanisms.       42         4.6 Register Updates and Corresponding Pipeline Phases.       44         4.7 Register Reads and Writes During Normal Operation.       44         4.8 D2 Read Protection.       46         4.9 E1 Read Protection.       46         4.9 E1 Read Protection.       46         4.9 It need Protection.       48         4.1 In Protection During Interrupt.       49         5 Addressing Modes       50         5.1 Addressing Modes Overview.       51         5.2 Addressing Mode Fields       54         5.3 Alignment and Pipeline Considerations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                  |    |

| 3 Interrupts       25         3.1 CPU Interrupts Architecture Block Diagram.       26         3.2 RESET, NMI, RTINT, and INT.       27         3.2 RESET, NMI, RTINT, and INT.       30         3.4 CPU Interrupt Control Registers.       30         3.5 Interrupt Nesting       34         3.6 Security.       35         4 Pipeline       37         4.1 Introduction.       38         4.2 Decoupled Pipeline Phases.       40         4.3 Dual Instruction Prefetch Buffers       41         4.4 Pipeline Advancement and Stalls.       42         4.5 Pipeline Hazards and Protection Mechanisms.       42         4.6 Register Updates and Corresponding Pipeline Phases.       44         4.7 Register Reads and Writes During Normal Operation       44         4.8 D2 Read Protection.       44         4.9 E1 Read Protection.       47         4.10 WAW Protection During Interrupt.       49         5 Addressing Modes.       50         5.1 Addressing Mode Soverview       51         5.2 Addressing Mode Fields       54         5.3 Alignment and Pipeline Considerations       62         6.4 Protected Call and Return.       72         6.1 SSU Overview.       73         6.2 Links and Task Isol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | •                                                |    |

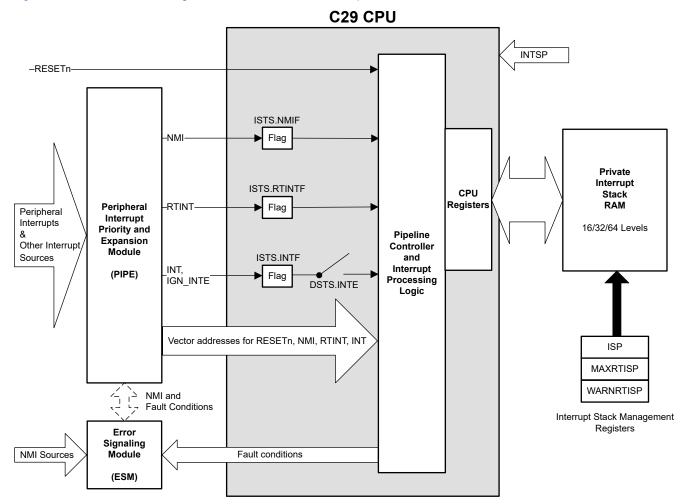

| 3.1 CPU Interrupts Architecture Block Diagram.       26         3.2 RESET, NMI, RTINT, and INT.       27         3.3 Conditions Blocking Interrupts.       30         3.4 CPU Interrupt Control Registers.       31         3.5 Interrupt Nesting.       34         3.6 Security.       35         4 Pipeline.       37         4.1 Introduction.       38         4.2 Decoupled Pipeline Phases.       40         4.3 Dual Instruction Prefetch Buffers.       41         4.4 Pipeline Advancement and Stalls.       42         4.5 Pipeline Hazards and Protection Mechanisms.       42         4.6 Register Updates and Corresponding Pipeline Phases.       44         4.7 Register Reads and Writes During Normal Operation.       44         4.8 D2 Read Protection.       46         4.9 E1 Read Protection.       46         4.9 It Protection During Interrupt.       48         4.11 Protection During Interrupt.       49         5 Addressing Modes       50         5.1 Addressing Mode Fields       54         5.2 Addressing Mode Fields       54         5.3 Alignment and Pipeline Considerations       62         5.4 Types of Addressing Modes.       50         5.1 SSU Overview.       72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                  |    |

| 3.2 RESET, NMI, RTINT, and INT       27         3.3 Conditions Blocking Interrupts.       30         3.4 CPU Interrupt Control Registers.       31         3.5 Interrupt Nesting.       34         3.6 Security.       35         4 Pipeline.       37         4.1 Introduction       38         4.2 Decoupled Pipeline Phases.       40         4.3 Dual Instruction Prefetch Buffers.       41         4.4 Pipeline Advancement and Stalls       42         4.5 Pipeline Hazards and Protection Mechanisms       42         4.6 Register Updates and Corresponding Pipeline Phases.       44         4.7 Register Reads and Writes During Normal Operation.       44         4.8 D2 Read Protection       44         4.9 E1 Read Protection       46         4.10 WAW Protection       47         4.11 Protection During Interrupt       49         5 Addressing Modes       50         5.1 Addressing Modes Overview       51         5.2 Addressing Modes Fields       51         5.3 Alignment and Pipeline Considerations       62         5.4 Types of Addressing Modes       63         6.3 Safety and Security Unit (SSU)       73         6.1 SSU Overview       73         6.2 Links and Task Isolation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                  |    |

| 3.3 Conditions Blocking Interrupts.       30         3.4 CPU Interrupt Control Registers.       31         3.5 Interrupt Nesting.       34         3.6 Security.       35         4 Pipeline.       37         4.1 Introduction       38         4.2 Decoupled Pipeline Phases.       40         4.3 Dual Instruction Prefetch Buffers.       41         4.4 Pipeline Advancement and Stalls.       42         4.5 Pipeline Hazards and Protection Mechanisms.       42         4.5 Pipeline Hazards and Protection Mechanisms.       42         4.6 Register Updates and Corresponding Pipeline Phases.       44         4.7 Register Reads and Writes During Normal Operation.       44         4.8 D2 Read Protection       46         4.9 E1 Read Protection       46         4.9 E2 Read Protection       48         4.11 Protection During Interrupt.       49         5 Addressing Modes.       50         5.1 Addressing Modes Overview.       51         5.2 Addressing Modes Fields.       54         5.3 Alignment and Pipeline Considerations.       52         5.4 Types of Addressing Modes.       62         5.1 SSU Overview.       73         6.2 Links and Task Isolation.       76         6.3 Prote                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                  |    |

| 3.4 CPU Interrupt Control Registers.       31         3.5 Interrupt Nesting.       34         3.6 Security.       35         4 Pipeline.       37         4.1 Introduction.       38         4.2 Decoupled Pipeline Phases.       40         4.3 Dual Instruction Prefetch Buffers.       41         4.4 Pipeline Advancement and Stalls.       42         4.5 Pipeline Hazards and Protection Mechanisms       42         4.6 Register Updates and Corresponding Pipeline Phases.       44         4.7 Register Reads and Writes During Normal Operation.       44         4.8 D2 Read Protection.       46         4.9 E1 Read Protection.       47         4.10 WAW Protection.       48         4.11 Protection During Interrupt.       49         5 Addressing Modes.       50         5.1 Addressing Modes Overview.       51         5.2 Addressing Mode Fields.       54         5.3 Alignment and Pipeline Considerations.       62         5.4 Types of Addressing Modes.       63         6.1 SSU Overview.       72         6.1 SSU Overview.       73         6.2 Links and Task Isolation.       74         6.3 Sharing Data Outside Task Isolation Boundary.       76         6.4 Protected Call and Ret                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                  |    |

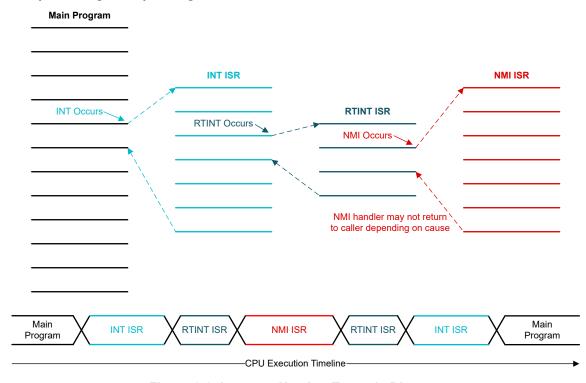

| 3.5 Interrupt Nesting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                  |    |

| 3.6 Security.       35         4 Pipeline.       37         4.1 Introduction.       38         4.2 Decoupled Pipeline Phases.       40         4.3 Dual Instruction Prefetch Buffers.       41         4.4 Pipeline Advancement and Stalls.       42         4.5 Pipeline Hazards and Protection Mechanisms.       42         4.6 Register Updates and Corresponding Pipeline Phases.       44         4.7 Register Reads and Writes During Normal Operation.       44         4.8 D2 Read Protection.       46         4.9 E1 Read Protection.       46         4.9 E1 Read Protection.       47         4.1 I WAW Protection.       48         4.1 1 Protection During Interrupt.       49         5 Addressing Modes       50         5.1 Addressing Modes Overview.       51         5.2 Addressing Mode Fields.       54         5.3 Alignment and Pipeline Considerations.       62         5.4 Types of Addressing Modes.       63         6 Safety and Security Unit (SSU).       72         6.1 SSU Overview.       73         6.2 Sharing Data Outside Task Isolation Boundary.       76         6.4 Protected Call and Return.       77         7 Emulation.       78         7.1 Overview of Emulation Feat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                  |    |

| 4 Pipeline       37         4.1 Introduction       38         4.2 Decoupled Pipeline Phases       40         4.3 Dual Instruction Prefetch Buffers       41         4.4 Pipeline Advancement and Stalls       42         4.5 Pipeline Hazards and Protection Mechanisms       42         4.6 Register Updates and Corresponding Pipeline Phases       44         4.7 Register Reads and Writes During Normal Operation       44         4.8 D2 Read Protection       46         4.9 E1 Read Protection       47         4.10 WAW Protection       48         4.11 Protection During Interrupt       48         5 Addressing Modes       50         5.1 Addressing Modes       50         5.2 Addressing Mode Fields       54         5.3 Alignment and Pipeline Considerations       62         5.4 Types of Addressing Modes       63         6 Safety and Security Unit (SSU)       72         6.1 SSU Overview       73         6.2 Links and Task Isolation       74         6.3 Sharing Data Outside Task Isolation Boundary       76         6.4 Protected Call and Return       77         7 Emulation       78         7.1 Overview of Emulation Features       79         7.2 Debug Terminology <td< td=""><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                  |    |

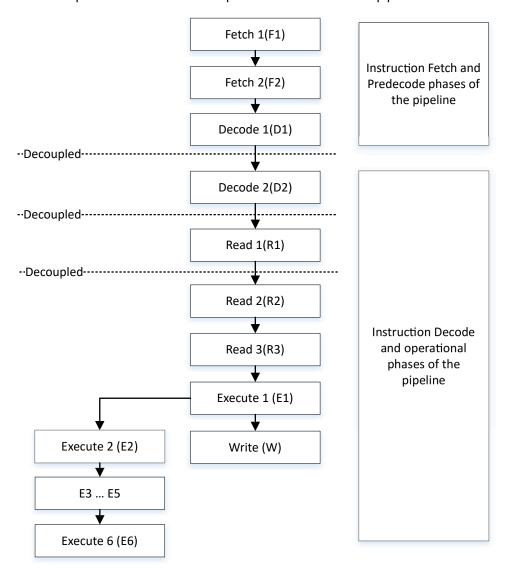

| 4.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                  |    |

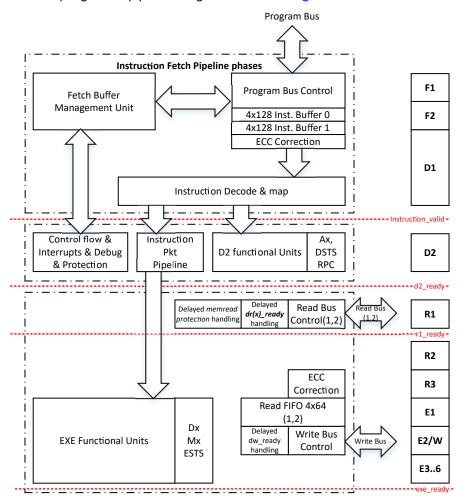

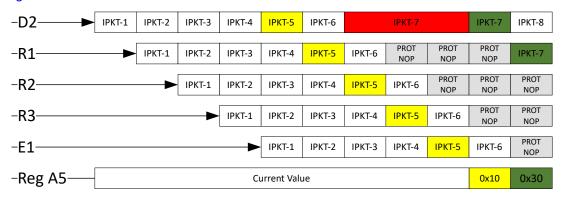

| 4.2 Decoupled Pipeline Phases.       40         4.3 Dual Instruction Prefetch Buffers.       41         4.4 Pipeline Advancement and Stalls.       42         4.5 Pipeline Hazards and Protection Mechanisms.       42         4.6 Register Updates and Corresponding Pipeline Phases.       44         4.7 Register Reads and Writes During Normal Operation.       44         4.8 D2 Read Protection.       46         4.9 E1 Read Protection.       47         4.10 WAW Protection.       48         4.11 Protection During Interrupt.       49         5 Addressing Modes.       50         5.1 Addressing Modes Overview.       51         5.2 Addressing Mode Fields.       54         5.3 Alignment and Pipeline Considerations.       62         5.4 Types of Addressing Modes.       63         6 Safety and Security Unit (SSU).       72         6.1 SSU Overview.       73         6.2 Links and Task Isolation.       74         6.3 Pharing Data Outside Task Isolation Boundary.       76         6.4 Protected Call and Return.       77         7 Emulation.       78         7.1 Overview of Emulation Features.       79         7.2 Debug Terminology.       79         7.3 Debug Interface.       79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                  |    |

| 4.3 Dual Instruction Prefetch Buffers       41         4.4 Pipeline Advancement and Stalls       42         4.5 Pipeline Hazards and Protection Mechanisms       42         4.6 Register Updates and Corresponding Pipeline Phases       44         4.7 Register Reads and Writes During Normal Operation       44         4.8 D2 Read Protection       46         4.9 E1 Read Protection       47         4.10 WAW Protection       48         4.11 Protection During Interrupt       49         5 Addressing Modes       50         5.1 Addressing Modes Overview       51         5.2 Addressing Mode Fields       54         5.3 Alignment and Pipeline Considerations       62         5.4 Types of Addressing Modes       63         6 Safety and Security Unit (SSU)       72         6.1 SSU Overview       73         6.2 Links and Task Isolation       74         6.3 Sharing Data Outside Task Isolation Boundary       76         6.4 Protected Call and Return       77         7 Emulation       78         7.1 Overview of Emulation Features       79         7.2 Debug Terminology       79         7.3 Debug Interface       79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                  |    |

| 4.4 Pipeline Advancement and Stalls       42         4.5 Pipeline Hazards and Protection Mechanisms       42         4.6 Register Updates and Corresponding Pipeline Phases       44         4.7 Register Reads and Writes During Normal Operation       44         4.8 D2 Read Protection       46         4.9 E1 Read Protection       47         4.10 WAW Protection       48         4.11 Protection During Interrupt       49         5 Addressing Modes       50         5.1 Addressing Modes Overview       51         5.2 Addressing Mode Fields       54         5.3 Alignment and Pipeline Considerations       62         5.4 Types of Addressing Modes       63         6 Safety and Security Unit (SSU)       72         6.1 SSU Overview       73         6.2 Links and Task Isolation       74         6.3 Sharing Data Outside Task Isolation Boundary       76         6.4 Protected Call and Return       77         7 Emulation       78         7.1 Overview of Emulation Features       79         7.2 Debug Terminology       79         7.3 Debug Interface       79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                  |    |

| 4.5 Pipeline Hazards and Protection Mechanisms       42         4.6 Register Updates and Corresponding Pipeline Phases       44         4.7 Register Reads and Writes During Normal Operation       44         4.8 D2 Read Protection       46         4.9 E1 Read Protection       47         4.10 WAW Protection       48         4.11 Protection During Interrupt       49         5 Addressing Modes       50         5.1 Addressing Modes Overview       51         5.2 Addressing Mode Fields       54         5.3 Alignment and Pipeline Considerations       62         5.4 Types of Addressing Modes       63         6 Safety and Security Unit (SSU)       72         6.1 SSU Overview       73         6.2 Links and Task Isolation       74         6.3 Sharing Data Outside Task Isolation Boundary       76         6.4 Protected Call and Return       77         7 Emulation       78         7.1 Overview of Emulation Features       79         7.2 Debug Terminology       79         7.3 Debug Interface       79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                  |    |

| 4.6 Register Updates and Corresponding Pipeline Phases       44         4.7 Register Reads and Writes During Normal Operation       44         4.8 D2 Read Protection       46         4.9 E1 Read Protection       47         4.10 WAW Protection       48         4.11 Protection During Interrupt       49         5 Addressing Modes       50         5.1 Addressing Modes Overview       51         5.2 Addressing Mode Fields       54         5.3 Alignment and Pipeline Considerations       62         5.4 Types of Addressing Modes       63         6 Safety and Security Unit (SSU)       72         6.1 SSU Overview       73         6.2 Links and Task Isolation       74         6.3 Sharing Data Outside Task Isolation Boundary       76         6.4 Protected Call and Return       77         7 Emulation       78         7.1 Overview of Emulation Features       79         7.2 Debug Terminology       79         7.3 Debug Interface       79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                  |    |

| 4.7 Register Reads and Writes During Normal Operation       44         4.8 D2 Read Protection       46         4.9 E1 Read Protection       47         4.10 WAW Protection       48         4.11 Protection During Interrupt       49         5 Addressing Modes       50         5.1 Addressing Modes Overview       51         5.2 Addressing Mode Fields       54         5.3 Alignment and Pipeline Considerations       62         5.4 Types of Addressing Modes       63         6 Safety and Security Unit (SSU)       72         6.1 SSU Overview       73         6.2 Links and Task Isolation       74         6.3 Sharing Data Outside Task Isolation Boundary       76         6.4 Protected Call and Return       77         7 Emulation       78         7.1 Overview of Emulation Features       79         7.2 Debug Terminology       79         7.3 Debug Interface       79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                  |    |

| 4.8 D2 Read Protection       46         4.9 E1 Read Protection       47         4.10 WAW Protection       48         4.11 Protection During Interrupt       49         5 Addressing Modes       50         5.1 Addressing Modes Overview       51         5.2 Addressing Mode Fields       54         5.3 Alignment and Pipeline Considerations       62         5.4 Types of Addressing Modes       63         6 Safety and Security Unit (SSU)       72         6.1 SSU Overview       73         6.2 Links and Task Isolation       74         6.3 Sharing Data Outside Task Isolation Boundary       76         6.4 Protected Call and Return       77         7 Emulation       78         7.1 Overview of Emulation Features       79         7.2 Debug Terminology       79         7.3 Debug Interface       79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                  |    |

| 4.9 E1 Read Protection.       47         4.10 WAW Protection.       48         4.11 Protection During Interrupt.       49         5 Addressing Modes.       50         5.1 Addressing Modes Overview.       51         5.2 Addressing Mode Fields.       54         5.3 Alignment and Pipeline Considerations.       62         5.4 Types of Addressing Modes.       63         6 Safety and Security Unit (SSU).       72         6.1 SSU Overview.       73         6.2 Links and Task Isolation.       74         6.3 Sharing Data Outside Task Isolation Boundary.       76         6.4 Protected Call and Return.       77         7 Emulation.       78         7.1 Overview of Emulation Features.       79         7.2 Debug Terminology.       79         7.3 Debug Interface.       79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                  |    |

| 4.10 WAW Protection.       48         4.11 Protection During Interrupt.       49         5 Addressing Modes.       50         5.1 Addressing Modes Overview.       51         5.2 Addressing Mode Fields.       54         5.3 Alignment and Pipeline Considerations.       62         5.4 Types of Addressing Modes.       63         6 Safety and Security Unit (SSU).       72         6.1 SSU Overview.       73         6.2 Links and Task Isolation       74         6.3 Sharing Data Outside Task Isolation Boundary.       76         6.4 Protected Call and Return.       77         7 Emulation.       78         7.1 Overview of Emulation Features.       79         7.2 Debug Terminology.       79         7.3 Debug Interface.       79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                  |    |

| 4.11 Protection During Interrupt.       49         5 Addressing Modes       50         5.1 Addressing Modes Overview.       51         5.2 Addressing Mode Fields.       54         5.3 Alignment and Pipeline Considerations.       62         5.4 Types of Addressing Modes.       63         6 Safety and Security Unit (SSU).       72         6.1 SSU Overview.       73         6.2 Links and Task Isolation       74         6.3 Sharing Data Outside Task Isolation Boundary.       76         6.4 Protected Call and Return.       77         7 Emulation.       78         7.1 Overview of Emulation Features.       79         7.2 Debug Terminology.       79         7.3 Debug Interface.       79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                  |    |

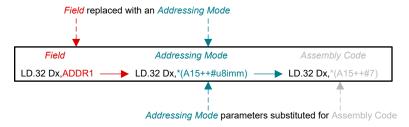

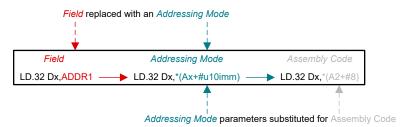

| 5 Addressing Modes       50         5.1 Addressing Modes Overview       51         5.2 Addressing Mode Fields       54         5.3 Alignment and Pipeline Considerations       62         5.4 Types of Addressing Modes       63         6 Safety and Security Unit (SSU)       72         6.1 SSU Overview       73         6.2 Links and Task Isolation       74         6.3 Sharing Data Outside Task Isolation Boundary       76         6.4 Protected Call and Return       77         7 Emulation       78         7.1 Overview of Emulation Features       79         7.2 Debug Terminology       79         7.3 Debug Interface       79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                  |    |

| 5.1 Addressing Modes Overview.       51         5.2 Addressing Mode Fields.       54         5.3 Alignment and Pipeline Considerations.       62         5.4 Types of Addressing Modes.       63         6 Safety and Security Unit (SSU).       72         6.1 SSU Overview.       73         6.2 Links and Task Isolation.       74         6.3 Sharing Data Outside Task Isolation Boundary.       76         6.4 Protected Call and Return.       77         7 Emulation.       78         7.1 Overview of Emulation Features.       79         7.2 Debug Terminology.       79         7.3 Debug Interface.       79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                  |    |

| 5.2 Addressing Mode Fields       54         5.3 Alignment and Pipeline Considerations       62         5.4 Types of Addressing Modes       63         6 Safety and Security Unit (SSU)       72         6.1 SSU Overview       73         6.2 Links and Task Isolation       74         6.3 Sharing Data Outside Task Isolation Boundary       76         6.4 Protected Call and Return       77         7 Emulation       78         7.1 Overview of Emulation Features       79         7.2 Debug Terminology       79         7.3 Debug Interface       79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                  |    |

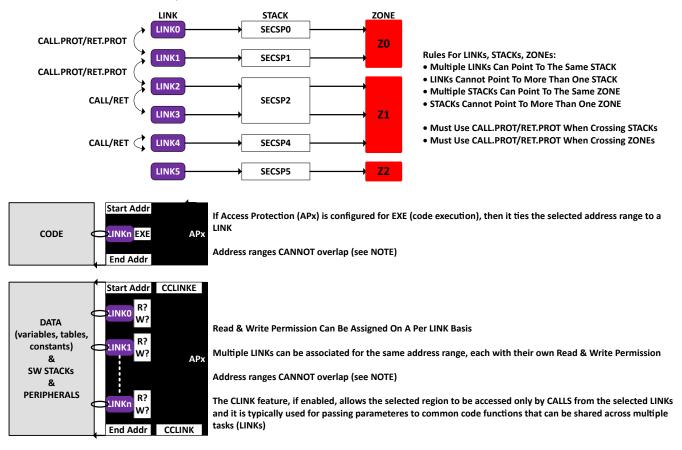

| 5.3 Alignment and Pipeline Considerations.       62         5.4 Types of Addressing Modes.       63         6 Safety and Security Unit (SSU).       72         6.1 SSU Overview.       73         6.2 Links and Task Isolation.       74         6.3 Sharing Data Outside Task Isolation Boundary.       76         6.4 Protected Call and Return.       77         7 Emulation.       78         7.1 Overview of Emulation Features.       79         7.2 Debug Terminology.       79         7.3 Debug Interface.       79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                  |    |