# **Current Limiting with Comparator Circuit**

Chuck Sins

#### **Design Goals**

| LOAD CURRENT (I <sub>L</sub> )  | SYSTEM SUPPLY (V <sub>S</sub> ) | CURRENT SENSE AMP | COMPARATOR                       | DUTPUT STATUS                         |

|---------------------------------|---------------------------------|-------------------|----------------------------------|---------------------------------------|

| Over Current (I <sub>OC</sub> ) | Typical                         | Gain              | Over Current                     | Normal Operation                      |

| 200mA                           | 24V                             | 20V/V             | V <sub>OH</sub> = V <sub>S</sub> | V <sub>OL</sub> = V <sub>S</sub> - 5V |

#### **Design Description**

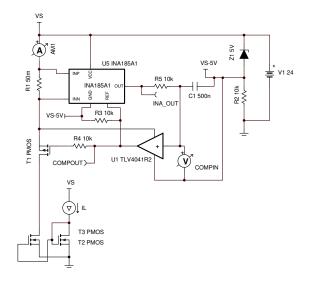

This high-side, current sensing solution uses a current sense amplifier, a comparator with an integrated reference, and a P-channel MOSFET to create an over-current latch circuit. When a load current greater than 200mA is detected, the circuit disconnects the system from its power source. Since the comparator drives the gate of the P-channel MOSFET and feeds the signal back into the reference pin of the current sense amplifier, the comparator output will latch (hold the gate source voltage of the P-channel MOSFET to 0V) until power to the circuit is cycled.

#### **Design Notes**

- 1. Select a precision, current sense amplifier (INA) with an external reference pin so its output voltage can be adjusted.

- 2. Select a comparator with a rail-to-rail input so its output will be valid over the entire operating voltage range of the current sense amplifier.

- 3. Select a comparator with a push-pull output stage that can drive the gate of a MOSFET and an integrated reference to optimize circuit accuracy.

- 4. Create a floating 5V supply that can power the INA and comparator.

#### **Design Steps**

Select the value of R<sub>1</sub> so V<sub>SHUNT</sub> is at least 100x greater than the current sense amplifier input offset voltage (V<sub>OS</sub>). Note that making R<sub>6</sub> very large will improve OC detection accuracy but will reduce supply headroom and power dissipation.

$$V_{SHUNT} = (I_{OC} \times R_1) \ge 100 \times V_{OS}$$

Set

$$R_1 \ge \frac{100 \times V_{OS}}{I_{OC}} = 50 \text{m}\Omega$$

for  $I_{OC} = 200 \text{mA}$  &  $V_{OS} = 100 \mu V$

2. Determine the desired gain  $(A_V)$  option for the INA based on the switching threshold of the comparator. When the load current  $(I_L)$  reaches the over-current threshold  $(I_{OC})$ , the INA output must cross the switching threshold  $(V_{TH})$  of the comparator.

$$V_{TH} = (I_{OC} \times R_1) \times A_V = 0.2V$$

Set

$$A_V = \frac{V_{TH}}{I_{OC} \times R_1} = \frac{0.2}{0.2 \times 0.05} = 20 V/V$$

for  $R_1 = 50 m\Omega$

- 3. Since many INA's and comparators have 5V operating voltage ranges, a 5V supply voltage needs to be derived from the system supply  $V_S$ . In addition, the 5V supply needs to float below  $V_S$  so the comparator output can drive the source-gate voltage of the P-channel MOSFET to 0V when an over-current condition occurs and 5V when the load current is less than  $I_{OC}$ . The method used in this circuit is a 5V zener diode with a 10 k $\Omega$  bias resistor ( $R_2$ ). Other options such as shunt regulators can also be utilized as long as proper bias current through the device is maintained.

- 4. A low pass filter is added between the INA output and the comparator input to attenuate any high frequency current spikes. It is more important to trigger the over-current latch with a delay than to falsely disconnect the system from the supply voltage. The low pass filter is derived from R<sub>5</sub> and C<sub>1</sub>. Since the switching threshold of the comparator is 0.2V, the delay is less than 1 time constant (R<sub>5</sub>×C<sub>1</sub>=5ms).

- 5. A current limiting resistor  $R_4$  is inserted between the comparator output and the gate of the P-channel MOSFET. Setting  $R_4$  to 10 k $\Omega$  reduces current spikes on the supply when the comparator output needs to charge the MOSFET gate-source capacitance as a compromise to increasing the charge time. Inserting  $R_4$  also serves the purpose of protecting the comparator output from any supply transients that can be present on the supply line.

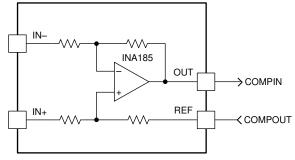

- 6. The output of the comparator is directly connected to the REF pin of the INA in order to apply an offset to the INA's output voltage. When  $I_L < I_{OC}$ , the comparator output is low (equal to  $V_S$ -5V) and no offset is added to the INA. However, when  $I_L > I_{OC}$ , the comparator output goes high (equal to  $V_S$ ) and a 5V offset is added to the INA. This offset causes the INA output to saturate at a level equal to  $V_S$ . Since an INA output level of  $V_S$  is higher than the  $V_{TH}$  of the comparator, the comparator output will remain high. This condition is referred to as a *latched* output state since the circuit will remain in this state until power to the circuit is cycled.

- 7. R<sub>3</sub> is added between the INA reference pin (REF) and GND (V<sub>S</sub>-5V) to ensure a proper ground path as the 5V supply ramps up to the comparator minimum operating voltage.

- 8. If a latching feature is not preferred, the comparator output can be disconnected from the current sense amplifier reference pin and R<sub>3</sub> can be replaced with a short. In this configuration, the circuit will behave as a 200mA current limiter.

www.ti.com Trademarks

# **Design Simulations**

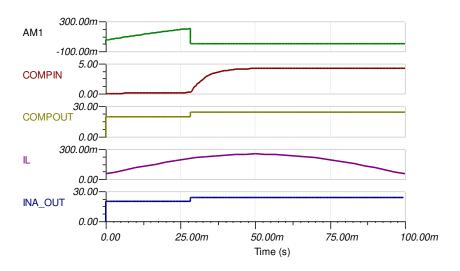

#### **Transient Simulation Results**

## **Design References**

Texas Instruments, SBVM944 simulation file, circuit software

## **Design Featured Comparator**

| TLV4041R2            |              |  |  |

|----------------------|--------------|--|--|

| V <sub>S</sub>       | 1.6V to 5.5V |  |  |

| V <sub>inCM</sub>    | Rail-to-rail |  |  |

| V <sub>OUT</sub>     | Push-Pull    |  |  |

| Integrated Reference | 200mV ± 3mV  |  |  |

| IQ                   | 2μΑ          |  |  |

| t <sub>PD</sub>      | 360ns        |  |  |

| TLV4041R2            |              |  |  |

# **Design Featured Current Sense Amplifier**

| INA185            |                                   |  |  |

|-------------------|-----------------------------------|--|--|

| V <sub>S</sub>    | 2.7V to 5.5V                      |  |  |

| V <sub>inCM</sub> | -0.2V to 26V                      |  |  |

| Gain Options      | 20V/V, 50V/V, 100V/V, 200V/V      |  |  |

| Gain Error        | 0.2 %                             |  |  |

| V <sub>os</sub>   | 100μV (A1), 25μV (A2, A3, and A4) |  |  |

| IQ                | 200μΑ                             |  |  |

| INA185            |                                   |  |  |

# **Trademarks**

All trademarks are the property of their respective owners.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated