# Application Note How to Compensate for Cable Losses With BQ25758

Jeff Falin

#### ABSTRACT

Many dc/dc converters like BQ25758 provide a remote sense pin for regulating the converters output voltage. This remote sense pin can be unable to connect directly to the system load. A cable that connects this regulated output to the system load has a finite resistance. The voltage drop created by this resistance and load current varies with system load. This results in the load voltage being less than the programmed voltage as the system load increases. This application note provides an external analog circuit to compensate for the resistive voltage drop across a cable as a function of system load.

### **Table of Contents**

| 1 Introduction     | 2 |

|--------------------|---|

| 2 Derivation       |   |

| 3 Measured Results |   |

| 4 Summary          |   |

| 5 References       |   |

|                    |   |

### **List of Figures**

| Figure 1-1. BQ25758 Typical Application Block Diagram             | 2 |

|-------------------------------------------------------------------|---|

| ······································                            |   |

| Figure 2-1. BQ25758 with Cable Compensation Circuit Block Diagram | 2 |

|                                                                   |   |

### List of Tables

| Table 3-1. Measured Results for VAC = 20V and $T_A$ = 25° | C4 |

|-----------------------------------------------------------|----|

|-----------------------------------------------------------|----|

### Trademarks

All trademarks are the property of their respective owners.

# **1** Introduction

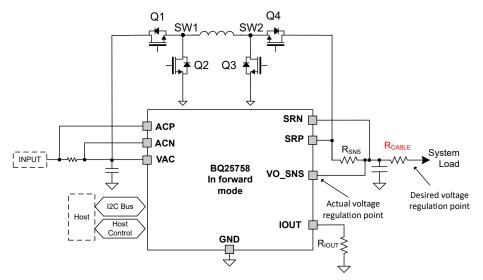

Figure 1-1 is a block diagram of the BQ25758 dc/dc regulator.

Figure 1-1. BQ25758 Typical Application Block Diagram

The BQ25758's regulation point is the VO\_SNS pin. The converter's VO\_SNS is connected as close as possible to the system load to account for resistance losses. However, if a cable is required to connect the output of the end equipment to the system load, the cable resistance causes a voltage drop from the VO\_SNS regulation point to the system load. If the cable resistance and the system load current is always known, or an ADC is available to measure the system load, host software can increase the regulation point as a function of system load to account for the voltage drop. Typically, the system load varies too much or too quickly for the host software to respond. A different method to dynamically compensate for the voltage drop across a known cable resistance is presented in the following section.

## 2 Derivation

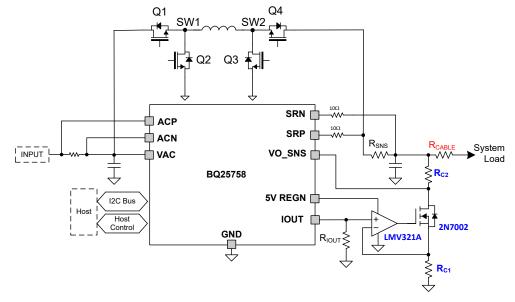

Composed of four additional components, an analog feedback circuit, as highlighted in blue in Figure 2-1, can account for the voltage drop across the cable as a function of system load.

Figure 2-1. BQ25758 with Cable Compensation Circuit Block Diagram

$$V(SRN) = V_{OUT\_REG} + I_{SYS} \times R_{CABLE} = V_{SYS\_LOAD} + I_{SYS} \times R_{CABLE}$$

(1)

The IOUT pin voltage, V(IOUT), is proportional to the system load current as sensed across resistor  $R_{SNS}$  by SRN and SRP pins. Specifically,

$$V(IOUT) = \frac{I_{SYS} \times V_{REF\_IOUT} \times R_{IOUT}}{K_{IOUT}(A \times k\Omega)}$$

(2)

Where V<sub>REF\_IOUT</sub> is 2V  $\pm$  0.5% and K<sub>IOUT</sub> is 50A x k $\Omega \pm$  4%. The LMV321A amplifier negative feedback loop regulates the voltage across compensation resistor RC1 to be V(IOUT) so

$$V_{OUT\_REG} + \frac{V(IOUT)}{R_{C1}} \times R_{C2} = V(SRN)$$

(3)

Combining these equations gives

$$V_{SYS\_LOAD} + I_{SYS} \times R_{CABLE} = V_{OUT\_REG} + \frac{I_{SYS} \times V_{REF\_IOUT} \times R_{IOUT}}{K_{IOUT}(A \times k\Omega)} \times \frac{R_{C2}}{R_{C1}}$$

(4)

Where as,

$$V_{SYS\_LOAD} + I_{SYS} \times R_{CABLE} = V_{OUT\_REG} + \frac{I_{SYS} \times V_{REF\_IOUT} \times R_{IOUT}}{K_{IOUT}(A \times k\Omega)} \times \frac{R_{C2}}{R_{C1}}$$

(5)

Which reduces to

$$\frac{R_{C2}}{R_{C1}} = R_{CABLE} \times \frac{K_{IOUT}(A \times k\Omega)}{V_{REF_{-}IOUT} \times R_{IOUT}}$$

(6)

With  $R_{SNS} \ll R_{CABLE}$  and knowing that  $K_{IOUT}/V_{REF_IOUT}$  is approximately  $125\Omega / R_{SNS}$ , the equation below can be used to find the value of one compensation resistors after selecting the other to be in the  $10k\Omega$  range.

$$\frac{R_{C2}}{R_{C1}} = \frac{125\Omega \times R_{CABLE}}{R_{SNS} \times R_{IOUT}}$$

(7)

### **3 Measured Results**

With PFM disabled to lower the voltage regulation point at no load, the converter's voltage regulation accuracy over temperature at the VO\_SNS pin is  $\pm 2\%$ , regardless of system load current. If R<sub>CABLE</sub> = 0.250 $\Omega$  connects VO\_SNS to the system load and no cable compensation is provided, the voltage at VSYS\_LOAD can be VOUT\_REG  $\pm 2\%$  - 0.250mV/A of system load.

The cable compensation circuit intends to correct for this reduction in voltage at the system load. Measured results with the cable compensation circuit,  $R_{CABLE} = 0.250\Omega$ ,  $R_{IOUT} = 6.19k\Omega$ , RC1 = 10k $\Omega$  and from Equation 7, RC2 =10.1k $\Omega$  are shown in Table 3-1.

| VOUT_REG (V) | ISYS_LOAD (A) | VSYS_LOAD (V) |

|--------------|---------------|---------------|

| 5            | 0             | 5.007         |

| 5            | 1             | 5.035         |

| 5            | 3             | 5.063         |

| 9            | 0             | 9.025         |

| 9            | 1             | 9.042         |

| 9            | 3             | 9.066         |

| 12           | 0             | 12.018        |

| 12           | 1             | 12.037        |

| 12           | 3             | 12.063        |

| 15           | 0             | 15.023        |

| 15           | 1             | 15.046        |

| 15           | 3             | 15.072        |

| 15           | 5             | 15.090        |

| 20           | 0             | 20.057        |

| 20           | 1             | 20.077        |

| 20           | 3             | 20.095        |

| 20           | 5             | 20.105        |

#### Table 3-1. Measured Results for VAC = 20V and $T_A = 25^{\circ}C$

With V(IOUT) having K ±4% and VREF ± 0.5% variation in the computation and ignoring the effects of ±0.5% or better resistors, the worst case dc regulation accuracy over temperature is ± (4%+0.5%+2%) = 6.5% with an average +14mV/A rising slope, a 20X improvement over the -250mV/A for a 0.250 $\Omega$  cable.

### 4 Summary

This application note provides an external analog circuit, consisting of an op amp, n-channel mosfet and two resistors, to compensate for the resistive losses that create a voltage drop from the BQ25758 VO\_SNS pin to the system load connection point.

### 5 References

- Texas Instruments, BQ25758: I2C Controlled, Bidirectional Buck-Boost Controller with Wide Voltage Range, data sheet.

- Texas Instruments, LMV3xxA Low-Voltage Rail-to-Rail Output Operational Amplifiers, data sheet.

- Onsemi, 2N7002-N-Channel Enhancement Mode Field Effect Transistor, data sheet.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated