# Application Brief Configure a One Shot With TI Programmable Logic Devices

Texas Instruments

#### Malcolm Lyn

#### Interface Logic

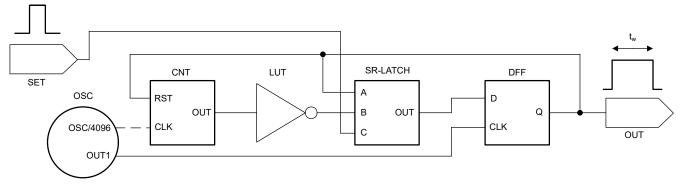

TI programmable logic devices (TPLD) can be configured to behave as monostable multivibrators (also known as one-shots), which, upon receiving an input trigger signal of variable length, output a fixed length pulse signal. The design captured in Figure 1 utilizes the internal oscillator, counter, and lookup table modules in a TPLD device to act as a non-retriggerrable one-shot.

Figure 1. One Shot Schematic

#### **Example Configuration**

The 2MHz oscillator is predivided by 8 and outputs a frequency of 250kHz. The counter module (CNT in Figure 1) further divides this frequency by 4096, and thus is driven by a 61Hz signal on the CLK input. The counter module data is set to 255, meaning the counter outputs a high pulse every 255 clock cycles. In this design, the input frequency to the counter module has a period of  $1 \div 61Hz = 16.4ms$ , which means the counter pulses high approximately every 4.2s. This means the output pulse width will be approximately 4.2s upon receiving an appropriate input trigger signal.

| OSCILLATOR 💿                |                        |     |                            |                               |     |

|-----------------------------|------------------------|-----|----------------------------|-------------------------------|-----|

| Name                        | OSC                    |     |                            |                               |     |

| Label                       |                        |     | COUNTER 💿                  |                               |     |

| Power Mode                  | Auto Power On          | -   |                            |                               |     |

| Clock Source                | Internal RC Oscillator | -   | Name                       | CNT                           |     |

| Frequency                   | 2 MHz                  | -   | Label                      |                               |     |

| Clock Pre Divider           | /8                     | *   | Clock Source               | OSC/4096                      | •   |

| OUT0 Second Stage Divider   | /12                    |     | Control Data               | 255                           |     |

| OUT1 Second Stage Divider   | /12                    | -   | Reset Mode                 | Both falling and rising edges | *   |

| Power Control Source Select | From register          | *   | Device MacroCell Allocated | LUT4_0_CNTDLY2                | ₹ 🖯 |

| PDWN Control                | Power down             | Ŧ   |                            |                               |     |

| Device MacroCell Allocated  | OSC0                   | - € |                            |                               |     |

### Figure 2. Oscillator and Counter Configurations

1

The output of the counter module is inverted and connected to a lookup table configured as an SR-Latch. The *C* input of the LUT configured as an SR-Latch is connected to the input pin named *SET* which provides the desired trigger signal. When *SET* pulses high, the SR-Latch outputs high and the DFF latches the input signal and begins outputting the pulse signal. The DFF also resets the counter module so that the counter module has to count all 255 clock cycles from the internal oscillator. Once the counter receives 255 clock cycles from the internal oscillator, the module pulses high, causing the SR-Latch to reset the DFF until the *SET* pin receives another high pulse.

| LOOKUP TABLE 🔊                 |                 | ۹ (D D | D FLIP FLOP 💿              |                  |   |

|--------------------------------|-----------------|--------|----------------------------|------------------|---|

| Name                           | SR-LATCH        |        | Name<br>Label              | DFF              |   |

| Label                          | , +1 more lines |        | Mode                       | DFF              |   |

| Number of Inputs               | 3               | •      | Generate Inverted Output   |                  |   |

| Boolean Function<br>Equation   | Equation        | *      | Invert Clock Input         |                  |   |

| Disable Top Label Calculations | (A & B)   C     |        | Initial Polarity           | Low              | • |

| Device MacroCell Allocated     | LUT3_2          | - €    | Reset/Set Select           | No Reset or Set  | * |

|                                |                 |        | Device MacroCell Allocated | Any(LUT2_1_DFF1) | • |

## Figure 3. DFF and LUT (SR-Latch) Configurations

#### **Design Considerations**

- The output pulse width can be calculated using the equation (counter data × t<sub>CNT</sub>), where t<sub>CNT</sub> is equal to the period of the counter CLK input or (1 ÷ counter clock frequency). In the above design, the counter clock frequency was 61Hz and t<sub>CNT</sub> was 16.4ms

- The input pulse width must be greater than 3t<sub>CNT</sub> to trigger the one-shot, since the counter module pulses high for the next two incoming clock cycles upon reset

- TPLD oscillators have an accuracy of ±5% and the output pulse width can vary considerably from device to device. If precision pulse generation is necessary, consider providing an external clock signal from a crystal oscillator

- If a button or otherwise noisy input signal is being used to trigger the pulse, configure the input pin as a Schmitt trigger input and provide an external RC filter to prevent unwanted pulses from triggering

- Need additional assistance? Ask our engineers a question on the *TI E2E<sup>™</sup> logic support forum*.

## Trademarks

E2E<sup>™</sup> is a trademark of Texas Instruments. All trademarks are the property of their respective owners.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated