# Analog Engineer's Circuit Auxiliary Circuits for High-Performance Audio

Paul Frost

#### **Design Goals**

| LDO Input Voltage | LDO Output Voltage | Voltage Supervisor Mute Threshold <sup>(1)</sup> |

|-------------------|--------------------|--------------------------------------------------|

| 12V               | 3.3V               | 7V                                               |

(1) If the V<sub>BATTERY</sub> voltage is below this threshold, MUTE should be asserted.

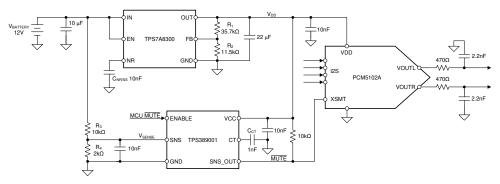

#### **Design Description**

Power conditioning is a critical aspect in audio applications. Circuits commonly found in automotive head units and premium aftermarket automotive audio systems will implement a hardware level mute that verifies that the audio digital-to-analog converters (DACs) and amplifiers are muted as supplies are established. The supplies will also need some conditioning to reduce noise coupled into the audio DAC. This circuit shows a low-noise, low-dropout (LDO) voltage regulator used to generate the +3.3-V supply for an audio DAC. An added benefit of an LDO is that there is a wider input voltage range at which the LDO can maintain the supply voltage. A voltage supervisor is used to notify the DAC when the source of the LDO begins to collapse, so the audio DAC can soft-mute the output before its supply is removed. This will reduce unwanted clicking or pops during shutdown and startup.

### **Design Notes**

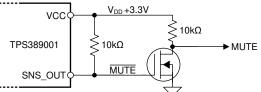

In this circuit the DAC mutes the output when soft-mute pin (XSMT) is held low, but not all DACs feature active-low mute inputs. Some devices feature enable signals for other devices such as mute switches and amplifiers require MUTE to be active high. In those cases, a simple N-channel MOSFET can be added to the output to invert the signal.

2. During power-up events, the capacitor on the CT pin ( $C_{CT}$ ) of the supervisor allows additional delay from when the SNS pin value rises above the threshold voltage and when the SNS\_OUT goes high. This can be used to the delay the deactivation of the MUTE output for the LDO to establish its voltage (as it must charge the output capacitors). In addition, this can be useful if there are other devices that need time to initialize

before the DAC comes out of mute. The additional propagation delay can be calculated using the following equation:

$t_{PD} = C_{CT} \times 1.07s + 25\mu s$

- 3. Brown-out events occur when the supplies of a device are partially reduced, but not low enough to issue a full power-on reset (POR) within the device. For this reason, it is recommended to confirm a full reset occurs during these events. The supervisor circuit accomplishes this as the XSMT acts as a reset circuit for the audio DAC.

- 4. Most audio DACs operate in either a VCOM or VREF architecture. The VCOM architecture uses a simple voltage divider from the supply to create the output amplitude reference. This is beneficial as it ensures that there will not be output clipping from the DAC if the supply is not the nominal value, as the output scales with the input voltage. The drawback of this architecture is the limited power-supply rejection ratio (PSRR) for the power supply noise. While a capacitor on the VCOM pin of the audio DAC will provide some filtering, it may still impact the output.

In a VREF configuration, an internal reference is generated by the audio DAC. This will result in better PSRR performance for the system. The drawback of this design is that if the supply voltage does drop, the output could clip.

## **Design Steps**

- 1. Select an LDO regulator for its current output capability, voltage-input range, and output noise. At minimum, the LDO sourcing the audio DAC must be able to supply the required current of the DAC. In addition, if there are other devices on the same bus, such as amplifiers, then the quiescent current of those devices must be taken into account. The LDO input voltage range must accommodate the main supply source, which, in this circuit, is assumed to be a 12-V battery.

- 2. The feedback (FB) voltage must be calculated to provide the correct output voltage. In this circuit, the resistors  $R_1$  and  $R_2$  can be calculated as the following shows.

$$R_1 = R_2 \left( \frac{V_{DD}}{V_{REF}} - 1 \right)$$

Given the design goal of +3.3V for V<sub>DD</sub>, and the V<sub>REF</sub> for this LDO is approximately 0.8V, use a R<sub>1</sub> of 35.7k $\Omega$  and R<sub>2</sub> of 11.5k $\Omega$ . In addition, note that the FB node has a current requirement and it is recommended that the following equation is used for guidance when selecting R2.

$$\frac{V_{REF}}{R_2} > 5\mu A$$

- 3. Select the voltage supervisor for the features desired in the system. In this circuit, the selected supervisor has an enable input pin. This feature allows a user (or microcontroller) mute signal to be used to override the supervisor output. In addition, some supervisors allow multiple supply rails to be monitored, which is useful for the output amplifiers.

- 4. The sense voltage is calculated using the following equation.

$$V_{SENSE} = V_{BATTERY} \times \frac{R_4}{R_3 + R_4}$$

The SNS-OUT pin is pulled low when the SNS voltage is less than the reference voltage, approximately 1.15V. Using 10k $\Omega$  for R<sub>3</sub> and 2k $\Omega$  for R<sub>4</sub>, it is estimated that the device will be muted if the V<sub>BATTERY</sub> supply drops below approximately 6.9V.

The capacitor C<sub>NR/SS</sub> is used by the LDO to reduce noise and enables the LDO soft-start function.

5. The DAC is selected based on the needs of the application. Consider the required SNR, THD+N, and supported I2S interface sample rates. While most audio DACs support rates ranging from 16kHz to 192kHz, not all support rates like 384kHz or 768kHz. Higher rates result in noise shaping that moves the out-of-band noise further from the audible range, but not all audio sources can provide them.

- 6. The capacitors used for the audio filter should be COG, NP0 type ceramics. COG, NP0 type capacitors have a lower voltage coefficient of capacitance, meaning that the capacitive value of the component is less impacted by the voltage bias across the device. As the capacitors are key for performance of the filter, other types of ceramic capacitors should be avoided in the signal path.

- 7. The capacitors used for the input and output of the LDO should have low equivalent series resistance (ESR), such as X7R-, X5R-, and COG-type capacitors.

- 8. The resistors used for the LDO and voltage supervisor can be thick-film, though the accuracy of the resistor dividers will impact the LDO output voltage and the supervisor threshold. For this reason, it recommended that R<sub>1</sub>, R<sub>2</sub>, R<sub>3</sub>, and R<sub>4</sub> have a maximum tolerance of 1%.

- 9. Thin-film resistors are recommended for the resistive elements in the DAC output filter.

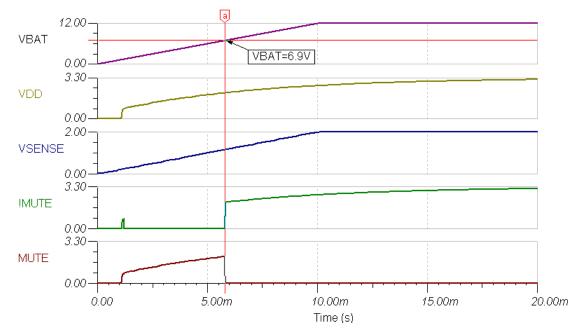

# Power-Up Mute Transient

The following simulation shows the power-up transient of the circuit. It can be seen that MUTE output is not released until the VBAT input reaches approximately 6.9V.

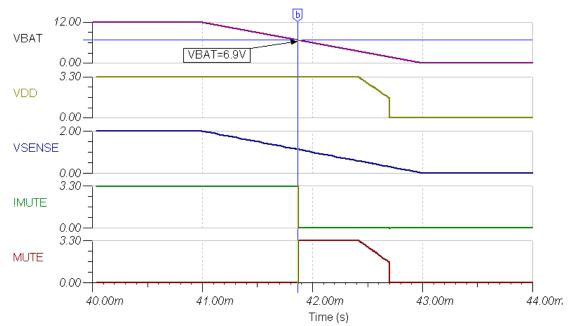

# Power-Down Mute Transient

The following simulation shows that the  $\overline{\text{MUTE}}$  output is asserted to low when the VBAT input drops below 6.9V.

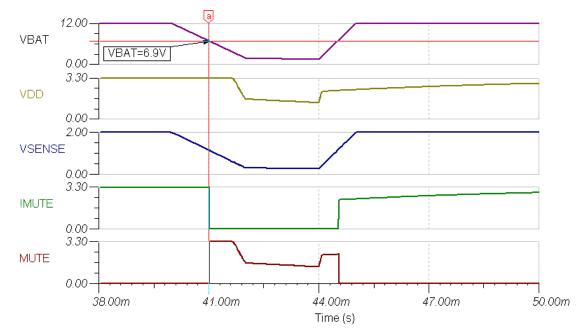

#### **Brown-Out Mute Transient**

The following simulation demonstrates that the DAC will be in a mute condition before the VDD supply of the DAC is compromised by the brown-out event. When the VBAT voltage drops below approximately 6.9V, the MUTE signal is asserted low. Once the VBAT recovers, the MUTE signal deasserted.

#### **Design Featured Devices**

| Device     | Key Features                                                                  | Link                                                                                                | Other Possible Devices                |

|------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------|

| PCM5102A   | 2VRMS DirectPath™, 112-dB audio stereo DAC with 32-bit, 384-kHz PCM interface | 2VRMS DirectPath™, 112dB Audio Stereo DAC with 32-bit, 384kHz PCM Interface                         | Audio DACs                            |

| TPS7A8300  | 2A, $6\mu V_{RMS}$ , low-noise, LDO voltage regulator                         | 2A, Iow-VIN, Iow-2A, Iow-VIN, Iow-noise, ultra-Iow-<br>dropout voltage regulator with power good wi | Linear & low-dropout (LDO) regulators |

| TPS389001  | Low quiescent current, 1% accurate voltage supervisor with programmable delay | Low-quiescent current 1% accuracy supervisor with programmable delay                                | Supervisor & reset ICs                |

| CSD13380F3 | 12-V N-channel FemtoFET™ MOSFET                                               | 12V, N channel NexFET™ power MOSFET, single<br>LGA 0.6mm x 0.7mm, 76mOhm, gate ESD protection       | MOSFETs                               |

### **Design References**

Texas Instruments, SBAM414 circuit companion simulation files, software

#### Other Links:

Texas Instruments, Precision DAC Learning Center, portfolio overview

Texas Instruments, Audio DACs, portfolio overview

## Trademarks

All trademarks are the property of their respective owners.

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated