Sample &

Buy

SLOS431B - MARCH 2004 - REVISED FEBRUARY 2015

# **TPA6120A2 High Fidelity Headphone Amplifier**

Technical

Documents

## 1 Features

- SNR of 128dB A-Weighted.

- THD of 112.5dB

- Current-Feedback Architecture

- Output Voltage Noise of 0.9μV<sub>rms</sub> at Gain = 1V/V (16Ω Load)

- Power Supply Range: ±5V to ±15V

- 1300V/µs Slew Rate

- Can be configured for Single Ended or Differential Inputs

- Independent Power Supplies for Low Crosstalk

## 2 Applications

- Professional Audio Equipment

- HiFi Smartphone

- Consumer Home Audio Equipment

- Headphone Drivers

## 3 Description

Tools &

Software

In applications requiring a high-power output, very high fidelity headphone amplifier, the TPA6120A2 replaces a costly discrete design and allows music, not the amplifier, to be heard. The TPA6120A2's current-feedback AB amplifier architecture delivers high bandwidth, extremely low noise, and up to 128dB of dynamic range.

Support &

Community

20

Three key features make current-feedback amplifiers outstanding for audio. The first feature is the high slew rate that prevents odd order distortion anomalies. The second feature is current-on-demand at the output that enables the amplifier to respond quickly and linearly when necessary without risk of output distortion. When large amounts of output power are suddenly needed, the amplifier can respond extremely quickly without raising the noise floor of the system and degrading the signal-to-noise ratio. The third feature is the gain-independent frequency response that allows the full bandwidth of the amplifier to be used over a wide range of gain settings.

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM) |

|-------------|-----------|-----------------|

| TPA6120A2   | HSOP (20) | 7.5mm x 12.82mm |

|             | VQFN (14) | 3.5mm x 3.5mm   |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

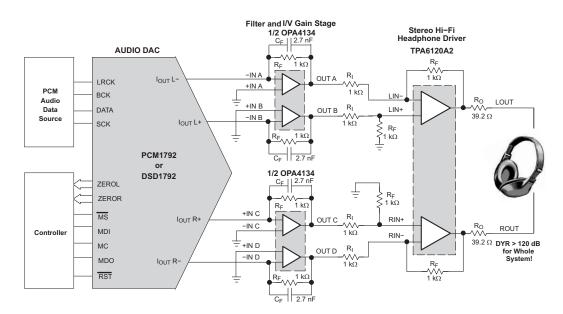

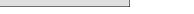

# 4 Simplified Schematic

# **Table of Contents**

| 1 | Feat | ures 1                             |

|---|------|------------------------------------|

| 2 | Арр  | lications1                         |

| 3 | Des  | cription1                          |

| 4 | Sim  | plified Schematic1                 |

| 5 |      | ision History 2                    |

| 6 |      | Configuration and Functions 3      |

| 7 | Spe  | cifications                        |

|   | 7.1  | Absolute Maximum Ratings 4         |

|   | 7.2  | ESD Ratings 4                      |

|   | 7.3  | Recommended Operating Conditions 4 |

|   | 7.4  | Thermal Information 4              |

|   | 7.5  | Electrical Characteristics5        |

|   | 7.6  | Operating Characteristics5         |

|   | 7.7  | Typical Characteristics 6          |

| 8 | Para | ameter Measurement Information     |

| 9 | Deta | ailed Description8                 |

|   | 9.1  | Overview                           |

|   | 9.2  | Functional Block Diagram 8         |

|    | 9.3   | Feature Description               | 8    |

|----|-------|-----------------------------------|------|

|    | 9.4   | Device Functional Modes           | 9    |

| 10 | App   | lications and Implementation      | 9    |

|    | 10.1  | Application Information           | 9    |

|    | 10.2  | Typical Application               | 9    |

| 11 | Pow   | er Supply Recommendations         | . 16 |

|    | 11.1  | Independent Power Supplies        | . 16 |

|    | 11.2  | Power Supply Decoupling           | . 16 |

| 12 | Layo  | out                               | 17   |

|    | 12.1  | Layout Guidelines                 | . 17 |

|    | 12.2  | Layout Example                    | . 18 |

| 13 | Devi  | ce and Documentation Support      | . 20 |

|    | 13.1  | Documentation Support             | . 20 |

|    | 13.2  | Trademarks                        | . 20 |

|    | 13.3  | Electrostatic Discharge Caution   | . 20 |

|    | 13.4  | Glossary                          | . 20 |

| 14 |       | hanical, Packaging, and Orderable |      |

|    | Infor | mation                            | 20   |

|    |       |                                   |      |

# 5 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| CI | nanges from Revision A (July 2014) to Revision B                                                | Page |

|----|-------------------------------------------------------------------------------------------------|------|

| •  | Changed the Device Information Packages From: DWP (20) and RGY (14) To: HSOP (20) and VQFN (14) | 1    |

| •  | Changed QFN to VQFN in the Pin Functions table                                                  | 3    |

| •  | Added a NOTE to the Applications and Implementation section                                     | 9    |

| •  | Added Title: Application Information                                                            | 9    |

| •  | Deleted Title: Application Circuit                                                              | 9    |

| •  | Changed the Design Requirements                                                                 | 10   |

| •  | Deleted Title: Application Circuit                                                              | 14   |

| •  | Moved two paragraphs following Figure 19 to proceed Figure 19                                   | 14   |

### Changes from Original (March 2004) to Revision A

| • | Changed Added ESD Rating table, Feature Description section, Device Functional Modes, Application and<br>Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation<br>Support section, and Mechanical, Packaging, and Orderable Information section | 1 |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| • | Added the VQFN package information                                                                                                                                                                                                                                                               | 1 |

| • | Updated Pin descriptions to clarify power supply.                                                                                                                                                                                                                                                | 3 |

| • | Lowered minimum V <sub>IC</sub> (±5Vcc) From: ±3.6 To: ±3.4                                                                                                                                                                                                                                      | 5 |

| • | Lowered minimum V <sub>IC</sub> (±15Vcc) From: ±13.4V To: ±13.2V                                                                                                                                                                                                                                 | 5 |

| • | Deleted IMD (Intermodulation Distortion), ±12Vcc data, Dynamic Range (replaced with SNR, in 1V/V gain)                                                                                                                                                                                           | 5 |

| • | Changed the THD=N UNIT From: % To: dB                                                                                                                                                                                                                                                            | 5 |

| • | Changed the SNR to show the latest data from newer QFN based EVM.                                                                                                                                                                                                                                | 5 |

www.ti.com

#### Page

#### Copyright © 2004–2015, Texas Instruments Incorporated

2

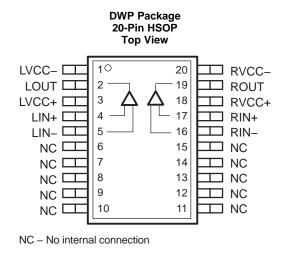

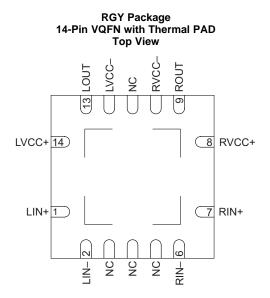

# 6 Pin Configuration and Functions

### **Pin Functions**

|             | PIN                           |             |     | DECODIDITIONS                                                                                                        |  |  |

|-------------|-------------------------------|-------------|-----|----------------------------------------------------------------------------------------------------------------------|--|--|

| NAME        | HSOP NO.                      | VQFN NO.    | I/O | DESCRIPTIONS                                                                                                         |  |  |

| LVCC-       | 1                             | 12          | I   | Left channel negative power supply – must be kept at the same potential as RVCC- if both amplifiers are to be used.  |  |  |

| LOUT        | 2                             | 13          | 0   | Left channel output                                                                                                  |  |  |

| LVCC+       | 3                             | 14          | I   | Left channel positive power supply – must be kept at the same potential as RVCC+ if both amplifiers are to be used.  |  |  |

| LIN+        | 4                             | 1           | I   | Left channel positive input                                                                                          |  |  |

| LIN-        | 5                             | 2           | I   | Left channel negative input                                                                                          |  |  |

| NC          | 6,7,8,9,10,11,<br>12,13,14,15 | 3, 4, 5, 11 | -   | Not internally connected                                                                                             |  |  |

| RIN-        | 16                            | 6           | I   | Right channel negative input                                                                                         |  |  |

| RIN+        | 17                            | 7           | I   | Right channel positive input                                                                                         |  |  |

| RVCC+       | 18                            | 8           | I   | Right channel positive power supply - must be kept at the same potential as LVCC+ if both amplifiers are to be used. |  |  |

| ROUT        | 19                            | 9           | 0   | Right channel output                                                                                                 |  |  |

| RVCC-       | 20                            | 10          | I   | Right channel negative power supply - must be kept at the same potential as LVCC- if both amplifiers are to be used. |  |  |

| Thermal Pad | -                             | -           | -   | Connect to ground. The thermal pad must be soldered down in all applications to properly secure device on the PCB.   |  |  |

# 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                                                                     | MIN        | MAX            | UNIT |

|---------------------------------------------------------------------|------------|----------------|------|

| Supply voltage, $xV_{CC+}$ to $xV_{CC-}$ Where x=L or R channel     | 9          | 33             | V    |

| Input voltage, VI <sup>(2)</sup>                                    |            | $\pm V_{CC}$   |      |

| Differential input voltage, VID                                     |            | 6              | V    |

| Minimum load impedance                                              |            | 8              | Ω    |

| Continuous total power dissipation                                  | See Therma | al Information |      |

| Operating free-air temperature range, T <sub>A</sub>                | -40        | 85             | °C   |

| Operating junction temperature range, T <sub>J</sub> <sup>(3)</sup> | -40        | 150            | °C   |

| Storage Temperature, T <sub>stg</sub>                               | -40        | 125            | °C   |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute—maximum—rated conditions for extended periods may affect device reliability.

(2) When the TPA6120A2 is powered down, the input source voltage must be kept below 600mV peak.

(3) The TPA6120A2 incorporates an exposed PowerPAD on the underside of the chip. This acts as a heatsink and must be connected to a thermally dissipating plane for proper power dissipation. Failure to do so may result in exceeding the maximum junction temperature that could permanently damage the device. See TI Technical Brief SLMA002 for more information about utilizing the PowerPAD thermally enhanced package.

## 7.2 ESD Ratings

|                                               |                                                                    |                                                                   |                                     | VALUE | UNIT |

|-----------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------|-------|------|

|                                               |                                                                    | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | For Pins: LVCC+, RVCC+, LVCC-, RVCC | ±500  |      |

| V <sub>(ESD)</sub> Electrostatic<br>Discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all other pins | For all pins except:<br>LVCC+, RVCC+, LVCC-,<br>RVCC              | ±2000                               | V     |      |

|                                               |                                                                    | Charged device model (CDM), per JEDEC specification J             | ESD22-C101                          | ±1500 |      |

(1) Level listed above is the passing level per ANSI, ESDA, and JEDEC JS-001. JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

|                                                |                                       | MIN | NOM MAX | UNIT |

|------------------------------------------------|---------------------------------------|-----|---------|------|

|                                                | Split Supply                          | ±5  | ±15     | V    |

| Supply voltage, $V_{CC+}$ and $V_{CC-}$        | Single Supply                         | 10  | 30      | V    |

| Load impedance                                 | $V_{CC} = \pm 5V \text{ or } \pm 15V$ | 16  |         | Ω    |

| Operating free–air temperature, T <sub>A</sub> |                                       | -40 | 85      | °C   |

## 7.4 Thermal Information

|                     |                                              | TPA6120A2 | TPA6120A2    |      |

|---------------------|----------------------------------------------|-----------|--------------|------|

|                     | THERMAL METRIC <sup>(1)</sup>                | DWP [HSOP | ] RGY [VQFN] | UNIT |

|                     |                                              | 20 PINS   | 14 PINS      |      |

| $R_{\thetaJA}$      | Junction-to-ambient thermal resistance       | 44.5      | 49.4         |      |

| R <sub>0JCtop</sub> | Junction-to-case (top) thermal resistance    | 55.2      | 62.0         |      |

| $R_{\theta JB}$     | Junction-to-board thermal resistance         | 36.1      | 25.4         | °C/W |

| $\Psi_{JT}$         | Junction-to-top characterization parameter   | 23.1      | 1.6          |      |

| Ψ <sub>JB</sub>     | Junction-to-board characterization parameter | 36.2      | 25.5         |      |

| R <sub>0JCbot</sub> | Junction-to-case (bottom) thermal resistance | 7.6       | 6.2          |      |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

## 7.5 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                 | PARAMETER                                         | TEST CONDITIONS                       | MIN           | TYP           | MAX | UNIT  |  |

|-----------------|---------------------------------------------------|---------------------------------------|---------------|---------------|-----|-------|--|

| V <sub>IO</sub> | Input offset voltage (measured<br>differentially) | $V_{CC} = \pm 5V \text{ or } \pm 15V$ |               | 2             | 5   | mV    |  |

| PSRR            | Power supply rejection ratio                      | $V_{CC} = \pm 5V \text{ to} \pm 15V$  |               | 75            |     | dB    |  |

| V               | Common mode input voltage                         | $V_{CC} = \pm 5V$                     | ±3.4          | ±3.7          |     | V     |  |

| V <sub>IC</sub> | Common mode input voltage                         | $V_{CC} = \pm 15V$                    | ±13.2         | ±13.5         |     | V     |  |

|                 | Supply surrent (assh shannel)                     | $V_{CC} = \pm 5V$                     |               | 11.5          | 13  | mA    |  |

| I <sub>CC</sub> | Supply current (each channel)                     | $V_{CC} = \pm 15V$                    |               |               | 15  |       |  |

| lo              | Output current (per channel)                      | $V_{CC}$ = ±5V to ±15V                |               | 700           |     | mA    |  |

|                 | Input offset voltage drift                        | $V_{CC} = \pm 5V \text{ or } \pm 15V$ |               | 20            |     | µV/°C |  |

| r <sub>i</sub>  | Input resistance                                  |                                       |               | 300           |     | kΩ    |  |

| r <sub>o</sub>  | Output resistance                                 | Open Loop                             |               | 13            |     | Ω     |  |

| Vo              | Output voltage swing                              | $V_{CC} = \pm 15V, R_L = 25\Omega$    | 11.8 to -11.5 | 12.5 to -12.2 |     | V     |  |

# 7.6 Operating Characteristics<sup>(1)</sup>

$T_A = 25^{\circ}C$ ,  $R_L = 25\Omega$ , Gain = 1V/V (unless otherwise noted)

| PARAMETER        |                                            | TEST                                                                       | CONDITIONS                                            | MIN | TYP   | MAX | UNIT  |

|------------------|--------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------|-----|-------|-----|-------|

|                  |                                            | $R_L = 32\Omega$                                                           | $V_{CC} = \pm 5V P_O = 10mW$                          |     | 101   |     |       |

|                  |                                            | f = 1 kHz                                                                  | $V_{CC} = \pm 15 V P_{O} = 100 mW$                    |     | 90    |     | -     |

|                  |                                            | $R_1 = 64\Omega$                                                           | $V_{CC} = \pm 5 V P_O = 10 mW$                        |     | 104   |     |       |

|                  |                                            | f = 1 kHz                                                                  | $V_{CC} = \pm 15V P_{O} = 100mW$                      |     | 94    |     |       |

| THD+N            | Total harmonic distortion plus noise       | V <sub>CC</sub> = ±5V,<br>Gain = 1V/V                                      | $V_{O} = 3V_{PP},$<br>$R_{L} = 10k\Omega$<br>f = 1kHz |     | 104   |     | dB    |

|                  |                                            | V <sub>CC</sub> = ±15V,<br>Gain = 1V/V                                     |                                                       |     | 108   |     |       |

|                  |                                            | $V_{CC} = \pm 15V,$<br>Gain = 1V/V                                         | $V_{O} = 2V_{PP},$<br>$R_{L} = 10k\Omega$<br>f = 1kHz |     | 112.5 |     |       |

|                  | Supply voltage rejection ratio             | $R_{L} = 32\Omega$<br>f = 1kHz<br>V <sub>(RIPPLE)</sub> = 1V <sub>PP</sub> | V <sub>CC</sub> = ±5V                                 |     | -75   |     | dB    |

|                  |                                            |                                                                            | $V_{CC}=\pm 15V$                                      |     | -78   |     |       |

| k <sub>SVR</sub> |                                            | $R_L = 64\Omega$                                                           | V <sub>CC</sub> = ±5V                                 |     | -75   |     |       |

|                  |                                            | f = 1kHz<br>V <sub>(RIPPLE)</sub> = 1V <sub>PP</sub>                       | $V_{CC}=\pm 15V$                                      |     | -75   |     |       |

| CMRR             | Common mode rejection ratio (differential) | $V_{CC} = \pm 5V \text{ or } \pm 15V$                                      |                                                       |     | 100   |     | dB    |

| SR               | Slew rate                                  | $V_{CC} = \pm 15V$ , Gain = 5V/V                                           | /, V <sub>O</sub> = 20 V <sub>PP</sub>                |     | 1300  |     | 1//   |

| 3K               | Siew fale                                  | $V_{CC} = \pm 5V$ , Gain = 2V/V,                                           | $V_{O} = 5 V_{PP}$                                    |     | 900   |     | V/µs  |

| V <sub>n</sub>   | Output noise voltage                       | $V_{CC} = \pm 5V$ to $\pm 15V$<br>R <sub>L</sub> = 16 $\Omega$             | Gain = 1V/V                                           |     | 0.9   |     | μVrms |

|                  | Signal-to-noise ratio                      | $R_1 = 32\Omega$ to $64\Omega$                                             | V <sub>CC</sub> = ±15V, Gain = 1V/V. A<br>Weighted    |     | 128   |     | -ID   |

| SNR              |                                            | f = 1kHz                                                                   | $V_{CC} = \pm 5V$ , Gain = 1V/V. A Weighted           |     | 116   |     | dB    |

|                  |                                            | $V_{I} = 1V_{RMS}$                                                         | $V_{CC} = \pm 15V$                                    |     | -112  |     |       |

|                  | Crosstalk                                  | $R_{F} = 1k\Omega$ $R_{L} = 32\Omega \text{ to } 64\Omega$ $f = 1kHz$      | $V_{CC} = \pm 5V$                                     |     | -105  |     | dB    |

(1) For THD+N,  $k_{SVR}$ , and crosstalk, the bandwidth of the measurement instruments was set to 80kHz.

TPA6120A2

SLOS431B-MARCH 2004-REVISED FEBRUARY 2015

www.ti.com

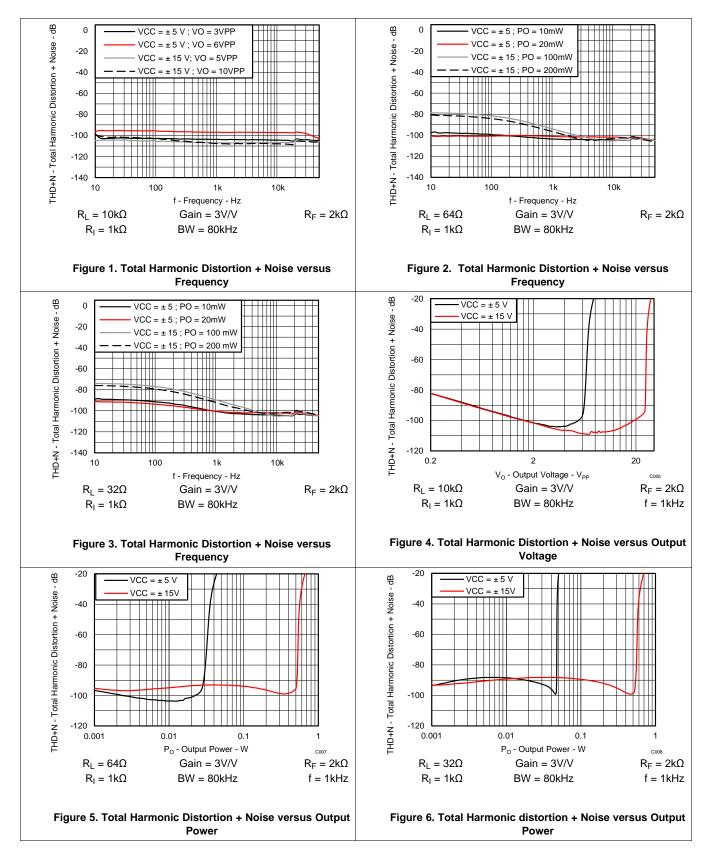

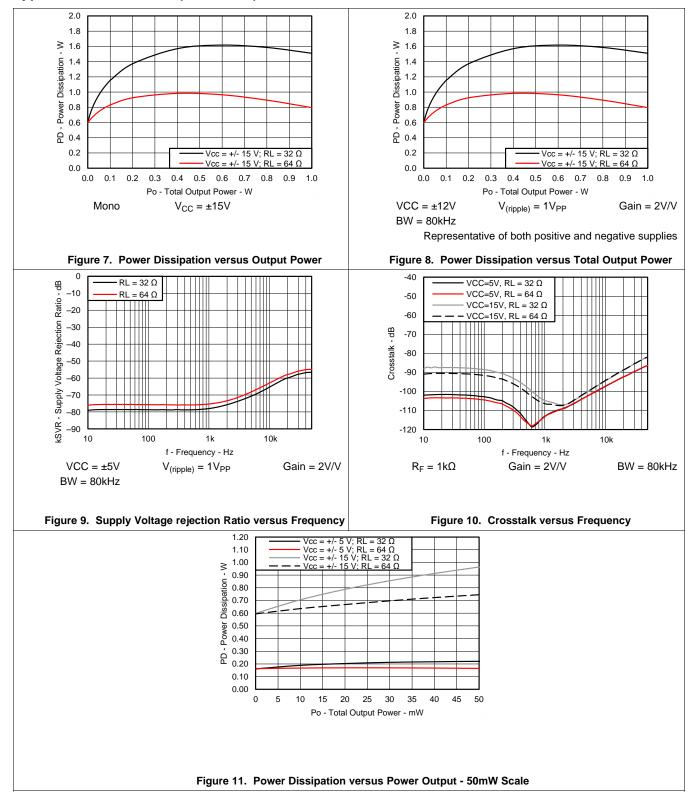

## 7.7 Typical Characteristics

6

## **Typical Characteristics (continued)**

TEXAS INSTRUMENTS

www.ti.com

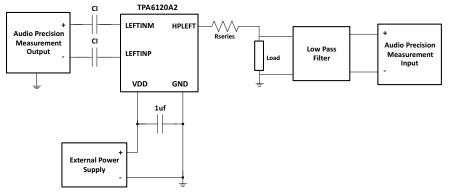

## 8 Parameter Measurement Information

- A. Separate power supply decoupling capacitors are used on all Vcc pins.

- B. The low-pass filter is used to remove harmonic content above the audible range.

Figure 12. Test Circuit

## 9 Detailed Description

## 9.1 Overview

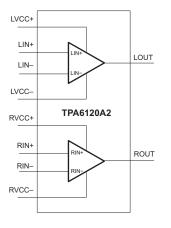

The TPA6120A2 is a current-feedback amplifier with differential inputs and single-ended outputs.

## 9.2 Functional Block Diagram

## 9.3 Feature Description

### 9.3.1 Current-Feedback Amplifier

Current feedback results in low voltage noise, low distortion, high open-loop gain throughout a large frequency range, and can be used in a similar fashion as voltage-feedback amplifiers. The low distortion of the TPA6120A2 results in a signal-to-noise ratio of 128 dB.

### 9.3.2 Independent Power Supplies

Because the power supplies for the two amplifiers are available separately, one amplifier can be turned off to conserve power.

See Power Supply Recommendations.

#### 9.4 Device Functional Modes

This device operates as a wide-bandwidth, current-feedback amplifier.

## **10** Applications and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### **10.1** Application Information

In many applications, the audio source is digital, and must go through a digital-to-analog converter (DAC) so that traditional analog amplifiers can drive the speakers or headphones.

### **10.2 Typical Application**

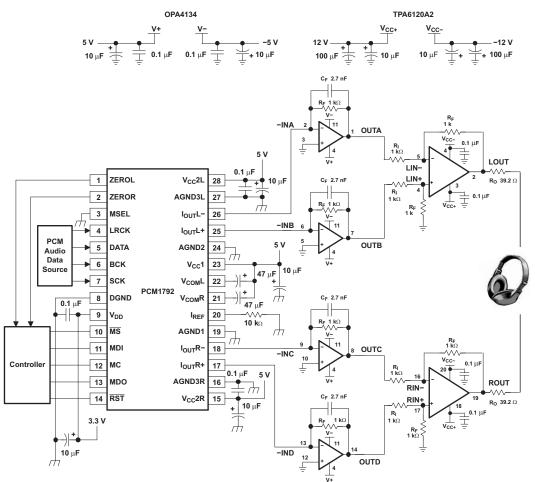

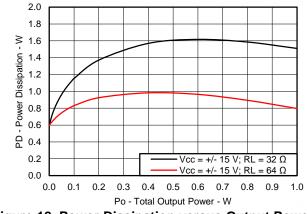

#### 10.2.1 High Voltage, High Fidelity DAC + Headphone Amplifier Solution

Figure 13 shows a complete circuit schematic for such a system. The digital audio is fed into a high performance DAC. The PCM1792, a Burr-Brown product from TI, is a 24-bit, stereo DAC.

Figure 13. Typical Application Circuit

**TPA6120A2**

SLOS431B-MARCH 2004-REVISED FEBRUARY 2015

# Typical Application (continued)

# 10.2.1.1 Design Requirements

- ±12V Operation from bipolar power supply

- Differential voltage source

- Be transparent to the user

# 10.2.1.2 Detailed Design Procedure

The output of the PCM1792 is current, not voltage, so the OPA4134 is used to convert the current input to a voltage output. The OPA4134 (SBOS058), is a low-noise, high-speed, high-performance operational amplifier.  $C_F$  and  $R_F$  are used to set the cutoff frequency of the filter. The RC combination in Figure 13 has a cutoff frequency of 59 kHz. All four amplifiers of the OPA4134 are used so the TPA6120A2 can be driven differentially.

The output of the OPA4134 goes into the TPA6120A2. The TPA6120A2 is configured for use with differential inputs, stereo use, and a gain of 2V/V. Note that the  $0.1\mu$ F capacitors are placed at every supply pin of the TPA6120A2, as well as the  $39.2\Omega$  series output resistor.

Each output goes to one channel of a pair of stereo headphones, where the listener enjoys crisp, clean, virtually noise free music with a dynamic range greater than the human ear is capable of detecting.

## 10.2.1.2.1 Resistor Values

Figure 14. Single-Ended Input With A Noninverting Gain Of 2V/V

In the most basic configuration (see Figure 14), four resistors must be considered, not including the load impedance. The feedback and input resistors,  $R_F$  and  $R_I$ , respectively, determine the closed-loop gain of the amplifier.  $R_O$  is a series output resistor designed to protect the amplifier from any capacitance on the output path, including board and load capacitance.  $R_S$  is a series input resistor.

The series output resistor should be between  $10\Omega$  and  $100\Omega$ . The output series resistance eases the work of the output power stage by increasing the load when low impedance headphones are connected, as well as isolating any capacitance on the following traces and headphone cable.

Because the TPA6120A2 is a current-feedback amplifier, take care when choosing the feedback resistor. TI recommends a lower level of  $800\Omega$  for the feedback resistance. No capacitors should be used in the feedback path, as they will form a short circuit at high frequencies.

The value of the feedback resistor should be chosen by using Figure 17 as a guideline. The gain can then be set by adjusting the input resistor. The smaller the feedback resistor, the less noise is introduced into the system. However, smaller values move the dominant pole to higher and higher frequencies, making the device more susceptible to oscillations. Higher feedback resistor values add more noise to the system, but pull the dominant pole down to lower frequencies, making the device more stable. Higher impedance loads tend to make the device more unstable. One way to combat this problem is to increase the value of the feedback resistor. It is not recommended that the feedback resistor exceed a value of  $10k\Omega$ . The typical value for the feedback resistor for the TPA6120A2 is  $1k\Omega$ . In some cases, where a high-impedance load is used along with a relatively large gain and a capacitive load, it may be necessary to increase the value of the feedback resistor from  $1k\Omega$  to  $2k\Omega$ , thus adding more stability to the system. Another method to deal with oscillations is to increase the size of  $R_0$ .

### CAUTION

Do not place a capacitor in the feedback path. Doing so can cause oscillations.

www.ti.com

### **Typical Application (continued)**

Capacitance at the outputs can cause oscillations. Capacitance from some sources, such as layout, can be minimized. Other sources, such as those from the load (for example, the inherent capacitance in a pair of headphones), cannot be easily minimized. In this case, adjustments to  $R_O$  and/or  $R_F$  may be necessary.

The series output resistor should be kept at a minimum of  $10\Omega$ ; small enough so that the effect on the load is minimal, but large enough to provide the protection necessary such that the output of the amplifier sees little capacitance. The value can be increased to provide further isolation, up to  $100\Omega$ . Care should be taken in selecting the thermal capacity of the output series resistor, as it will create a potential divider with the load and dissipate power.

The series resistor, R<sub>S</sub>, should be used for two reasons:

- 1. It prevents the positive input pin from being exposed to capacitance from the line and source.

- 2. It prevents the source from seeing the input capacitance of the TPA6120A2.

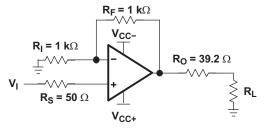

The 50 $\Omega$  resistor was chosen because it provides ample protection without interfering in any noticeable way with the signal. Not shown is another 50 $\Omega$  resistor that can be placed on the source side of R<sub>S</sub> to ground. In that capacity, it serves as an impedance match to any 50 $\Omega$  source. See Figure 15.

Figure 15. Single-Ended Input With A Noninverting Gain Of –1V/V

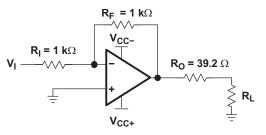

Figure 16 shows the TPA6120A2 connected with differential inputs. Differential inputs are useful because they take the greatest advantage of the high CMRR of the device. The two feedback resistor values must be kept the same, as do the input resistor values.

Figure 16. Differential Input With A Noninverting Gain Of 2V/V

Special note regarding mono operation:

- If both amplifiers are powered on, but only one channel is to be used, the unused amplifier MUST have a feedback resistor from the output to the negative input. Additionally, the positive input should be grounded as close to the pin as possible. Terminate the output as close to the output pin as possible with a 25Ω load to ground.

- These measures should be followed to prevent the unused amplifier from oscillating. If it oscillates, and the power pins of both amplifiers are tied together, the performance of the amplifier could be seriously degraded.

12

## **Typical Application (continued)**

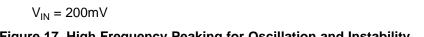

### 10.2.1.2.2 Checking For Oscillations And Instability

1 ൗ 0

> -1 -2 -3 -4

> -5

-6

$V_{CC} = \pm 5V$

10

Output Amplitude -

Checking the stability of the amplifier setup is recommended. High frequency oscillations in the megahertz region can cause undesirable effects in the audio band.

Sometimes, the oscillations can be quite clear. An unexpectedly large draw from the power supply may be an indication of oscillations. These oscillations can be seen with an oscilloscope. However, if the oscillations are not obvious, or there is a chance that the system is stable but close to the edge, placing a scope probe with 10pF of capacitance can make the oscillations worse, or actually cause them to start.

A network analyzer can be used to determine the inherent stability of a system. An output versus frequency curve generated by a network analyzer can be a good indicator of stability. At high frequencies, the curve shows whether a system is oscillating, close to oscillation, or stable. In Figure 17 the system is stable because the high frequency rolloff is smooth and has no peaking. Increasing R<sub>F</sub> decreases the frequency at which this rolloff occurs (see the Resistor Values section). Another scenario shows some peaking at high frequency. If the peaking is 2dB, the amplifier is stable as there is still 45 degrees of phase margin. As the peaking increases, the phase margin shrinks, causing the amplifier and the system to approach instability. The same system that normally has a 2dB peak has an increased peak when a capacitor is added to the output, indicating that the system is either on the verge of oscillation or is oscillating; corrective action is required.

1M

100k f - Frequency - Hz 10M 100M 500M

$R_L = 25\Omega$

Figure 17. High Frequency Peaking for Oscillation and Instability

10k

Gain = 1V/V

R<sub>F</sub> = 620 Ω R<sub>F</sub> = 1 kΩ

R<sub>F</sub> = 1.5 kΩ

1k

100

Product Folder Links: TPA6120A2

### **Typical Application (continued)**

#### 10.2.1.2.3 Thermal Considerations

There is no one to one relationship between output power and heat dissipation, so the following equations must be used:

Efficiency of an amplifier =

$$\frac{P_L}{P_{SUP}}$$

(1)

Where

$$P_{L} = \frac{V_{LRMS}^{2}}{R_{L}}$$

, and  $V_{LRMS} = \frac{V_{P}}{\sqrt{2}}$ , therefore,  $P_{L} = \frac{V_{P}^{2}}{2R_{L}}$  per channel (2)

$$P_{SUP} = V_{CC} I_{CCavg} + V_{CC} I_{CC(q)}$$

$$I_{CCavg} = \frac{1}{\pi} \int_{0}^{\frac{\pi}{2}} \frac{V_{P}}{R_{L}} \sin(t) dt = -\frac{V_{P}}{\pi R_{L}} [\cos(t)]_{0}^{\frac{\pi}{2}} = \frac{V_{P}}{\pi R_{L}}$$

(4)

Where

$$V_{\mathsf{P}} = \sqrt{2 \,\mathsf{P}_{\mathsf{L}} \,\mathsf{R}_{\mathsf{L}}} \tag{5}$$

Therefore,

$$\mathsf{P}_{\mathsf{SUP}} = \frac{\mathsf{V}_{\mathsf{CC}} \; \mathsf{V}_{\mathsf{P}}}{\pi \mathsf{R}_{\mathsf{L}}} \; + \; \mathsf{V}_{\mathsf{CC}} \; \mathsf{I}_{\mathsf{CC}}(\mathsf{q})$$

$$\begin{split} &\mathsf{P}_{\mathsf{L}} = \mathsf{Power \ delivered \ to \ load \ (per \ channel)} \\ &\mathsf{P}_{\mathsf{SUP}} = \mathsf{Power \ drawn \ from \ power \ supply} \\ &\mathsf{V}_{\mathsf{LRMS}} = \mathsf{RMS \ voltage \ on \ the \ load} \\ &\mathsf{R}_{\mathsf{L}} = \mathsf{Load \ resistance} \\ &\mathsf{V}_{\mathsf{P}} = \mathsf{Peak \ voltage \ on \ the \ load} \\ &\mathsf{I}_{\mathsf{CC}} \mathsf{avg} = \mathsf{Average \ current \ drawn \ from \ the \ power \ supply} \\ &\mathsf{I}_{\mathsf{CC}}(\mathsf{q}) = \mathsf{Quiescent \ current \ (per \ channel)} \\ &\mathsf{V}_{\mathsf{CC}} = \mathsf{Power \ supply \ voltage \ (total \ supply \ voltage = 30 \ V \ if \ running \ on \ a \ \pm 15 \text{-V \ power \ supply} \\ &\mathsf{\eta} = \mathsf{Efficiency \ of \ a \ SE \ amplifier} \end{split}$$

For stereo operation, the efficiency does not change because both  $P_L$  and  $P_{SUP}$  are doubled, affecting the amount of power dissipated by the package in the form of heat.

A simple formula for calculating the power dissipated, P<sub>DISS</sub>, is shown in Equation 7:

$P_{DISS} = (1 - \eta) P_{SUP}$

In stereo operation,  $\mathsf{P}_{\mathsf{SUP}}$  is twice the quantity that is present in mono operation.

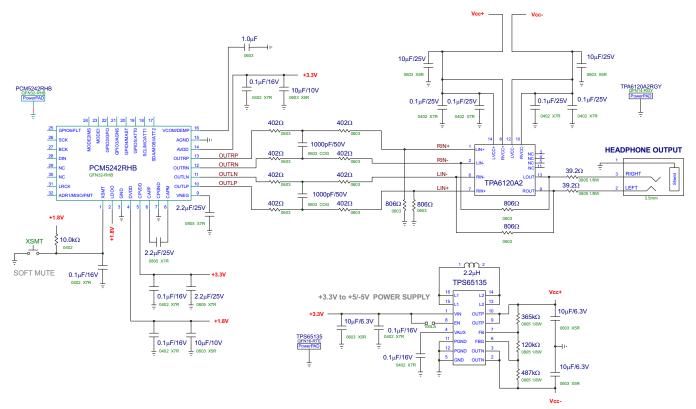

The maximum ambient temperature,  $T_A$ , depends on the heat-sinking ability of the system.  $R_{\theta JA}$  for a 20-pin DWP, whose thermal pad is properly soldered down, is shown in *Thermal Information*. Also see Figure 18.

$T_A Max = T_J Max - \theta_{JA} P_{DISS}$

(3)

(6)

(7)

(8)

TEXAS INSTRUMENTS

www.ti.com

#### 10.2.1.3 Application Performance Plots

Figure 18. Power Dissipation versus Output Power

### 10.2.2 High Fidelity Smartphone Application

A new trend in portable applications are termed "Hifi Smartphones". In these systems, a standard portable audio codec continues to be used for telephony, while a separate, higher performance DAC and Headphone Amplifier is used for music playback.

Figure 19 shows a complete circuit schematic for such a system. The digital audio is fed into a high performance DAC. The PCM5242, a Burr-Brown product from TI, is a 32-bit, stereo DAC.

Figure 19. Typical Application Circuit

## TPA6120A2 SLOS431B – MARCH 2004 – REVISED FEBRUARY 2015

### 10.2.2.1 Design Requirements

- ±5V Operation from an over system power supply of 3.3V

- Stereo differential inputs (DAC is differential)

- Be transparent to the user. (DAC SNR and THD+N performance all the way to the headphone)

### 10.2.2.2 Detailed Design Procedure

For optimal performance, the TPA6120A2 is configured for use with differential inputs, stereo use, and a gain of 1V/V.

The TPA6120A2 requires a bipolar power supply to drive a ground centered output. The application employs a TPS65135 DC-DC converter that generates ±5V from a single 3.3V supply.

The PCM5242 DAC is configured for a 1VRMS output so that clipping is avoided should the 3.3V power supply sag. The PCM5242 offers a ground centered output, so that no DC blocking capacitors are required between it and the TPA6120A2.

Resistor values around the TPA6120A2 of  $806\Omega$  and a  $39.2\Omega$  were found to offer the optimal conditions of SNR and THD. Starting with  $1K\Omega$  resistors for input and feedback, and  $10\Omega$  output resistance, the feedback resistance was lowered to increase the amount of current in the feedback network. The output resistance was increased to ease the load on the headphone amplifier when low impedance headphones are connected. Both of these additions contribute to the excellent SNR and THD of the TPA6120A2 in such a low voltage application.

Note that the 0.1-uF X7R capacitors are placed at every supply pin of the TPA6120A2.

Using such a solution makes the TPA6120A2 transparent in the circuit, even into a low impedance 320hm load.

The remaining steps are the same as those described in Resistor Values.

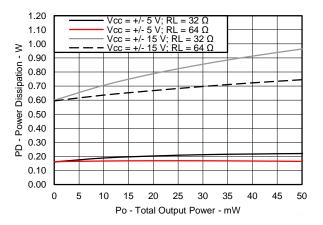

### 10.2.2.3 Application Performance Plots

Figure 20. Power Dissipation versus Power Output - 50mW Scale

In this particular application, the TPA6120A2's performance is transparent and the performance of the system is dictated by the PCM5242 DAC.

## **11** Power Supply Recommendations

### **11.1 Independent Power Supplies**

The TPA6120A2 consists of two independent high-fidelity amplifiers. Each amplifier has its own voltage supply, allowing the user to leave one of the amplifiers off, saving power, reducing the generated heat, and reducing crosstalk.

Although the power supplies are independent, there are some limitations. When both amplifiers are used, the same voltage must be applied to each amplifier. For example, if the left channel amplifier is connected to a  $\pm 12$ -V supply, the right channel amplifier must also be connected to a  $\pm 12$ -V supply. If the device is connected to a different supply voltage, it may not operate properly and consistently.

When the use of only one amplifier is preferred, it must be the left amplifier. The voltage supply to the left amplifier is also responsible for internal start-up and bias circuitry of the device. Regardless of whether one or both amplifiers are used, the  $V_{CC-}$  pins of both amplifiers must always be at the same potential.

To power down the right channel amplifier, disconnect the  $V_{CC+}$  pin from the power source.

The two independent power supplies can be tied together on the board to receive their power from the same source.

### 11.2 Power Supply Decoupling

As with any design, proper power supply decoupling is essential. Decoupling prevents noise from entering the device via the power traces and provides the extra power the device can sometimes require in a rapid fashion, preventing the device from being momentarily current-starved. Both of these functions serve to reduce distortion, leaving a clean, uninterrupted signal at the output.

Bulk decoupling capacitors should be used where the main power is brought to the board. Smaller capacitors should be placed as close as possible to the actual power pins of the device. Because the TPA6120A2 has four power pins, use four surface mount capacitors. Both types of capacitors should be low ESR.

## 12 Layout

## 12.1 Layout Guidelines

Proper board layout is crucial to getting the maximum performance out of the TPA6120A2.

A ground plane should be used on the board to provide a low inductive ground connection. Having a ground plane underneath traces adds capacitance, so care must be taken when laying out the ground plane on the underside of the board (assuming a 2-layer board). The ground plane is necessary on the bottom for thermal reasons.

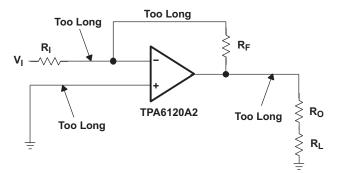

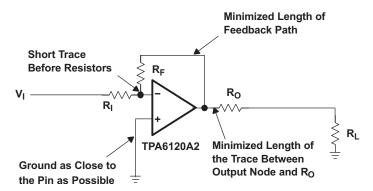

Stray capacitance can still make its way onto the sensitive outputs and inputs. Place components as close as possible to the pins and reduce trace lengths. See Figure 21 and Figure 22. Place the feedback resistor and the series output resistor extremely close to the pins. The input resistor should also be placed close to the pin. If the amplifier is to be driven in a noninverting configuration, ground the input close to the device so the current has a short, straight path to the PowerPAD (gnd).

Figure 21. Layout That Can Cause Oscillation

Figure 22. Layout Designed To Reduce Capacitance On Critical Nodes

**TPA6120A2** SLOS431B – MARCH 2004 – REVISED FEBRUARY 2015

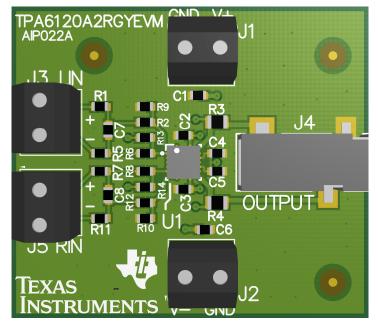

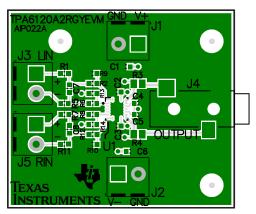

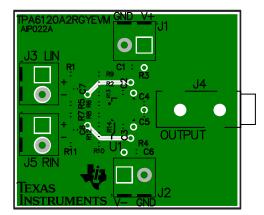

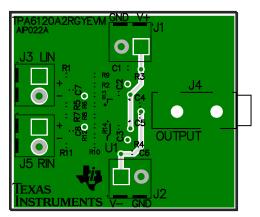

## 12.2 Layout Example

This is part of a 4-layer board, where ground, V+, V- are on the bottom and two middle traces, respectively. Key items to note in this layout:

- 1. R4 and R3 are the output resistors in the schematic. They are sized as 0603 surface mount resistors instead of 0402 for their thermal capacity, as they will be dissipating heat, depending on the output power.

- 2. Traces are kept as short as possible to avoid any capacitance or oscillation issues.

- 3. In systems that may be using the DWP package with through hole resistors, it's strongly suggested that the input and output pins and components do not have a ground plane directly beneath them, to avoid stray capacitance.

Figure 23. PCB Layout Example

Figure 24. Example PCB Layout, Top Layer and Silkscreen, Top View

Figure 25. Example PCB Layout, Middle-1 Layer and Silkscreen, Top View

# Layout Example (continued)

Figure 26. Example PCB Layout, Middle-2 Layer and Silkscreen, Top View

Figure 27. Example PCB Layout, Bottom Layer and Silkscreen, Top View

TEXAS INSTRUMENTS

www.ti.com

## **13** Device and Documentation Support

### **13.1 Documentation Support**

#### 13.1.1 Related Documentation

#### Headphone Amplifier Parametric Table

SoundPlus<sup>™</sup> High Performance Audio Operational Amplifiers, SBOS058

### 13.2 Trademarks

All trademarks are the property of their respective owners.

### 13.3 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## 13.4 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

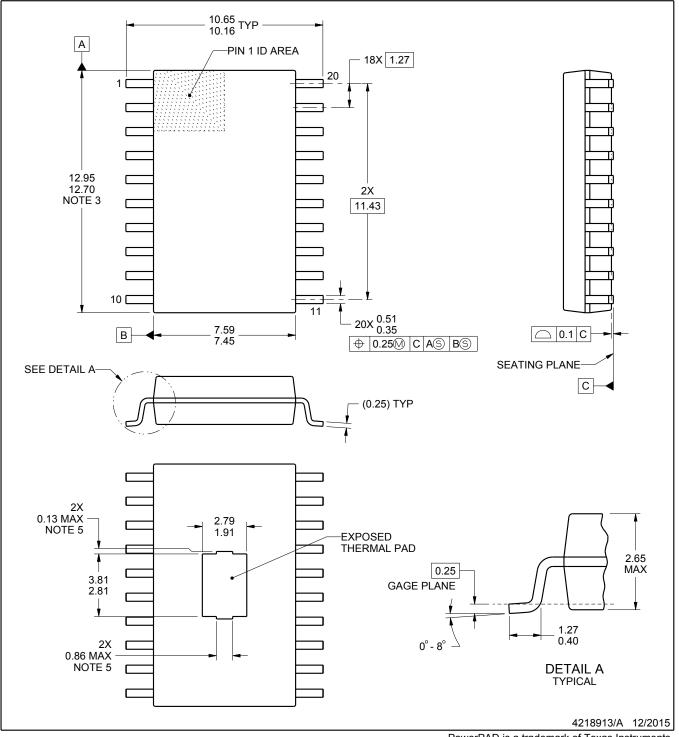

## 14 Mechanical, Packaging, and Orderable Information

The following pages include mechanical packaging and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

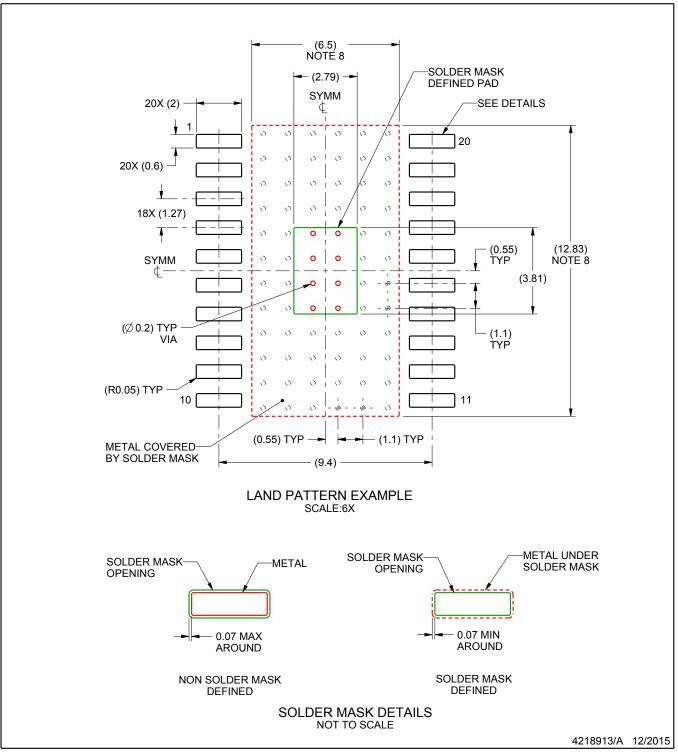

# **PACKAGE OUTLINE**

# PowerPAD<sup>™</sup> SOIC - 2.65 mm max height

PLASTIC SMALL OUTLINE

NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

exceed 0.15 mm per side. 4. Features may not present.

# **DWP0020B**

# **EXAMPLE BOARD LAYOUT**

# PowerPAD<sup>™</sup> SOIC - 2.65 mm max height

PLASTIC SMALL OUTLINE

NOTES: (continued)

- 5. Publication IPC-7351 may have alternate designs.

- 6. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- 7. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 (www.ti.com/lit/slma002) and SLMA004 (www.ti.com/lit/slma004).

- 8. Size of metal pad may vary due to creepage requirement.

# **DWP0020B**

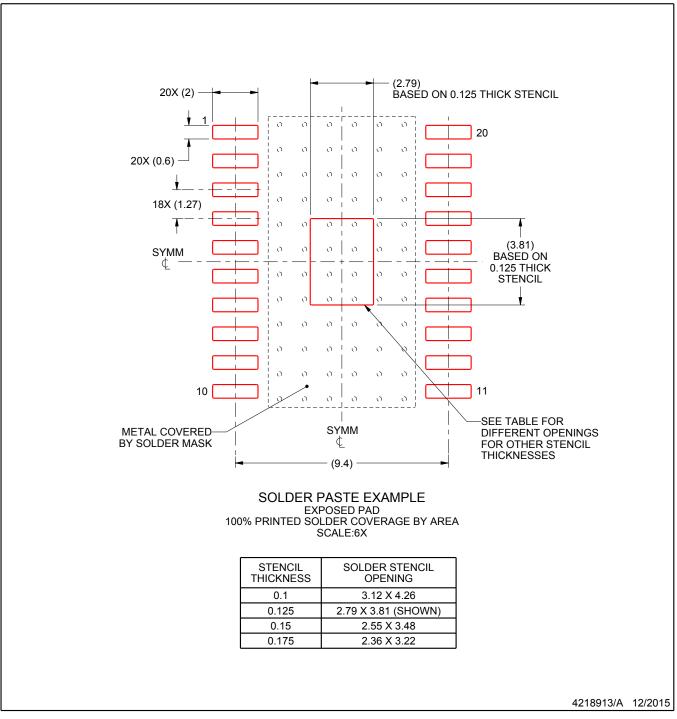

# **EXAMPLE STENCIL DESIGN**

# PowerPAD<sup>™</sup> SOIC - 2.65 mm max height

PLASTIC SMALL OUTLINE

NOTES: (continued)

9. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

10. Board assembly site may have different recommendations for stencil design.

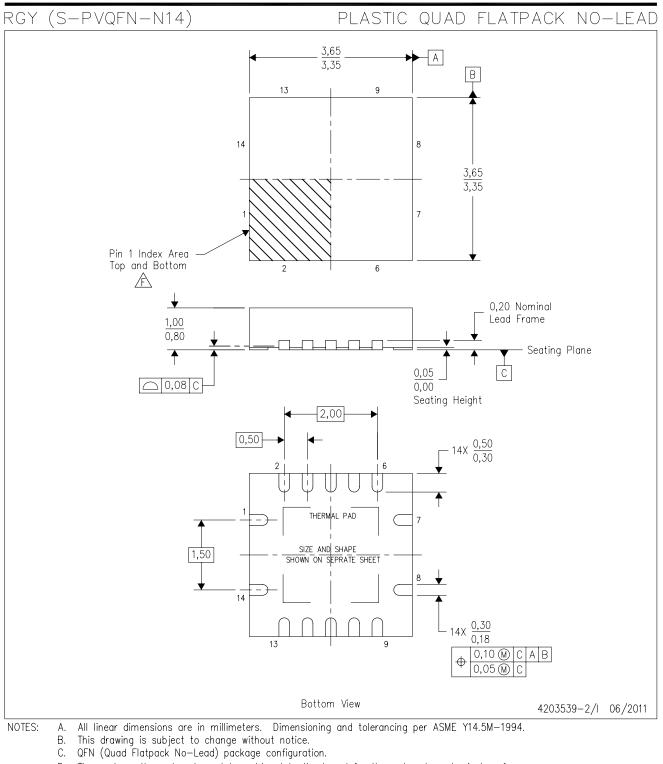

# **MECHANICAL DATA**

- D. The package thermal pad must be soldered to the board for thermal and mechanical performance.

- E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- earrow Pin 1 identifiers are located on both top and bottom of the package and within the zone indicated.

- The Pin 1 identifiers are either a molded, marked, or metal feature.

- G. Package complies to JEDEC MO-241 variation BA.

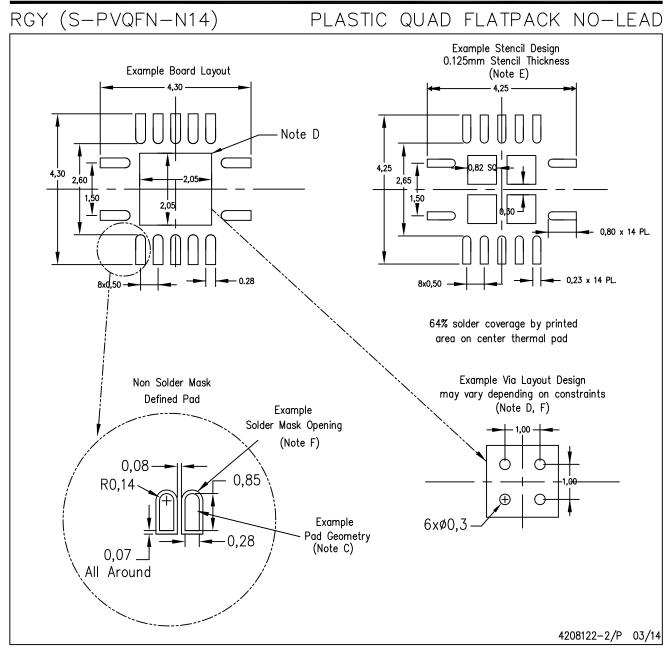

# RGY (S-PVQFN-N14)

# PLASTIC QUAD FLATPACK NO-LEAD

### THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No-Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at www.ti.com.

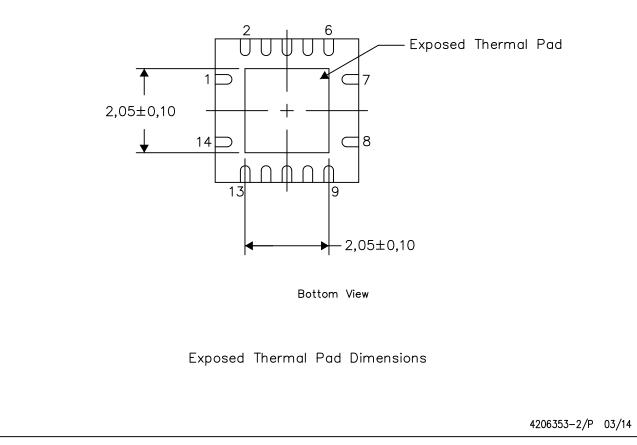

The exposed thermal pad dimensions for this package are shown in the following illustration.

#### NOTE: All linear dimensions are in millimeters

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

D. This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, Quad Flat-Pack QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>.

E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

F. Customers should contact their board fabrication site for minimum solder mask web tolerances between signal pads.

## PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|-------------------------------|---------------------|--------------|-------------------------|---------|

|                  | (1)           |              | j                  |      | ,              | (2)             | (6)                           | (3)                 |              | (4/3)                   |         |

| TPA6120A2DWP     | ACTIVE        | SO PowerPAD  | DWP                | 20   | 25             | RoHS & Green    | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | 6120A2                  | Samples |

| TPA6120A2DWPG4   | ACTIVE        | SO PowerPAD  | DWP                | 20   | 25             | TBD             | Call TI                       | Call TI             | -40 to 85    |                         | Samples |

| TPA6120A2DWPR    | ACTIVE        | SO PowerPAD  | DWP                | 20   | 2000           | RoHS & Green    | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | 6120A2                  | Samples |

| TPA6120A2RGYR    | ACTIVE        | VQFN         | RGY                | 14   | 3000           | RoHS & Green    | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 85    | 6120A2                  | Samples |

| TPA6120A2RGYT    | ACTIVE        | VQFN         | RGY                | 14   | 250            | RoHS & Green    | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | 6120A2                  | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

# PACKAGE OPTION ADDENDUM

11-Jul-2024

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

Texas

STRUMENTS

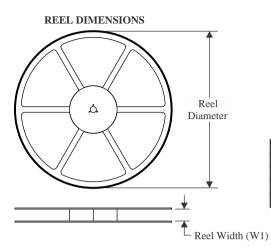

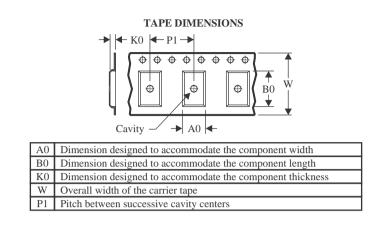

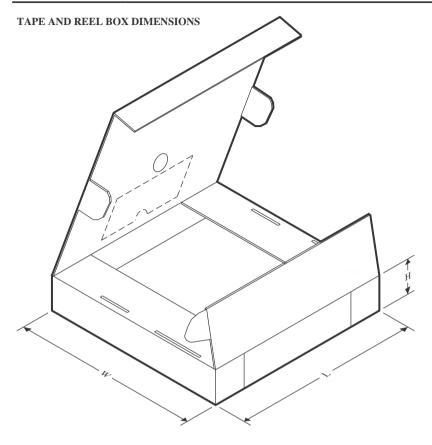

## TAPE AND REEL INFORMATION

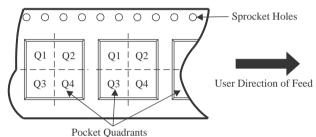

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |          |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|----------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | -        | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| TPA6120A2DWPR               | SO       | DWP                | 20 | 2000 | 330.0                    | 24.4                     | 10.8       | 13.3       | 2.7        | 12.0       | 24.0      | Q1               |

|                             | PowerPAD |                    |    |      |                          |                          |            |            |            |            |           |                  |

| TPA6120A2RGYR               | VQFN     | RGY                | 14 | 3000 | 330.0                    | 12.4                     | 3.75       | 3.75       | 1.15       | 8.0        | 12.0      | Q2               |

| TPA6120A2RGYT               | VQFN     | RGY                | 14 | 250  | 180.0                    | 12.4                     | 3.75       | 3.75       | 1.15       | 8.0        | 12.0      | Q2               |

# PACKAGE MATERIALS INFORMATION

5-Dec-2023

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPA6120A2DWPR | SO PowerPAD  | DWP             | 20   | 2000 | 350.0       | 350.0      | 43.0        |

| TPA6120A2RGYR | VQFN         | RGY             | 14   | 3000 | 346.0       | 346.0      | 33.0        |

| TPA6120A2RGYT | VQFN         | RGY             | 14   | 250  | 210.0       | 185.0      | 35.0        |

# TEXAS INSTRUMENTS

www.ti.com

5-Dec-2023

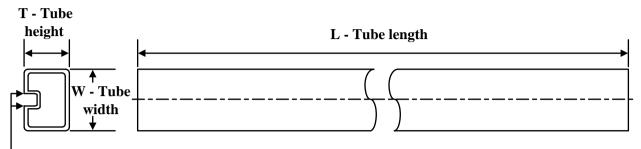

# TUBE

# - B - Alignment groove width

\*All dimensions are nominal

| Device       | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | Τ (μm) | B (mm) |

|--------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| TPA6120A2DWP | DWP          | HSOIC        | 20   | 25  | 506.98 | 12.7   | 4826   | 6.6    |

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated