Support & training

## TAS2320 15W Mono Digital Input Class-D Speaker Amp with 15V Support

## **1** Features

Texas

- Powerful Class-D amplifier

- 15W 1% THD+N

INSTRUMENTS

- 15V external PVDD supply

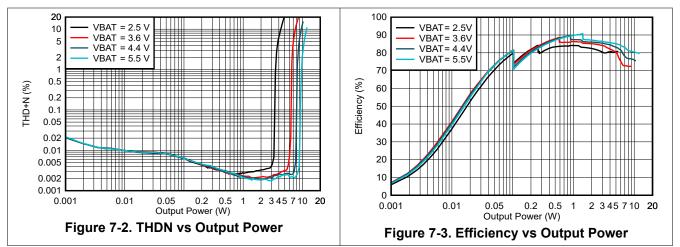

- · Best in class efficiency

- Upto 89% efficiency at system level for 8Ω load

- 14.2mW idle channel power, noise gate off

- 5mW idle channel power, noise gate on

- Integrated 1.8V Y-bridge

- High performance audio channel

- 17.2µV A-wt. idle channel noise

- 109dB Dynamic Range

- -89dB THD+N

- Low EMI performance with ERC and SSM

- < 1µs chip to chip group delay matching</li>

- Advanced integrated features

- Signal detection high efficiency modes

- High accuracy voltage monitor & temp sensor

- Ease of use features

- Hardware pin control or I<sup>2</sup>C control

- External PVDD supply

- Clock based power up/down

- Auto clock rate detection: 16 to 192kHz

- MCLK free operation

- Thermal and over current protection

- Power Supplies and user interface

- VBAT: 2.5V to 5.5V

- VDD: 1.65V to 1.95V

- IOVDD: 1.8V or 3.3V

- PVDD: 2.5V to 15V

- I<sup>2</sup>S/TDM: 8 channels

- HW pin control or I<sup>2</sup>C based control

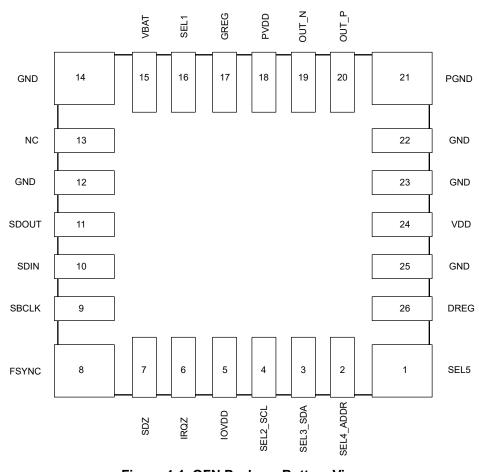

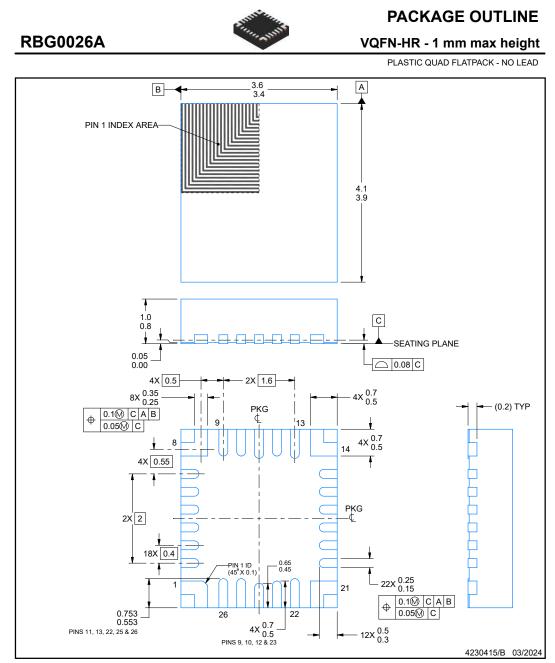

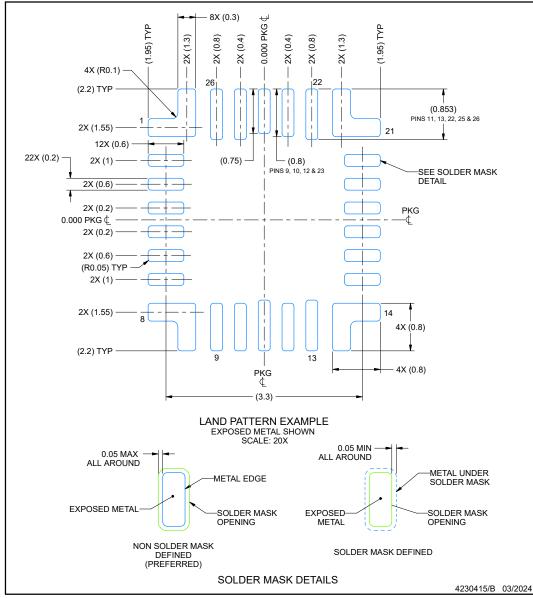

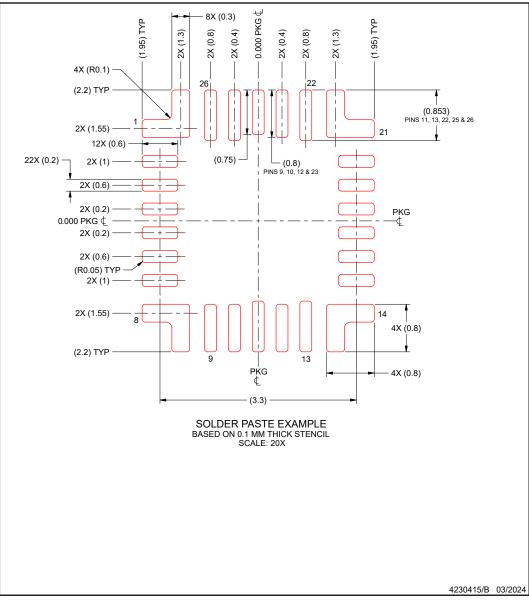

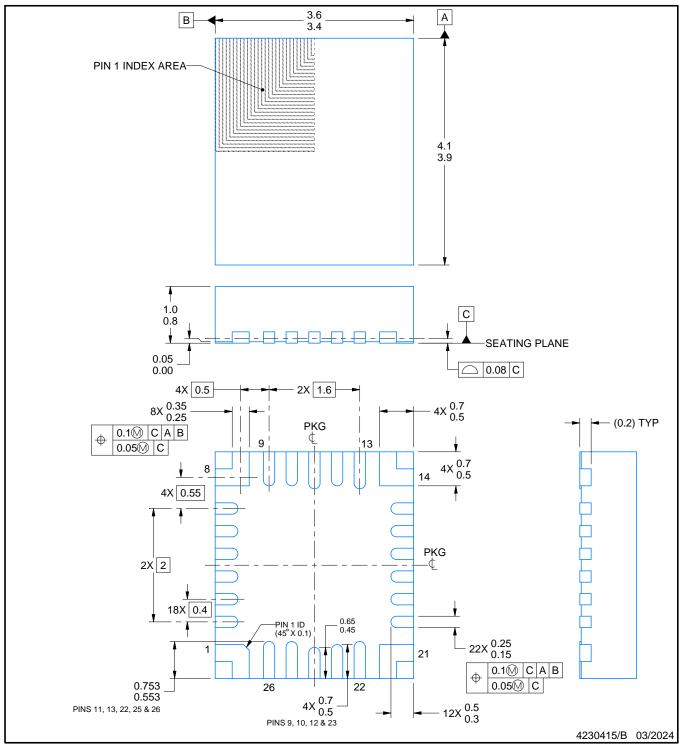

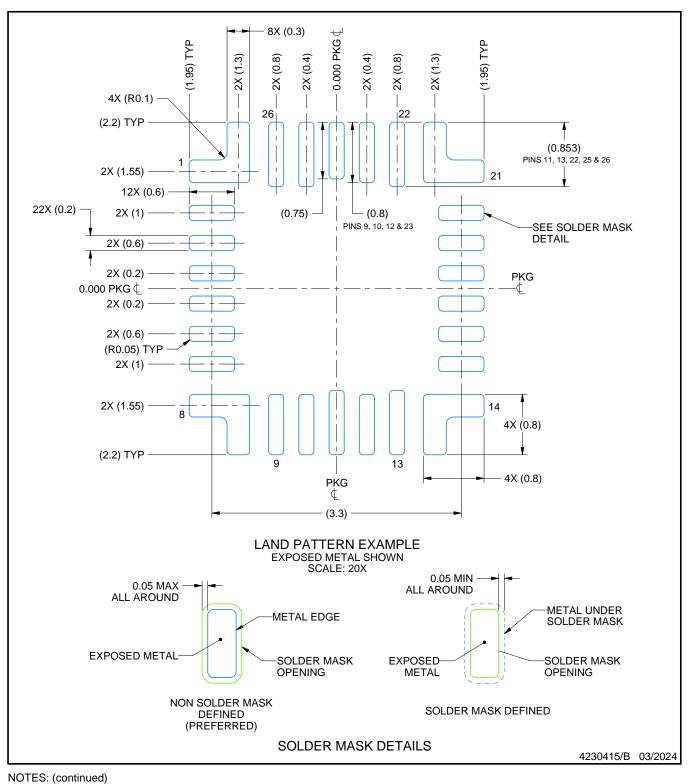

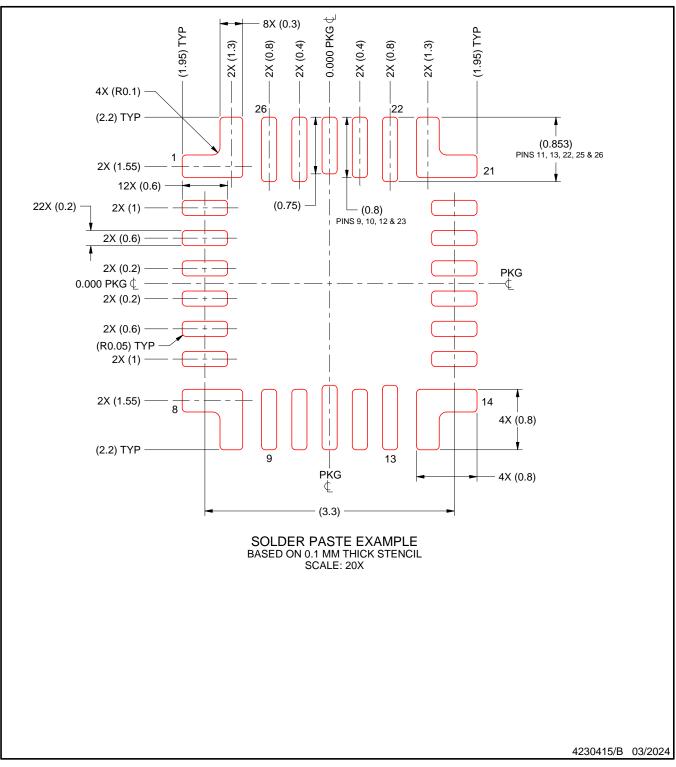

- 26-Pin, 0.4mm Pitch, QFN package

## 2 Applications

- Smart Speakers with Voice Assistance

- Bluetooth and Wireless speakers

- Tablets, Wearables

- Laptop, Desktop Computers

## **3 Description**

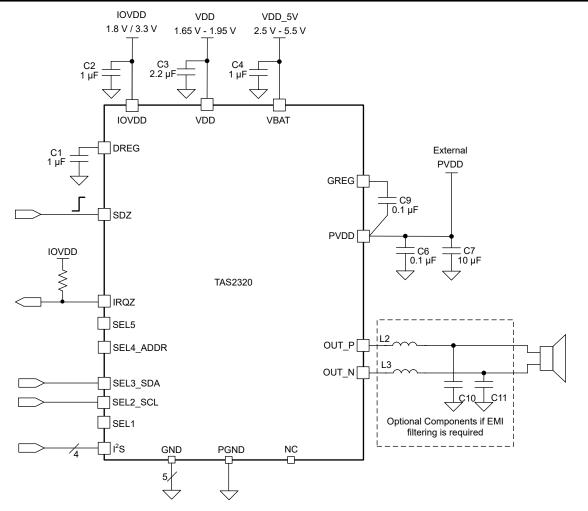

The TAS2320 is a mono, digital input Class-D audio amplifier designed for efficiently driving high peak power into loudspeakers.

Device is optimized to deliver best battery life for real-use cases of music playback and voice calls. Advanced efficiency optimization features like Y-bridge, and algorithms enable the device to produce best-in-class efficiency across all power regions of operation. The Class-D amplifier is capable of delivering 15W output power using external PVDD supply.

Up to four devices can share a common bus via  $I^2S/TDM + I^2C$  interfaces. The device also supports five HW Control pins that can configure the device for the desired mode of operation.

#### **Device Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |  |  |

|-------------|------------------------|-----------------------------|--|--|

| TAS2320     | QFN                    | 4mm × 3.5mm                 |  |  |

- (1) For all available packages, see the orderable addendum at the end of the data sheet.

- (2) The package size (length × width) is a nominal value and includes pins, where applicable.

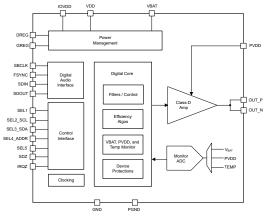

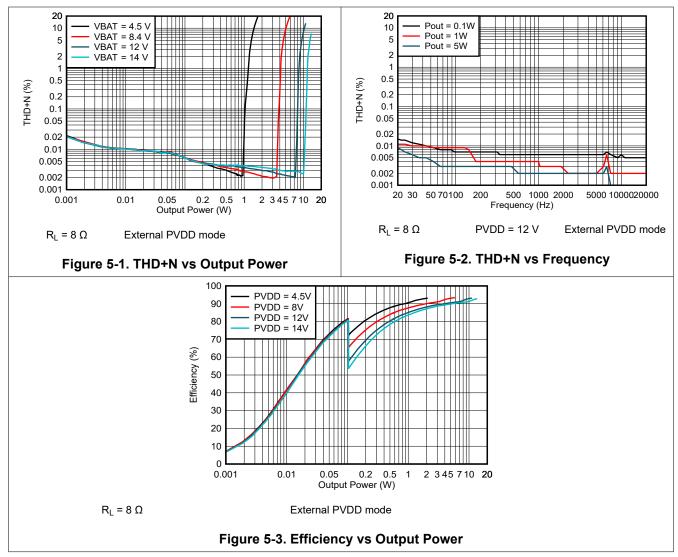

#### Functional block diagram

## **Table of Contents**

| 1 Features1                           |

|---------------------------------------|

| 2 Applications1                       |

| 3 Description1                        |

| 4 Pin Configuration and Functions2    |

| 5 Specifications                      |

| 5.1 Absolute Maximum Ratings4         |

| 5.2 ESD Ratings                       |

| 5.3 Recommended Operating Conditions4 |

| 5.4 Thermal Information4              |

| 5.5 Electrical Characteristics5       |

| 5.6 Timing Requirements8              |

| 5.7 Typical Characteristics9          |

| 6 Detailed Description                |

| 6.1 Overview                          |

| 6.2 Functional Block Diagram11        |

| 6.3 Device Functional Modes11         |

| 6.4 Feature Description17             |

| 6.5 Programming                       |

| 7 Application and Implementation      |

| 7.1 Application Information                          | 32                |

|------------------------------------------------------|-------------------|

| 7.2 Typical Application                              |                   |

| 8 Power Supply Recommendations                       |                   |

| 9 Layout                                             |                   |

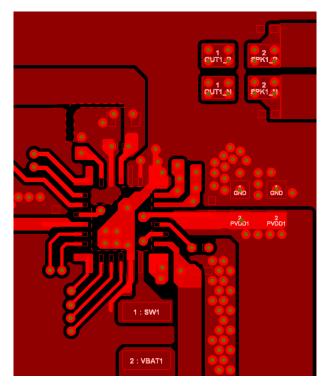

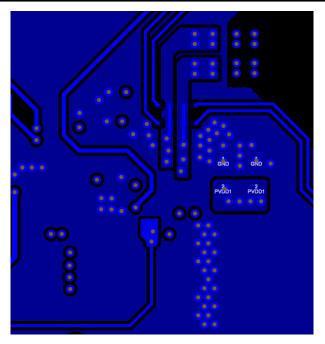

| 9.1 Layout Guidelines                                |                   |

| 9.2 Layout Example                                   |                   |

| 10 Device and Documentation Support                  | 39                |

| 10.1 Documentation Support                           | 39                |

| 10.2 Receiving Notification of Documentation Updates | s <mark>39</mark> |

| 10.3 Support Resources                               | 39                |

| 10.4 Trademarks                                      | 39                |

| 10.5 Electrostatic Discharge Caution                 | 39                |

| 10.6 Glossary                                        | 40                |

| 11 Revision History                                  | 40                |

| 12 Mechanical, Packaging, and Orderable              |                   |

| Information                                          | 40                |

| 12.1 Package Option Addendum                         | 41                |

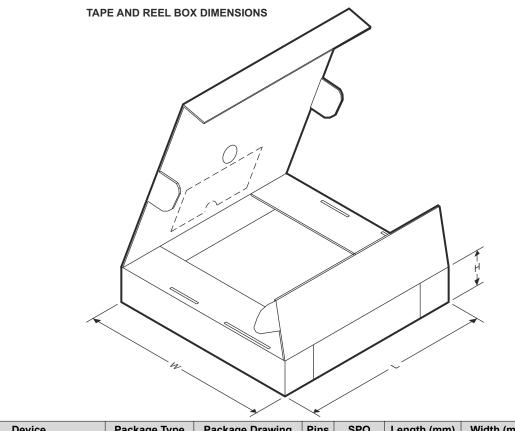

| 12.2 Tape and Reel Information                       | 42                |

| •                                                    |                   |

## **4** Pin Configuration and Functions

#### **Pin Functions**

| PIN                                                                                                                                                        |                       | Type <sup>(1)</sup> DESCRIPTION | DESCRIPTION                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                                                                                                                       | NO.                   | Type                            | DESCRIPTION                                                                                                                                                                    |

| DREG                                                                                                                                                       | 26                    | Р                               | Digital core voltage regulator output. Bypass to GND with a capacitor. Do not connect to an external load.                                                                     |

| FSYNC                                                                                                                                                      | 8                     | I                               | I <sup>2</sup> S word clock or TDM frame sync.                                                                                                                                 |

| GREG                                                                                                                                                       | 17                    | Р                               | High-side gate CP regulator output. Do not connect to an external load.                                                                                                        |

| GND                                                                                                                                                        | 12, 14, 22, 23,<br>25 | Р                               | Connect to PCB GND plane. Strong connection to ground plane required through multiple vias.                                                                                    |

| IOVDD                                                                                                                                                      | 5                     | Р                               | 1.8V or 3.3V Digital IO supply. Decouple to GND with capacitor.                                                                                                                |

| IRQZ                                                                                                                                                       | 6                     | 0                               | Open drain, active low interrupt pin. Pull up to IOVDD with resistor if optional internal pullup is not used.                                                                  |

| NC                                                                                                                                                         | 13                    | -                               | No connect. Keep floating.                                                                                                                                                     |

| OUT_N 19 O Class-D negative output.                                                                                                                        |                       | Class-D negative output.        |                                                                                                                                                                                |

| OUT_P                                                                                                                                                      | 20                    | 0                               | Class-D positive output.                                                                                                                                                       |

| PGND                                                                                                                                                       | 21                    | Р                               | Class-D Power stage ground. Connect to PCB GND plane strongly through multiple vias.                                                                                           |

| PVDD         18         P         Class-D power stage supply.                                                                                              |                       | Class-D power stage supply.     |                                                                                                                                                                                |

| SBCLK                                                                                                                                                      | 9                     | I                               | I <sup>2</sup> S/TDM serial bit clock.                                                                                                                                         |

| SDIN                                                                                                                                                       | 10                    | I                               | I <sup>2</sup> S or TDM serial data input.                                                                                                                                     |

| SDOUT                                                                                                                                                      | 11                    | I/O                             | I <sup>2</sup> S or TDM serial data output.                                                                                                                                    |

| SDZ                                                                                                                                                        | 7                     | I                               | Active low hardware shutdown.                                                                                                                                                  |

| SEL1                                                                                                                                                       | 16                    | I                               | HW Mode: Select 1 Pin. Amplifier gain level selection with volume ramp enable and disable options.<br>I <sup>2</sup> C Mode: Short to GND for I <sup>2</sup> C mode selection. |

| SEL2_SCL                                                                                                                                                   | 4                     | I                               | HW Mode: Select 2 Pin. I <sup>2</sup> S, TDM, Left justified selection.<br>I <sup>2</sup> C Mode: Clock Pin. Pull up to IOVDD with a resistor.                                 |

| SEL3_SDA                                                                                                                                                   | 3                     | I/O                             | HW Mode: Select 3 Pin. Data valid rising edge and falling edge selection.<br>I <sup>2</sup> C Mode: Data Pin. Pull up to IOVDD with a resistor.                                |

| SEL4_ADDR     2     I     HW Mode: Select 4 Pin.Y-bridge threshold configuration setting.       I     I <sup>2</sup> C Mode: I <sup>2</sup> C address pin. |                       | <b>o o o</b>                    |                                                                                                                                                                                |

| SEL5                                                                                                                                                       | 1                     | I/O                             | HW Mode: Connect to IOVDD for external PVDD selection.                                                                                                                         |

| VBAT                                                                                                                                                       | 15                    | Р                               | Battery power supply input. Connect to a 2.5 to 5.5V supply and decouple with a capacitor.                                                                                     |

| VDD                                                                                                                                                        | 24                    | Р                               | Connect to 1.8V supply and decouple to GND with capacitor.                                                                                                                     |

(1) I = Input, O = Output, I/O = Input or Output, G = Ground, P = Power.

## 5 Specifications

## 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                           |                                         | MIN  | MAX      | UNIT |

|---------------------------|-----------------------------------------|------|----------|------|

| Supply Voltage            | PVDD                                    | -0.3 | 19       | V    |

| Supply Voltage            | VBAT                                    | -0.3 | 6        | V    |

| Supply Voltage            | VDD                                     | -0.3 | 2        | V    |

| Supply Voltage            | IOVDD                                   | -0.3 | 6        | V    |

| Class-D Output            | OUTP, OUTM                              | -0.7 | 19       | V    |

| High Side Drive Regulator | GREG                                    | -0.3 | PVDD + 6 | V    |

| Digital Supply Regulator  | DREG                                    | -0.3 | 1.65     | V    |

| Digital IO Pins           | Digital pins referenced to IOVDD supply | -0.3 | 6        | V    |

| T <sub>stg</sub>          | Storage temperature                     | -65  | 150      | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 5.2 ESD Ratings

|                    |                         |                                                                                     | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001, all pins <sup>(1)</sup>     | ±2000 | M    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per ANSI/ESDA/<br>JEDEC JS-002, all pins <sup>(2)</sup> | ±500  | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 5.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                   |                                       | MIN              | NOM | MAX  | UNIT |

|-------------------|---------------------------------------|------------------|-----|------|------|

| V <sub>PVDD</sub> | Amplifier Supply (External PVDD Mode) | V <sub>BAT</sub> | 12  | 15   | V    |

| V <sub>VDD</sub>  | Supply Voltage                        | 1.65             | 1.8 | 1.95 | V    |

| VIOVDD            | IO Supply Voltage 1.8V                | 1.62             | 1.8 | 1.98 | V    |

| VIOVDD            | IO Supply Voltage 3.3V                | 3.0              | 3.3 | 3.6  | V    |

| R <sub>SPK</sub>  | Speaker resistance                    | 3.2              | 8   | 38.4 | Ω    |

| L <sub>SPK</sub>  | Speaker inductance                    | 5                | 33  | 100  | μH   |

| T <sub>A</sub>    | Ambient temperature                   | -40              |     | 85   | °C   |

| TJ                | Junction temperature                  | -40              |     | 150  | °C   |

## 5.4 Thermal Information

|                       |                                              | Standard JEDEC <sup>(2)</sup> |      |

|-----------------------|----------------------------------------------|-------------------------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | HR-QFN                        | UNIT |

|                       |                                              | 26 PINS                       |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 51.5                          | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 28.5                          | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 15.3                          | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.9                           | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 15.2                          | °C/W |

## 5.4 Thermal Information (continued)

|                       |                                              | Standard JEDEC <sup>(2)</sup>                      |      |

|-----------------------|----------------------------------------------|----------------------------------------------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | HR-QFN                                             | UNIT |

|                       |                                              | ERMAL METRIC <sup>(1)</sup> HR-QFN UNIT<br>26 PINS |      |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | n/a                                                | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

(2) JEDEC Standard 4 Layer PCB

### **5.5 Electrical Characteristics**

TA = 25 °C, VBAT = 3.6 V, PVDD = 12 V (External PVDD mode enabled), VDD = 1.8 V, IOVDD = 1.8V, RL =  $8\Omega$  +  $33\mu$ H, fin = 1 kHz, fs = 48 kHz, Gain = 21dBV, SDZ = 1, Noise gate disabled, Measured filter free with an Audio Precision using 22 Hz to 20 kHz un-weighted bandwidth (unless otherwise noted).

|                                                           | PARAMETER                                     | TEST CONDITIONS                                                                                                                                                                                                                                             | MIN TYP MAX | UNIT |

|-----------------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|

| AMPLIFIE                                                  | R PERFORMANCE - EXTERNAL PVDD                 | /lode                                                                                                                                                                                                                                                       |             |      |

| P <sub>OUT EXT</sub> Maximum Continuous Output Power - 1% |                                               | R <sub>L</sub> = 8 Ω + 33 μH                                                                                                                                                                                                                                | 8.3         | W    |

| _PVDD                                                     | THDN                                          | R <sub>L</sub> = 4 Ω + 33 μH                                                                                                                                                                                                                                | 14.9        | W    |

| P <sub>OUT_EXT</sub><br>_pvdd                             | Maximum Continuous Output Power - 1%<br>THDN  | R <sub>L</sub> = 8 Ω + 33 µH, HW pin control mode                                                                                                                                                                                                           | 8.3         | w    |

| _                                                         |                                               | RL = 8 Ω + 33 μH                                                                                                                                                                                                                                            | 10.3        | W    |

| POUT_EXT                                                  | Maximum Continuous Output Power -<br>10% THDN | RL = 4 Ω + 33 μH                                                                                                                                                                                                                                            | 18.4        | W    |

| _PVDD                                                     |                                               | RL = 4 Ω + 33 μH, PVDD=14V                                                                                                                                                                                                                                  | 24.5        | W    |

| η <sub>SYSTEM_</sub>                                      | System Efficiency at P <sub>OUT</sub> = 0.5W  | R <sub>L</sub> = 8 Ω + 33 μH                                                                                                                                                                                                                                | 83.9        | %    |

|                                                           | System Enciency at POUT - 0.5W                | R <sub>L</sub> = 4 Ω + 33 μH                                                                                                                                                                                                                                | 80.0        | %    |

| N <sub>SYSTEM_</sub>                                      | System Efficiency at P <sub>OUT</sub> = 1.0W  | R <sub>L</sub> = 8 Ω + 33 μH                                                                                                                                                                                                                                | 88.1        | %    |

| _EXT_1W                                                   | System Enciency at P <sub>OUT</sub> – 1.0W    | R <sub>L</sub> = 4 Ω + 33 μH                                                                                                                                                                                                                                | 84.2        | %    |

| η <sub>SYSTEM_</sub><br>_EXT_1W                           | System Efficiency at P <sub>OUT</sub> = 1.0W  | R <sub>L</sub> = 8 Ω + 33 µH, HW pin control mode                                                                                                                                                                                                           | 88.1        | %    |

| η <sub>SYSTEM_</sub>                                      | System Efficiency at 1% THD+N power           | R <sub>L</sub> = 8 Ω + 33 μH                                                                                                                                                                                                                                | 93.2        | %    |

| EXT_MAX_<br>POUT                                          | Level                                         | R <sub>L</sub> = 4 Ω + 33 μH                                                                                                                                                                                                                                | 88.5        | %    |

| η <sub>SYSTEM_</sub><br>EXT_MAX_<br>POUT                  | System Efficiency at 1% THD+N power<br>Level  | R <sub>L</sub> = 8 Ω + 33 μH, HW pin control mode                                                                                                                                                                                                           | 93.2        | %    |

| V <sub>N_EXT</sub>                                        | Idle channel Noise                            | A-Weighted, Gain = 21dBV (Speaker<br>Mode), DAC-Running                                                                                                                                                                                                     | 14.4        | μV   |

| DNR_EX<br>T                                               | Dynamic Range                                 | A-Weighted, -60 dBFS Method, RL = 8 $\Omega$ + 33 $\mu H$                                                                                                                                                                                                   | 114.4       | dB   |

| THD+N_                                                    | Total Harmonic distortion + Noise             | $P_{OUT}$ = 1 W, R <sub>L</sub> = 8 $\Omega$ + 33 µH, f <sub>in</sub> = 1 kHz                                                                                                                                                                               | 0.003       | %    |

| EXT                                                       | Total Harmonic distortion + Noise             | $P_{OUT}$ = 1 W, R <sub>L</sub> = 4 $\Omega$ + 33 µH, f <sub>in</sub> = 1 kHz                                                                                                                                                                               | 0.004       | %    |

| K <sub>CP</sub> _EXT                                      | Click and pop performance                     | All dynamic power up/downs of audio<br>channel except for faults. Includes In/Out<br>of Mute, Power Up and power Down,<br>Noise Gate mode entry and Exit.<br>Measured at Peak A-weighted Voltage.<br>RL = 8 $\Omega$ + 33 $\mu$ H, Input = Digital Silience | -68         | dBV  |

| V <sub>OS</sub> _EX<br>T                                  | Output Offset Voltage                         | Idle channel                                                                                                                                                                                                                                                | -1 1        | mV   |

## 5.5 Electrical Characteristics (continued)

TA = 25 °C, VBAT = 3.6 V, PVDD = 12 V (External PVDD mode enabled), VDD = 1.8 V, IOVDD = 1.8V, RL =  $8\Omega$  +  $33\mu$ H, fin = 1 kHz, fs = 48 kHz, Gain = 21dBV, SDZ = 1, Noise gate disabled, Measured filter free with an Audio Precision using 22 Hz to 20 kHz un-weighted bandwidth (unless otherwise noted).

|                                              | PARAMETER                                                | TEST CONDITIONS                                                                            | MIN TYP | MAX   | UNIT   |

|----------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------|---------|-------|--------|

|                                              |                                                          | PVDD = 12 V + 200 mVpp, fripple = 217<br>Hz                                                | 115     |       | dB     |

| PSRR <sub>PV</sub><br>dd_ext                 | PVDD power-supply rejection ratio                        | PVDD = 12 V + 200 mVpp, fripple = 1<br>kHz                                                 | 115     |       | dB     |

|                                              |                                                          | PVDD = 12 V + 200 mVpp, fripple = 20<br>kHz                                                | 95      |       | dB     |

|                                              |                                                          | VBAT = $3.6 \text{ V} + 200 \text{ mV}_{\text{pp}}$ , $f_{\text{ripple}} = 217 \text{ Hz}$ | 115     |       | dB     |

| PSRR <sub>VB</sub><br><sub>AT</sub> _EXT     | VBAT power-supply rejection ratio                        | VBAT = $3.6 \text{ V} + 200 \text{ mV}_{\text{pp}}$ , $f_{\text{ripple}} = 1 \text{ kHz}$  | 115     |       | dB     |

| <u>.                                    </u> |                                                          | VBAT = 3.6 V + 200 mV <sub>pp</sub> , $f_{ripple}$ = 20 kHz                                | 90      |       | dB     |

|                                              |                                                          | VDD = 1.8 V + 200 mV <sub>pp</sub> , f <sub>ripple</sub> = 217 Hz                          | 110     |       | dB     |

| PSRR <sub>VD</sub>                           | VDD power-supply rejection ratio                         | VDD = 1.8 V + 200 mV <sub>pp</sub> , f <sub>ripple</sub> = 1 kHz                           | 110     |       | dB     |

|                                              |                                                          | VDD = 1.8 V + 200 mV <sub>pp</sub> , f <sub>ripple</sub> = 20 kHz                          | 90      |       | dB     |

| TDM Seri                                     | ial Port                                                 |                                                                                            |         |       |        |

|                                              | PCM Sample Rates and FSYNC Input<br>Frequency            |                                                                                            | 16      | 192   | kHz    |

|                                              | SBCLK Input Frequency                                    | I <sup>2</sup> S/TDM Operation                                                             | 0.512   | 24.57 | MHz    |

|                                              | CDCL// Maximum Input litter                              | RMS Jitter below 40 kHz that<br>can be tolerated without performance<br>degradation        |         | 0.5   | ns     |

|                                              | SBCLK Maximum Input Jitter                               | RMS Jitter above 40 kHz that<br>can be tolerated without performance<br>degradation        |         | 5     | ns     |

|                                              | SBCLK Cycles per FSYNC in I <sup>2</sup> S and TDM Modes | Values: 64, 96, 128, 192, 256, 384 and 512                                                 | 64      | 512   | Cycles |

| PCM Play                                     | yback Characteristics to fs ≤ 48 kHz                     |                                                                                            |         |       |        |

| fs                                           | Sample Rates                                             |                                                                                            | 16      | 48    | kHz    |

|                                              | Audio Channel Passband LPF Corner                        | Ripple < pass-band ripple                                                                  | 0.454   |       | fs     |

|                                              | Audio Channel Passband Ripple                            | 20 Hz to LPF cutoff                                                                        | ± 0.1   |       | dB     |

|                                              | Audio Channel Stop Band Attenuation                      | ≥ 0.55 fs                                                                                  | 60      |       | dB     |

|                                              | Audio Channel Stop Band Attendation                      | ≥ 1 fs                                                                                     | 65      |       | dB     |

|                                              |                                                          | Fin = 1kHz, Class-H mode                                                                   | 31.5    |       | 1/fs   |

|                                              |                                                          | Fin = 1kHz, Class-H bypassed                                                               | 6.5     |       | 1/fs   |

|                                              | Audio Channel Group Delay                                | DC to 20kHz, HPF bypassed, Class-H bypassed                                                | 11.0    |       | 1/fs   |

|                                              |                                                          | DC to 20kHz, HPF bypassed, Class-H mode                                                    | 37.0    |       | 1/fs   |

| PCM Play                                     | yback Characteristics to fs > 48 kHz                     |                                                                                            |         |       |        |

| fs                                           | Sample Rates                                             |                                                                                            | 88.2    | 192   | kHz    |

|                                              | Audio Channel Passband LPF Corner                        | fs = 96 kHz                                                                                | 0.469   |       | fs     |

|                                              |                                                          | fs = 192 kHz                                                                               | 0.234   |       | fs     |

|                                              | Audio Channel Passband Ripple                            | 20 Hz to LPF cutoff                                                                        | ± 0.2   |       | dB     |

|                                              |                                                          | fs = 96 kHz, fin ≥ 0.55 fs                                                                 | 60      |       | dB     |

|                                              | Audio Channel Stop Band Attenuation                      | fs = 96 kHz, fin ≥ 1 fs                                                                    | 65      |       | dB     |

|                                              |                                                          | fs = 192 kHz, 0.55 fs ≥ fin ≥ 0.275 fs                                                     | 60      |       | dB     |

## 5.5 Electrical Characteristics (continued)

TA = 25 °C, VBAT = 3.6 V, PVDD = 12 V (External PVDD mode enabled), VDD = 1.8 V, IOVDD = 1.8V, RL =  $8\Omega$  +  $33\mu$ H, fin = 1 kHz, fs = 48 kHz, Gain = 21dBV, SDZ = 1, Noise gate disabled, Measured filter free with an Audio Precision using 22 Hz to 20 kHz un-weighted bandwidth (unless otherwise noted).

|                           | PARAMETER                                                      | TEST CONDITIONS                                                                      | MIN | ТҮР   | MAX | UNIT |

|---------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------|-----|-------|-----|------|

|                           |                                                                | fin=1kHz, fs=96 kHz, Class-H mode                                                    |     | 56.7  |     | 1/fs |

|                           | Audio Channel Group Delay                                      | DC to 40kHz, fs=96 kHz, HPF Bypassed,<br>Class-H bypassed                            |     | 8.6   |     | 1/fs |

|                           |                                                                | DC to 40kHz, fs=192 kHz, HPF<br>Bypassed, Class-H Mode                               |     | 117.8 |     | 1/fs |

| Protectio                 | n Circuits                                                     | · · · · ·                                                                            |     |       |     |      |

|                           | Thermal shutdown temperature                                   |                                                                                      |     | 140   |     | °C   |

|                           | Thermal shutdown retry time                                    |                                                                                      |     | 1.5   |     | s    |

|                           | VBAT undervoltage lockout threshold                            | UVLO is asserted                                                                     | 1.9 |       |     | V    |

|                           | (UVLO)                                                         | UVLO is released                                                                     |     |       | 2.3 | V    |

|                           | VDD undervoltage lockout threshold                             | UVLO is asserted                                                                     | 1.4 |       |     | V    |

|                           | (UVLO)                                                         | UVLO is released                                                                     |     |       | 1.6 | V    |

|                           | PVDD undervoltage lockout threshold                            | UVLO is asserted, external PVDD mode only                                            | 2.6 |       |     | V    |

|                           | (UVLO)                                                         | UVLO is released, external PVDD mode only                                            |     |       | 2.8 | V    |

|                           | PVDD overvoltage lockout threshold<br>(OVLO)                   | OVLO is asserted, OVLO protection enabled.                                           |     | 16    |     | V    |

|                           | Output Short circuit protection                                | Output to Output, Output to GND, Output<br>to PVDD, Output to VBAT, H-bridge<br>mode |     | 4.1   |     | А    |

| Power up                  | o/down Time                                                    |                                                                                      |     |       |     |      |

| T <sub>STDBY</sub>        | Turn ON time from SDZ Asserted to device ready for i2c Command |                                                                                      |     |       | 300 | us   |

| F                         | Turn ON time from release of Software                          | Volume ramping disabled                                                              |     | 1.6   |     | ms   |

| <b>F<sub>ACTIVE</sub></b> | Shutdown to Amplifier output Active                            | Volume ramping enabled                                                               |     | 3.9   |     | ms   |

| F                         | Turn OFF time from assertion of Software                       | Volume ramping disabled                                                              |     | 0.2   |     | ms   |

| T <sub>TURNOFF</sub>      | Shutdown to Amplifier output Hi-Z                              | Volume ramping enabled                                                               |     | 13.9  |     | ms   |

| Current C                 | Consumption - External PVDD Mode                               |                                                                                      |     |       |     |      |

|                           |                                                                | PVDD, SDZ=0                                                                          |     | 1     |     | uA   |

|                           | Current consumption in Hardware                                | VBAT, SDZ=0                                                                          |     | 0.1   |     | uA   |

| Q_HW_SD                   | Shutdown                                                       | VDD, SDZ=0                                                                           |     | 0.2   |     | uA   |

|                           |                                                                | IOVDD, SDZ=0                                                                         |     | 0.1   |     | uA   |

|                           |                                                                | PVDD, All clocks Stopped                                                             |     | 1     |     | uA   |

|                           | Current consumption in Software                                | VBAT, All clocks Stopped                                                             |     | 0.1   |     | uA   |

| Q_SW_SD                   | Shutdown                                                       | VDD, All clocks Stopped                                                              |     | 12    |     | uA   |

|                           |                                                                | IOVDD, All clocks Stopped                                                            |     | 0.1   |     | uA   |

|                           |                                                                | PVDD, P <sub>OUT</sub> = 0, Noise gate enabled                                       |     | 0.1   |     | mA   |

|                           |                                                                | VBAT, P <sub>OUT</sub> = 0, Noise gate enabled                                       |     | 0.15  |     | mA   |

|                           | Current consumption in Idla channel                            | VDD, P <sub>OUT</sub> = 0, Noise gate enabled                                        |     | 2.2   |     | mA   |

| Q_NG                      | Current consumption in Idle channel                            | IOVDD, P <sub>OUT</sub> = 0, Noise gate enabled                                      |     | 0.1   |     | mA   |

|                           |                                                                | Total Power, P <sub>OUT</sub> = 0, Noise gate<br>enabled                             |     | 5.3   |     | mW   |

## 5.5 Electrical Characteristics (continued)

TA = 25 °C, VBAT = 3.6 V, PVDD = 12 V (External PVDD mode enabled), VDD = 1.8 V, IOVDD = 1.8V, RL =  $8\Omega$  +  $33\mu$ H, fin = 1 kHz, fs = 48 kHz, Gain = 21dBV, SDZ = 1, Noise gate disabled, Measured filter free with an Audio Precision using 22 Hz to 20 kHz un-weighted bandwidth (unless otherwise noted).

|                       | PARAMETER                                                       | TEST CONDITIONS                                                     | MIN              | TYP  | MAX            | UNIT |

|-----------------------|-----------------------------------------------------------------|---------------------------------------------------------------------|------------------|------|----------------|------|

|                       |                                                                 | PVDD, $P_{OUT} = 0$ , Noise gate disabled                           |                  | 0.2  |                | mA   |

|                       |                                                                 | VBAT, P <sub>OUT</sub> = 0, Noise gate disabled                     |                  | 0.5  |                | mA   |

|                       | Current consumption in Idle channel                             | VDD, P <sub>OUT</sub> = 0, Noise gate disabled                      |                  | 5.6  |                | mA   |

| 'Q_IDLE               |                                                                 | IOVDD, P <sub>OUT</sub> = 0, Noise gate disabled                    |                  | 0.1  |                | mA   |

|                       |                                                                 | Total Power, P <sub>OUT</sub> = 0, Noise gate<br>disabled           |                  | 14.0 |                | mW   |

|                       |                                                                 | PVDD, $P_{OUT}$ = 0, Noise gate disabled                            |                  |      |                | mA   |

|                       |                                                                 | VBAT, P <sub>OUT</sub> = 0, Noise gate disabled                     |                  |      |                | mA   |

|                       | Current consumption in Idle channel, ,                          | VDD, P <sub>OUT</sub> = 0, Noise gate disabled                      |                  |      |                | mA   |

| 'Q_IDLE               | HW pin control mode                                             | IOVDD, P <sub>OUT</sub> = 0, Noise gate disabled                    |                  |      |                | mA   |

|                       |                                                                 | Total Power, P <sub>OUT</sub> = 0, Noise gate<br>disabled           |                  |      |                | mW   |

| DIGITAL I             | lOs                                                             |                                                                     |                  |      |                |      |

| V <sub>IH</sub>       | High-level digital input logic voltage threshold                | All digital pins                                                    | 0.7 x<br>IOVDD   |      |                | V    |

| V <sub>IL</sub>       | Low-level digital input logic voltage threshold                 | All digital pins                                                    |                  |      | 0.3 x<br>IOVDD | V    |

| V <sub>OH</sub>       | High-level digital output voltage                               | All digital pins except SDA, SCL and IRQZ; $I_{OH}$ = 100µA         | IOVDD -<br>0.2 V |      |                | V    |

| V <sub>OL</sub>       | Low-level digital output voltage                                | All digital pins except SDA, SCL and IRQZ; I <sub>OL</sub> = -100µA |                  |      | 0.2            | V    |

| V <sub>OL(I2C)</sub>  | Low-level digital output voltage                                | SDA and SCL; I <sub>OL</sub> = -1mA                                 |                  |      | 0.2 x<br>IOVDD | V    |

| V <sub>OL(IRQZ)</sub> | Low-level digital output voltage for open drain output          | IRQZ pin; I <sub>OL</sub> = -1mA                                    |                  |      | 0.2            | V    |

| I <sub>IH</sub>       | Input logic-high leakage for digital inputs                     | All digital pins; Input = IOVDD.                                    | -1               |      | 1              | μA   |

| IIL                   | Input logic-low leakage for digital inputs                      | All digital pins; Input = GND                                       | -1               |      | 1              | μA   |

| C <sub>IN</sub>       | Input capacitance for digital inputs                            | All digital pins                                                    |                  | 5    |                | pF   |

| R <sub>PD</sub>       | Pull down resistance for digital input/IO pins when asserted on | All digital pins. Pull down resistance option enabled               |                  | 18   |                | kΩ   |

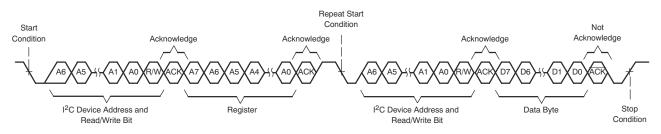

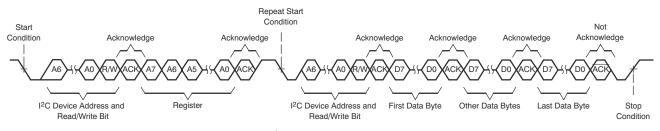

## 5.6 Timing Requirements

$T_A = 25 \text{ °C}$ , VDD = IOVDD = 1.8 V (unless other wise noted)

|                     |                                                                                              | MIN | NOM MAX | UNIT |

|---------------------|----------------------------------------------------------------------------------------------|-----|---------|------|

| I2C - Star          | ndard-Mode                                                                                   | ·   |         |      |

| f <sub>SCL</sub>    | SCL clock frequency                                                                          | 0   | 100     | kHz  |

| t <sub>HD;STA</sub> | Hold time (repeated) START condition. After this period, the first clock pulse is generated. | 4   |         | μs   |

| t <sub>LOW</sub>    | LOW period of the SCL clock                                                                  | 4.7 |         | μs   |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                                                                 | 4   |         | μs   |

| t <sub>SU;STA</sub> | Setup time for a repeated START condition                                                    | 4.7 |         | μs   |

| t <sub>HD;DAT</sub> | Data hold time: For I <sup>2</sup> C bus devices                                             | 0   | 3.45    | μs   |

| t <sub>SU;DAT</sub> | Data set-up time                                                                             | 250 |         | ns   |

| t <sub>r</sub>      | SDA and SCL rise time                                                                        |     | 1000    | ns   |

| t <sub>f</sub>      | SDA and SCL fall time                                                                        |     | 300     | ns   |

## **5.6 Timing Requirements (continued)**

T<sub>A</sub> = 25 °C, VDD = IOVDD = 1.8 V (unless other wise noted)

|                                        |                                                                                              | MIN              | NOM | MAX | UNIT |

|----------------------------------------|----------------------------------------------------------------------------------------------|------------------|-----|-----|------|

| SU;STO                                 | Set-up time for STOP condition                                                               | 4                |     |     | μs   |

| BUF                                    | Bus free time between a STOP and START condition                                             | 4.7              |     |     | μs   |

| C <sub>b</sub>                         | Capacitive load for each bus line                                                            |                  |     | 400 | pF   |

| I2C - Fast-M                           | Node                                                                                         |                  |     | I   |      |

| f <sub>SCL</sub>                       | SCL clock frequency                                                                          | 0                |     | 400 | kHz  |

| t <sub>HD;STA</sub>                    | Hold time (repeated) START condition. After this period, the first clock pulse is generated. | 0.6              |     |     | μs   |

| t <sub>LOW</sub>                       | LOW period of the SCL clock                                                                  | 1.3              |     |     | μs   |

| нідн                                   | HIGH period of the SCL clock                                                                 | 0.6              |     |     | μs   |

| SU;STA                                 | Setup time for a repeated START condition                                                    | 0.6              |     |     | μs   |

| t <sub>HD;DAT</sub>                    | Data hold time: For I <sup>2</sup> C bus devices                                             | 0                |     | 0.9 | μs   |

| t <sub>SU;DAT</sub>                    | Data set-up time                                                                             | 100              |     |     | ns   |

| t <sub>r</sub>                         | SDA and SCL rise time                                                                        | 20 + 0.1 ×<br>Cb |     | 300 | ns   |

| f                                      | SDA and SCL fall time                                                                        | 20 + 0.1 ×<br>Cb |     | 300 | ns   |

| SU;STO                                 | Set-up time for STOP condition                                                               | 0.6              |     |     | μs   |

| BUF                                    | Bus free time between a STOP and START condition                                             | 1.3              |     |     | μs   |

| Cb                                     | Capacitive load for each bus line                                                            |                  |     | 400 | pF   |

| TDM Port                               |                                                                                              |                  |     |     |      |

| <sub>H</sub> (SBCLK)                   | SBCLK high period                                                                            | 20               |     |     | ns   |

| t <sub>L</sub> (SBCLK)                 | SBCLK low period                                                                             | 20               |     |     | ns   |

| t <sub>SU</sub> (FSYNC<br>)            | FSYNC setup time                                                                             | 8                |     |     | ns   |

| t <sub>HLD</sub> (FSYN<br>C)           | FSYNC hold time                                                                              | 8                |     |     | ns   |

| t <sub>SU</sub> (SDIN/<br>ICC)         | SDIN/ICC setup time                                                                          | 8                |     |     | ns   |

| t <sub>HLD</sub> (SDIN/<br>ICC)        | SDIN/ICC hold time                                                                           | 8                |     |     | ns   |

| t <sub>d</sub> (SDO/<br>ICC-<br>SBCLK) | SBCLK to SDOUT/ICC delay : 50% of SBCLK to 50% of SDOUT<br>IOVDD=1.8V                        |                  |     | 13  | ns   |

| t <sub>d</sub> (SDO/<br>ICC-<br>SBCLK) | SBCLK to SDOUT/ICC delay : 50% of SBCLK to 50% of SDOUT<br>IOVDD=3.3V                        |                  |     | 30  | ns   |

| r(SBCLK)                               | SBCLK rise time : 10 % - 90 % Rise Time                                                      |                  |     | 8   | ns   |

| f(SBCLK)                               | SBCLK fall time : 90 % - 10 % Rise Time                                                      |                  |     | 8   | ns   |

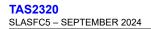

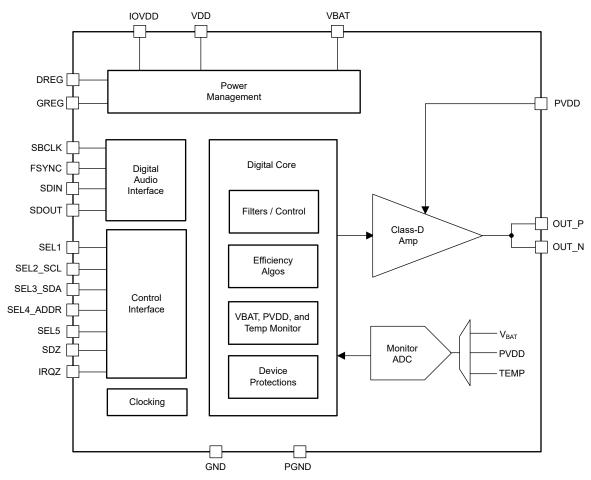

## **5.7 Typical Characteristics**

$T_A = 25^{\circ}$ C, VBAT = 3.6V, PVDD = 12V (External PVDD mode enabled), VDD=1.8 V, IOVDD=1.8 V, Load = 8 $\Omega$  + 33 $\mu$ H,  $F_{IN}$  = 1kHz, Fs = 48kHz, Gain = 21dBV, SDZ=1, Noise gate mode disabled, Measured filter free with an Audio Precision with a 22Hz to 20kHz un-weighted bandwidth, unless otherwise noted.

## 6 Detailed Description

## 6.1 Overview

The TAS2320 is a mono digital input Class-D amplifier optimized for delivering the highest efficiency across all powers for longer battery life operation. It comes with a small solution size for board space-constrained applications. It integrates battery/temperature sensors for system-level protection features.

## 6.2 Functional Block Diagram

Figure 6-1. Top Level Functional block diagram

#### 6.3 Device Functional Modes

#### 6.3.1 Operational Modes

#### 6.3.1.1 Hardware Shutdown

The device can be powered down by asserting SDZ pin low. The shutdown behavior of the device when SDZ pin is pulled low is controlled by SDZ\_MODE register settings.

In Hardware Shutdown mode (SDZ\_MODE[1:0] = 00 or 01) if the SDZ pin is asserted low, the device consumes the minimum quiescent current from VDD and VBAT supplies. All registers lose state in this mode and go back to default settings, and  $I^2C$  communication is disabled.

If configured in SDZ\_MODE[1:0] = 00, when the SDZ pin is asserted low while audio is playing, the device will follow the normal power down sequencing like volume ramp down on the audio (if enabled), stop the Class-D

switching, power down analog and digital blocks to ensure no power down pop and finally put the device into Hardware Shutdown mode. I2C communication is disabled while the SDZ pin is asserted low in this mode.

If configured in SDZ MODE[1:0] = 01, when the SDZ pin is asserted low the device will immediately enter the hardware shutdown and will not go through any power-down sequencing routine. It is recommended to ensure that the audio input signal is ramped down to the idle channel before asserting the SDZ pin low in this mode (device software mute mode can be used to realize this). I2C communication is disabled while the SDZ pin is asserted low in this mode.

Finally, the device can be configured to Software shutdown mode by setting SDZ MODE[1:0] = 10. In this mode, when the SDZ pin is pulled low, the device will follow normal power-down sequencing and enter software shutdown mode. All the device register configuration programmed is retained as is from the state the device was in before the SDZ pin was pulled low. I2C communication is still available while the SDZ pin is asserted low in this mode.

| Table 6-1. Shutdown Control |                                                       |  |  |

|-----------------------------|-------------------------------------------------------|--|--|

| SDZ_MODE[1:0]               | Configuration                                         |  |  |

| 00 (default)                | Hardware shutdown mode with<br>power-down sequencing  |  |  |

| 01                          | Hardware shutdown mode -<br>immediate                 |  |  |

| 10                          | Software shutdown mode (All register values retained) |  |  |

| 11                          | Reserved                                              |  |  |

| Table 6-1. Shutdown Cont | rol |

|--------------------------|-----|

|--------------------------|-----|

When SDZ MODE[1:0] is 00 or 10, the device goes through shutdown sequencing and the SDZ pin must be held low for the entire duration of the shutdown time. The shutdown time is specified in the Power up/down Time section of the Electrical Characteristics section. When SDZ is released, the device will sample the AD1 and AD2 pins and enter the software shutdown mode.

#### 6.3.1.2 Hardware Config Modes

The device can operate in a pre-configured HW Mode depending on the resistor terminations used for Select pin1 to Select Pin5. HW Mode behavior of the device is designed to simplify device configuration without using any software based configurations through I<sup>2</sup>C communication.

| SEL1 Connection      | Configuration                           |

|----------------------|-----------------------------------------|

| Direct Short to GND  | I <sup>2</sup> C Mode selection         |

| 1.2k to GND          | 6dBV Amp Gain, Volume ramp<br>disabled  |

| 1.2k to VBAT         | 12dBV Amp Gain, Volume ramp<br>disabled |

| 5k to GND            | 18dBV Amp Gain, Volume ramp<br>disabled |

| 330 to VBAT          | 21dBV Amp Gain, Volume ramp<br>disabled |

| 4.7k to VBAT         | 6dBV Amp Gain, Volume ramp<br>enabled   |

| 24k to GND           | 12dBV Amp Gain, Volume ramp<br>enabled  |

| 24k to VBAT          | 18dBV Amp Gain, Volume ramp<br>enabled  |

| Direct Short to VBAT | 21dBV Amp Gain, Volume ramp<br>enabled  |

| Table 6-2. | SEL1 | нw | Mode | configuration |

|------------|------|----|------|---------------|

|            |      |    | mode | ooninguruuon  |

| Table 6-5. SELZ HW Mode configuration |                                  |  |  |  |

|---------------------------------------|----------------------------------|--|--|--|

| SEL2_SCL Connection                   | Configuration                    |  |  |  |

| Direct Short to GND                   | I <sup>2</sup> S L or TDM0       |  |  |  |

| 470 to IOVDD                          | I <sup>2</sup> S R or TDM1       |  |  |  |

| Direct Short to IOVDD                 | I <sup>2</sup> S (L+R)/2 or TDM2 |  |  |  |

| 1.2k to GND                           | Left-Justified L or TDM3         |  |  |  |

| 1.2k to IOVDD                         | Left-Justified R or TDM4         |  |  |  |

| 4.7k to GND                           | Left-Justified (L+R)/2 or TDM5   |  |  |  |

| 4.7k to IOVDD                         | I <sup>2</sup> S L+Tx or TDM6    |  |  |  |

| 24k to GND                            | I <sup>2</sup> S R+Tx or TDM7    |  |  |  |

| 24k to IOVDD                          | Reserved                         |  |  |  |

|                                       |                                  |  |  |  |

## Table 6-3. SEL2 HW Mode configuration

| Table 6-4. | SEL3 HW | / Mode | configuration |

|------------|---------|--------|---------------|

|------------|---------|--------|---------------|

| SEL3_SDA Connection   | Configuration              |  |  |

|-----------------------|----------------------------|--|--|

| Direct Short to GND   | Data valid on rising edge  |  |  |

| Direct Short to IOVDD | Data valid on falling edge |  |  |

#### Table 6-5. SEL4 HW Mode configuration

| SEL4_ADDR Connection  | Configuration              |  |  |

|-----------------------|----------------------------|--|--|

| Direct Short to GND   | Y-bridge threshold of 80mW |  |  |

| Direct Short to IOVDD | Y-bridge threshold of 40mW |  |  |

| 24k to IOVDD          | Y-bridge threshold of 1mW  |  |  |

#### Table 6-6. SEL5 HW Mode configuration

| SEL5 Connection       | Configuration      |  |

|-----------------------|--------------------|--|

| Direct Short to IOVDD | External PVDD Mode |  |

#### 6.3.1.3 Software Power Modes Control and Software Reset

The TAS2320 power state can be controlled using the register MODE[1:0]. Change in any of the MODE settings will not cause the device to lose any of the existing device configuration register settings.

Active state: When MODE[1:0] is configured as '00', the device enters an active mode of operation with proper power-up sequencing to minimize the click and pop.

**Software shutdown state:** When MODE[1:0] is configured as '10', the device enters software shutdown mode. This mode powers down all analog blocks required to playback audio but does not cause the device to lose register state. If audio is playing when Software Shutdown is asserted, the Class-D will volume ramp down before shutting down. When de-asserted, the Class-D will begin switching and volume ramp back to the programmed digital volume setting.

**Clock based Active and shutdown state:** When MODE[1:0] is configured as '11' the device toggles between Active and Shutdown state based on valid ASI clock signals applied on the ASI input pins, BCLK and FSYNC. When clocks are applied, the device will automatically detect the clock signals and follow proper power-up sequencing to avoid any power-up click and pop. When the audio channels are powered up and the ASI clock is removed, the device will automatically start power-down sequencing and avoid any click and pop. It is recommended to do a volume ramp-down in the input data stream before stopping the clocks for the best pop & click experience (device software mute mode can be used to realize this).

| MODE[1:0] | Configuration                      |

|-----------|------------------------------------|

| 00        | Device in active mode of operation |

#### Table 6-7. Software Mode Control

|              | · · ·                                          |

|--------------|------------------------------------------------|

| MODE[1:0]    | Configuration                                  |

| 01           | Reserved                                       |

| 10 (default) | Device in software shutdown<br>mode            |

| 11           | Device in Clock based Active and shutdown mode |

#### Table 6-7. Software Mode Control (continued)

TAS2320 can be reset to its default configuration by setting the SW\_RESET register to '1'. If the device is powered up, when the SW\_RESET bit is set high, all the channels are powered down immediately. All the registers are restored to the default state when SW\_RESET is set high. This bit is self-clearing and goes back to '0' once the reset is complete.

The device can also signal to the host once the status of the device reaches Active mode of operation using the *INT\_LTCH0[1]* bit (Section 6.3.2). This bit is a live device status bit and reflects the device status in real-time. This bit is set high when the device is in Active mode and set low when the device is in shutdown mode.

#### 6.3.1.4 Efficiency and power saving modes

TAS2320 has multiple power-saving modes of operation designed to achieve the highest system level efficiency under all operating conditions. The device transitions from one mode to the next based on the configured mode and the signal condition. The transitions from one mode to another are automatic and designed to ensure high-performance audio levels during the transition of the modes.

#### 6.3.1.4.1 Noise Gate

When the Noise gate feature is enabled, the device automatically detects periods of silence during active playback mode and reduces the idle channel power consumption significantly to extend the battery life. This feature is useful for signals playback having long periods of silence, eg voice calls, movie tracks, etc.

The device monitors the input audio signal level against the programmed Noise gate threshold configured by the *NG\_TH\_LVL[2:0]* register. When the audio signal falls below the threshold, an internal Hysteresis timer is enabled. If the signal level remains below the configured *NG\_TH\_LVL[2:0]* for the entire duration of the *NG\_HYST\_TIMER[1:0]*, the device enters into the Noise gate mode and reduces the idle channel power consumption. In the Noise gate mode of operation, the high switching blocks like class-D PWM output are turned OFF and outputs are pulled low. The output impedance of class-D can be controlled when the Noise gate mode is active using the *CLASSD\_HIZ\_MODE* register. While the Noise gate mode is active, class-D outputs are not switching and the device does not produce any audio output signal. When the device is in Noise gate mode, the *NG\_STATUS* bit is set as high and when the device comes out of noise gate mode, the status bit is set to low.

When the signal level increases above the NG\_TH\_LVL[1:0], the device automatically wakes up the blocks in low IQ mode and starts playing out the audio input signals. The wake up from Noise gate maintains the signal fidelity by buffering the input signal data during the transition time from noise gate mode to active playback mode. The device does not lose any audio input samples while transitioning from noise gate to active playback.

The transition into noise gate mode and recovery out of noise gate mode is designed to be click and pop-free by following the proper shutdown and power up sequencing.

| Table 6-0. Noise gate threshold |               |

|---------------------------------|---------------|

| NG_TH_LVL[2:0]                  | Configuration |

| 000                             | -85 dBFs      |

| 001                             | -90 dBFs      |

| 010                             | -95 dBFs      |

| 011                             | -100 dBFs     |

#### Table 6-8. Noise gate threshold

| Jaco a Jaco a Contra (Contra a) |               |

|---------------------------------|---------------|

| NG_TH_LVL[2:0]                  | Configuration |

| 100 (default)                   | -105 dBFs     |

| 101                             | -110 dBFs     |

| 110                             | -115 dBFs     |

| 111                             | -120 dBFs     |

|                                 |               |

#### Table 6-8. Noise gate threshold (continued)

#### Table 6-9. Noise gate hysteresis timer

| j.                 | ·····         |

|--------------------|---------------|

| NG_HYST_TIMER[1:0] | Configuration |

| 00                 | 10 ms         |

| 01 (default)       | 50 ms         |

| 10                 | 100 ms        |

| 11                 | 1000 ms       |

#### 6.3.1.4.2 Music Efficiency Mode

When the Music efficiency mode feature is enabled, the device automatically detects low-power signal states during active playback mode and reduces the overall  $I_Q$  power consumption to extend the battery life. This feature is useful for dynamic audio signals with varying signal levels for example music tracks, voice calls movie tracks, and so forth.

The device monitors the input audio signal level against the programmed Music efficiency threshold configured by the *MUSIC\_EFF\_MODE\_THR*[23:0] register. When the audio signal falls below the threshold, an internal hysteresis timer is enabled. If the signal level remains below the configured *MUSIC\_EFF\_MODE\_THR*[23:0] for the entire duration of the *MUSIC\_EFF\_MODE\_TIMER*[23:0], the device enters into the Music efficiency mode. When the device is in Music efficiency mode, the *MUSIC\_EFF\_STATUS* bit is set as high and when the device comes out of music efficiency mode, the status bit is set low.

When the signal level increases above the  $MUSIC\_EFF\_MODE\_THR[23:0]$ , the device automatically wakes up the blocks in low  $I_Q$  mode and continues playing out the audio input signals. The transition from Music efficiency mode to normal operation occurs with minimal click and pop. While the device is in Music efficiency mode, the audio channel performance is maintained and doesn't impact the output signal level or noise.

The *MUSIC\_EFF\_MODE\_THR*[23:0] and *MUSIC\_EFF\_MODE\_TIMER*[23:0] registers can be configured using the PPC3 Software Section 6.4.1.

#### 6.3.2 Faults and Status

During power-up sequencing, the power-on-reset circuit (POR) monitors the VDD and IOVDD pins and holds device in reset (including all the configuration registers) until the supplies are valid. Any supply voltage dip on VDD or IOVDD below the UVLO voltage thresholds resets the device immediately along with all the register configurations.

During operation modes, the device monitors internal device status and fault conditions and can notify the host of error and status conditions using the IRQZ interrupt pin and internal I<sup>2</sup>C based interrupt registers. The interrupt generation in IRQZ pin can be masked by configuring the corresponding Interrupt mask register bit.

Table 6-10 lists the different faults and interrupts that the device monitors and the corresponding configuration bits to enable/disable the interrupt generation and reading the I2C interrupt status

|                                          | Table                         | 6-10. Faults and Inter         | rupts               |                                 |

|------------------------------------------|-------------------------------|--------------------------------|---------------------|---------------------------------|

| Category                                 | Interrupt                     | Interrupt Mask register<br>bit | Default Mask status | Interrupt Latched status<br>bit |

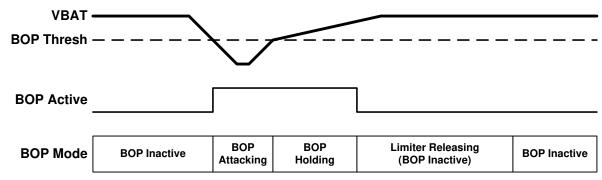

| Limiter & Brown out protection           | Brownout detected             | INT_MASK0[3]                   | Not Masked          | INT_LTCH0[3]                    |

|                                          | BOP Active                    | INT_MASK0[2]                   | Not Masked          | INT_LTCH0[2]                    |

|                                          | BOP infinite hold             | INT_MASK0[7]                   | Not Masked          | INT_LTCH0[7]                    |

|                                          | Limiter Active                | INT_MASK0[4]                   | Not Masked          | INT_LTCH0[4]                    |

| Section 6.4.2.4                          | Limiter attenuation           | INT_MASK0[6]                   | Not Masked          | INT_LTCH0[6]                    |

|                                          | Supply below inflection point | INT_MASK0[5]                   | Not Masked          | INT_LTCH0[5]                    |

|                                          | PVDD Over voltage             | INT_MASK3[2]                   | Not Masked          | INT_LTCH3[2]                    |

|                                          | PVDD Under voltage            | INT_MASK1[7]                   | Not Masked          | INT_LTCH1[7]                    |

| Supply Voltage Monitors<br>Section 6.4.4 | VBAT2S supply under voltage   | INT_MASK1[6]                   | Not Masked          | INT_LTCH1[6]                    |

| -                                        | VBAT supply under voltage     | INT_MASK4[7]                   | Not Masked          | INT_LTCH4[7]                    |

|                                          | Thermal warning at 135C       | INT_MASK1[4]                   | Masked              | INT_LTCH1[4]                    |

|                                          | Thermal warning at 125C       | INT_MASK1[3]                   | Masked              | INT_LTCH1[3]                    |

| Thermal protection<br>Section 6.4.5      | Thermal warning at 115C       | INT_MASK1[2]                   | Masked              | INT_LTCH1[2]                    |

|                                          | Thermal warning at 105C       | INT_MASK1[1]                   | Masked              | INT_LTCH1[1]                    |

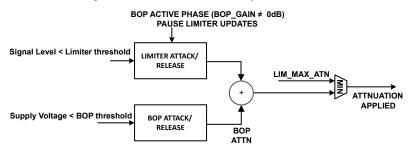

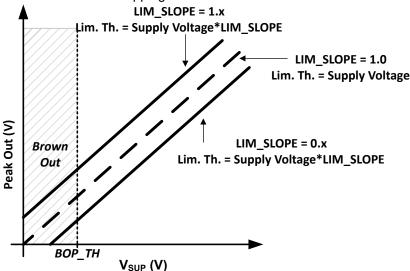

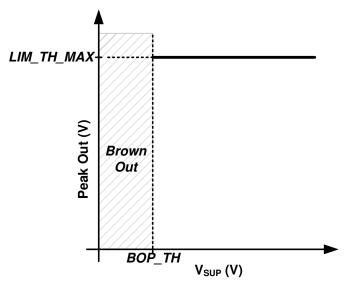

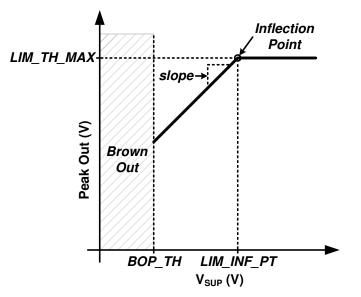

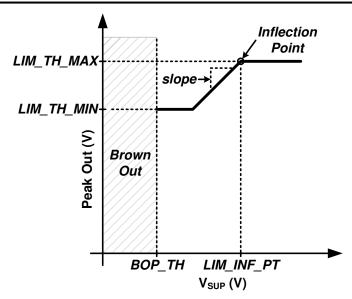

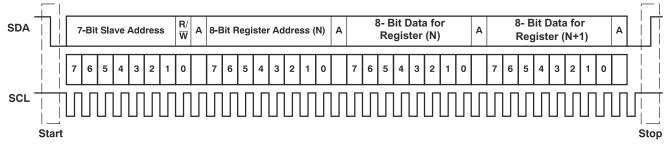

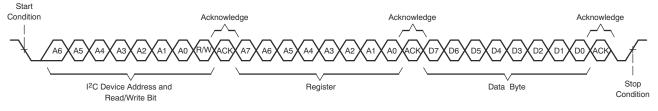

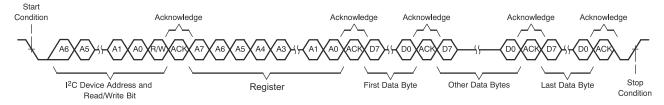

|                                          | Over temperature error        | INT_MASK3[7]                   | Not Masked          | INT_LTCH3[7]                    |