# LP5899 SPI-Compatible Connectivity for LP589x Device Family

# 1 Features

- Operating voltage V<sub>CC</sub> range: 2.5V to 5.5V

- SPI peripheral

- Data transfer rate up to 20MHz

- Support multiple peripherals with one controller

- Continuous Clock Serial Interface (CCSI) Controller and Peripheral

- Data transfer rate up to 20MHz

- \_ Programmable clock jitter for EMI enhancement

- Diagnostics

- Open-drain FAULT pin

- SPI communication loss detection

- CRC for SPI communication

- CCSI data integrity

- Data ready interrupt for availability of data

# 2 Applications

SPI compatible connectivity for LP5890 and LP5891

# **3 Description**

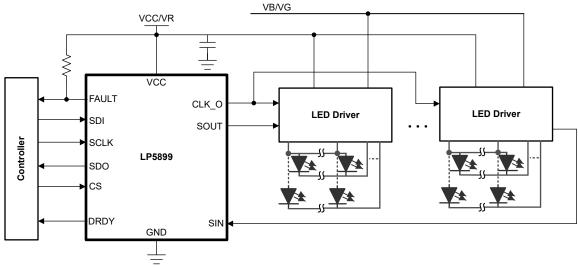

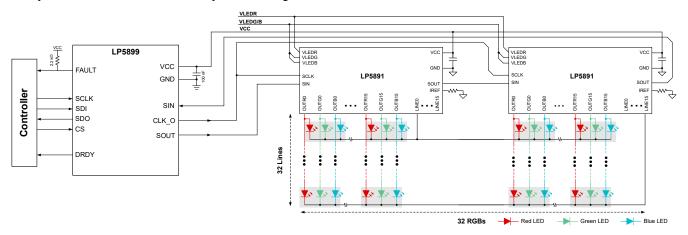

The LP5899 SPI-compatible connectivity enables LP589x device family to be controlled using a standard SPI controller. The device features an internal oscillator to generate the continuous clock required by the LP589x device family. Jitter can be added to the continuous clock for EMI enhancement. The transmitted data is aligned to the continuous clock to maintain the timing requirements of the CCSI interface.

LP5899 incorporates reporting of faults in both the LP589x daisy chain and LP5899 internal. Data transmission of register and VSYNC commands to the LP589x daisy chain is CRC protected by LP5899. In addition, the data line is guarded by LP5899 for stuck-at faults.

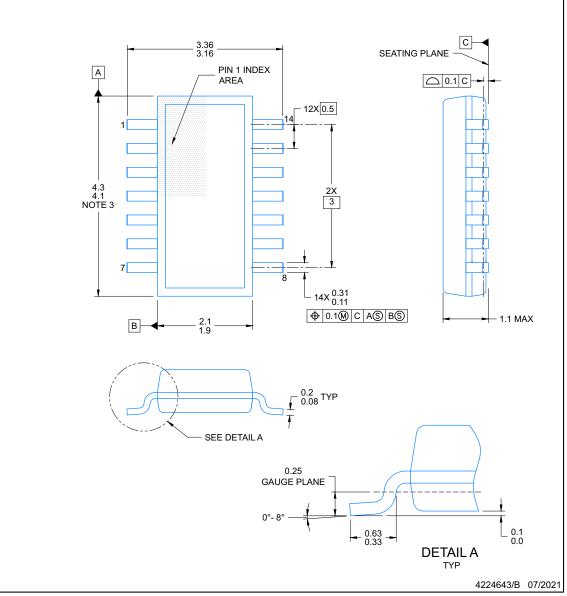

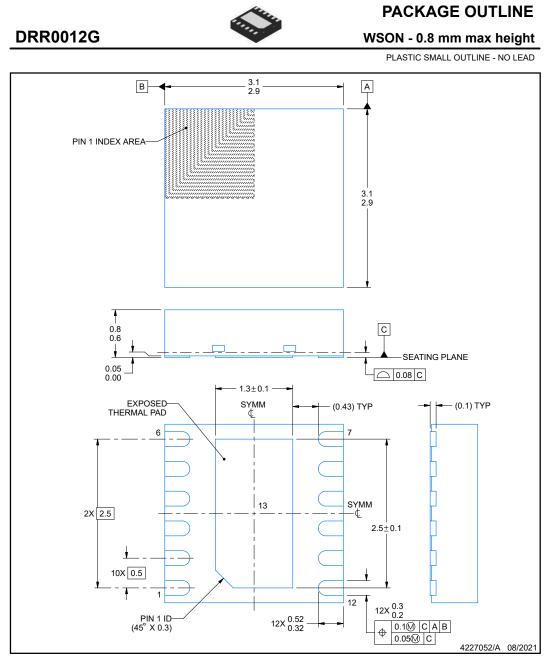

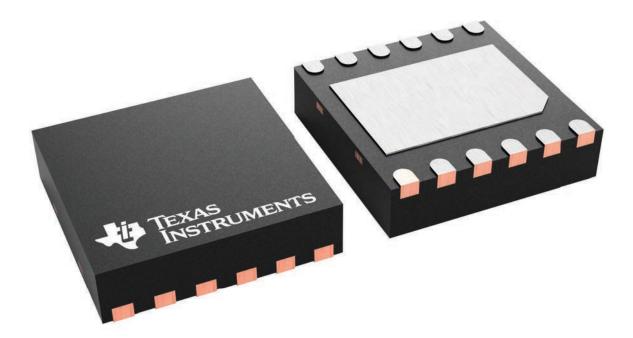

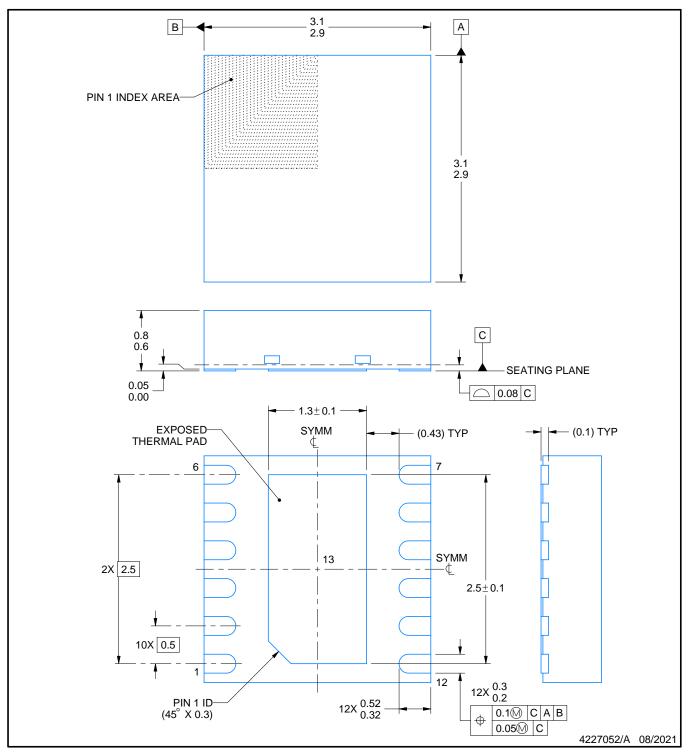

#### **Package Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |

|-------------|------------------------|-----------------------------|

| LP5899      | SOT-23-THN (14)        | 4.20mm x 2.00mm             |

|             | WSON (12)              | 3.00mm x 3.00mm             |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

(2)The package size (length × width) is a nominal value.

Figure 3-1. Typical Application Diagram

# **Table of Contents**

| 1 Features                           | 1 |

|--------------------------------------|---|

| 2 Applications                       | 1 |

| 3 Description                        | 1 |

| 4 Device Comparison                  | 3 |

| 5 Pin Configuration and Functions    |   |

| 6 Specifications                     | 4 |

| 6.1 Absolute Maximum Ratings         | 4 |

| 6.2 ESD Ratings                      |   |

| 6.3 Thermal Information              |   |

| 6.4 Recommended Operating Conditions |   |

| 6.5 Electrical Characteristics       |   |

| 6.6 Timing Requirements              | 6 |

| 6.7 Switching Characteristics        |   |

| 6.8 Timing Diagrams                  |   |

| 6.9 Typical Characteristics          | 8 |

| 7 Detailed Description               |   |

| 7.1 Overview                         |   |

| 7.2 Functional Block Diagram         | 9 |

| 7.3 Feature Description              |   |

| 7.4 Device Functional Modes          |   |

| 7.5 Programming                                     | . 23 |

|-----------------------------------------------------|------|

| 7.6 Device Registers                                |      |

| 8 Application and Implementation                    |      |

| 8.1 Application Information                         |      |

| 8.2 Typical Application                             |      |

| 8.3 Power Supply Recommendations                    | 50   |

| 8.4 Layout                                          | 50   |

| 9 Device and Documentation Support                  | 52   |

| 9.1 Device Support                                  | . 52 |

| 9.2 Documentation Support                           |      |

| 9.3 Receiving Notification of Documentation Updates | 52   |

| 9.4 Support Resources                               | . 52 |

| 9.5 Trademarks                                      |      |

| 9.6 Electrostatic Discharge Caution                 | 52   |

| 9.7 Glossary                                        | 52   |

| 10 Revision History                                 | 52   |

| 11 Mechanical, Packaging, and Orderable             |      |

| Information                                         | 52   |

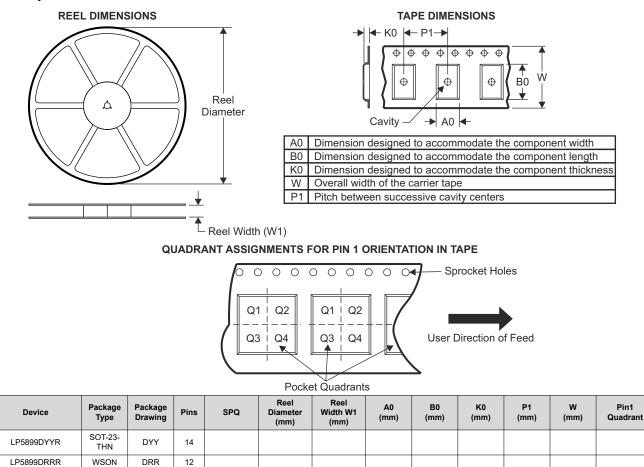

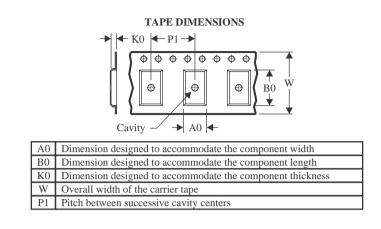

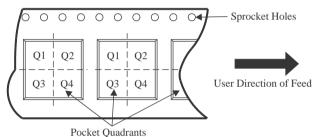

| 11.1 Tape and Reel Information                      |      |

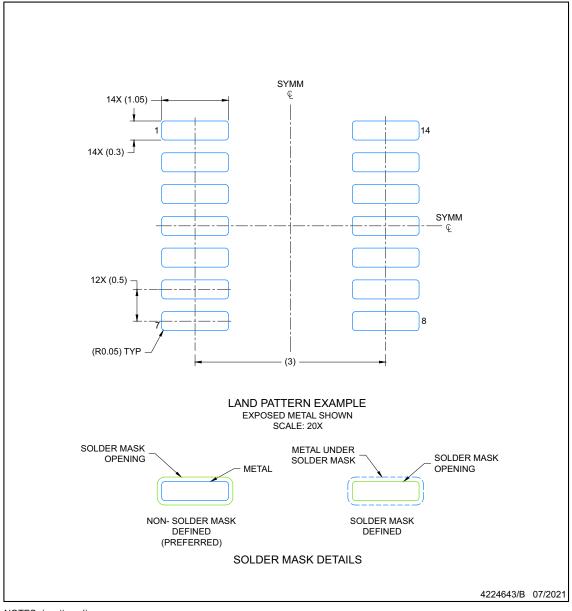

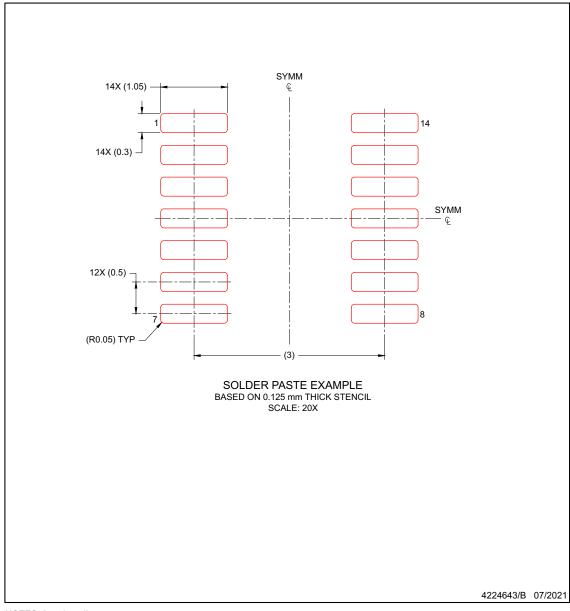

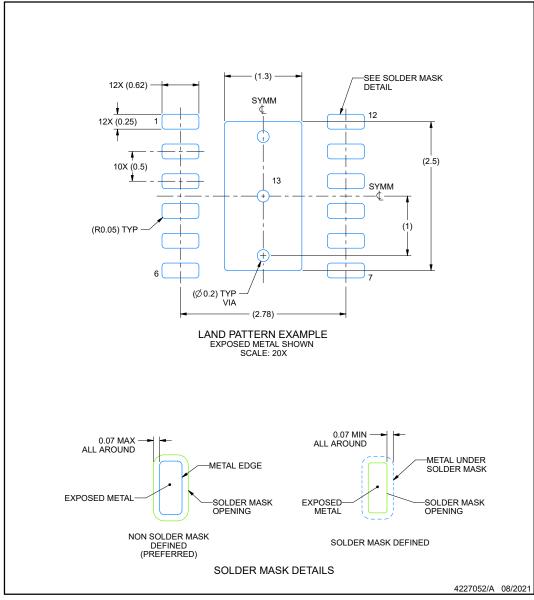

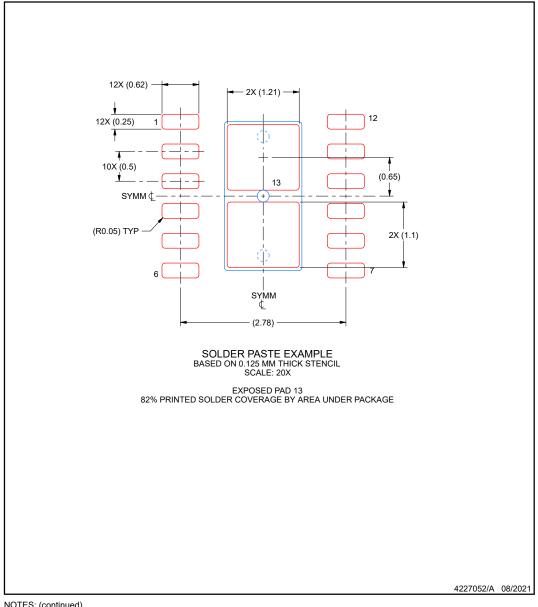

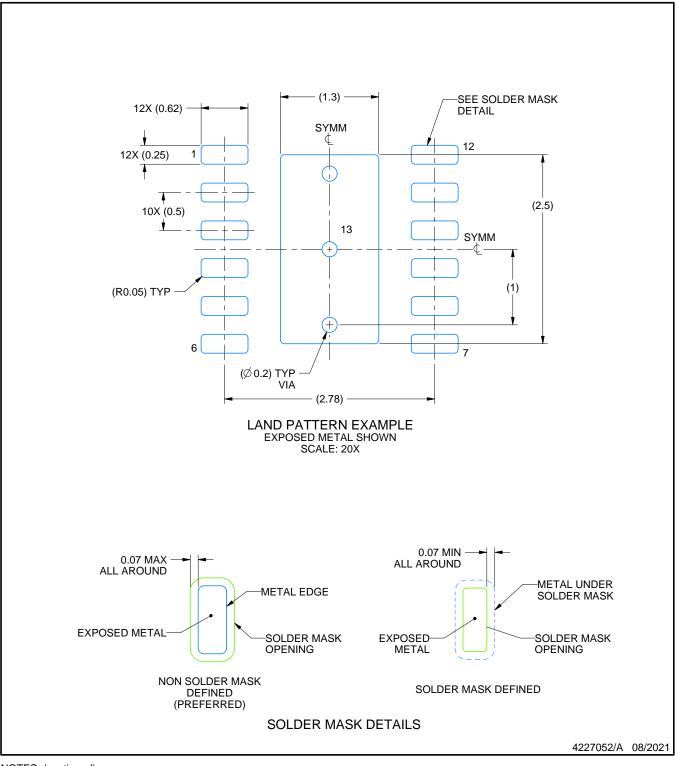

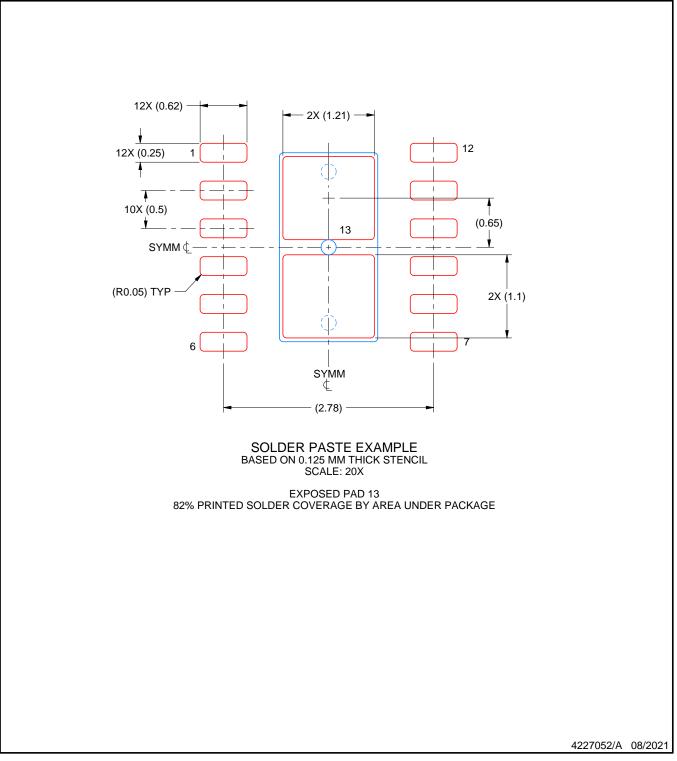

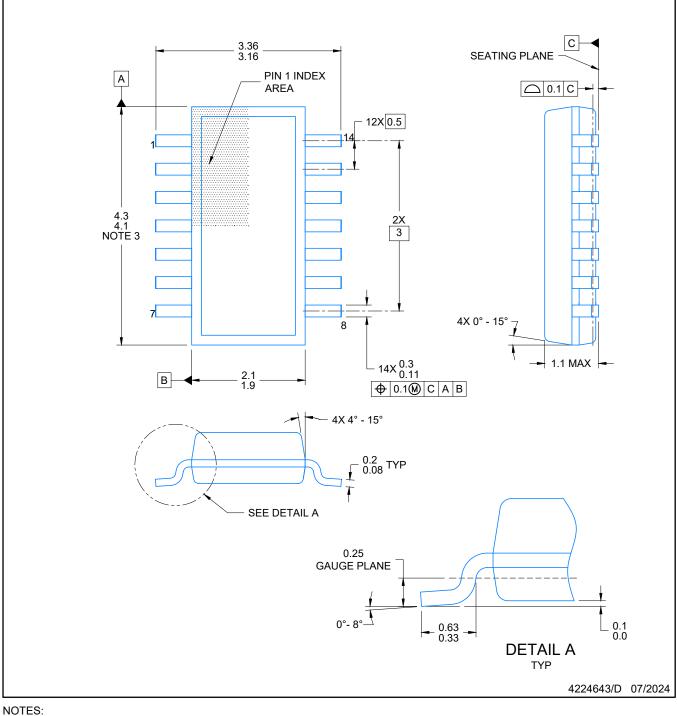

| 11.2 Mechanical Data                                | . 55 |

|                                                     |      |

# **4 Device Comparison**

| PART NUMBER | MATERIAL   | PACKAGE         |

|-------------|------------|-----------------|

| LP5899      | LP5899DYYR | SOT-23-THN (14) |

|             | LP5899DRRR | WSON (12)       |

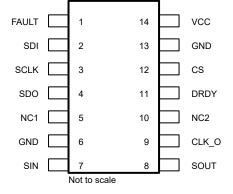

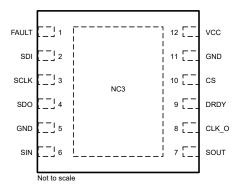

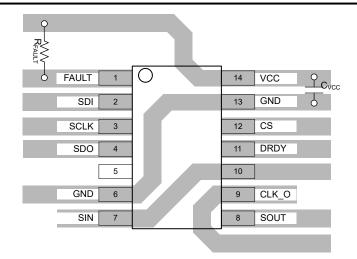

# **5** Pin Configuration and Functions

#### Table 5-1. Pin Functions

|       | PIN     |                | TYPE <sup>(1)</sup> | DESCRIPTION                                                                    |

|-------|---------|----------------|---------------------|--------------------------------------------------------------------------------|

| NAME  | DYY NO. | DRR NO.        |                     | DESCRIPTION                                                                    |

| FAULT | 1       | 1              | 0                   | Fault indicator pin                                                            |

| SDI   | 2       | 2              | I                   | SPI Serial Data Input                                                          |

| SCLK  | 3       | 3              | I                   | SPI Serial Clock Input                                                         |

| SDO   | 4       | 4              | 0                   | SPI Serial Data Output                                                         |

| NC1   | 5       | -              | NC                  | No connection. Can be used for signal routing.                                 |

| GND   | 6       | 5              | G                   | Ground pin (must connect to Ground)                                            |

| SIN   | 7       | 6              | I                   | CCSI Serial Data Input                                                         |

| SOUT  | 8       | 7              | 0                   | CCSI Serial Data Output                                                        |

| CLK_O | 9       | 8              | 0                   | CCSI Serial Clock Output                                                       |

| NC2   | 10      | -              | NC                  | No connection. Can be used for signal routing.                                 |

| DRDY  | 11      | 9              | 0                   | Data ready interrupt.                                                          |

| CS    | 12      | 10             | I                   | SPI Chip Select                                                                |

| GND   | 13      | 11             | G                   | Ground pin (must connect to Ground)                                            |

| VCC   | 14      | 12             | Р                   | VCC Power Supply Input                                                         |

| NC3   | -       | Exposed<br>Pad | NC                  | No connection. Need to be electrically isolated from any signal except Ground. |

(1) I = Input, O = Output, G = Ground, P = Power, NC = Not Connected.

# 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                            |                        | MIN  | MAX       | UNIT |

|--------------------------------------------|------------------------|------|-----------|------|

| Voltage on pins S<br>F<br>T <sub>J</sub> J | VCC                    | -0.3 | 6         | V    |

|                                            | SDI, SCLK, CS, SIN     | -0.3 | VCC + 0.3 | V    |

| voltage on pins                            | SDO, DRDY, SOUT, CLK_O | -0.3 | VCC + 0.3 | V    |

|                                            | FAULT                  | -0.3 | 6         | V    |

| TJ                                         | Junction temperature   | -40  | 150       | °C   |

| T <sub>stg</sub>                           | Storage temperature    | -55  | 150       | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

#### 6.2 ESD Ratings

|                    |                         |                                                                           | VALUE | UNIT |  |

|--------------------|-------------------------|---------------------------------------------------------------------------|-------|------|--|

| V                  | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001 <sup>(1)</sup>     | ±4000 | V    |  |

| V <sub>(ESD)</sub> |                         | Charged-device model (CDM), per ANSI/ESDA/<br>JEDEC JS-002 <sup>(2)</sup> | ±1000 | v    |  |

(1) JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

#### **6.3 Thermal Information**

|                       | THERMAL METRIC <sup>(1)</sup>                | DRR (SON) | DYY (SOT) |      |

|-----------------------|----------------------------------------------|-----------|-----------|------|

|                       |                                              | 12 PINS   | 14 PINS   |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 66.6      | 127.7     | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 57.1      | 58.9      | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 37.1      | 54.6      | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 2.3       | 3.2       | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 36.9      | 54.1      | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 12.7      |           | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 6.4 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                   |                                      | MIN | NOM | MAX             | UNIT |

|-------------------|--------------------------------------|-----|-----|-----------------|------|

| V <sub>CC</sub>   | Supply voltage                       | 2.5 |     | 5.5             | V    |

|                   | SDI, SCLK, CS, SIN                   | 0   |     | V <sub>CC</sub> | V    |

| Voltage on pins   | SDO, DRDY, SOUT, CLK_O               | 0   |     | V <sub>CC</sub> | V    |

|                   | FAULT                                | 0   |     | V <sub>CC</sub> | V    |

| f <sub>SCLK</sub> | SPI clock frequency                  |     |     | 20              | MHz  |

| C <sub>VCC</sub>  | V <sub>CC</sub> decoupling capacitor | 100 |     |                 | nF   |

| T <sub>A</sub>    | Ambient temperature                  | -40 |     | 85              | °C   |

### **6.5 Electrical Characteristics**

over operating free-air temperature range (unless otherwise noted),  $2.5V < V_{CC} < 5.5V$

|                        | PARAMETER                                          | TEST CONDITIONS                                                    | MIN       | TYP  | MAX  | UNIT |

|------------------------|----------------------------------------------------|--------------------------------------------------------------------|-----------|------|------|------|

| Input Supp             | bly                                                |                                                                    |           |      |      |      |

| V <sub>CC</sub>        | Device supply voltage                              |                                                                    |           |      | 5.5  | V    |

| V <sub>UVR</sub>       | Undervoltage restart                               | V <sub>CC</sub> rising                                             |           |      | 2.3  | V    |

| V <sub>UVF</sub>       | Undervoltage shutdown                              | V <sub>CC</sub> falling                                            | 2         |      |      | V    |

| V <sub>UV,HYS</sub>    | Undervoltage shutdown hysteresis                   |                                                                    |           | 0.12 |      | V    |

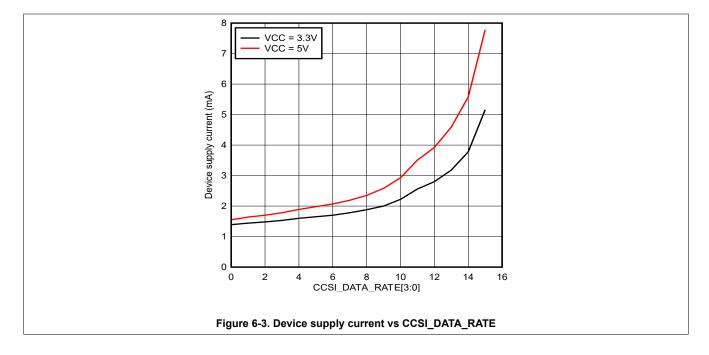

| I <sub>CC</sub>        | Device supply current                              | V <sub>CC</sub> = 3.3V, CCSI_DATA_RATE[3:0] =<br>4b'1110           |           | 3.6  |      | mA   |

| Oscillator             | •                                                  |                                                                    |           |      |      |      |

| f <sub>OSC</sub>       | Internal Oscillator frequency                      |                                                                    | -3%       | 40   | 3%   | MHz  |

| t <sub>WD,OSC</sub>    | Internal Oscillator Watchdog                       |                                                                    | 0.66      | 1.45 | 2.48 | μs   |

| Digital IO             | •                                                  |                                                                    |           |      |      |      |

| V <sub>IH</sub>        | High level input voltage (SCLK, SDI, CS, SIN)      |                                                                    | 1.05      |      |      | V    |

| V <sub>IL</sub>        | Low level input voltage (SCLK, SDI, CS, SIN)       |                                                                    |           |      | 0.45 | V    |

| V <sub>OH</sub>        | High level output voltage (SOUT, CLK_O, SDO, DRDY) | I <sub>OH</sub> = -3mA                                             | VCC - 0.4 |      | VCC  | V    |

| V <sub>OL</sub>        | Low level output voltage (SOUT, CLK_O, SDO, DRDY)  | I <sub>OL</sub> = 3mA                                              |           |      | 0.4  | V    |

| ILOGIC                 | Logic pin current (SCLK, SDI, CS, SIN)             | SCLK/SDI/CS/SIN = V <sub>CC</sub> or GND                           | -1        |      | 1    | μA   |

| FAULT                  |                                                    |                                                                    |           |      |      |      |

| I <sub>PD,FAULT</sub>  | FAULT pull-down current capability                 | V <sub>FAULT</sub> = 0.4V                                          | 22        | 59   |      | mA   |

| I <sub>LKG,FAULT</sub> | FAULT leakage current                              |                                                                    |           |      | 1    | μA   |

| V <sub>OH,FAULT</sub>  | High level output voltage (FAULT)                  | Voltage applied to FAULT pin through external pullup resistor      |           |      | VCC  | V    |

| V <sub>OL,FAULT</sub>  | Low level output voltage (FAULT)                   | I <sub>OL</sub> = 3mA, must be limited by external pullup resistor |           |      | 0.4  | V    |

| Diagnostic             | ss                                                 |                                                                    |           |      |      |      |

| t <sub>WD,SIN</sub>    | SIN Watchdog                                       |                                                                    |           | 5    |      | ms   |

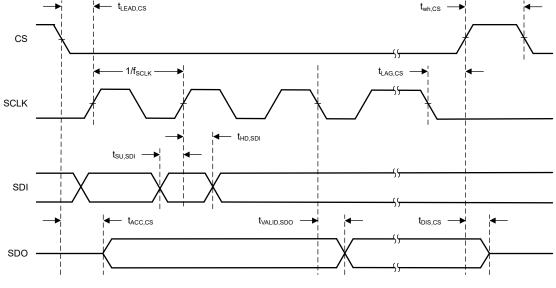

# 6.6 Timing Requirements

|                          | PARAMETER                                                | TEST CONDITIONS | MIN | NOM | MAX | UNIT |

|--------------------------|----------------------------------------------------------|-----------------|-----|-----|-----|------|

| f <sub>SCLK,NORMAL</sub> | SCLK clock frequency in NORMAL state                     |                 |     |     | 20  | MHz  |

| f <sub>SCLK,INIT</sub>   | SCLK clock frequency in INIT state                       |                 |     |     | 5   | MHz  |

| t <sub>LEAD,CS</sub>     | Delay time, first SCLK rising edge after CS falling edge |                 | 15  |     |     | ns   |

| t <sub>LAG,CS</sub>      | Delay time, CS rising edge after final SCLK falling edge |                 | 5   |     |     | ns   |

| t <sub>SU,SDI</sub>      | SDI input data setup time before SCLK rising egde        |                 | 10  |     |     | ns   |

| t <sub>HD,SDI</sub>      | SDI input data hold time after SCLK rising edge          |                 | 5   |     |     | ns   |

| t <sub>wh,CS</sub>       | Pulse duration, CS high                                  |                 | 40  |     |     | ns   |

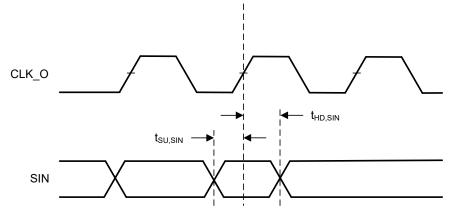

| t <sub>SU,SIN</sub>      | SIN input data setup time before CLK_O rising edge       |                 | 10  |     |     | ns   |

| t <sub>HD,SIN</sub>      | SIN input data hold time after CLK_O rising edge         |                 | 2   |     |     | ns   |

# 6.7 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

|                        | PARAMETER                                                                                                               | TEST CONDITIONS                                   | MIN TYP | MAX  | UNIT |

|------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|---------|------|------|

| t <sub>ACC,CS</sub>    | Propagation delay time, CS falling edge to SDO driven                                                                   |                                                   |         | 50   | ns   |

| t <sub>DIS,CS</sub>    | Propagation delay time, CS rising edge to SDO high impedance                                                            |                                                   |         | 75   | ns   |

| t <sub>VALID,SDO</sub> | Propagation delay time, SCLK falling edge to valid new SDO                                                              |                                                   |         | 22   | ns   |

|                        |                                                                                                                         | CCSI_DATA_RATE[3:0] = 4b'1110                     | 33.33%  |      |      |

| DC <sub>CLK_O</sub>    | Duty cycle CLK_O                                                                                                        | CCSI_DATA_RATE[3:0] = 4b'1100                     | 40%     |      |      |

|                        |                                                                                                                         | CCSI_DATA_RATE[3:0] = Others                      | 50%     |      |      |

| t <sub>r,SOUT</sub>    | Rise time (SOUT) - from 10% of $V_{CC}$ to 90% of $V_{CC}$                                                              | V <sub>CC</sub> = 3.3V, C <sub>SOUT</sub> = 30pF  | 2       | 10   | ns   |

| t <sub>f,SOUT</sub>    | Fall time (SOUT) - from 90% of V_{CC} to 10% of V_{CC}                                                                  | V <sub>CC</sub> = 3.3V, C <sub>SOUT</sub> = 30pF  | 2       | 10   | ns   |

| f <sub>CLK_O</sub>     | CLK_O output frequency. The output voltage reaches at least 10% and 90% $V_{\rm CC}$ at the specified toggle frequency. | V <sub>CC</sub> = 3.3V, C <sub>CLK_O</sub> = 30pF |         | 20.6 | MHz  |

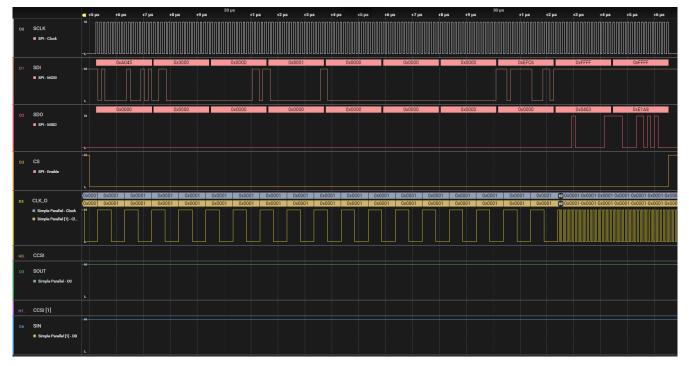

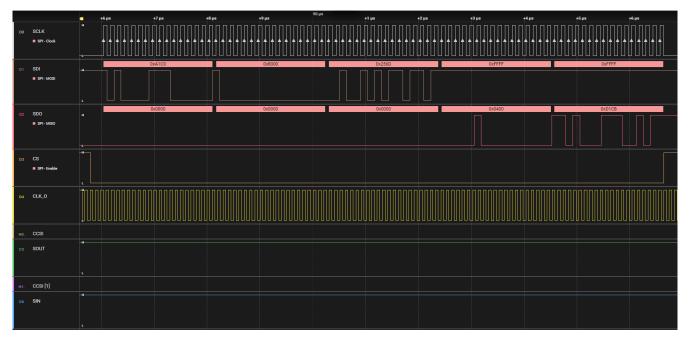

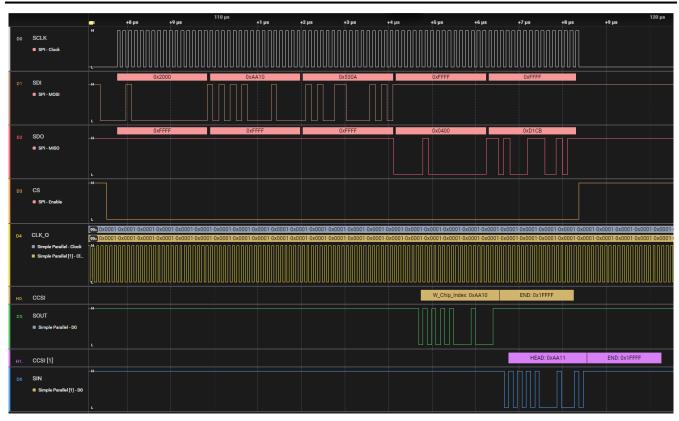

# 6.8 Timing Diagrams

Figure 6-1. SPI Peripheral Timing Diagram

Figure 6-2. CCSI Peripheral Timing Diagram

# **6.9 Typical Characteristics**

At  $T_A$  = 25°C and  $V_{CC}$  = 3.3V, unless otherwise noted.

# 7 Detailed Description

### 7.1 Overview

The LP5899 is an SPI-compatible connectivity between an SPI and a Continuous Clock Serial Interface (CCSI). The device can drive any number of cascaded LED drivers of the LP589x family. The maximum number of cascaded devices is limited by the LED driver.

The LP5899 uses an internal oscillator and clock divider to provide a programmable continuous clock frequency for the CCSI. Data words received by the SPI peripheral are forwarded by the CCSI controller where the data is aligned to the continuous clock. Data words received by the CCSI peripheral can be stored by the LP5899 and read by the Controller using SPI. The continuous clock incorporates a programmable pseudo-random jitter (spread spectrum) feature to reduce EMI emissions.

The LP5899 automatically inserts the required start bit and check bits when forwarding the data words received by SPI peripheral. For data words received by the CCSI peripheral, the LP5899 automatically analyses the check bits and reports when an error is detected. When the data words are stored for reading by SPI, the start bit and check bits are removed from the data string.

The LP5899 automatically inserts the required end byte when forwarding the data words received by SPI peripheral to make sure that different SPI commands are recognized as different CCSI commands. When the data words are stored for reading by SPI, the end byte is removed from the data string.

#### VCC Bandgap ESD Spread osc Internal Spectrum UVLO I DO SCLK SOUT SRAM CCSI SDI (TXFIFO) Controller CLK\_O SPI Peripheral SDO cs SRAM CCSI Digital Core (RXFIFO Peripheral SIN CRC FAULT OTP DRDY GND

# 7.2 Functional Block Diagram

Figure 7-1. Functional Block Diagram

### 7.3 Feature Description

### 7.3.1 Internal Oscillator and Clocks

#### 7.3.1.1 System Clock

The LP5899 has an internal oscillator which provides a 40MHz system clock for the device. The system clock is used to operate the digital logic.

#### Internal Oscillator Watchdog

The internal oscillator watchdog timer ( $t_{WD,OSC}$ ) is automatically enabled upon exit from POR. If the internal oscillator stops toggling for more than  $t_{WD,OSC}$ , the watchdog expires and holds the logic in reset (POR) until the oscillator begins toggling again. The internal oscillator is used as the system clock.

#### 7.3.1.2 Continuous Clock Serial Interface (CCSI) Clock

The clock for transmitting data by the CCSI controller is derived from the system clock. There are 16 divider options available (CCSI\_DATA\_RATE in register CCSICTRL) to achieve the desired clock frequency for the daisy chain of LED drivers.

The CCSI clock can be modulated by a programmable digital spread spectrum to improve the system level EMI performance. Field CCSI\_SS\_CLKO in register CCSICTRL determines if the spread spectrum is enabled. When CCSI\_DATA\_RATE \* CCSI\_SS\_CLKO \* 2 is smaller than 120kBit/s, a modulation frequency of 30kHz is used. Otherwise the modulation frequency is 120kHz. When CCSI\_DATA\_RATE in register CCSICTRL is set to 4b'1111 or 4b'1110, spread spectrum is not recommended to be enabled.

### 7.3.2 Continuous Clock Serial Interface (CCSI)

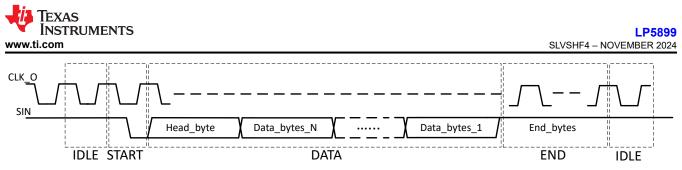

The continuous clock series interface (CCSI) provides access to the programmable functions and registers of the LED drivers that are connected in a daisy chain between the CCSI controller and CCSI peripheral. The serial data output (SOUT) and serial clock output (CLK\_O) are used for the CCSI controller. When the CCSI controller is not transmitting, the SOUT is set to logic HIGH, while the CLK\_O remains active and continuous. The continuous clock starts after the device powers up. To start transmission by the CCSI controller, the device needs to be in NORMAL state and the flag FLAG\_POR has to be cleared.

The CCSI peripheral consists of one wire, which is the serial data input (SIN). The data is shifted in using the same clock source as CLK\_O.

#### 7.3.2.1 Command Format

The command format is viewed from the CCSI peripheral side. Figure 7-2 defines the format of the command transmission. There are three states in one command:

- IDLE: CLK\_O is always active and continuous. SIN is always HIGH.

- **START:** SIN changes from HIGH to LOW after the IDLE state.

- DATA:

- **Head\_byte:** The command identifier, contains one 16-bit data and one check bit.

- Data\_bytes\_N-1: Each data-byte contains 3 × 17-bit data, each 17-bit data contains one 16-bit data word and one check bit.

- END: The device recognizes continuous 18-bit HIGH on SIN, and then returns to IDLE state.

- CHECK BIT: The check bit (17<sup>th</sup> bit) value is the *NOT* of 16<sup>th</sup> bit value to avoid continuous 18-bit HIGH (to distinguish with END).

The IDLE state is not necessary, which means the START state of the next command can connect to the END state of the current command.

Figure 7-2. Command Format

#### 7.3.2.2 Command Recognition and Synchronization

Two different CCSI commands require at least one END byte in between the commands to be able to be recognized as separate commands. The LP5899 automatically inserts one END byte after all the data from one SPI command has been transmitted. However, for certain CCSI commands, the LED drivers add data to the data stream. In this case, one END byte during transmission is not sufficient to distinguish the two CCSI commands by the CCSI peripheral. Without sufficient END bytes, the CCSI controller and CCSI peripheral get out of synchronization. The synchronization is required for several actions. For example, to determine if the received data needs to be stored on the RXFIFO or if a CRC needs to be calculated over the received data and compared to the CRC over the transmitted data. In case the synchronization is lost, the SPI command SOFTRESET\_CRC can be used to bring the CCSI controller and peripheral back in sync. The SPI controller is responsible there are sufficient END bytes between CCSI commands to keep the synchronization by using a dedicated SPI command that inserts extra END bytes.

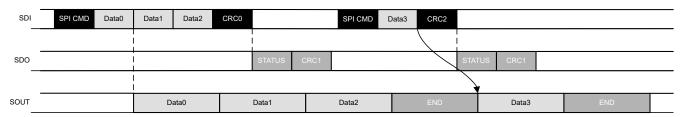

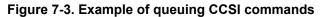

#### 7.3.2.3 CCSI Command Queue

The CCSI controller has the ability to queue multiple SPI commands. This means that when the CCSI controller is still transmitting, a new SPI forward command can be received by the SPI peripheral. This new command is automatically transmitted after the old command is finished transmitting. An example is depicted in Figure 7-3. Note that in this figure every data word is 16 bits. That means that when the width of the block is larger, the clock frequency is lower. In this example the CCSI frequency is lower than the SPI frequency.

#### 7.3.2.4 CCSI Start Bit and Check Bits Insertion and Removal

The LP5899 automatically inserts and removes the start bit and check bits that are required for the CCSI. This means that those bits do not have to be inserted in the SPI data words when transmitted by the controller. In addition, when reading back data using SPI, the start bit and check bits are removed. This results in standard 16 bits SPI data words. An example of this feature is depicted in Figure 7-4. In the remaining part of this document, the start bit and check bits are not explicitly shown anymore.

Figure 7-4. Example of insertion and removal of start bit and check bits

### 7.3.3 FIFO

The LP5899 has both a transmit and receive FIFO. The naming of the FIFOs are viewed from the Continuous Clock Serial Interface (CCSI). That means the transmit FIFO (TXFIFO) is the data that was received by the SPI peripheral and transmitted by the CCSI controller. The receive FIFO (RXFIFO) is the data received by the CCSI peripheral which can be read by the controller via SPI peripheral.

Both FIFOs are 16-bit-wide first-in-first-out memory buffers. The FIFOs are used to store data words to fulfil the timing requirements while the data is crossing between the SPI clock domain and CCSI clock domain. The TXFIFO holds the data during the crossover from the SPI clock to the CCSI clock domain. The RXFIFO holds the data during the crossover from the CCSI clock domain to the SPI clock domain.

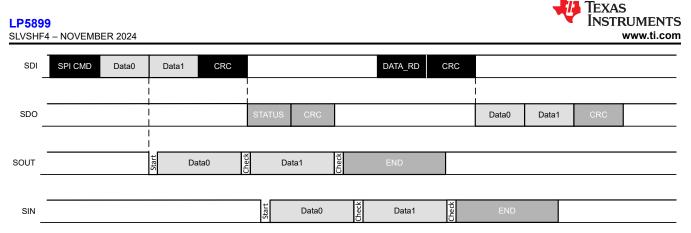

When the SPI clock domain runs at a higher frequency than the CCSI clock domain, the TXFIFO stores data already received by the SPI peripheral which has not been transmitted yet by the CCSI controller. A counter (TXFFST) keeps track of the number of words currently stored in the TXFIFO. The example where the SPI peripheral runs at a higher clock frequency than the CCSI controller is depicted in Figure 7-5. Note that in this figure every data word is 16 bits. That means that when the width of the block is larger, the clock frequency is lower.

Figure 7-5. Example of SPI peripheral running at higher frequency than CCSI controller

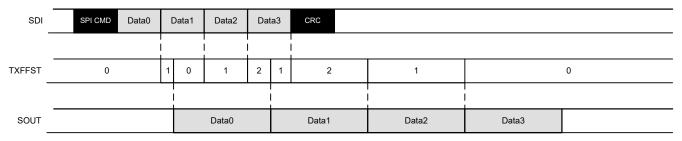

When the SPI peripheral runs at a lower clock frequency than the CCSI controller, the TXFIFO is used to first store a number of data words received by the SPI peripheral before the transmission by the CCSI controller starts. Following this method, the data stream on the CCSI can be made continuous without requiring the continuous clock to stop because the data word was not received yet by the SPI peripheral. An example of this situation is depicted in Figure 7-6.

| SDI    | SPI CMD | Data0 | Data1 | Data2 |       | Data  | 3     | С     |       |  |

|--------|---------|-------|-------|-------|-------|-------|-------|-------|-------|--|

|        |         |       |       |       |       |       |       |       |       |  |

| TXFFST | 0       |       | 1     | 2     | 3 2 1 |       |       | 1     | 0     |  |

|        |         |       |       |       |       |       |       |       |       |  |

| SOUT   |         |       |       |       | C     | Data0 | Data1 | Data2 | Data3 |  |

### Figure 7-6. Example of SPI peripheral running at lower frequency than CCSI controller

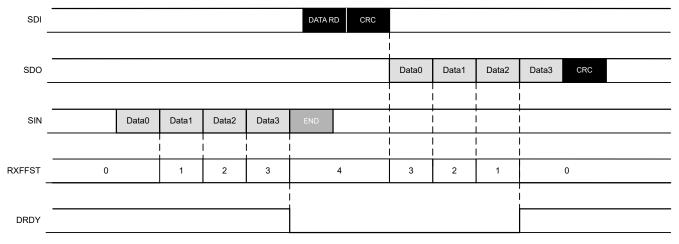

For the RXFIFO, the CCSI peripheral receives the data and stores them on the RXFIFO. The SPI peripheral reads the data from the RXFIFO and transmits them to the SPI controller. Also for the RXFIFO a counter (RXFFST) exists to keep track of the number of data words currently stored.

Note that when an END byte is received, the storage stops. The END byte itself is not stored on the RXFIFO. Also the START bit and CHECK bits are not stored.

#### 7.3.3.1 FIFO level and Data Ready (DRDY) Interrupt

The TXFIFO level (TXFFLVL) controls the start of the transmission of the CCSI controller for SPI forward commands that are independent of the SPI CRC. With correct setting of the FIFO level, FIFO overflow and underflow can be prevented. The setting is dependent on the difference between the SPI clock frequency and CCSI clock frequency, the accuracy of the clock provided to the SPI peripheral, accuracy of the clock of the CCSI controller, and the maximum length of data that is being forwarded.

The RXFIFO level (RXFFLVL) controls the Data Ready (DRDY) interrupt. When the number of data words on the RXFIFO exceed the RXFFLVL, the DRDY pin becomes logic LOW. This DRDY pin remains logic LOW until there are no more words on the RXFIFO. The RXFFLVL setting has the same dependencies as the TXFFLVL except the maximum length of data that is being forwarded is replaced by the maximum number of data words that is received by the CCSI peripheral. An example of the DRDY pin's behavior is depicted in Figure 7-7.

#### Figure 7-7. Example of DRDY pin with RXFFLVL register set to 3

The DRDY pin also becomes logic LOW when an END byte is detected and the number of words on the RXFIFO has not reached the RXFFLVL yet.

#### 7.3.3.2 FIFO Clearance

To stop an ongoing CCSI transmission, the TXFIFO can be cleared by bit TXFFCLR in register TXFFLVL. This resets the TXFIFO counter (TXFFST) to 0. All the commands in the queue are cleared. The CCSI controller automatically inserts an END byte to reset the LED drivers. The CCSI peripheral continues to work as normal. The TXFFCLR bit automatically returns to 0.

The data on the RXFIFO can be cleared by bit RXFFCLR in register RXFFLVL. This resets the RXFIFO counter (RXFFST) to 0. If the CCSI peripheral is receiving data that needs to be stored on the RXFIFO, the storage is stopped for this command. The next CCSI command received by the CCSI peripheral follows the original request of the SPI command. The CCSI controller continues to work as normal. The RXFFCLR bit automatically returns to 0.

#### 7.3.4 Diagnostics

The LP5899 provides both device internal and device external diagnostics. The device detects failures and reports the status out through the FAULT pin and the status registers. The SPI controller is required to take action to bring the device in a normal operating condition. Faults can be cleared by writing bit CLR\_FLAG in the STATUS register. Only the OTP CRC error and Failsafe state flags cannot be cleared by this bit. The CLR\_FLAG bit automatically returns to 0. If a fault remains, the error flag is set after the next detection.

#### 7.3.4.1 Undervoltage Lockout

When VCC voltage drops below the UVLO threshold, the device enters Unpowered state. Upon voltage recovery, the device automatically switches to Initialization state with FLAG\_POR and FLAG\_ERR set to 1. The SPI controller can write 1 to register CLR FLAG to clear the flags.

#### 7.3.4.2 Oscillator Fault Diagnostics

The internal clock watchdog timer ( $t_{WD,OSC}$ ) is automatically enabled upon exit from POR. If the internal oscillator stops toggling for more than  $t_{WD,OSC}$ , the watchdog expires and the FAULT pin is pulled low. The fault is latched and when the oscillator begins toggling again, the FLAG\_OSC and FLAG\_ERR are set to 1. The SPI controller can access the LP5899 and write 1 to CLR\_FLAG to clear the flags.

#### 7.3.4.3 SPI Communications Loss

The LP5899 monitors the SPI for communication with an internal watchdog timer. The device expects to receive a valid SPI command within the communications loss interval. The timer starts counting when the device enters the Normal state. The timer resets when a valid SPI command is detected. When the watchdog timer overflows, device automatically switches to Failsafe state and sets the DEV\_STATE to 0x3 and FLAG\_ERR is set to 1. The SPI controller can access the LP5899 and write 1 to EXIT\_FS in register DEVCTRL to set the device to Normal state again when the communication recovers. The watchdog timer is programmable by 2-bit field SPI\_WDT\_CFG in register SPICTRL. Disabling the watchdog timer by setting SPI\_WDT\_CFG to 0x3 prevents the device from automatically entering into Failsafe state.

#### 7.3.4.4 SPI Communications Error

#### 7.3.4.4.1 Reset Timer

The LP5899 monitors the SPI for communication with an internal SPI reset timer. Once an SPI command is started, the timer starts and the device expects the full command (including reading of data) is completed before the timer overflows. The timer starts counting from the first clock pulse on the SCLK pin (with CS pin at active state) when the device is trying to detect the SPI command word. The timer is reset when the device starts to wait for the next SPI command word. If the watchdog timer overflows, the SPI peripheral is reset and starts to wait to receive the next SPI command word. In addition, the FLAG\_SPI\_TIMEOUT, FLAG\_SPI, and FLAG\_ERR are set to 1. The SPI controller can access the LP5899 and write 1 to CLR\_FLAG to clear the flags. The SPI reset timer is programmable by 4-bit field SPI\_RST\_TIMEOUT\_CFG in register SPICTRL. TI recommends to enable this timer when the CS pin is always tied to the active state.

#### 7.3.4.4.2 Chip Select (CS) Reset

The SPI peripheral is reset by pulling the CS pin to logic HIGH. This is normally done when the whole SPI command has been completed and the SPI peripheral is waiting for the next command. In case the CS pin is pulled high after the SPI peripheral has received the SPI command word, but before the whole command is received, the FLAG\_SPI\_CS, FLAG\_SPI, and FLAG\_ERR are set to 1. The SPI controller can access the LP5899 and write 1 to CLR\_FLAG to clear the flags.

#### 7.3.4.4.3 CRC Error

The CRC word is the final word of a command the SPI controller transmits to make sure the LP5899 correctly has received all the words from SPI controller. The SPI controller must calculate the CRC value for all words including SPI command word and any data words. The LP5899 receives all words, calculates the CRC word and compares the calculated CRC word with received CRC word. If two CRC words do not match, the LP5899 sets FLAG\_SPI\_CRC and FLAG\_ERR to 1. Dependent on the received command, the LP5899 ignores the command or continues processing the command. The SPI controller can access the device and write 1 to CLR\_FLAG to clear the flags. Two different CRC algorithms are supported. The default algorithm is CCITT-FALSE. This can be changed to the CRC-16/XMODEM algorithm using the REG\_WR SPI command. After changing the CRC algorithm, the next SPI command uses the new algorithm.

#### 7.3.4.4.4 Register write failure

The CCSICTRL register is prohibted to be written while the CCSI controller is transmitting or CCSI peripheral is receiving. In that way the continuous clock output on CLK\_O remains aligned with the data being transmitted on SOUT and received on SIN. When the user tries to write the CCSICTRL register during CCSI controller and/or peripheral activity, the device automatically detects this and sets FLAG\_SPI\_REG\_WRITE to 1. The SPI controller can access the device and write 1 to CLR\_FLAG to clear the flag.

#### 7.3.4.5 CCSI Communications Loss

#### 7.3.4.5.1 SIN Stuck-at Diagnostics

The data input (SIN) pin of the CCSI peripheral is monitored. After the CCSI controller starts transmitting (logic high to low transition on SOUT pin), the timer starts counting. If no toggling has been detected on the SIN pin before the timer overflows (after 5 milliseconds), the FLAG\_CCSI\_SIN, FLAG\_CCSI, and FLAG\_ERR are set to 1. The SPI controller can access the LP5899 and write 1 to CLR\_FLAG to clear the flags.

When the FLAG\_CCSI\_SIN is set, the CCSI controller and CCSI peripheral are likely to get out of synchronization. Therefore, TI recommends to perform a SOFTRESET command after this flag has been set.

#### 7.3.4.6 CCSI Communications Error

The CCSI peripheral diagnoses the received data. The check bit detection is checked on all received data while the data integrity is only checked for CCSI commands that did not add or modify data which was transmitted by the CCSI controller.

#### 7.3.4.6.1 CHECK Bit Error

The CHECK (17<sup>th</sup>) bit of each CCSI data byte must be the *NOT* of the 16<sup>th</sup> bit. When the CHECK bit is the same as the 16<sup>th</sup> bit, the FLAG\_CCSI\_CHECK\_BIT, FLAG\_CCSI, and FLAG\_ERR are set to 1. The SPI controller can access the LP5899 and write 1 to CLR\_FLAG to clear the flags. The CCSI peripheral stops receiving the current CCSI command and waits until an END byte is received. Afterwards, the CCSI peripheral works normally independent of the status of the error flags.

#### 7.3.4.6.2 Data Integrity Diagnostics

Data that is transmitted by the CCSI controller which is not modified or extended within the daisy chain of LED drivers is protected by the LP5899 device with a CRC. Over all the transmitted words of the CCSI command a CRC value is calculated. Once the command is received by the CCSI peripheral, another CRC is calculated over all the received words. When the CRC over the transmitted words does not match the CRC over the received words, the FLAG\_CCSI\_CRC, FLAG\_CCSI, and FLAG\_ERR are set to 1. The SPI controller can access the LP5899 and write 1 to CLR\_FLAG to clear the flags.

When an SPI command starts with FWD (commands 0x2 to 0x7), the first data word of the SPI command is checked. When this word matches a write FC0 to FC15 (0xAA00 to 0xAA0F) or VSYNC (0xAAF0) CCSI command, the data integrity diagnostics is executed.

When this error flag is triggered consecutively, the CCSI controller and CCSI peripheral are likely out of synchronization. In that case, TI recommends to perform a SOFTRESET command.

#### 7.3.4.6.3 CCSI Command Queue Overflow

The LP5899 provides a detection when there are too many commands in the queue to be transmitted by the CCSI controller or expected to be received by the CCSI peripheral. When the command queue is full and a new CCSI command is received by the SPI peripheral, the FLAG\_CCSI\_CMD\_QUEUE\_OVF, FLAG\_CCSI, and FLAG\_ERR are set to 1. In addition, the CCSI command queue and TXFIFO are cleared in the same way as TXFFCLR. The SPI controller can access the LP5899 and write 1 to CLR\_FLAG to clear the flags. The error flag has to be cleared to be able to store new CCSI commands and the CCSI controller can start transmitting.

When the FLAG\_CCSI\_CMD\_QUEUE\_OVF is set, the CCSI controller and CCSI peripheral are likely to get out of synchronization. Therefore, TI recommends to perform a SOFTRESET command after this flag has been set.

#### 7.3.4.7 FIFO Diagnostics

Both the TXFIFO and RXFIFO have their own overflow and underflow diagnostics. Below sections decribe these in more detail.

#### 7.3.4.7.1 TXFIFO Overflow

When the TXFIFO is full (TXFFST = 0x1FF) and new data words are received by the SPI peripheral which have to be stored in the TXFIFO, the FLAG\_TXFFOVF, FLAG\_TXFF, and FLAG\_ERR are set to 1. In addition, the TXFIFO is cleared in the same way as TXFFCLR. The SPI controller can access the LP5899 and write 1 to CLR\_FLAG to clear the flags. The error flag has to be cleared to be able to store new CCSI data words on the TXFIFO and the CCSI controller can start transmitting.

#### 7.3.4.7.2 TXFIFO Underflow

When the FIFO is empty (TXFFST = 0x0) and the CCSI controller tries to read a new word from the TXFIFO, the FLAG\_TXFFUVF, FLAG\_TXFF, and FLAG\_ERR are set to 1. The ongoing transmission by the CCSI controller is stopped. The SPI controller can access the LP5899 and write 1 to CLR\_FLAG to clear the flags. The error flag has to be cleared to be able to store new CCSI data words on the TXFIFO and the CCSI controller can start transmitting.

#### 7.3.4.7.3 TXFIFO Single Error Detection (SED)

The TXFIFO is protected with a parity bit. When a single bit error is detected during a read operation from the TXFIFO, the FLAG\_TXFFSED, FLAG\_TXFF, and FLAG\_ERR are set to 1. The ongoing transmission by the CCSI controller is stopped. However, the TXFIFO is not automatically cleared. The SPI controller can access the

LP5899 and write 1 to CLR\_FLAG to clear the flags. The error flag has to be cleared to be able to store new CCSI data words on the TXFIFO and the CCSI controller can start transmitting.

#### 7.3.4.7.4 RXFIFO Overflow

When the RXFIFO is full (RXFFST = 0x0FF) and new data words are received by the CCSI peripheral which have to be stored in the RXFIFO, the FLAG\_RXFFOVF, FLAG\_RXFF, and FLAG\_ERR are set to 1. The RXFIFO is not cleared and data can still be accessed by the SPI controller. The SPI controller can access the LP5899 and write 1 to CLR\_FLAG to clear the flags. The CCSI peripheral can only start storing new data in the RXFIFO after the error flag is cleared. The storage starts from the first CCSI head\_byte that is received from a FWD\_RD\_END\_CRC SPI command.

#### 7.3.4.7.5 RXFIFO Underflow

When the RXFIFO is empty (RXFFST = 0x0) and the SPI peripheral tries to read new data words from the RXFIFO, the FLAG\_RXFFUVF, FLAG\_RXFF, and FLAG\_ERR are set to 1. The SPI controller can access the LP5899 and write 1 to CLR\_FLAG to clear the flags. The CCSI peripheral can only start storing new data in the RXFIFO after the error flag is cleared. The storage starts from the first CCSI head\_byte that is received from a FWD\_RD\_END\_or FWD\_RD\_END\_CRC SPI command.

#### 7.3.4.7.6 RXFIFO Single Error Detection (SED)

The RXFIFO is protected with a parity bit. When a single bit error is detected during a read operation from the RXFIFO, the FLAG\_RXFFSED, FLAG\_RXFF, and FLAG\_ERR are set to 1. The SPI controller can access the LP5899 and write 1 to CLR\_FLAG to clear the flags.

#### 7.3.4.8 OTP CRC Error

The internal OTP is protected by an 8-bit CRC based on the polynomial  $X^8 + X^2 + X + 1$ . When the device powers up, the OTP is read and the read CRC is compared to the calculated CRC of all the read OTP bytes. When the CRC does not match, the FLAG\_OTP\_CRC and FLAG\_ERR are set to 1. This flag cannot be cleared by the SPI controller. The device remains in Initialization state. Only powering down and up VCC can restart the reading of the OTP.

#### 7.3.4.9 Fault Masking

The LP5899 provides fault masking capability using masking registers. The device is capable of masking faults by fault types. The fault masking does not disable diagnostics features but only prevents fault reporting to FLAG\_ERR register and FAULT output. The below table gives the detailed description for each fault mask register.

| Fault Detected       | Mask Bit                | Flag Name                                                | FAULT Pin            |

|----------------------|-------------------------|----------------------------------------------------------|----------------------|

| SPI CRC error        | MASK_SPI_CRC = 1        | FLAG_SPI_CRC = 1<br>FLAG_ERR = 0                         | No action            |

|                      | MASK_SPI_CRC = 0        | FLAG_SPI_CRC = 1<br>FLAG_ERR = 1                         | Constant pulled down |

| SIN stuck error      | MASK_CCSI_SIN = 1       | FLAG_CCSI_SIN = 1<br>FLAG_CCSI = 1<br>FLAG_ERR = 0       | No action            |

|                      | MASK_CCSI_SIN = 0       | FLAG_CCSI_CC = 1<br>FLAG_CCSI = 1<br>FLAG_ERR = 1        | Constant pulled down |

| CCSI CHECK bit error | MASK_CCSI_CHECK_BIT = 1 | FLAG_CCSI_CHECK_BIT = 1<br>FLAG_CCSI = 1<br>FLAG_ERR = 0 | No action            |

|                      | MASK_CCSI_CHECK_BIT = 0 | FLAG_CCSI_CHECK_BIT = 1<br>FLAG_CCSI = 1<br>FLAG_ERR = 1 | Constant pulled down |

| CCSI CRC error       | MASK_CCSI_CRC = 1       | FLAG_CCSI_CRC = 1<br>FLAG_CCSI = 1<br>FLAG_ERR = 0       | No action            |

|                      | MASK_CCSI_CRC = 0       | FLAG_CCSI_CRC = 1<br>FLAG_CCSI = 1<br>FLAG_ERR = 1       | Constant pulled down |

#### 7.3.4.10 Diagnostics Table

Table 7-1. Diagnostics Table

| FAULT TYPE                     | DETECTION CRITERIA                                                                                       | CONDITIONS                                                       | FAULT ACTIONS                                                      | FAULT OUTPUT                                            | FAULT PIN                          |

|--------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------|------------------------------------|

| VCC UVLO                       | V <sub>CC</sub> < V <sub>UVF</sub>                                                                       |                                                                  | Device switch to<br>Unpowered state                                | FLAG_POR<br>FLAG_ERR                                    | Constant pulled down               |

| Oscillator error               | t <sub>WD,OSC</sub> overflows                                                                            |                                                                  | No action                                                          | FLAG_OSC<br>FLAG_ERR                                    | Constant pulled down               |

| SPI communication loss fault   | t <sub>SPI_WDT</sub> overflows                                                                           |                                                                  | Device enters<br>FAILSAFE state                                    | DEV_STATE = FAILSAFE<br>FLAG_ERR                        | Constant pulled down               |

| SPI command<br>timeout fault   | t <sub>SPI_RST_TIMEOUT</sub> overflows                                                                   |                                                                  | Reset SPI logic                                                    | FLAG_SPI_TIMEOUT<br>FLAG_SPI<br>FLAG_ERR                | Constant pulled down               |

| SPI Chip Select<br>(CS) fault  | CS pin is pulled high in middle of SPI<br>command                                                        |                                                                  | Reset SPI logic                                                    | FLAG_SPI_CS<br>FLAG_SPI<br>FLAG_ERR                     | Constant pulled down               |

| SPI CRC error                  | Calculated CRC is different than received CRC                                                            |                                                                  | No action                                                          | FLAG_SPI_CRC<br>FLAG_ERR (maskable)                     | Constant pulled<br>down (maskable) |

| Register write failure         | CCSICTRL is written during CCSI controller/peripheral activity                                           |                                                                  | No action                                                          | FLAG_SPI_REG_WRITE                                      | No action                          |

| SIN stuck error                | t <sub>WD,SIN</sub> overflows                                                                            |                                                                  | No action                                                          | FLAG_CCSI_SIN<br>FLAG_CCSI<br>FLAG_ERR (maskable)       | Constant pulled<br>down (maskable) |

| CCSI CHECK bit<br>error        | CHECK bit is not the inverted of the 16 <sup>th</sup> bit value                                          |                                                                  | No action                                                          | FLAG_CCSI_CHECK_BIT<br>FLAG_CCSI<br>FLAG_ERR (maskable) | Constant pulled<br>down (maskable) |

| CCSI CRC error                 | CCSI SOUT Head_bytes and<br>Data_bytes_N result in a different CRC<br>value than what is received on SIN | Head_bytes = VSYNC (0xAAF0)<br>or<br>write FCx (0xAA00 - 0xAA0F) | No action                                                          | FLAG_CCSI_CRC<br>FLAG_CCSI<br>FLAG_ERR (maskable)       | Constant pulled<br>down (maskable) |

| CCSI Command<br>Queue overflow | Command queue is full<br>and<br>SPI receives new CCSI command                                            |                                                                  | CCSI controller<br>stops (if ongoing)<br>and TXFFST is set<br>to 0 | FLAG_CCSI_CMD_QUEUE_OVF<br>FLAG_CCSI<br>FLAG_ERR        | Constant pulled<br>down            |

| TXFIFO overflow                | TXFFST = 511<br>and<br>SPI data word needs to be stored                                                  | SPI command type starts with FWD                                 | CCSI controller<br>stops (if ongoing)<br>and TXFFST is set<br>to 0 | FLAG_TXFFOVF<br>FLAG_TXFF<br>FLAG_ERR                   | Constant pulled down               |

| TXFIFO underflow               | TXFFST = 0<br>and<br>CCSI controller requests a new word for<br>transmission                             |                                                                  | CCSI controller<br>stops                                           | FLAG_TXFFUVF<br>FLAG_TXFF<br>FLAG_ERR                   | Constant pulled<br>down            |

|                               |                                                                                 | Table 7-1. Diagnostics Table (co          | ,                                                        |                                       |                      |

|-------------------------------|---------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------|---------------------------------------|----------------------|

| FAULT TYPE                    | DETECTION CRITERIA                                                              | CONDITIONS                                | FAULT ACTIONS                                            | FAULT OUTPUT                          | FAULT PIN            |

| TXFIFO single error detection | CCSI controller requests a new word for<br>transmission and TXFIFO parity error |                                           | CCSI controller<br>stops                                 | FLAG_TXFFSED<br>FLAG_TXFF<br>FLAG_ERR | Constant pulled down |

| RXFIFO overflow               | RXFFST = 255<br>and<br>CCSI data word needs to be stored                        |                                           | CCSI peripheral<br>does not store any<br>words in RXFIFO | FLAG_RXFFOVF<br>FLAG_RXFF<br>FLAG_ERR | Constant pulled down |

| RXFIFO underflow              | RXFFST = 0<br>and<br>SPI peripheral requests a new word for<br>transmission     | SPI command type starts with<br>DATA_READ | CCSI peripheral<br>does not store any<br>words in RXFIFO | FLAG_RXFFUVF<br>FLAG_RXFF<br>FLAG_ERR | Constant pulled down |

| RXFIFO single error detection | SPI peripheral requests a new word for<br>transmission and RXFIFO parity error  | SPI command type starts with<br>DATA_READ | No action                                                | FLAG_RXFFSED<br>FLAG_RXFF<br>FLAG_ERR | Constant pulled down |

| OTP CRC error                 | CALC_OTPCRC is different OTPCRC                                                 |                                           | No action                                                | FLAG_OTP_CRC<br>FLAG_ERR              | Constant pulled down |

### Table 7-1. Diagnostics Table (continued)

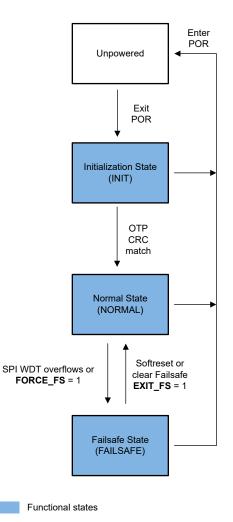

### 7.4 Device Functional Modes

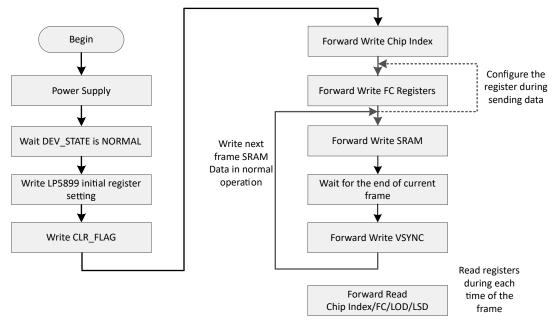

Figure 7-8. Device Functional Modes

### 7.4.1 Unpowered

As long as VCC is below the UVLO threshold, the device is kept in POR. All registers are kept in the reset state. If VCC falls below UVLO threshold in other states, the device immediately is kept in POR.

### 7.4.2 Initialization State

After VCC is above the UVLO threshold, the device enters initialization state. In this state the SPI peripheral is enabled, but the maximum supported frequency is lower than in Normal state. The continuous clock of the CCSI controller is enabled, but transmission can only start in Normal State. Also, the OTP is read and the read CRC is compared to the calculated CRC of all the read OTP bytes. If the CRC matches, the OTP registers are updated and the device enters Normal State.

#### 7.4.3 Normal State

To enable the transmission by the CCSI controller, the FLAG\_POR needs to be cleared. If the communications watchdog timer is enabled, and then expires due to a lack of communication, the device enters Failsafe state. The device can be also forced into Failsafe state anytime in Normal state by setting bit FORCE\_FS in register DEVCTRL to 1. The FORCE\_FS bit automatically returns to 0.

#### 7.4.4 Failsafe State

When the device enters the Failsafe state, the TXFFCLR bit is set to stop any ongoing CCSI transmission.

The SPI peripheral is first reset when entering the Failsafe state. Afterwards, the SPI peripheral is kept alive to allow communication to the device. However, there is no control over the CCSI controller and CCSI peripheral. This means that when the SPI command starts with FWD, the data is ignored and not stored in the TXFIFO.

The device can quit from Failsafe to Normal state by setting bit EXIT\_FS in register DEVCTRL to 1. The EXIT\_FS bit automatically returns to 0. Another method to bring the device to Normal state is by sending the SOFTRESET\_CRC SPI command.

### 7.5 Programming

The LP5899 has a serial peripheral interface (SPI) peripheral which is a high-speed synchronous serial input and output (I/O) port that allows a serial bit stream of 16 bits length to be shifted into and out of the device based on the externally provided clock rate. The bit stream shifted into the device provides access to the programmable functions and registers. The interface consists of 4 wires:

- Serial Data In (SDI)

- Serial Data Out (SDO)

- Serial Clock (SCLK)

- Chip Select (CS)

#### 7.5.1 SPI Data Validity

The data on SDI wire must be stable at the rising edge of the SCLK wire. The data on SDO shifts out at the falling edge of the SCLK wire. SDO can be forced to be disabled by the bit SPI\_SDO\_DIS in the SPICTRL register. This is useful when the same command is broadcasted to multiple LP5899 devices on a single SPI bus. When no data is shifted into the device, the SCLK wire is expected to be logic LOW.

#### 7.5.2 Chip Select (CS) and SPI Reset Control

The CS signal provides the ability to gate any spurious clock and data pulses. A HIGH logic signal on CS blocks the peripheral to receive data. This prevents the SPI peripheral from losing synchronization with the controller. TI does not recommend that the CS always be tied to the active state.

If the SPI peripheral does ever lose synchronization with the controller, providing a HIGH logic signal on CS resets SPI peripheral including the bit counter. Another method is to stop the SCLK and wait longer than the setting of the field SPI\_RST\_TIMEOUT\_CFG in the SPICTRL register. This timeout starts counting from the first rising clock edge of SCLK when the SPI peripheral is expecting the command word.

#### 7.5.3 SPI Command Format

Figure 7-9 and Table 7-2 define the format of the SPI command transmission. Each SPI command contains multiple 16-bit words. The different types of words are:

- **Command word:** The command word always includes an identifier of the command type. Dependent on the type, the command word also includes:

- Start address to be written or read. When field address = 0 means address 0x00.

- Length of the data that is transmitted or expected to be read. When the length field starts with opt, the data is optional. Therefore, opt\_data\_length = 0 means 0 data words. For fields that do not start with opt, data\_length = 0 means 1 data word.

- Number of extra END bytes to append when forwarding data. When field extra\_end\_bytes = 0 means 0 additional END bytes. A maximum of 127 extra END bytes can be appended with one SPI command.

Fixed data (in case of SOFTRESET\_CRC command)

- Fixed data (in case of SOF I RESEI\_CRC command)

- **Data word:** Dependent of the command type this is data that needs to be forwarded (0 to N), register data that is written to (0 to N) or read from (N+1 to M) the device, or data read from (N+1 to M) the RXFIFO.

- **CRC word:** There are 2 different CRC words in each command:

- CRC word that is generated by the SPI controller. This CRC is calculated over the SPI command word and all transmitted data words (0 to N)

- CRC word that is generated by the SPI peripheral. This CRC is calculated over all the returned data words (N+1 to M).

Two different CRC algorithms are supported. The default algorithm is CCITT-FALSE. This can be changed to the CRC-16/XMODEM algorithm using the REG\_WR command. After changing the CRC algorithm, the next SPI command uses the new algorithm. Both algorithms are based on the polynomial  $X^{16} + X^{12} + X^{5} + 1$ .

| SCLK |              |             |   |             |            |               | <br>            |            |   |

|------|--------------|-------------|---|-------------|------------|---------------|-----------------|------------|---|

| SDI  |              |             |   |             |            |               |                 |            |   |

|      | Command word | Data word 0 | X | Data word N | CRC word 0 | Χ             |                 |            |   |

| SDO  |              |             |   |             |            |               | <br><b>_</b>    | ,          | _ |

| {    |              |             |   |             |            | Data word N+1 | <br>Data word M | CRC word 1 | - |

| CS   |              |             |   |             |            |               |                 | г          |   |

| L    |              |             |   |             |            |               |                 |            |   |

Figure 7-9. SPI Command Format

| Table 7-2. SPI Command Detail |            |       |                      |            |             |        |                          |                        |       |                  |        |                         |                         |                         |                                     |      |

|-------------------------------|------------|-------|----------------------|------------|-------------|--------|--------------------------|------------------------|-------|------------------|--------|-------------------------|-------------------------|-------------------------|-------------------------------------|------|

| Command Type                  |            |       |                      |            | Com         | mano   | d Woi                    | rd                     |       |                  |        |                         |                         |                         | Data words                          | CRC  |

|                               | CMD[15:12] | 11    | 10                   | 9          | 8           | 7      | 7 6 5 4 3 2 1 0          |                        |       |                  |        |                         |                         |                         |                                     | word |

| FWD_WR_CRC                    | 0x2        |       | 0x0                  |            |             |        |                          | data_                  | leng  | th[8:0           | ]      |                         |                         |                         | data word 0-data_length             | CRC  |

| FWD_WR                        | 0x3        |       |                      |            |             | dat    | a_len                    | igth[1                 | 1:0]  |                  |        |                         |                         |                         | data word 0-data_length             | CRC  |

| FWD_WR_END_CRC                | 0x4        | ор    | t_dat                | a_len      | gth[4       | :0]    |                          | ex                     | tra_e | end_b            | ytes[6 | 6:0]                    |                         |                         | data word 0-<br>(opt_data_length-1) | CRC  |

| FWD_WR_END                    | 0x5        | ор    | opt_data_length[4:0] |            |             |        |                          | extra_end_bytes[6:0]   |       |                  |        |                         |                         |                         | data word 0-<br>(opt_data_length-1) | CRC  |

| FWD_RD_END_CRC                | 0x6        |       | data_                | lengt      | h[4:0       | ]      |                          | extra_end_bytes[6:0]   |       |                  |        |                         |                         | data word 0-data_length | CRC                                 |      |

| FWD_RD_END                    | 0x7        | (     | data_                | lengt      | h[4:0       | ]      | extra_end_bytes[6:0]     |                        |       |                  |        | 6:0]                    |                         | data word 0-data_length | CRC                                 |      |

| DATA_RD_CRC                   | 0x8        |       | 0>                   | <b>(</b> 0 |             |        |                          | data_length[7:0]       |       |                  |        |                         |                         |                         | N/A                                 | CRC  |

| DATA_RD                       | 0x9        |       | 0>                   | <b>(</b> 0 |             |        |                          | da                     | ta_le | ength[7          | 7:0]   |                         |                         |                         | N/A                                 | CRC  |

| REG_WR_CRC                    | 0xA        | 0>    | <b>(</b> 0           | a          | addre       | ss[3:0 | )]                       | ] 0x0 data_length[3:0] |       | data_length[3:0] |        | data word 0-data_length | CRC                     |                         |                                     |      |

| REG_WR                        | 0xB        | 0>    | <b>(</b> 0           | a          | addre       | ss[3:0 | )]                       | 0                      | x0    | data_length[3:0] |        | 0]                      | data word 0-data_length | CRC                     |                                     |      |

| REG_RD_CRC                    | 0xC        | 0>    | <b>(</b> 0           | a          | address[3:0 |        |                          | 0                      | x0    | da               | ta_le  | ngth                    | [3:                     | 0]                      | N/A                                 | CRC  |

| REG_RD                        | 0xD        | 0>    | (0                   | a          | addre       | ss[3:0 | :0] 0x0 data_length[3:0] |                        |       | 0]               | N/A    | CRC                     |                         |                         |                                     |      |

| SOFTRESET_CRC                 | 0xE        | 0x1E1 |                      |            |             |        |                          |                        |       | N/A              | CRC    |                         |                         |                         |                                     |      |

#### 7.5.4 SPI Command Detail

For each command except SOFTRESET\_CRC there are two versions. The version without CRC at the end of the type name is always executed even when the CRC value is incorrect. The version with CRC at the end of the type name is only executed when the CRC that is received matches the calculated CRC over the command word and data words.

The commands starting with FWD, forward the received data words by the CCSI controller. As long as the data length is larger than 0, the CCSI controller automatically inserts one start bit, the check bits, and one END byte. The SPI data words of one SPI command are therefore considered to be one CCSI command with 1 start bit before the first SPI data word, a check bit after every data word, and one END byte after the last SPI data word.

Commands starting with REG are used to write and read the register of the LP5899 device. The DATA\_RD commands return the data stored on the RXFIFO.

Commands starting with FWD, REG\_WR, and SOFTRESET\_CRC return the STATUS register and the CRC calculated over the STATUS register. This acknowledgement can be disabled by bit SPI\_ACK\_DIS in the SPICTRL register. Care has to be taken when executing SOFTRESET\_CRC while the acknowledgement is disabled. In this case, TI recommends to wait at least one SPI word before sending the next command.

Whenever the LP5899 device returns data to the controller on the SDO pin, the controller has to provide sufficient clock pulses on the SCLK pin to shift out the data. TI recommends to keep the SDI pin at logic HIGH while providing the clock pulses to shift out the data.

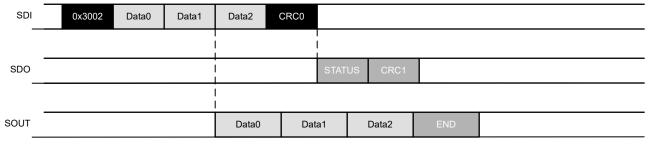

<u>FWD\_WR\_CRC (Forward Write CRC command)</u>

Return to the SPI Command Table

The FWD\_WR\_CRC command is used to transmit data words by the CCSI controller in the device. All the data words received by the SPI peripheral are stored on the TXFIFO. Only when the received CRC matches with the calculated CRC over the command word and data words, the CCSI controller starts to transmit. This means that the TXFFLVL does not impact the start of this transmission. Caution has to be taken by the SPI controller that the data length is less than the size of the TXFIFO. This SPI command supports up to 512 data words and returns the STATUS register and the CRC calculated over the STATUS register. An example of FWD\_WR\_CRC command forwarding 2 data words is depicted in Figure 7-10.

| SDI  | 0x2001 | Data0 | Data1 | CRC0 |        |      |   |     |  |  |

|------|--------|-------|-------|------|--------|------|---|-----|--|--|

|      |        |       |       |      |        |      |   |     |  |  |

| SDO  |        |       |       |      | STATUS | CRC1 |   |     |  |  |

|      |        |       |       |      |        |      |   |     |  |  |

| SOUT |        |       |       |      | Data0  | Data | 1 | END |  |  |

Figure 7-10. Example of FWD\_WR\_CRC command

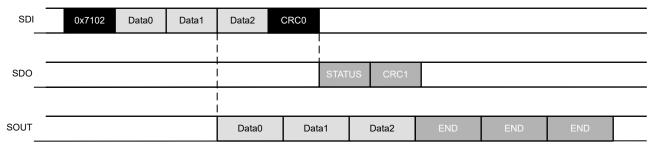

#### FWD\_WR (Forward Write command)

#### Return to the SPI Command Table

The FWD\_WR command is used to transmit data words by the CCSI controller in the device. All the data words received by the SPI peripheral are stored on the TXFIFO. If one or more of the following conditions is met, the CCSI controller starts transmitting.

- The number of words stored on the TXFIFO reach TXFFLVL

- All the data words of the SPI command have been received

This means that the CRC does not impact the start of this transmission. When the received CRC does not match the calculated CRC over the command word and data words, the FAULT pin is pulled low (when not masked) and the flag FLAG\_SPI\_CRC is set. This SPI command supports up to 4096 data words and returns the STATUS register and the CRC calculated over the STATUS register. An example of FWD\_WR command forwarding 3 words with TXFFLVL set to 2 data words is depicted in Figure 7-11.

Figure 7-11. Example of FWD\_WR command

#### FWD\_WR\_END\_CRC (Forward Write CRC with END bytes command)

#### Return to the SPI Command Table

The FWD\_WR\_END\_CRC command is used to transmit data words by the CCSI controller in the device. All the data words received by the SPI peripheral are stored on the TXFIFO. Only when the received CRC matches with the calculated CRC over the command word and data words, the CCSI controller starts to transmit. This means that the TXFFLVL does not impact the start of this transmission. After all the data words have been transmitted by the CCSI controller, the specified number of extra END bytes are appended. The transmission of data words and the transmission of the extra END bytes are considered as 2 separate CCSI commands. This SPI command supports up to 31 data words and returns the STATUS register and the CRC calculated over the STATUS register. An example of FWD\_WR\_END\_CRC command forwarding 0 data words (and therefore does not insert one END byte) and 3 extra END bytes is depicted in Figure 7-12.

| SDI  | 0x4003 | CRC0 |        |      |     |  |

|------|--------|------|--------|------|-----|--|

|      |        |      |        |      |     |  |

| SDO  |        |      | STATUS | CRC1 |     |  |

|      |        |      |        |      |     |  |

| SOUT |        |      | END    | END  | END |  |

Figure 7-12. Example of FWD\_WR\_END\_CRC command

#### FWD\_WR\_END (Forward Write with END bytes command)

#### Return to the SPI Command Table

The FWD\_WR\_END command is used to transmit data words by the CCSI controller in the device. All the data words received by the SPI peripheral are stored on the TXFIFO. If one or more of the following conditions is met, the CCSI controller starts transmitting.

- The number of words stored on the TXFIFO reach TXFFLVL

- All the data words of the SPI command have been received

This means that the CRC does not impact the start of this transmission. When the received CRC does not match the calculated CRC over the command word and data words, the FAULT pin is pulled low (when not masked) and the flag FLAG\_SPI\_CRC is set. After all the data words have been transmitted by the CCSI controller, the specified number of extra END bytes are appended. The transmission of data words and the transmission of the extra END bytes are considered as 2 separate CCSI commands. This SPI command supports up to 31 data words and returns the STATUS register and the CRC calculated over the STATUS register. An example of FWD\_WR\_END command forwarding 2 data words and 1 extra END bytes is depicted in Figure 7-13. Note that in this example the TXFFLVL is set to 2 words or higher.

|  | 0x5101 | Data0  | Data1        | CRC0               |      |        |            |             |             |

|--|--------|--------|--------------|--------------------|------|--------|------------|-------------|-------------|

|  |        |        |              |                    |      |        |            |             |             |

|  |        |        | STATUS       | CRC                | 1    |        |            |             |             |

|  |        |        |              |                    |      |        |            |             |             |

|  |        |        |              | Data0              | Data | a1     | END        | END         |             |

|  |        | 0x5101 | 0x5101 Data0 | 0x5101 Data0 Data1 |      | STATUS | STATUS CRC | STATUS CRC1 | STATUS CRC1 |

Figure 7-13. Example of FWD\_WR\_END command

### FWD\_RD\_END\_CRC (Forward Read CRC with END bytes command)

#### Return to the SPI Command Table

The FWD\_RD\_END\_CRC command is used to transmit data words by the CCSI controller in the device. All the data words received by the SPI peripheral are stored on the TXFIFO. Only when the received CRC matches with the calculated CRC over the command word and data words, the CCSI controller starts to transmit. This means that the TXFFLVL does not impact the start of this transmission. After all the data words have been transmitted by the CCSI controller, the specified number of extra END bytes are appended. The transmission of data words and the transmission of the extra END bytes are considered as 2 separate CCSI commands. All the data words that are received by the CCSI peripheral for this command are stored on the RXFIFO. This SPI command supports up to 32 data words and returns the STATUS register and the CRC calculated over the STATUS register. An example of FWD\_RD\_END\_CRC command forwarding 2 data words and 1 extra END bytes is depicted in Figure 7-14.

| SDI  |  | 0x6081 | Data0 | Data1 | CRC0   |       |       |     |     |  |

|------|--|--------|-------|-------|--------|-------|-------|-----|-----|--|

|      |  |        |       |       |        |       |       |     |     |  |

| SDO  |  |        |       |       | STATUS | CRC1  |       |     |     |  |

|      |  |        |       |       |        | <br>  |       |     |     |  |

| SOUT |  |        |       |       |        | Data0 | Data1 | END | END |  |

#### FWD\_RD\_END (Forward Read with END bytes command)

#### Return to the SPI Command Table

The FWD\_RD\_END command is used to transmit data words by the CCSI controller in the device. All the data words received by the SPI peripheral are stored on the TXFIFO. If one or more of the following conditions is met, the CCSI controller starts transmitting.

- The number of words stored on the TXFIFO reach TXFFLVL

- All the data words of the SPI command have been received

This means that the CRC does not impact the start of this transmission. When the received CRC does not match the calculated CRC over the command word and data words, the FAULT pin is pulled low (when not masked) and the flag FLAG\_SPI\_CRC is set. After all the data words have been transmitted by the CCSI controller, the specified number of extra END bytes are appended. The transmission of data words and the transmission of the extra END bytes are considered as 2 separate CCSI commands. All the data words that are received by the CCSI peripheral for this command are stored on the RXFIFO. This SPI command supports up to 32 data words and returns the STATUS register and the CRC calculated over the STATUS register. An example of FWD\_RD\_END command forwarding 3 data words with TXFFLVL set to 2 data words and 2 extra END bytes is depicted in Figure 7-15.

Figure 7-15. Example of FWD\_RD\_END command

#### DATA\_RD\_CRC (Data Read CRC command)

#### Return to the SPI Command Table

The DATA\_RD\_CRC command is used to read data words from the RXFIFO. Only when the received CRC matches with the calculated CRC over the command word, the device returns the requested number of data words and the CRC calculated over the data words. When the CRC fails, the SDO is kept at logic HIGH. An example of DATA\_RD\_CRC command requesting 4 data words is depicted in Figure 7-16.

| SDI  | 0x8 | 8003 | CRC0 |       |       |       |       |      |  |

|------|-----|------|------|-------|-------|-------|-------|------|--|

|      |     |      |      |       |       |       |       |      |  |