# DLP650NE 0.65-Inch 1080p Digital Micromirror Device

### 1 Features

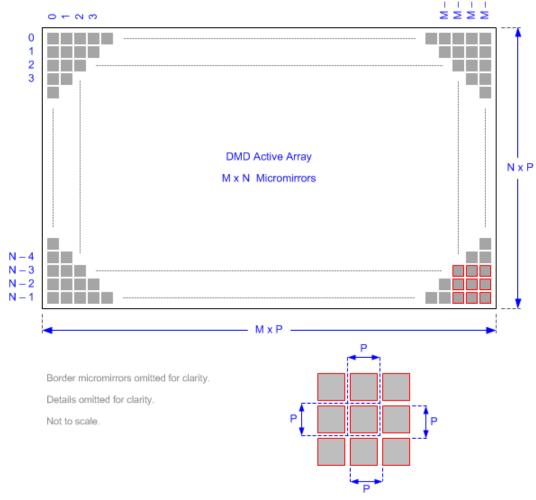

- 0.65-inch micromirror array diagonal

- 1080p (1920 × 1080)

- 7.56-micron micromirror pitch

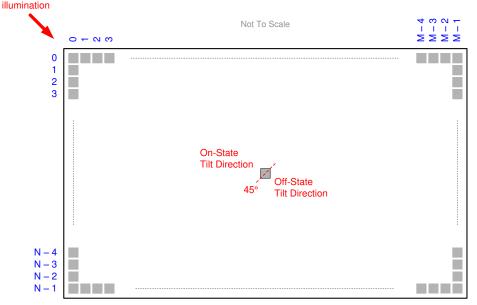

- ± 12° micromirror tilt angle (relative to flat state)

- Corner illumination

- 2xLVDS input data bus

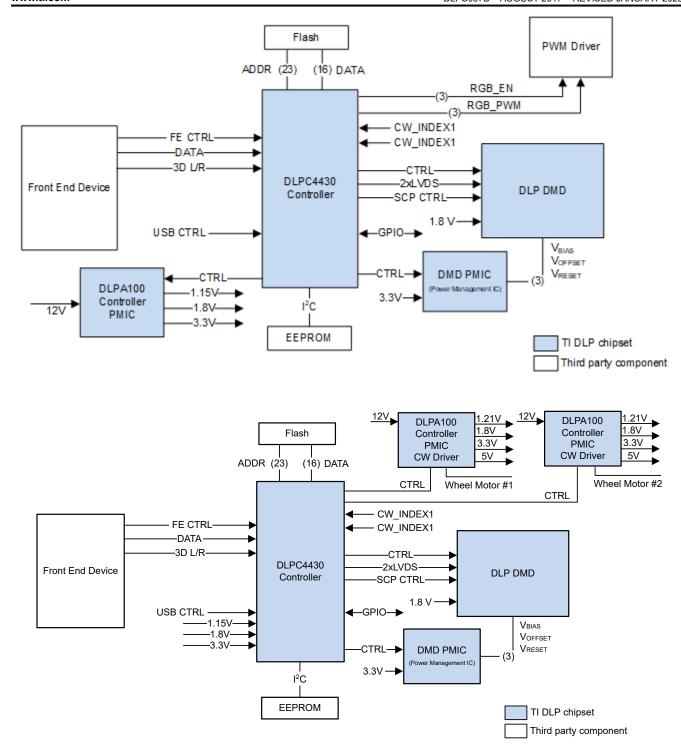

- The DLP650NE chipset includes:

- DLP650NE DMD

- DLPC4420 controller

- DLPA100 controller power management and motor driver IC

# 2 Applications

- Full HD (1080p) display

- Laser TV

- Mobile smart TV

- Digital signage

- Gaming

- Home cinema

# 3 Description

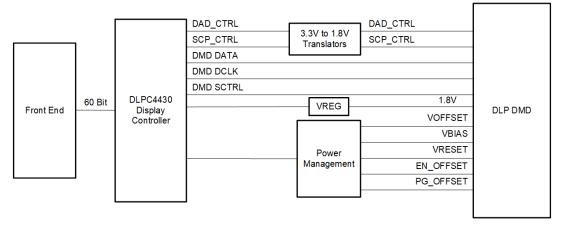

The TI DLP650NE digital micromirror device (DMD) is a digitally controlled micro-electromechanical system (MEMS) spatial light modulator (SLM) that enables bright, affordable DLP® 0.65-inch 1080p display solutions. The DLP650NE DMD-together with the DLPC4420 display controller and the DLPA100 power manager and motor driver—provides the capability to achieve high-performance systems, and is a great fit for display applications that require high resolution and 16:9 aspect ratio, high brightness, and system simplicity. The DLP650NE DMD can also utilize the DLPC4430 as a display controller.

The DMD ecosystem includes established resources to help the user accelerate the design cycle, visit the DLP® Products third-party search tools to find approved optical module manufacturers and third party providers.

Visit Getting Started With TI DLP Display Technology to learn more about how to start designing with the DMD.

#### **Device Information**

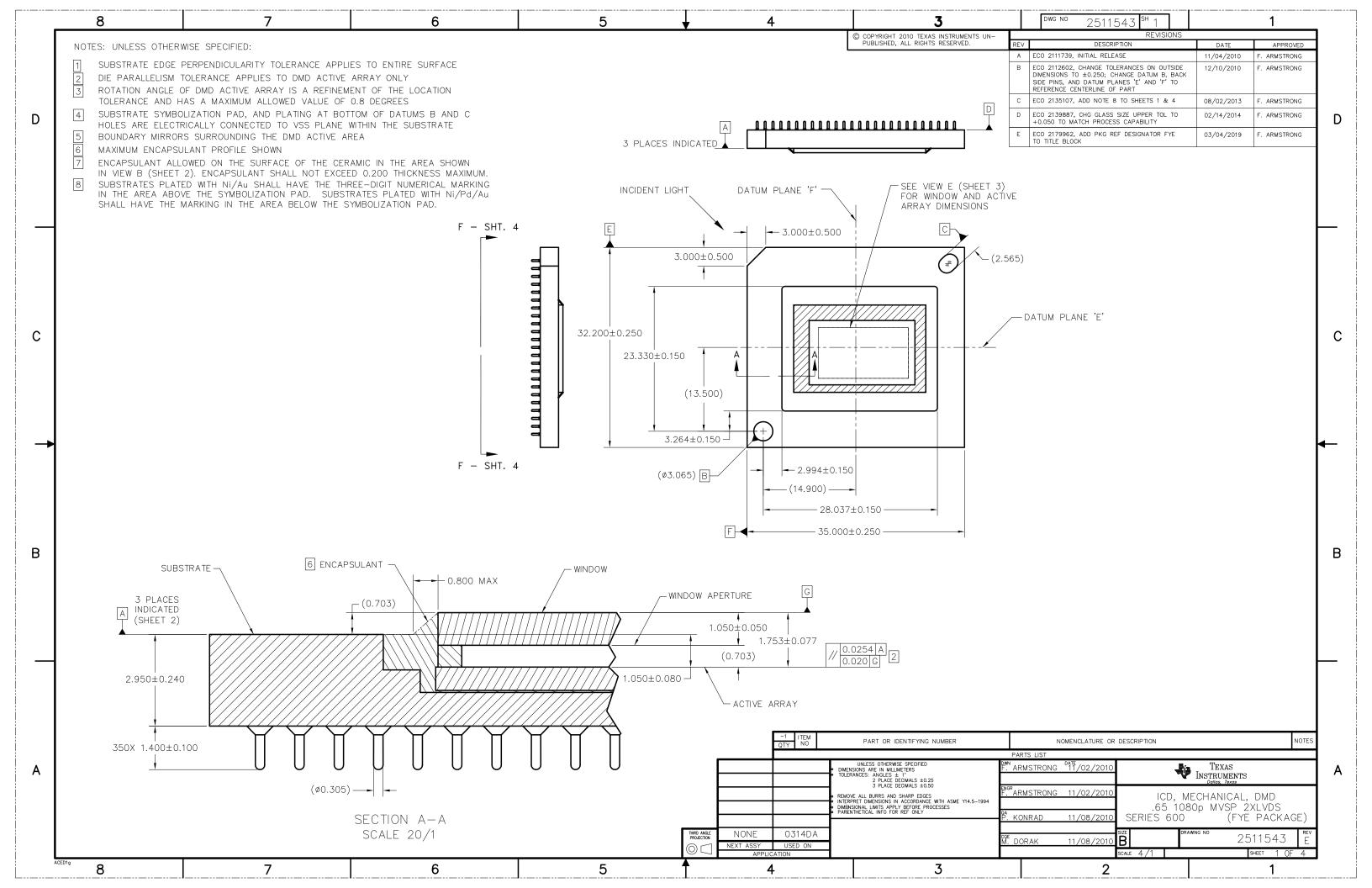

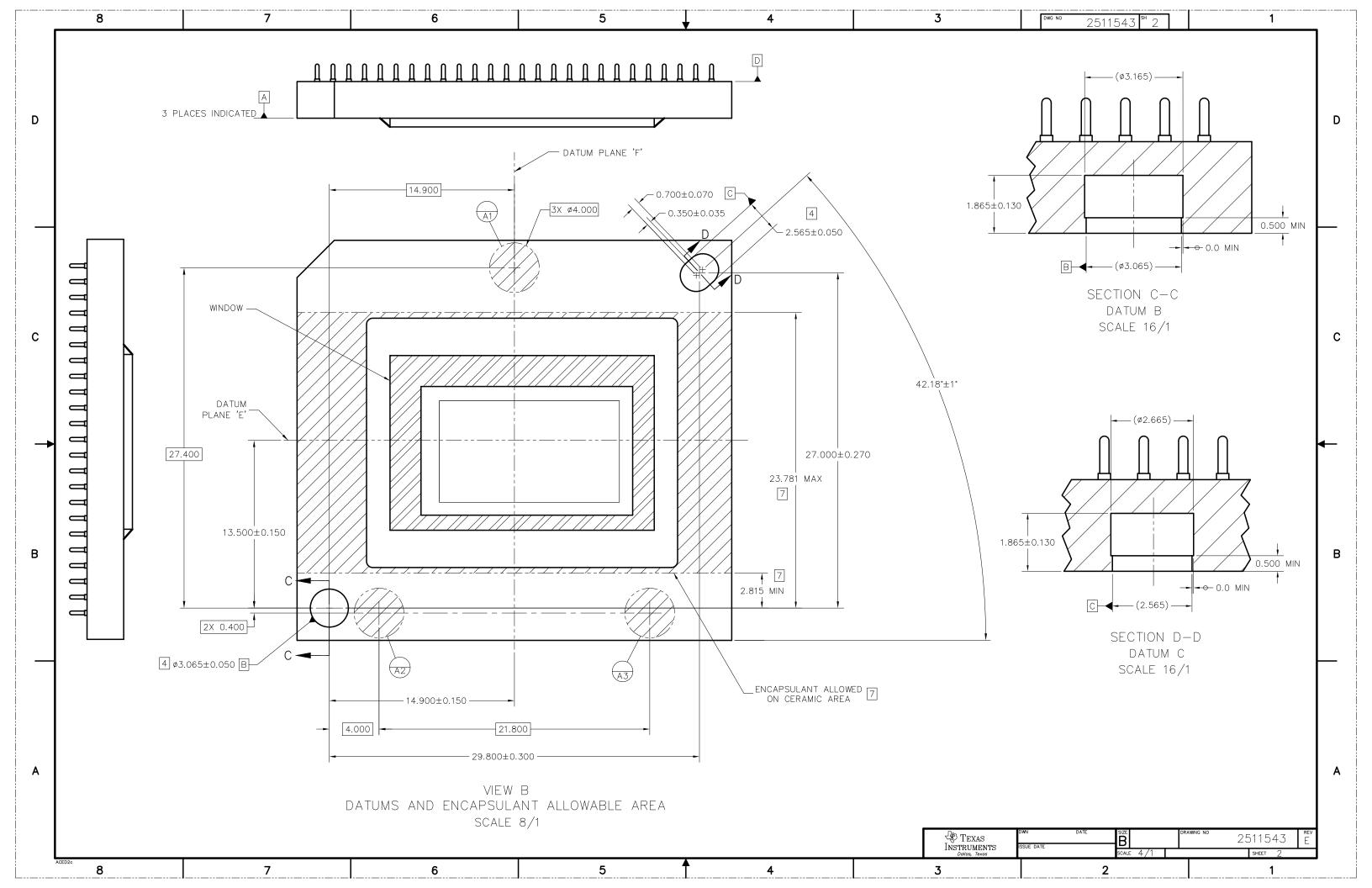

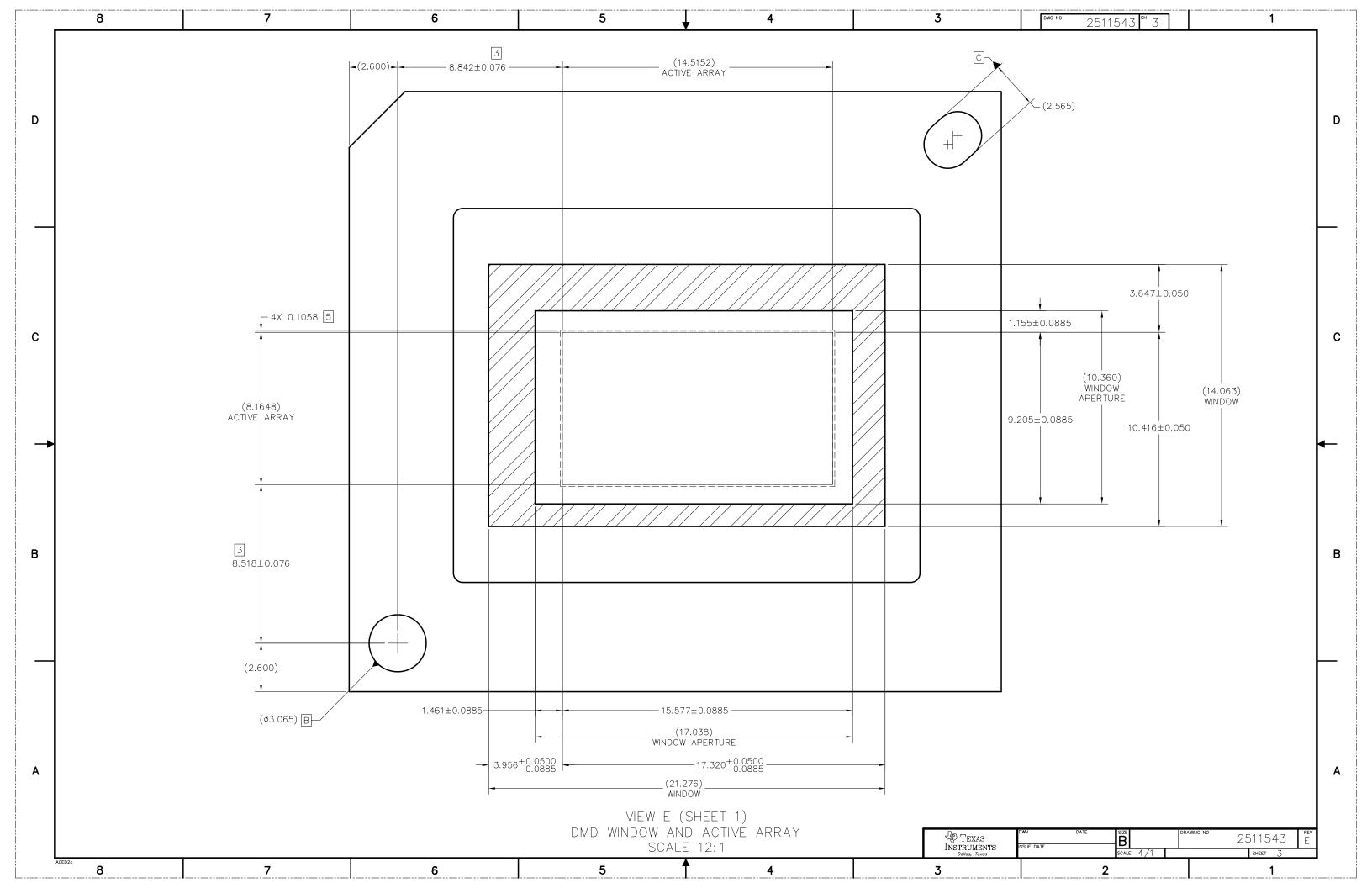

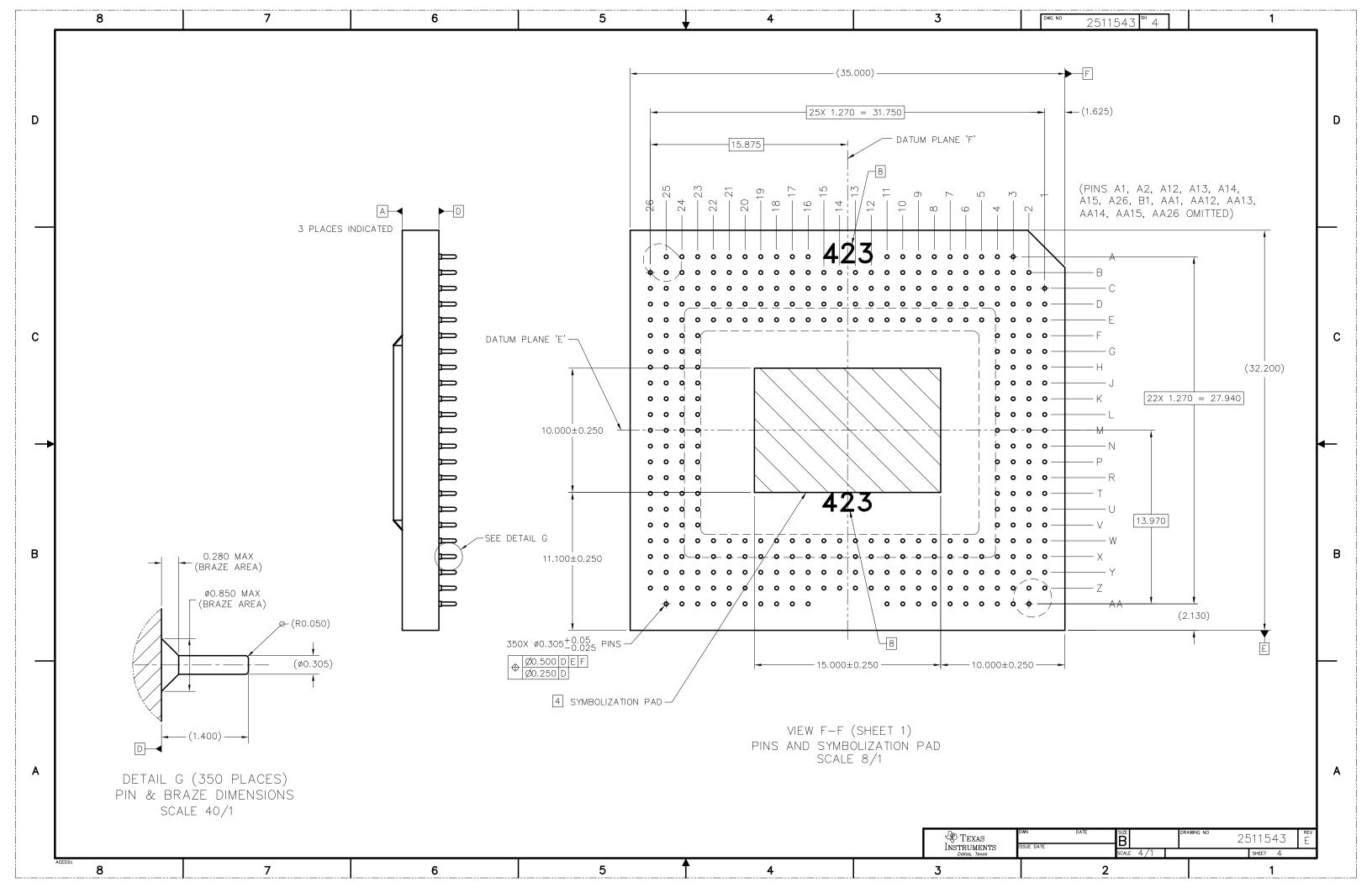

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE<br>SIZE         |

|-------------|------------------------|-------------------------|

| DLP650NE    | FYE (350)              | 35.0mm × 32.2mm × 5.1mm |

For more information, see the Mechanical, Packaging, and Orderable addendum.

**DLP650NE Simplified Application**

# **Table of Contents**

| 1 Features                                        | 6.5 Optica  |

|---------------------------------------------------|-------------|

| 2 Applications1                                   | Conside     |

| 3 Description1                                    | 6.6 Micror  |

| 4 Pin Configuration and Functions3                | 6.7 Micror  |

| 5 Specifications10                                | 6.8 Micror  |

| 5.1 Absolute Maximum Ratings10                    | 7 Power Su  |

| 5.2 Storage Conditions10                          | 7.1 DMD     |

| 5.3 ESD Ratings11                                 | 7.2 DMD     |

| 5.4 Recommended Operating Conditions11            | 7.3 DMD     |

| 5.5 Thermal Information13                         | 8 Device Do |

| 5.6 Electrical Characteristics14                  | 8.1 Third-  |

| 5.7 Timing Requirements15                         | 8.2 Device  |

| 5.8 Window Characteristics                        | 8.3 Docur   |

| 5.9 System Mounting Interface Loads19             | 8.4 Recei   |

| 5.10 Micromirror Array Physical Characteristics19 | 8.5 Suppo   |

| 5.11 Micromirror Array Optical Characteristics 21 | 8.6 Trade   |

| 5.12 Chipset Component Usage Specification 22     | 8.7 Electro |

| 6 Detailed Description23                          | 8.8 Gloss   |

| 6.1 Overview23                                    | 9 Revision  |

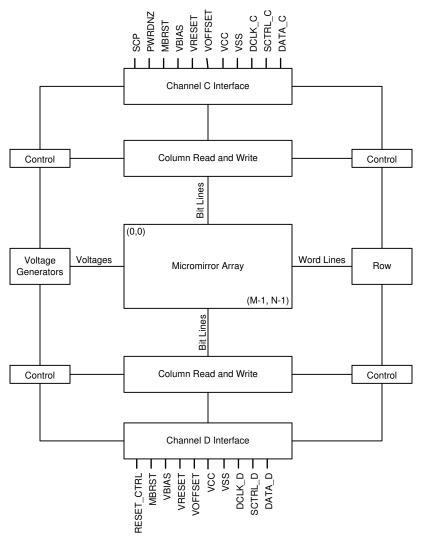

| 6.2 Functional Block Diagram23                    | 10 Mechani  |

| 6.3 Feature Description25                         | Informati   |

| 6.4 Device Functional Modes 25                    |             |

| 6.5 Optical Interface and System Image Quality      |      |

|-----------------------------------------------------|------|

| Considerations                                      | . 25 |

| 6.6 Micromirror Array Temperature Calculation       | . 26 |

| 6.7 Micromirror Power Density Calculation           | 27   |

| 6.8 Micromirror Landed-On or Landed-Off Duty Cycle  | . 29 |

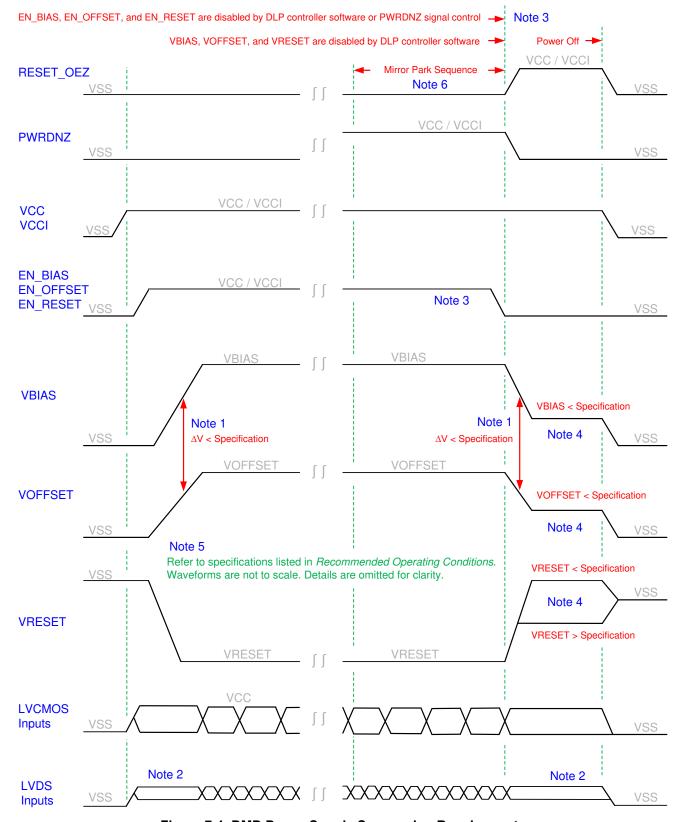

| 7 Power Supply Requirements                         | 35   |

| 7.1 DMD Power Supply Requirements                   | . 35 |

| 7.2 DMD Power Supply Power-Up Procedure             | .35  |

| 7.3 DMD Power Supply Power-Down Procedure           | . 35 |

| 8 Device Documentation Support                      |      |

| 8.1 Third-Party Products Disclaimer                 |      |

| 8.2 Device Support                                  |      |

| 8.3 Documentation Support                           |      |

| 8.4 Receiving Notification of Documentation Updates |      |

| 8.5 Support Resources                               | . 39 |

| 8.6 Trademarks                                      |      |

| 8.7 Electrostatic Discharge Caution                 | .39  |

| 8.8 Glossary                                        |      |

| 9 Revision History                                  |      |

| 10 Mechanical, Packaging, and Orderable             |      |

| Information                                         | . 40 |

|                                                     |      |

# 4 Pin Configuration and Functions

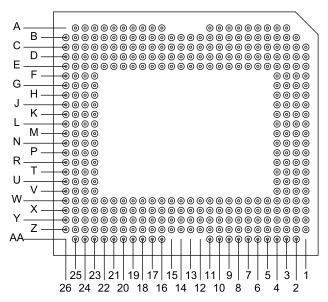

Figure 4-1. FYE Package 350-Pin Bottom View

**Table 4-1. Pin Functions**

| Table 4-1.1 III I dilctions |            |                     |        |                     |                                 |                |                             |  |  |  |  |

|-----------------------------|------------|---------------------|--------|---------------------|---------------------------------|----------------|-----------------------------|--|--|--|--|

| PIN <sup>(1)</sup>          |            | TYPE <sup>(5)</sup> | SIGNAL | DATA                | INTERNAL                        | DESCRIPTION    | TRACE (mils) <sup>(4)</sup> |  |  |  |  |

| NAME                        | NO.        |                     |        | RATE <sup>(2)</sup> | TERM <sup>(3)</sup> DESCRIPTION |                | ()                          |  |  |  |  |

|                             | DATA BUS A |                     |        |                     |                                 |                |                             |  |  |  |  |

| D_AN(0)                     | B14        | I                   |        | DDR                 | Differential                    | Data, negative | 494.88                      |  |  |  |  |

| D_AN(1)                     | B15        | I                   |        | DDR                 | Differential                    | Data, negative | 486.18                      |  |  |  |  |

| D_AN(2)                     | C16        | I                   |        | DDR                 | Differential                    | Data, negative | 495.16                      |  |  |  |  |

| D_AN(3)                     | K24        | I                   |        | DDR                 | Differential                    | Data, negative | 485.67                      |  |  |  |  |

| D_AN(4)                     | B18        | I                   |        | DDR                 | Differential                    | Data, negative | 494.76                      |  |  |  |  |

| D_AN(5)                     | L24        | ı                   |        | DDR                 | Differential                    | Data, negative | 490.63                      |  |  |  |  |

| D_AN(6)                     | C19        | I                   |        | DDR                 | Differential                    | Data, negative | 495.16                      |  |  |  |  |

| D_AN(7)                     | H24        | I                   | LVDS   | DDR                 | Differential                    | Data, negative | 485.55                      |  |  |  |  |

| D_AN(8)                     | H23        | I                   | LVDS   | DDR                 | Differential                    | Data, negative | 495.16                      |  |  |  |  |

| D_AN(9)                     | B25        | I                   |        | DDR                 | Differential                    | Data, negative | 485.59                      |  |  |  |  |

| D_AN(10)                    | D24        | I                   |        | DDR                 | Differential                    | Data, negative | 495.16                      |  |  |  |  |

| D_AN(11)                    | E25        | I                   |        | DDR                 | Differential                    | Data, negative | 495.16                      |  |  |  |  |

| D_AN(12)                    | F25        | I                   |        | DDR                 | Differential                    | Data, negative | 490.04                      |  |  |  |  |

| D_AN(13)                    | H25        | I                   |        | DDR                 | Differential                    | Data, negative | 485.91                      |  |  |  |  |

| D_AN(14)                    | L25        | I                   |        | DDR                 | Differential                    | Data, negative | 495.16                      |  |  |  |  |

| D_AN(15)                    | G24        | I                   |        | DDR                 | Differential                    | Data, negative | 495.16                      |  |  |  |  |

| PIN <sup>(1)</sup> |     | 14510 4             | DATA   | INTERNAL            |                     |                |                             |

|--------------------|-----|---------------------|--------|---------------------|---------------------|----------------|-----------------------------|

| NAME               | NO. | TYPE <sup>(5)</sup> | SIGNAL | RATE <sup>(2)</sup> | TERM <sup>(3)</sup> | DESCRIPTION    | TRACE (mils) <sup>(4)</sup> |

| D_AP(0)            | C14 | ı                   |        | DDR                 | Differential        | Data, positive | 494.84                      |

| D_AP(1)            | B16 | I                   |        | DDR                 | Differential        | Data, positive | 486.22                      |

| D_AP(2)            | C17 | I                   |        | DDR                 | Differential        | Data, positive | 494.65                      |

| D_AP(3)            | K23 | 1                   |        | DDR                 | Differential        | Data, positive | 488.42                      |

| D_AP(4)            | B19 | I                   |        | DDR                 | Differential        | Data, positive | 495.16                      |

| D_AP(5)            | L23 | I                   |        | DDR                 | Differential        | Data, positive | 490.67                      |

| D_AP(6)            | C20 | I                   |        | DDR                 | Differential        | Data, positive | 498.11                      |

| D_AP(7)            | J24 | I                   | 11/100 | DDR                 | Differential        | Data, positive | 486.22                      |

| D_AP(8)            | J23 | I                   | LVDS   | DDR                 | Differential        | Data, positive | 495.47                      |

| D_AP(9)            | C25 | I                   |        | DDR                 | Differential        | Data, positive | 485.94                      |

| D_AP(10)           | E24 | I                   |        | DDR                 | Differential        | Data, positive | 495.16                      |

| D_AP(11)           | D25 | I                   |        | DDR                 | Differential        | Data, positive | 494.13                      |

| D_AP(12)           | G25 | I                   |        | DDR                 | Differential        | Data, positive | 488.98                      |

| D_AP(13)           | J25 | I                   |        | DDR                 | Differential        | Data, positive | 492.56                      |

| D_AP(14)           | K25 | I                   |        | DDR                 | Differential        | Data, positive | 495.16                      |

| D_AP(15)           | F24 | I                   |        | DDR                 | Differential        | Data, positive | 495.16                      |

|                    | -   |                     |        | DATA                | A BUS B             |                |                             |

| D_BN(0)            | Z14 | I                   |        | DDR                 | Differential        | Data, negative | 494.92                      |

| D_BN(1)            | Z15 | I                   |        | DDR                 | Differential        | Data, negative | 486.18                      |

| D_BN(2)            | Y16 | I                   |        | DDR                 | Differential        | Data, negative | 496.46                      |

| D_BN(3)            | P24 | I                   |        | DDR                 | Differential        | Data, negative | 493.74                      |

| D_BN(4)            | Z18 | I                   |        | DDR                 | Differential        | Data, negative | 494.76                      |

| D_BN(5)            | N24 | ı                   |        | DDR                 | Differential        | Data, negative | 495.16                      |

| D_BN(6)            | Y19 | I                   |        | DDR                 | Differential        | Data, negative | 492.16                      |

| D_BN(7)            | T24 | I                   | LV/DC  | DDR                 | Differential        | Data, negative | 492.68                      |

| D_BN(8)            | T23 | I                   | LVDS   | DDR                 | Differential        | Data, negative | 484.45                      |

| D_BN(9)            | Z25 | I                   |        | DDR                 | Differential        | Data, negative | 492.09                      |

| D_BN(10)           | X24 | 1                   |        | DDR                 | Differential        | Data, negative | 497.72                      |

| D_BN(11)           | W25 | 1                   |        | DDR                 | Differential        | Data, negative | 495.16                      |

| D_BN(12)           | V25 | 1                   |        | DDR                 | Differential        | Data, negative | 484.17                      |

| D_BN(13)           | T25 | I                   |        | DDR                 | Differential        | Data, negative | 481.42                      |

| D_BN(14)           | N25 | I                   |        | DDR                 | Differential        | Data, negative | 495.16                      |

| D_BN(15)           | U24 | 1                   |        | DDR                 | Differential        | Data, negative | 489.8                       |

| PIN <sup>(1)</sup> DATA INTERNAL |          |   |        |                             |                                 |                                              |                             |

|----------------------------------|----------|---|--------|-----------------------------|---------------------------------|----------------------------------------------|-----------------------------|

|                                  | NAME NO. |   | SIGNAL | DATA<br>RATE <sup>(2)</sup> | INTERNAL<br>TERM <sup>(3)</sup> | DESCRIPTION                                  | TRACE (mils) <sup>(4)</sup> |

| D BP(0)                          | Y14      | ı |        | DDR                         | Differential                    | Data, positive                               | 494.88                      |

| D_BP(1)                          | Z16      | i |        | DDR                         | Differential                    | Data, positive                               | 486.26                      |

| D BP(2)                          | Y17      | ı |        | DDR                         | Differential                    | Data, positive                               | 495.16                      |

| D_BP(3)                          | P23      | ı |        | DDR                         | Differential                    | Data, positive                               | 492.48                      |

| D_BP(4)                          | Z19      | ı |        | DDR                         | Differential                    | Data, positive                               | 495.16                      |

| D_BP(5)                          | N23      | ı |        | DDR                         | Differential                    | Data, positive                               | 497.99                      |

| D_BP(6)                          | Y20      | ı |        | DDR                         | Differential                    | Data, positive                               | 495.16                      |

| D_BP(7)                          | R24      | ı |        | DDR                         | Differential                    | Data, positive                               | 492.05                      |

| D_BP(8)                          | R23      | ı | LVDS   | DDR                         | Differential                    | Data, positive                               | 484.45                      |

| D_BP(9)                          | Y25      | ı |        | DDR                         | Differential                    | Data, positive                               | 492.24                      |

| D_BP(10)                         | W24      | ı |        | DDR                         | Differential                    | Data, positive                               | 495.16                      |

| D_BP(11)                         | X25      | I |        | DDR                         | Differential                    | Data, positive                               | 494.72                      |

| D_BP(12)                         | U25      | I |        | DDR                         | Differential                    | Data, positive                               | 483.78                      |

| D_BP(13)                         | R25      | I |        | DDR                         | Differential                    | Data, positive                               | 489.13                      |

| D_BP(14)                         | P25      | I |        | DDR                         | Differential                    | Data, positive                               | 499.53                      |

| D_BP(15)                         | V24      | I |        | DDR                         | Differential                    | Data, positive                               | 488.66                      |

|                                  |          | 1 |        | SERIAL                      | CONTROL                         |                                              |                             |

| SCTRL_AN                         | C23      | I |        | DDR                         | Differential                    | Serial control, negative                     | 492.95                      |

| SCTRL_BN                         | Y23      | I | LV/DC  | DDR                         | Differential                    | Serial control, negative                     | 493.78                      |

| SCTRL_AP                         | C24      | I | LVDS   | DDR                         | Differential                    | Serial control, negative                     | 493.78                      |

| SCTRL_BP                         | Y24      | I |        | DDR                         | Differential                    | Serial control, negative                     | 493.11                      |

|                                  | '        |   |        | CL                          | оскѕ                            |                                              |                             |

| DCLK_AN                          | B23      | I |        |                             | Differential                    | Clock, negative                              | 480.35                      |

| DCLK_BN                          | Z23      | I | LVDS   |                             | Differential                    | Clock, negative                              | 486.22                      |

| DCLK_AP                          | B22      | I | LVDS   |                             | Differential                    | Clock, negative                              | 485.83                      |

| DCLK_BP                          | Z22      | ı |        |                             | Differential                    | Clock, negative                              | 491.93                      |

|                                  |          |   | SERIAL | COMMUNI                     | CATIONS PORT (                  | SCP)                                         |                             |

| SCP_DO                           | B8       | 0 |        | SDR                         |                                 | Serial communications port output            |                             |

| SCP_DI                           | B7       | I |        | SDR                         |                                 | Serial communication port data I             |                             |

| SCP_CLK                          | В6       | I | LVCMOS |                             | Pulldown                        | Serial communications port clock             |                             |

| SCP_ENZ                          | C8       | I |        |                             |                                 | Active-low serial communications port enable |                             |

| DIN(1)             | Table 4-1. Pin Functions (continued) |                     |                            |                     |                                 |                                                             |                 |  |

|--------------------|--------------------------------------|---------------------|----------------------------|---------------------|---------------------------------|-------------------------------------------------------------|-----------------|--|

| PIN <sup>(1)</sup> |                                      | TYPE <sup>(5)</sup> | TYPE <sup>(5)</sup> SIGNAL |                     | INTERNAL<br>TERM <sup>(3)</sup> | DESCRIPTION                                                 | TRACE (mils)(4) |  |

| NAME               | NO.                                  |                     |                            | RATE <sup>(2)</sup> |                                 |                                                             |                 |  |

|                    | 1                                    |                     | MICF                       | ROMIRROR            | RESET CONTRO                    | DL                                                          |                 |  |

| RESET_ADDR(0)      | Х9                                   | I                   |                            |                     |                                 | Reset driver address select                                 |                 |  |

| RESET_ADDR(1)      | X8                                   | 1                   |                            |                     |                                 | Reset driver address select                                 |                 |  |

| RESET_ADDR(2)      | Z8                                   | I                   |                            |                     |                                 | Reset driver address select                                 |                 |  |

| RESET_ADDR(3)      | <b>Z</b> 7                           | I                   | LVCMOS                     |                     | Pulldown                        | Reset driver address select                                 |                 |  |

| RESET_MODE(0)      | W11                                  | I                   | EVOIVIOO                   |                     | T undown                        | Reset driver mode select                                    |                 |  |

| RESET_MODE(1)      | Z10                                  | I                   |                            |                     |                                 | Reset driver mode select                                    |                 |  |

| RESET_SEL(0)       | Y10                                  | I                   |                            |                     |                                 | Reset driver level select                                   |                 |  |

| RESET_SEL(1)       | Y9                                   | I                   |                            |                     |                                 | Reset driver level select                                   |                 |  |

| RESET_STROBE       | Y7                                   | I                   |                            |                     |                                 | Reset address, mode,<br>and level latched on<br>rising-edge |                 |  |

|                    |                                      | Ш                   | EN                         | IABLES AN           | ID INTERRUPTS                   |                                                             |                 |  |

| PWRDNZ             | D2                                   | I                   |                            |                     | Pulldown                        | Active-low device reset                                     |                 |  |

| RESET_OEZ          | W7                                   | I                   |                            |                     | Pulldown                        | Active-low output enable for DMD reset driver circuits      |                 |  |

| RESETZ             | Z6                                   | I                   | LVCMOS                     |                     | Pulldown                        | Active-low sets reset circuits in known VOFFSET state       |                 |  |

| RESET_IRQZ         | Z5                                   | 0                   |                            |                     |                                 | Active-low, output interrupt to ASIC                        |                 |  |

|                    |                                      |                     | VOLTA                      | GE REGUL            | ATOR MONITOR                    | RING                                                        |                 |  |

| PG_BIAS            | E11                                  | I                   |                            |                     |                                 | Active-low fault from external VBIAS regulator              |                 |  |

| PG_OFFSET          | B10                                  | I                   |                            |                     | Pullup                          | Active-low fault from external VOFFSET regulator            |                 |  |

| PG_RESET           | D11                                  | I                   |                            |                     |                                 | Active low from external VRESET regulator                   |                 |  |

| EN_BIAS            | D9                                   | 0                   | LVCMOS                     |                     |                                 | Active-high enable for external VBIAS regulator             |                 |  |

| EN_OFFSET          | C9                                   | 0                   |                            |                     |                                 | Active-high enable for external VOFFSET regulator           |                 |  |

| EN_RESET           | E9                                   | 0                   |                            |                     |                                 | Active-high enable for external VRESET regulator            |                 |  |

| Table 4-1. Pin Functions (continued) |     |                     |         |                     |                     |                                  |                             |  |

|--------------------------------------|-----|---------------------|---------|---------------------|---------------------|----------------------------------|-----------------------------|--|

| PIN <sup>(1)</sup>                   |     | TYPE <sup>(5)</sup> | SIGNAL  | DATA                | INTERNAL            | DESCRIPTION                      | TRACE (mils) <sup>(4)</sup> |  |

| NAME                                 | NO. |                     | SIGNAL  | RATE <sup>(2)</sup> | TERM <sup>(3)</sup> | DESCRIPTION                      | TRACE (IIIIIs)              |  |

| LEAVE P                              |     |                     |         |                     | INCONNECTED         |                                  |                             |  |

| MBRST(0)                             | C2  | 0                   |         |                     |                     |                                  |                             |  |

| MBRST(1)                             | C3  | 0                   |         |                     |                     |                                  |                             |  |

| MBRST(2)                             | C5  | 0                   |         |                     |                     |                                  |                             |  |

| MBRST(3)                             | C4  | 0                   |         |                     |                     |                                  |                             |  |

| MBRST(4)                             | E5  | 0                   |         |                     |                     |                                  |                             |  |

| MBRST(5)                             | E4  | 0                   |         |                     |                     |                                  |                             |  |

| MBRST(6)                             | E3  | 0                   |         |                     |                     |                                  |                             |  |

| MBRST(7)                             | G4  | 0                   | Analog  |                     | - Pulldown          | For proper DMD operation, do not |                             |  |

| MBRST(8)                             | G3  | 0                   | Allalog |                     | I dildowii          | connect.                         |                             |  |

| MBRST(9)                             | G2  | 0                   |         |                     |                     |                                  |                             |  |

| MBRST(10)                            | J4  | 0                   |         |                     |                     |                                  |                             |  |

| MBRST(11)                            | J3  | 0                   |         |                     |                     |                                  |                             |  |

| MBRST(12)                            | J2  | 0                   |         |                     |                     |                                  |                             |  |

| MBRST(13)                            | L4  | 0                   |         |                     |                     |                                  |                             |  |

| MBRST(14)                            | L3  | 0                   |         |                     |                     |                                  |                             |  |

| MBRST(15)                            | L2  | 0                   |         |                     |                     |                                  |                             |  |

|                                      |     |                     | LI      | EAVE PIN L          | INCONNECTED         |                                  |                             |  |

| RESERVED_PFE                         | E7  | I                   |         |                     |                     |                                  |                             |  |

| RESERVED_TM                          | D13 | I                   | LVCMOS  |                     | Pulldown            |                                  |                             |  |

| RESERVED_XI1                         | E13 | I                   |         |                     |                     | For proper DMD                   |                             |  |

| RESERVED_TP0                         | W12 | I                   |         |                     |                     | operation, do not connect.       |                             |  |

| RESERVED_TP1                         | Y11 | I                   | Analog  |                     |                     |                                  |                             |  |

| RESERVED_TP2                         | X11 | 1                   |         |                     |                     |                                  |                             |  |

|                                      |     | "                   | LI      | EAVE PIN L          | INCONNECTED         |                                  |                             |  |

| RESERVED_BA                          | Y12 | 0                   |         |                     |                     | For proper DMD                   |                             |  |

| RESERVED_BB                          | C12 | 0                   | LVCMOS  |                     |                     | operation, do not                |                             |  |

| RESERVED_TS                          | D5  | 0                   |         |                     |                     | connect.                         |                             |  |

|                                      |     |                     | LI      | EAVE PIN L          | INCONNECTED         |                                  |                             |  |

| NO CONNECT                           | B11 |                     |         |                     |                     |                                  |                             |  |

| NO CONNECT                           | C11 |                     |         |                     |                     |                                  |                             |  |

| NO CONNECT                           | C13 |                     |         |                     | 1                   | For proper DMD                   |                             |  |

| NO CONNECT                           | E12 |                     |         |                     | 1                   | operation, do not connect.       |                             |  |

| NO CONNECT                           | E14 |                     |         |                     | 1                   |                                  |                             |  |

| NO CONNECT                           | E23 |                     |         |                     | 1                   |                                  |                             |  |

| NO CONNECT                           | H4  |                     |         |                     |                     |                                  |                             |  |

| NO CONNECT                           | N2  |                     |         |                     | 1                   |                                  |                             |  |

| NO CONNECT                           | N3  |                     |         |                     | 1                   |                                  |                             |  |

| NO CONNECT                           | N4  |                     |         |                     | 1                   | For proper DMD                   |                             |  |

| NO CONNECT                           | R2  |                     |         |                     | 1                   | operation, do not connect.       |                             |  |

| NO CONNECT                           | R3  |                     |         |                     | 1                   | 55.111000.                       |                             |  |

| NO CONNECT                           | R4  |                     |         |                     | 1                   |                                  |                             |  |

| NO CONNECT                           | T4  |                     |         |                     | 1                   |                                  |                             |  |

|                                      |     |                     |         |                     | 1                   |                                  |                             |  |

| PIN <sup>(1)</sup> |     | TYPE <sup>(5)</sup> | SIGNAL | DATA                | INTERNAL            | DESCRIPTION                               | TRACE (mils) <sup>(4)</sup> |

|--------------------|-----|---------------------|--------|---------------------|---------------------|-------------------------------------------|-----------------------------|

| NAME               | NO. | ITPE(*)             | SIGNAL | RATE <sup>(2)</sup> | TERM <sup>(3)</sup> | DESCRIPTION                               | TRACE (IIIIS)               |

| NO CONNECT         | U2  |                     |        |                     |                     |                                           |                             |

| NO CONNECT         | U3  |                     |        |                     |                     |                                           |                             |

| NO CONNECT         | U4  |                     |        |                     |                     |                                           |                             |

| NO CONNECT         | W3  |                     |        |                     |                     | For proper DMD operation, do not connect. |                             |

| NO CONNECT         | W4  |                     |        |                     |                     |                                           |                             |

| NO CONNECT         | W5  |                     |        |                     |                     |                                           |                             |

| NO CONNECT         | W13 |                     |        |                     |                     |                                           |                             |

| NO CONNECT         | W14 |                     |        |                     |                     |                                           |                             |

| NO CONNECT         | W23 |                     |        |                     |                     |                                           |                             |

| NO CONNECT         | X4  |                     |        |                     |                     |                                           |                             |

| NO CONNECT         | X5  |                     |        |                     |                     |                                           |                             |

| NO CONNECT         | X13 |                     |        |                     |                     |                                           |                             |

| NO CONNECT         | Y2  |                     |        |                     |                     | For proper DMD                            |                             |

| NO CONNECT         | Y3  |                     |        |                     |                     | operation, do not connect.                |                             |

| NO CONNECT         | Y4  |                     |        |                     |                     |                                           |                             |

| NO CONNECT         | Y5  |                     |        |                     |                     |                                           |                             |

| NO CONNECT         | Z11 |                     |        |                     |                     |                                           |                             |

<sup>(1)</sup> The following power supplies are required to operate the DMD: VCC, VCCI, VOFFSET, VBIAS, and VRESET. VSS must also be connected.

(5) I = Input, O = Output, G = Ground

Submit Document Feedback

<sup>(2)</sup> DDR = Double Data Rate. SDR = Single Data Rate. Refer to Section 5.7 for specifications and relationships.

<sup>(3)</sup> Internal term—CMOS level internal termination. Refer to Section 5.4 for differential termination specification.

<sup>(4)</sup> Dielectric Constant for the DMD FYE package is approximately 9.6. For the package trace lengths shown: Propagation Speed = 11.8 / sqrt(9.6) = 3.808in/ns. Propagation Delay = 0.262ns/in = 262ps/in = 10.315ps/mm.

#### **Table 4-2. Power Pin Functions**

|                     | PIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TVDE (UQ/E)(2)              | CIONAL | DESCRIPTION                                                                                                                                                                                                   |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME <sup>(1)</sup> | NO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TYPE (I/O/P) <sup>(2)</sup> | SIGNAL | DESCRIPTION                                                                                                                                                                                                   |  |  |

| VBIAS               | A6, A7, A8, AA6, AA7, AA8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                             | Analog | Supply voltage for positive Bias level of micromirror reset signal                                                                                                                                            |  |  |

|                     | A3, A4, A25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                             | Analog | Supply voltage for HVCMOS logic                                                                                                                                                                               |  |  |

| VOFFSET             | B26, L26, M26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                             | Analog | Supply voltage for stepped high voltage at micromirror address electrodes                                                                                                                                     |  |  |

|                     | N26, Z26, AA3, AA4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                             | Analog | Supply voltage for positive Offset level of micromirror reset signal                                                                                                                                          |  |  |

| VRESET              | G1, H1, J1, R1, T1, U1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                             | Analog | Supply voltage for negative Reset level of micromirror reset signal                                                                                                                                           |  |  |

| VCC                 | A9, B3, B5, B12, C1, C6, C10, D4, D6, D8, E1, E2, E10, E15, E16, E17, F3, H2, K1, K3, M4, P1, P3, T2, V3, W1, W2, W6, W9, W10, W15, W16, W17, X3, X6, Y1, Y8, Y13, Z1, Z3, Z12, AA2, AA9, AA10                                                                                                                                                                                                                                                                                                                                                                                          |                             | Analog | Supply voltage for LVCMOS core logic. Supply voltage for normal high level at micromirror address electrodes. Supply voltage for positive Offset level of micromirror reset signal during power-down sequence |  |  |

| VCCI                | A16, A17, A18, A20, A21, A23,<br>AA16, AA17, AA18, AA20, AA21,<br>AA23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Р                           | Analog | Supply voltage for LVDS receivers                                                                                                                                                                             |  |  |

| VSS                 | A5, A10, A11, A19, A22, A24, B2, B4, B9, B13, B17, B20, B21, B24, C7, C15, C18, C21, C22, C26, D1, D3, D7, D10, D12, D14, D15, D16, D17, D18, D19, D20, D21, D22, D23, D26, E6, E8, E18, E19, E20, E21, E22, E26, F1, F2, F4, F23, F26, G23, G26, H3, H26, J26, K2, K4, K26, L1, M1, M2, M3, M23, M24, M25, N1, P2, P4, P26, R26, T3, T26, U23, U26, V1, V2, V4, V23, V26, W8, W18, W19, W20, W21, W22, W26, X1, X2, X7, X10, X12, X14, X15, X16, X17, X18, X19, X20, X21, X22, X23, X26, Y6, Y15, Y18, Y21, Y22, Y26, Z2, Z4, Z9, Z13, Z17, Z20, Z21, Z24, AA5, AA11, AA19, AA22, AA24 |                             | Analog | Device ground. Common return for all power                                                                                                                                                                    |  |  |

<sup>(1)</sup> The following power supplies are required to operate the DMD: VCC, VCCI, VOFFSET, VBIAS, and VRESET. VSS must also be connected.

<sup>(2)</sup> P = Power

# **5 Specifications**

# 5.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted). Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

|                              |                                                                                                               | MIN  | MAX         | UNIT |

|------------------------------|---------------------------------------------------------------------------------------------------------------|------|-------------|------|

| SUPPLY VOLTAGES              |                                                                                                               |      |             |      |

| VCC                          | Supply voltage for LVCMOS core logic <sup>(1)</sup>                                                           | -0.5 | 4           | V    |

| VCCI                         | Supply voltage for LVDS receivers <sup>(1)</sup>                                                              | -0.5 | 4           | V    |

| VOFFSET                      | Supply voltage for HVCMOS and micromirror electrode <sup>(1)</sup> (2)                                        | -0.5 | 9           | V    |

| VBIAS                        | Supply voltage for micromirror electrode <sup>(1)</sup>                                                       | -0.5 | 17          | V    |

| VRESET                       | Supply voltage for micromirror electrode <sup>(1)</sup>                                                       | -11  | 0.5         | V    |

| VCC – VCCI                   | Supply voltage change (absolute value) <sup>(3)</sup>                                                         |      | 0.3         | V    |

| VBIAS – VOFFSET              | Supply voltage change (absolute value) <sup>(4)</sup>                                                         |      | 8.75        | V    |

| INPUT VOLTAGES               |                                                                                                               |      |             |      |

|                              | Input voltage for all other LVCMOS input pins <sup>(1)</sup>                                                  | -0.5 | VCC + 0.15  | V    |

|                              | Input voltage for all other LVDS input pins <sup>(1)</sup> (5)                                                | -0.5 | VCCI + 0.15 | V    |

| V <sub>ID</sub>              | Input differential voltage (absolute value) <sup>(6)</sup>                                                    |      | 700         | mV   |

| I <sub>ID</sub>              | Input differential current <sup>(6)</sup>                                                                     |      | 7           | mA   |

| CLOCKS                       |                                                                                                               |      |             |      |

| $f_{clock}$                  | Clock frequency for LVDS interface, DCLK (all channels)                                                       |      | 460         | MHz  |

| ENVIRONMENTAL                |                                                                                                               |      |             |      |

| T                            | Temperature, operating <sup>(7)</sup>                                                                         | 0    | 90          | °C   |

| $T_{ARRAY}$ and $T_{WINDOW}$ | Temperature: non-operating <sup>(7)</sup>                                                                     | -40  | 90          | °C   |

| T <sub>DELTA</sub>           | Absolute Temperature delta between any point on the window edge and the ceramic test point TP1 <sup>(8)</sup> |      | 30          | °C   |

| T <sub>DP</sub>              | Dew Point temperature, operating and non-operating (non-condensing)                                           |      | 81          | °C   |

- (1) All voltages are referenced to common ground VSS. Supply voltages VCC, VCCI, VOFFSET, VBIAS, and VRESET are all required for proper DMD operation. VSS must also be connected.

- VOFFSET supply transients must fall within specified voltages.

- To prevent excess current, the supply voltage change |VCCI VCC| must be less than specified limit. (3)

- To prevent excess current, the supply voltage change |VBIAS VOFFSET| must be less than specified limit. Refer to Section 7 for additional information.

- This maximum LVDS input voltage rating applies when each input of a differential pair is at the same voltage potential.

- LVDS differential inputs must not exceed the specified limit or damage may result to the internal termination resistors

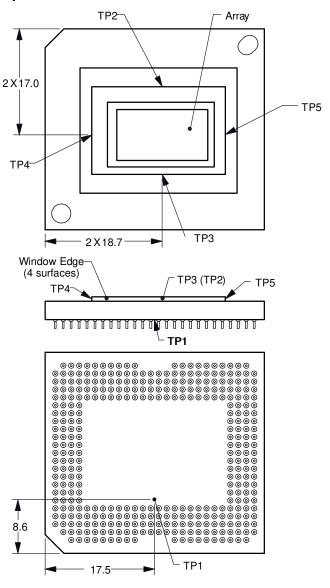

- The highest temperature of the active array (as calculated by Section 6.6) or of any point along the Window Edge as defined in Figure 6-1. The locations of thermal test points TP2, TP3, TP4, and TP5 in Figure 6-1 are intended to measure the highest window edge temperature. If a particular application causes another point on the window edge to be at a higher temperature, add a test point to that location.

- Temperature delta is the highest difference between the ceramic test point 1 (TP1) and anywhere on the window edge as shown in Figure 6-1. The window test points TP2, TP3, TP4, and TP5 in Figure 6-1 are intended to result in the worst-case delta. If a particular application causes another point on the window edge to result in a larger delta temperature, that point should be used.

#### **5.2 Storage Conditions**

Applicable for the DMD as a component or non-operational in a system.

|                     |                                                                      | MIN | MAX | UNIT |

|---------------------|----------------------------------------------------------------------|-----|-----|------|

| T <sub>DMD</sub>    | DMD storage temperature                                              | -40 | 80  | °C   |

| T <sub>DP-AVG</sub> | Average dew point temperature (non-condensing) <sup>(1)</sup>        |     | 28  | °C   |

| T <sub>DP-ELR</sub> | Elevated dew point temperature range (non-condensing) <sup>(2)</sup> | 28  | 36  | °C   |

## **5.2 Storage Conditions (continued)**

Applicable for the DMD as a component or non-operational in a system.

|                   |                                                         | MIN | MAX | UNIT   |

|-------------------|---------------------------------------------------------|-----|-----|--------|

| CT <sub>ELR</sub> | Cumulative time in elevated dew point temperature range |     | 24  | Months |

<sup>(1)</sup> The average over time (including storage and operating) that the device is not in the "elevated dew point temperature range."

# 5.3 ESD Ratings

|   |             |                         |                                                                   | VALUE | UNIT |

|---|-------------|-------------------------|-------------------------------------------------------------------|-------|------|

| ' | $V_{(ESD)}$ | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±2000 | V    |

(1) JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

# **5.4 Recommended Operating Conditions**

Over operating free-air temperature range (unless otherwise noted). The functional performance of the device specified in this data sheet is achieved when operating the device within the limits defined by this table. No level of performance is implied when operating the device above or below these limits.

|                         |                                                                             | MIN   | NOM | MAX        | UNIT |  |

|-------------------------|-----------------------------------------------------------------------------|-------|-----|------------|------|--|

| SUPPLY VOLTAGES         | <b>s</b> (1) (2)                                                            |       |     | <u> </u>   |      |  |

| VCC                     | Supply voltage for LVCMOS core logic                                        | 3.15  | 3.3 | 3.45       | V    |  |

| VCCI                    | Supply voltage for LVDS receivers                                           | 3.15  | 3.3 | 3.45       | V    |  |

| VOFFSET                 | Supply voltage for HVCMOS and micromirror electrodes <sup>(2)</sup>         | 8.25  | 8.5 | 8.75       | V    |  |

| VBIAS                   | Supply voltage for micromirror electrodes                                   | 15.5  | 16  | 16.5       | V    |  |

| VRESET                  | Supply voltage for micromirror electrodes                                   | -9.5  | -10 | -10.5      | V    |  |

| VCCI-VCC                | Supply voltage change (absolute value) <sup>(3)</sup>                       |       | 0   | 0.3        | V    |  |

| VBIAS-VOFFSET           | Supply voltage change (absolute value) <sup>(4)</sup>                       |       |     | 8.75       | V    |  |

| LVCMOS PINS             |                                                                             |       |     |            |      |  |

| V <sub>IH</sub>         | High level Input voltage <sup>(5)</sup>                                     | 1.7   | 2.5 | VCC + 0.15 | V    |  |

| V <sub>IL</sub>         | Low level Input voltage <sup>(5)</sup>                                      | - 0.3 |     | 0.7        | V    |  |

| I <sub>OH</sub>         | High level output current at V <sub>OH</sub> = 2.4V                         |       |     | -20        | mA   |  |

| I <sub>OL</sub>         | Low level output current at V <sub>OL</sub> = 0.4V                          |       |     | 15         | mA   |  |

| t <sub>PWRDNZ</sub>     | PWRDNZ pulse width <sup>(6)</sup>                                           | 10    |     |            | ns   |  |

| SCP INTERFACE           |                                                                             |       |     |            |      |  |

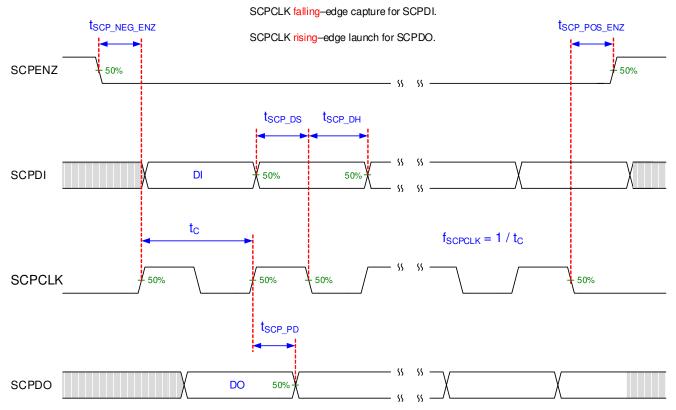

| fscpclk                 | SCP clock frequency <sup>(7)</sup>                                          |       |     | 500        | kHz  |  |

| t <sub>SCP_DS</sub>     | SCPDI clock setup time (before SCPCLK falling-edge) <sup>(8)</sup>          | 800   |     |            | ns   |  |

| t <sub>SCP_DH</sub>     | SCPDI hold time (after SCPCLK falling-edge) <sup>(8)</sup>                  | 900   |     |            | ns   |  |

| tscp_byte_interval      | Time between consecutive bytes                                              | 1     |     |            | μs   |  |

| tscp_neg_enz            | Time between falling edge of SCPENZ and the first rising edge of SCPCLK     | 30    |     |            | ns   |  |

| t <sub>SCP_PW_ENZ</sub> | SCPENZ inactive pulse width (high level)                                    | 1     |     |            | μs   |  |

| tscp_out_en             | Time required for SCP output buffer to recover after SCPENZ (from tristate) |       |     | 1.5        | ns   |  |

| $f_{ m clock}$          | SCP circuit clock oscillator frequency <sup>(9)</sup>                       | 9.6   |     | 11.1       | MHz  |  |

Copyright © 2025 Texas Instruments Incorporated

Submit Document Feedback

<sup>(2)</sup> Limit exposure to dew point temperatures in the elevated range during storage and operation to less than a total cumulative time of CT<sub>ELR</sub>.

# 5.4 Recommended Operating Conditions (continued)

Over operating free-air temperature range (unless otherwise noted). The functional performance of the device specified in this data sheet is achieved when operating the device within the limits defined by this table. No level of performance is implied when operating the device above or below these limits.

|                        |                                                                                                           | MIN | NOM  | MAX                      | UNIT   |

|------------------------|-----------------------------------------------------------------------------------------------------------|-----|------|--------------------------|--------|

| LVDS INTERFA           | CE                                                                                                        |     |      |                          |        |

| $f_{clock}$            | Clock frequency for LVDS interface, DCLK (all channels)                                                   |     |      | 400                      | MHz    |

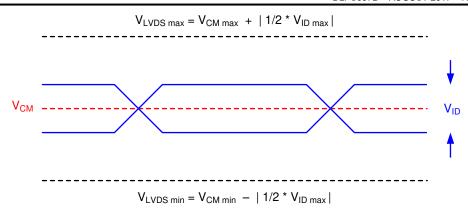

| V <sub>ID</sub>        | Input differential voltage (absolute value) <sup>(10)</sup>                                               | 100 | 400  | 600                      | mV     |

| V <sub>CM</sub>        | Common mode <sup>(10)</sup>                                                                               |     | 1200 |                          | mV     |

| V <sub>LVDS</sub>      | LVDS voltage <sup>(10)</sup>                                                                              | 0   |      | 2000                     | mV     |

| t <sub>LVDS_RSTZ</sub> | Time required for LVDS receivers to recover from PWRDNZ                                                   |     |      | 10                       | ns     |

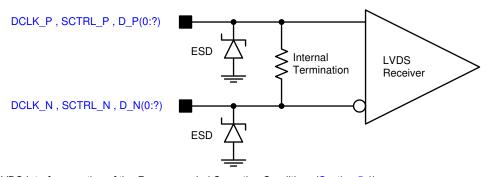

| Z <sub>IN</sub>        | Internal differential termination resistance                                                              | 95  |      | 105                      | Ω      |

| Z <sub>LINE</sub>      | Line differential impedance (PWB/trace)                                                                   | 90  | 100  | 110                      | Ω      |

| ENVIRONMENT            | AL                                                                                                        |     |      |                          |        |

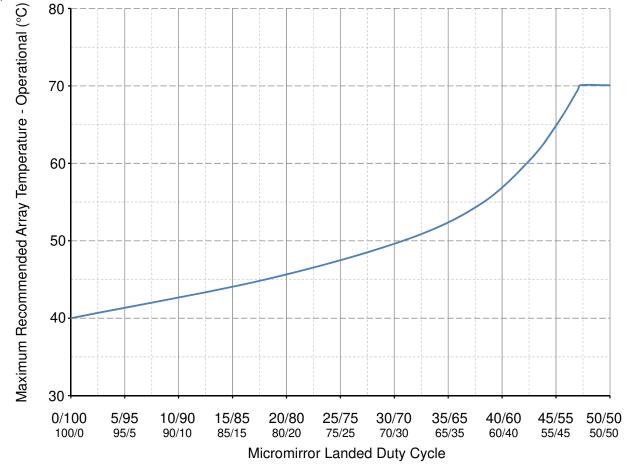

| <b>-</b>               | Array temperature, long-term operational <sup>(11)</sup> (12) (13)                                        | 10  |      | 40 to 70 <sup>(14)</sup> | °C     |

| T <sub>ARRAY</sub>     | Array temperature, short-term operational, 500-hr max <sup>(12)</sup> (15)                                | 0   |      | 10                       | C      |

| T <sub>WINDOW</sub>    | Window temperature – operational <sup>(16)</sup>                                                          |     |      | 85                       | °C     |

| T <sub>IDELTA  </sub>  | Absolute temperature delta between any point on the window edge and the ceramic test point TP1. (17) (18) |     |      | 26                       | °C     |

| T <sub>DP-AVG</sub>    | Average dew point temperature (non-condensing) <sup>(19)</sup>                                            |     |      | 28                       | °C     |

| T <sub>DP-ELR</sub>    | Elevated dew point temperature range (non-condensing) <sup>(20)</sup>                                     | 28  |      | 36                       | °C     |

| CT <sub>ELR</sub>      | Cumulative time in elevated dew point temperature range                                                   |     |      | 24                       | Months |

| SOLID STATE II         | LLUMINATION                                                                                               |     |      |                          |        |

| ILL <sub>UV</sub>      | Illumination power at wavelengths < 410nm <sup>(11)</sup> (22)                                            |     |      | 10                       | mW/cm2 |

| ILL <sub>VIS</sub>     | Illumination power at wavelengths ≥ 410nm and ≤ 800nm (21) (22)                                           |     |      | 23.7                     | W/cm2  |

| ILL <sub>IR</sub>      | Illumination power at wavelengths > 800nm <sup>(22)</sup>                                                 |     |      | 10                       | mW/cm2 |

| ILL <sub>BLU</sub>     | Illumination power at wavelengths ≥ 410nm and ≤ 475nm <sup>(21)</sup> (22)                                |     |      | 7.5                      | W/cm2  |

| ILL <sub>BLU1</sub>    | Illumination power at wavelengths ≥ 410nm and ≤ 440nm (21) (22)                                           |     |      | 1.3                      | W/cm2  |

| LAMP ILLUMINA          | ATION                                                                                                     |     |      |                          |        |

| ILL <sub>UV</sub>      | Illumination power at wavelengths < 395nm <sup>(11)</sup> (22)                                            |     |      | 2.0                      | mW/cm2 |

| ILL <sub>VIS</sub>     | Illumination power at wavelengths ≥ 395nm and ≤ 800nm <sup>(21)</sup> (22)                                |     |      | 23.7                     | W/cm2  |

| ILL <sub>IR</sub>      | Illumination power at wavelengths > 800nm <sup>(22)</sup>                                                 |     |      | 10                       | mW/cm2 |

- Supply voltages VCC, VCCI, VOFFSET, VBIAS, and VRESET are all required for proper DMD operation. VSS must also be connected.

- (2) VOFFSET supply transients must fall within specified max voltages.

- (3) To prevent excess current, the supply voltage change |VCCI VCC| must be less than specified limit.

- (4) To prevent excess current, the supply voltage change |VBIAS VOFFSET| must be less than the specified limit. Refer to Section 7 for additional information.

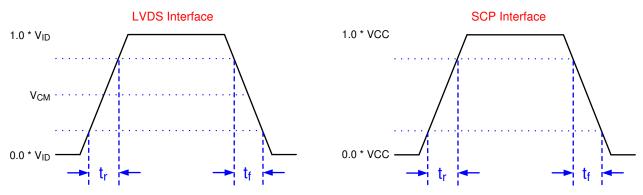

- (5) Tester conditions for V<sub>IH</sub> and V<sub>IL</sub>: Frequency = 60MHz. Maximum Rise Time = 2.5ns at (20% to 80%) Frequency = 60MHz. Maximum Fall Time = 2.5ns at (80% to 20%)

- (6) PWRDNZ input pin resets the SCP and disables the LVDS receivers. PWRDNZ input pin overrides SCPENZ input pin and tri-states the SCPDO output pin.

- (7) The SCP clock is a gated clock. Duty cycle shall be 50% ± 10%. SCP parameter is related to the frequency of DCLK.

- (8) Refer to Figure 5-2.

- (9) SCP internal oscillator is specified to operate all SCP registers. For all SCP operations, DCLK is required.

- (10) Refer to Figure 5-3, Figure 5-4, and Figure 5-5.

- (11) Simultaneous exposure of the DMD to the maximum Section 5.4 for temperature and UV illumination reduces device lifetime.

- (12) The array temperature cannot be measured directly and must be computed analytically from the temperature measured at test point 1 (TP1) shown in Figure 6-1 and the package thermal resistance using the calculation in Section 6.6.

- (13) Long-term is defined as the average over the usable life.

- (14) Per Figure 5-1, the maximum operational array temperature should be derated based on the micromirror landed duty cycle that the DMD experiences in the end application. See Section 6.8.

- (15) Short-term is defined as cumulative time over the usable life of the device.

Submit Document Feedback

#### www.ti.com

- (16) The locations of thermal test points TP2, TP3, TP4, and TP5 in Figure 6-1 are intended to measure the highest window edge temperature. For most applications, the locations shown are representative of the highest window edge temperature. If a particular application causes additional points on the window edge to be at a higher temperature, test points should be added to those locations.

- (17) Temperature delta is the highest difference between the ceramic test point 1 (TP1) and anywhere on the window edge as shown in Figure 6-1. The window test points TP2, TP3, TP4, and TP5 shown in Figure 6-1 are intended to result in the worst-case delta temperature. If a particular application causes another point on the window edge to result in a larger delta in temperature, that point should be used.

- (18) DMD is qualified at the combination of the maximum temperature and maximum lumens specified. Operation of the DMD outside of these limits has not been tested.

- (19) The average over time (including storage and operating) that the device is not in the 'elevated dew point temperature range'.

- (20) Exposure to dew point temperatures in the elevated range during storage and operation should be limited to less than a total cumulative time of CT<sub>ELR</sub>.

- (21) The maximum allowable optical power incident on the DMD is limited by the maximum optical power density for each wavelength range specified and the micromirror array temperature (T<sub>ARRAY</sub>).

- (22) To calculate see Section 6.7.

Figure 5-1. Recommended Maximum DMD Temperature—Derating Curve

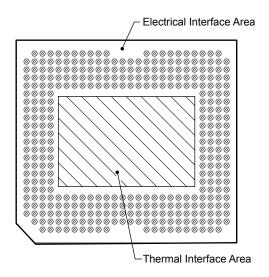

### 5.5 Thermal Information

| THERMAL METRIC <sup>(1)</sup>                              | DLP650NE    |      |

|------------------------------------------------------------|-------------|------|

|                                                            | FYE Package | UNIT |

|                                                            | 350 PINS    |      |

| Thermal resistance from active array to test point 1 (TP1) | 0.6         | °C/W |

(1) The DMD is designed to conduct absorbed and dissipated heat to the back of the package where it can be removed by an appropriate heat sink. The heat sink and cooling system must be capable of maintaining the package within the temperature range specified in the Recommended Operating Conditions.

The total heat load on the DMD is largely driven by the incident light absorbed by the active area; although other contributions include light energy absorbed by the window aperture and electrical power dissipation of the array.

Optical systems should be designed to minimize the light energy falling outside the window clear aperture since any additional thermal load in this area can significantly degrade the reliability of the device.

#### **5.6 Electrical Characteristics**

Over operating free-air temperature range (unless otherwise noted).

|                     | PARAMETER                                   | TEST CONDITIONS(1)                                             | MIN  | TYP | MAX  | UNIT |

|---------------------|---------------------------------------------|----------------------------------------------------------------|------|-----|------|------|

| V <sub>OH</sub>     | High-level output voltage                   | VCC = 3.3 V, I <sub>OH</sub> = -20 mA                          | 2.4  |     |      | V    |

| V <sub>OL</sub>     | Low -level output voltage                   | VCC = 3.45 V, I <sub>OL</sub> = 15 mA                          |      |     | 0.4  | V    |

| I <sub>IH</sub>     | High-level input current <sup>(2) (3)</sup> | VCC = 3.45 V, V <sub>I</sub> = VCC                             |      |     | 250  | μA   |

| I <sub>IL</sub>     | Low-level input current                     | VCC = 3.45 V, V <sub>I</sub> = 0                               | -250 |     |      | μA   |

| I <sub>OZ</sub>     | High-impedance output current               | VCC = 3.45 V                                                   |      |     | 10   | μA   |

| I <sub>CC</sub>     | — Supply current <sup>(4)</sup>             | VCC = 3.45 V                                                   |      |     | 1100 | mΛ   |

| I <sub>CCI</sub>    | — Supply current                            | VCCI = 3.45 V                                                  |      |     | 500  | mA   |

| I <sub>OFFSET</sub> | Cumply surrent(5)                           | VOFFSET = 8.75 V                                               |      | 10  | 25   | m A  |

| I <sub>BIAS</sub>   | — Supply current <sup>(5)</sup>             | VBIAS = 16.5 V                                                 |      | 10  | 14   | mA   |

| I <sub>RESET</sub>  | — Supply current                            | VRESET = -10.5 V                                               |      | 10  | 11   | mA   |

| I <sub>TOTAL</sub>  | — Зирріу сипені                             | Total Sum                                                      |      |     | 1650 | IIIA |

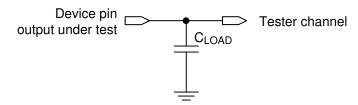

| Cı                  | Input capacitance                           | f = 1 MHz                                                      |      |     | 10   | pF   |

| Co                  | Output capacitance                          | f = 1 MHz                                                      |      |     | 10   | pF   |

| См                  | Reset group capacitance<br>MBRST(14:0)      | f = 1 MHz<br>all inputs interconnected,<br>(1920 x 1080) array | 330  |     | 390  | pF   |

<sup>(1)</sup> All voltages are referenced to common ground VSS. Supply voltages VCC, VCCI, VOFFSET, VBIAS, and VRESET are all required for proper DMD operation. VSS must also be connected.

(5) To prevent excess current, the supply voltage change |VBIAS - VOFFSET| must be less than specified limit.

<sup>(2)</sup> Applies to LVCMOS input pins only; excludes the LVDS pins and MBRST pins

<sup>(3)</sup> LVCMOS input pins utilize an internal 18000-Ω passive resistor for pullup and pulldown configurations. Refer to Section 4 to determine the pullup or pulldown configuration used.

<sup>4)</sup> To prevent excess current, the supply voltage change |VCCI - VCC| must be less than specified limit.

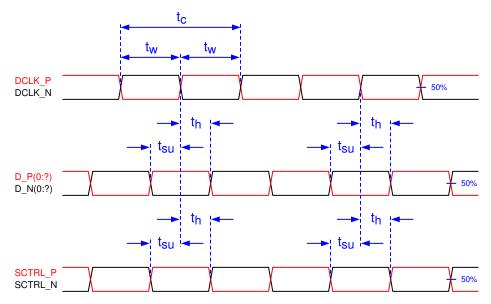

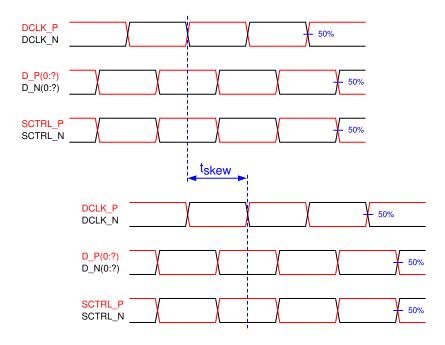

# 5.7 Timing Requirements

Over Recommended Operating Conditions (Section 5.4) unless otherwise noted. (5)

|                      | ·                       | DESC                                              | CRIPTION <sup>(1)</sup>                                                                                                                                       | MIN      | TYP  | MAX  | UNIT |

|----------------------|-------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|------|------|

| SCP IN               | TERFACE <sup>(2)</sup>  |                                                   |                                                                                                                                                               | <u> </u> | '    |      |      |