**ADC3664** JAJSKU4B - DECEMBER 2020 - REVISED JULY 2022

# ADC3664 14 ビット、125 MSPS、低ノイズ、低消費電力デュアル・チャネル **ADC**

## 1 特長

- 14 ビット、125MSPS ADC

- ノイズ・フロア:-156.9dBFS/Hz

- 低消費電力:100mW/ch

- レイテンシ:2 クロック・サイクル

- 電圧リファレンス:

- 外部:65~125MSPS

- 内部:100~125MSPS

- 14 ビット、ミッシングコードなしを保証

- 入力周波数带:1.4GHz (3dB)

- INL:±2.6LSB, DNL:±0.9LSB

- 産業用温度範囲:-40℃~+105℃

- オンチップ・デジタル・フィルタ (オプション)

- デシメーション比:2、4、8、16、32

- 32 ビット NCO

- シリアル LVDS デジタル・インターフェイス (2 線式、1 線式、1/2 線式)

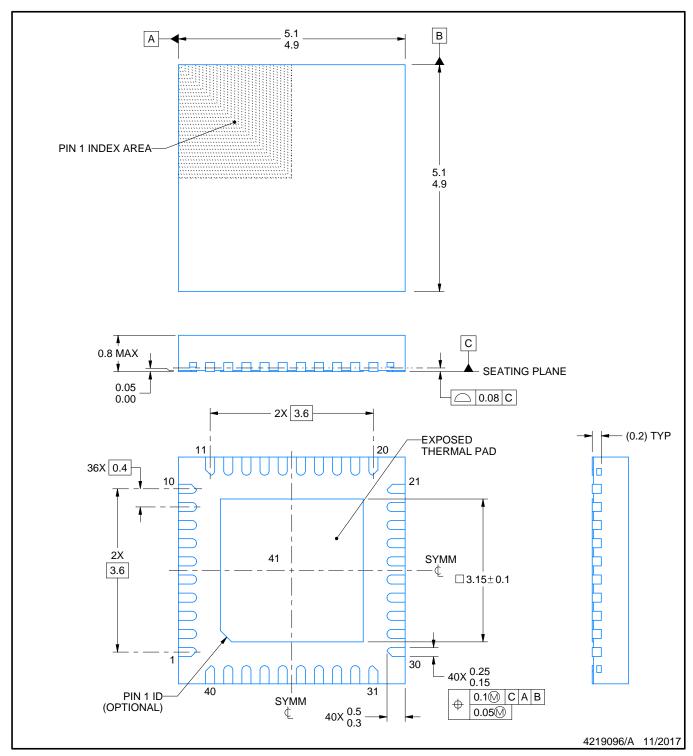

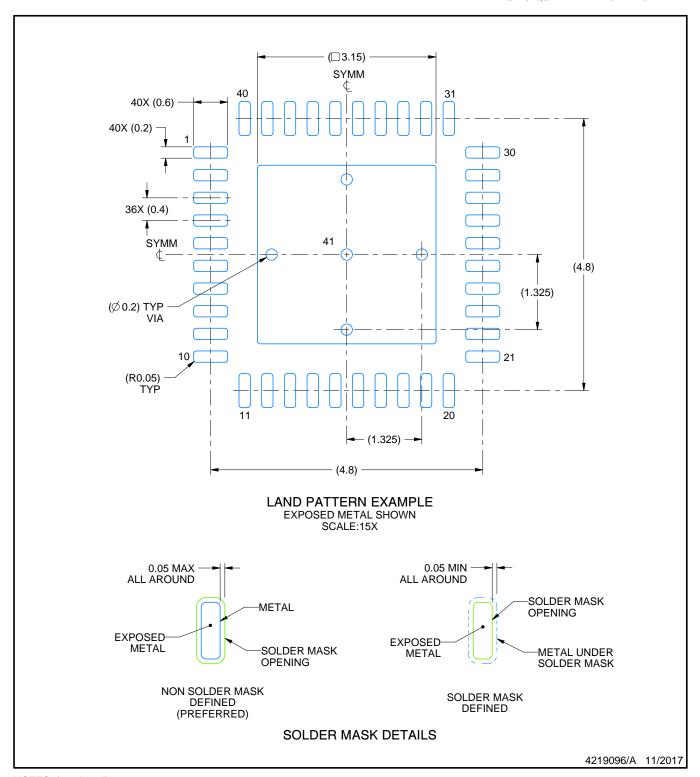

- 小型サイズ:40-VQFN (5mm × 5mm) パッケージ

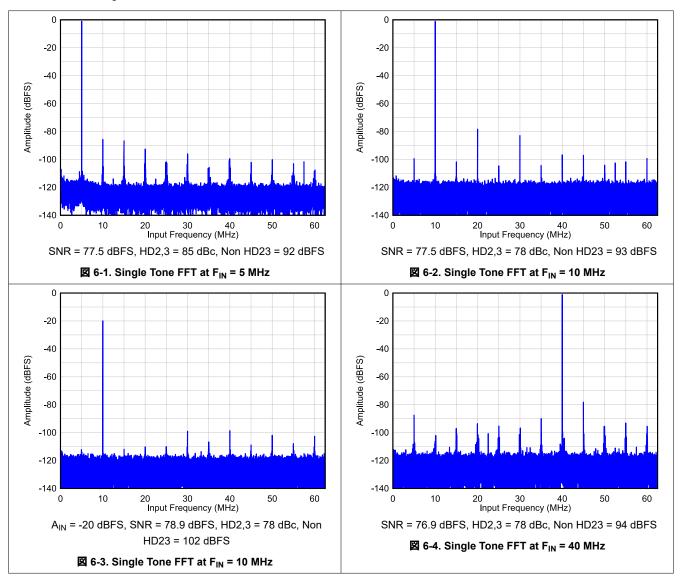

- スペクトル性能 (f<sub>IN</sub> = 5MHz):

- SNR:77.5dBFS

- SFDR:84dBc HD2、HD3

- SFDR:92dBFS の最大スプリアス

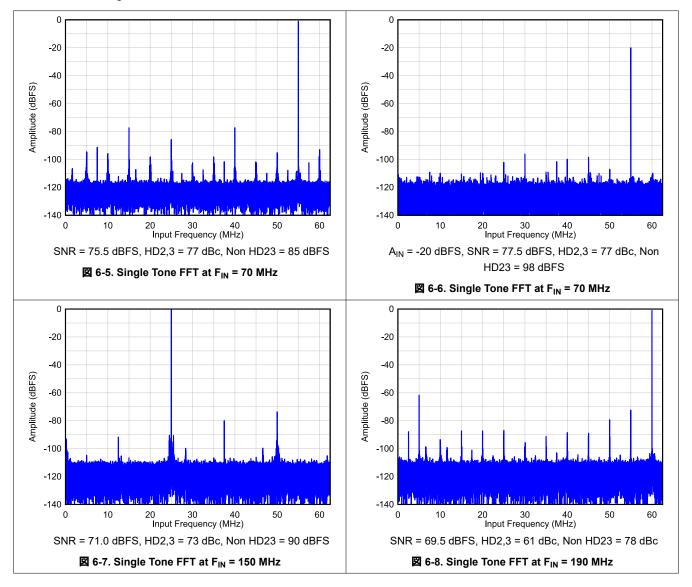

- スペクトル性能 (f<sub>IN</sub> = 70 MHz):

- SNR:75.5dBFS

- SFDR:76dBc HD2, HD3

- SFDR:84dBFS の最大スプリアス

# 2 アプリケーション

- 高速データ・アクイジション

- ソフトウェア無線

- 通信インフラ

- スペクトル・アナライザ

- OTDR

- 制御ループ

- ソース・メジャー・ユニット(SMU)

- 計測機器

- 分光器

- レーダー

# 3 概要

ADC3664 デバイスは、低ノイズ、超低消費電力、14 ビッ ト、125MSPS のデュアル・チャネル高速 A/D コンバータ (ADC) です。きわめて低いノイズ性能を実現するように設 計されており、ノイズ・スペクトル密度は -156.9dBFS/Hz で、優れた直線性とダイナミック・レンジを備えています。 ADC3664 デバイスは IF サンプリングをサポートしており、 広範なアプリケーションに最適です。レイテンシがわずか 1 クロック・サイクルと短いため、高速な制御ループを実現 できます。ADC の消費電力は 1 チャネルあたりわずか 100mW (125MSPS 時) であり、より低いサンプリング・レ ートでは、消費電力を非常によく低減できます。

ADC3664 は、シリアル LVDS (SLVDS) インターフェイス を使用してデータを出力し、デジタル相互接続の数を最 小限に抑えます。このデバイスは、2 レーン、1 レーン、お よびハーフ・レーンのオプションをサポートしています。 ADC3664 は 16 ビット分解能 ADC ファミリとピン互換で す。このデバイスは、-40~+105℃の拡張産業用温度範 囲をサポートしています。

#### パッケージ情報

|         | Y ' P P III IM       |               |

|---------|----------------------|---------------|

| 部品番号    | パッケージ <sup>(1)</sup> | 本体サイズ (公称)    |

| ADC3664 | VQFN (40)            | 5.00 × 5.00mm |

利用可能なパッケージについては、このデータシートの末尾にあ る注文情報を参照してください。

#### 表 3-1. デバイスの比較

| 部品番号    | 分解能    | サンプリング・レート |  |  |  |  |

|---------|--------|------------|--|--|--|--|

| ADC3661 | 16 ビット | 10MSPS     |  |  |  |  |

| ADC3662 | 16 ビット | 25MSPS     |  |  |  |  |

| ADC3663 | 16 ビット | 65MSPS     |  |  |  |  |

| ADC3664 | 14 ビット | 125MSPS    |  |  |  |  |

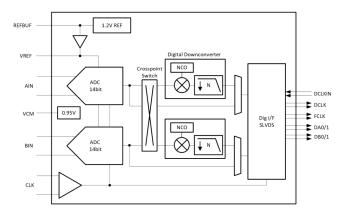

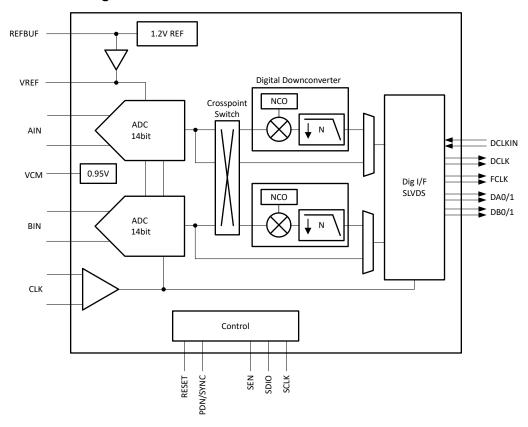

概略ブロック図

# **Table of Contents**

| 1 特長                                               | 1 | 8.2 Functional Block Diagram                          | . 20 |

|----------------------------------------------------|---|-------------------------------------------------------|------|

| 2 アプリケーション                                         |   | 8.3 Feature Description                               | 21   |

| 3 概要                                               |   | 8.4 Device Functional Modes                           | 41   |

| 4 Revision History                                 |   | 8.5 Programming                                       | . 42 |

| 5 Pin Configuration and Functions                  |   | 8.6 Register Maps                                     | 44   |

| 6 Specifications                                   |   | 9 Application Information Disclaimer                  | . 58 |

| 6.1 Absolute Maximum Ratings                       |   | 9.1 Typical Application                               | . 58 |

| 6.2 ESD Ratings                                    |   | 9.2 Initialization Set Up                             | . 61 |

| 6.3 Recommended Operating Conditions               |   | 9.3 Power Supply Recommendations                      | 62   |

| 6.4 Thermal Information                            |   | 9.4 Layout                                            | . 63 |

| 6.5 Electrical Characteristics - Power Consumption |   | 10 Device and Documentation Support                   | 65   |

| 6.6 Electrical Characteristics - DC Specifications |   | 10.1 Receiving Notification of Documentation Updates. | 65   |

| 6.7 Electrical Characteristics - AC Specifications |   | 10.2 サポート・リソース                                        | . 65 |

| 6.8 Timing Requirements                            |   | 10.3 Trademarks                                       | .65  |

| 6.9 Typical Characteristics                        |   | 10.4 Electrostatic Discharge Caution                  | .65  |

| 7 Parameter Measurement Information                |   | 10.5 Glossary                                         | .65  |

| 8 Detailed Description                             |   | 11 Mechanical, Packaging, and Orderable               |      |

| 8.1 Overview                                       |   | Information                                           | . 65 |

|                                                    |   |                                                       |      |

# **4 Revision History**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision A (August 2021) to Revision B (July 2022)                     | Page |

|-------------------------------------------------------------------------------------|------|

| Changed the output clock jitter unit from ps to ps pk-pk in the Timing Requirements | 10   |

| Added GND symbol to REFGND pin for all voltage reference option diagrams            | 25   |

| Added the section Output Bit Mapper                                                 | 37   |

| Added default power up configuration summary                                        | 42   |

| Updated power-up initialization diagram with correct indexing                       | 61   |

| Changes from Revision * (December 2020) to Revision A (August 2021)                 | Page |

| All wake up time values moved from MAX to NOM                                       |      |

| Added condition to resynch during operation to the SYNC section                     |      |

| , 3,                                                                                |      |

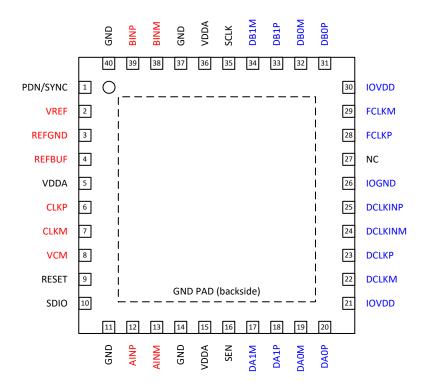

# **5 Pin Configuration and Functions**

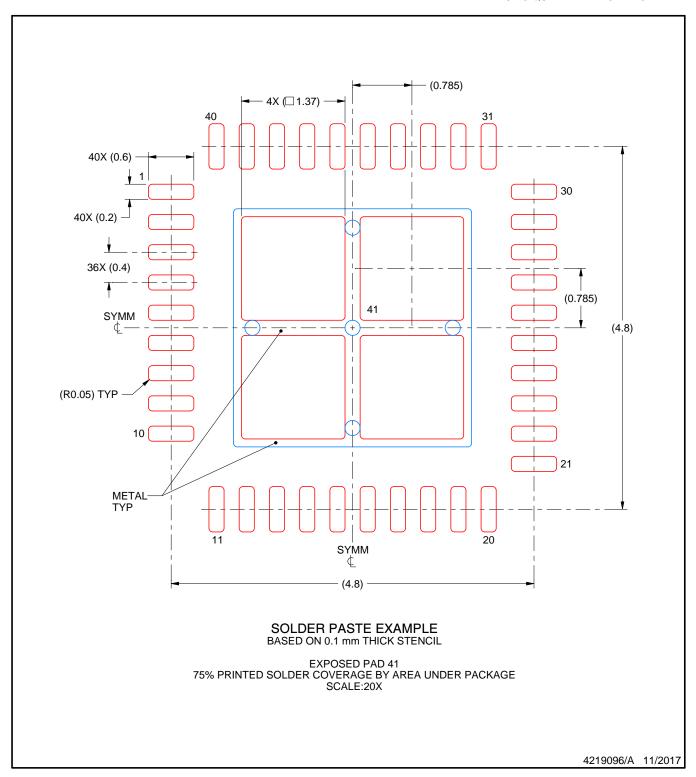

図 5-1. RSB (WQFN) Package, 40-Pin (Top View)

表 5-1. Pin Descriptions

| NAME NO.     |       | I/O | DESCRIPTION                                                                                                                                                                            |  |  |

|--------------|-------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|              |       |     | DESCRIPTION                                                                                                                                                                            |  |  |

| INPUT/REFER  | RENCE | •   |                                                                                                                                                                                        |  |  |

| AINM         | 13    | I   | Negative analog input, channel A                                                                                                                                                       |  |  |

| AINP         | 12    | I   | Positive analog input, channel A                                                                                                                                                       |  |  |

| BINP         | 39    | I   | Positive analog input, channel B                                                                                                                                                       |  |  |

| BINM         | 38    | I   | Negative analog input, channel B                                                                                                                                                       |  |  |

| REFBUF 4 I   |       | ı   | 1.2 V external voltage reference input for use with internal reference buffer. Internal 100 pull-up resistor to AVDD. This pin is also used to configure default operating conditions. |  |  |

| REFGND       | 3     | I   | Reference ground input, 0 V                                                                                                                                                            |  |  |

| VCM          | 8     | 0   | Common-mode voltage output for the analog inputs, 0.95V                                                                                                                                |  |  |

| VREF         | 2     | I   | External voltage reference input                                                                                                                                                       |  |  |

| CLOCK        | •     |     |                                                                                                                                                                                        |  |  |

| CLKM         | 7     | I   | Negative differential sampling clock input for the ADC                                                                                                                                 |  |  |

| CLKP         | 6     | I   | Positive differential sampling clock input for the ADC                                                                                                                                 |  |  |

| CONFIGURAT   | TION  | •   |                                                                                                                                                                                        |  |  |

| PDN/SYNC 1 I |       | I   | Power down/Synchronization input. This pin can be configured via the SPI interface. Actihigh. This pin has an internal 21 k $\Omega$ pull-down resistor.                               |  |  |

## 表 5-1. Pin Descriptions (continued)

| F                                                                         | PIN                                                                       | 1/0                                                             | DESCRIPTION                                                                                           |  |

|---------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|

| NAME                                                                      | NO.                                                                       | 1,0                                                             | DESCRIPTION                                                                                           |  |

| RESET                                                                     | 9                                                                         | I                                                               | Hardware reset. Active high. This pin has an internal 21 kΩ pull-down resistor.                       |  |

| SCLK                                                                      | 35                                                                        | I                                                               | Serial interface clock input. This pin has an internal 21 kΩ pull-down resistor.                      |  |

| SDIO                                                                      | 10                                                                        | I                                                               | Serial interface data input and output. This pin has an internal 21 kΩ pull-down resistor.            |  |

| SEN                                                                       | 16                                                                        | I                                                               | Serial interface enable. Active low. This pin has an internal 21 k $\Omega$ pull-up resistor to AVDD. |  |

| NC                                                                        | 27                                                                        | -                                                               | Do not connect                                                                                        |  |

| DIGITAL INTE                                                              | RFACE                                                                     |                                                                 |                                                                                                       |  |

| DA0P                                                                      | 20                                                                        | 0                                                               | Positive differential serial LVDS output for lane 0, channel A.                                       |  |

| DA0M                                                                      | 19 O Negative differential serial LVDS output for lane 0, channel A.      |                                                                 |                                                                                                       |  |

| DA1P                                                                      | DA1P 18 O Positive differential serial LVDS output for lane 1, channel A. |                                                                 |                                                                                                       |  |

| DA1M 17 O Negative differential serial LVDS output for lane 1, channel A. |                                                                           | Negative differential serial LVDS output for lane 1, channel A. |                                                                                                       |  |

| DB0P                                                                      | 31                                                                        | 0                                                               | Positive differential serial LVDS output for lane 0, channel B.                                       |  |

| DB0M                                                                      | 32                                                                        | 0                                                               | Negative differential serial LVDS output for lane 0, channel B.                                       |  |

| DB1P                                                                      | 33                                                                        | 0                                                               | Positive differential serial LVDS output for lane 1, channel B.                                       |  |

| DB1M                                                                      | 34                                                                        | 0                                                               | Negative differential serial LVDS output for lane 1, channel B.                                       |  |

| DCLKP                                                                     | 23                                                                        | 0                                                               | Positive differential serial LVDS bit clock output.                                                   |  |

| DCLKM                                                                     | 22                                                                        | 0                                                               | Negative differential serial LVDS bit clock output.                                                   |  |

| FCLKP                                                                     | 28                                                                        | 0                                                               | Positive differential serial LVDS frame clock output.                                                 |  |

| FCLKM                                                                     | 29                                                                        | 0                                                               | Negative differential serial LVDS frame clock output.                                                 |  |

| DCLKINP                                                                   | 25                                                                        | I                                                               | Positive differential serial LVDS bit clock input. Internal 100 $\Omega$ differential termination.    |  |

| DCLKINM                                                                   | 24                                                                        | I                                                               | Negative differential serial LVDS bit clock input. Internal 100 $\Omega$ differential termination.    |  |

| POWER SUPPLY                                                              |                                                                           |                                                                 |                                                                                                       |  |

| AVDD 5,15,36 I                                                            |                                                                           | I                                                               | Analog 1.8-V power supply                                                                             |  |

| GND 11,14,37,40, PowerPAD I                                               |                                                                           | I                                                               | Ground, 0 V                                                                                           |  |

| IOGND                                                                     | 26                                                                        | I                                                               | Ground, 0 V for digital interface                                                                     |  |

| IOVDD                                                                     | 21,30                                                                     | I                                                               | 1.8-V power supply for digital interface                                                              |  |

|                                                                           |                                                                           |                                                                 | I .                                                                                                   |  |

# **6 Specifications**

## **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1)

| - · · · · · · · · · · · · · · · · · · ·    |                                                 |      |     |      |  |  |  |  |

|--------------------------------------------|-------------------------------------------------|------|-----|------|--|--|--|--|

| PARAMETER                                  | TEST CONDITIONS                                 | MIN  | MAX | UNIT |  |  |  |  |

| Supply voltage rang                        | ge, AVDD, IOVDD                                 | -0.3 | 2.1 | V    |  |  |  |  |

| Supply voltage rang                        | upply voltage range, GND, IOGND, REFGND         |      |     | V    |  |  |  |  |

| Voltage applied to                         | AINP/M, BINP/M, CLKP/M, DCLKINP/M, VREF, REFBUF | -0.3 | 2.1 | V    |  |  |  |  |

| pput pins PDN/SYNC, RESET, SCLK, SEN, SDIO | PDN/SYNC, RESET, SCLK, SEN, SDIO                | -0.3 | 2.1 | V    |  |  |  |  |

| Junction temperatu                         | unction temperature, T <sub>J</sub>             |      | 105 | °C   |  |  |  |  |

| Storage temperatur                         | re, T <sub>stg</sub>                            | -65  | 150 | °C   |  |  |  |  |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |               |                                                                                          | VALUE | UNIT |

|--------------------|---------------|------------------------------------------------------------------------------------------|-------|------|

|                    | Electrostatic | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | 2500  |      |

| V <sub>(ESD)</sub> | discharge     | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | 1000  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                | ,                              | MIN  | NOM | MAX                | UNIT |

|----------------|--------------------------------|------|-----|--------------------|------|

| Supply         | AVDD <sup>(1)</sup>            | 1.75 | 1.8 | 1.85               | V    |

| voltage range  | IOVDD <sup>(1)</sup>           | 1.75 | 1.8 | 1.85               | V    |

| T <sub>A</sub> | Operating free-air temperature | -40  |     | 105                | °C   |

| TJ             | Operating junction temperature |      |     | 105 <sup>(2)</sup> | °C   |

- Measured to GND.

- (2) Prolonged use above this junction temperature may increase the device failure-in-time (FIT) rate.

## 6.4 Thermal Information

|                       |                                              | ADC3664   |      |

|-----------------------|----------------------------------------------|-----------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RSB (QFN) | UNIT |

|                       |                                              | 40 Pins   |      |

| R <sub>OJA</sub>      | Junction-to-ambient thermal resistance       | 30.7      | °C/W |

| R <sub>OJC(top)</sub> | Junction-to-case (top) thermal resistance    | 16.4      | °C/W |

| R <sub>⊝JB</sub>      | Junction-to-board thermal resistance         | 10.5      | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.2       | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 10.5      | °C/W |

| R <sub>OJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.0       | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

# **6.5 Electrical Characteristics - Power Consumption**

Typical values are over the operating free-air temperature range, at  $T_A$  = 25°C, full temperature range is  $T_{MIN}$  = -40°C to  $T_{MAX}$  = 105°C, ADC sampling rate = 125 MSPS, 50% clock duty cycle, AVDD = IOVDD = 1.8 V, external 1.6V reference, and -1-dBFS differential input, unless otherwise noted

|                    | PARAMETER                                                          | TEST CONDITIONS                          | MIN | TYP | MAX | UNIT |

|--------------------|--------------------------------------------------------------------|------------------------------------------|-----|-----|-----|------|

| ADC3664:           | 125 MSPS                                                           |                                          |     |     |     |      |

| I <sub>AVDD</sub>  | Analog supply current                                              | External reference                       |     | 64  | 80  | mA   |

| I <sub>IOVDD</sub> | I/O supply current                                                 | SLVDS 2-wire                             |     | 47  | 72  | MA   |

| P <sub>DIS</sub>   | Power dissipation                                                  | External reference, 2-wire               |     | 200 | 274 | mW   |

|                    |                                                                    | 2-wire, 1/2-swing                        |     | 35  |     |      |

|                    |                                                                    | 4x real decimation, 16-bit, 1-wire       |     | 50  |     |      |

|                    |                                                                    | 16x real decimation, 16-bit, 1-wire      |     | 45  |     |      |

|                    |                                                                    | 16x real decimation, 16-bit, 1/2-wire    |     | 41  |     | mA   |

|                    |                                                                    | 4x complex decimation, 16-bit, 1-wire    |     | 57  |     |      |

| I <sub>IOVDD</sub> | I/O supply current                                                 | 8x complex decimation, 16-bit, 1-wire    |     | 54  |     |      |

|                    |                                                                    | 8x complex decimation, 16-bit, 1/2-wire  |     | 50  |     |      |

|                    |                                                                    | 16x complex decimation, 16-bit, 1-wire   |     | 50  |     |      |

|                    |                                                                    | 16x complex decimation, 16-bit, 1/2-wire |     | 47  |     |      |

|                    |                                                                    | 32x complex decimation, 16-bit, 1-wire   |     | 48  |     |      |

|                    |                                                                    | 32x complex decimation, 16-bit, 1/2-wire |     | 43  |     |      |

| MISCELLA           | NOUS                                                               |                                          |     |     |     |      |

|                    | Internal reference, additional analog supply current               |                                          |     | 4   |     |      |

| I <sub>AVDD</sub>  | External 1.2V reference (REFBUF), additional analog supply current | Enabled via SPI                          |     | 0.5 |     | mA   |

|                    | Single ended clock input, reduces analog supply current by         |                                          |     | 1   |     |      |

| P <sub>DIS</sub>   | Power consumption in global power down mode                        | Default mask settings                    |     | 12  |     | mW   |

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

# 6.6 Electrical Characteristics - DC Specifications

|                                           | PARAMETER                           | TEST CONDITIONS         | MIN   | TYP    | MAX  | UNIT   |

|-------------------------------------------|-------------------------------------|-------------------------|-------|--------|------|--------|

| DC ACCURA                                 | ACY                                 |                         |       |        |      |        |

| No missing o                              | codes                               |                         | 14    |        |      | bits   |

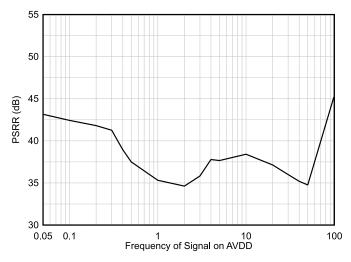

| PSRR                                      |                                     | F <sub>IN</sub> = 1 MHz |       | 35     |      | dB     |

| DNL                                       | Differential nonlinearity           | F <sub>IN</sub> = 5 MHz | -0.97 | ± 0.9  | 0.97 | LSB    |

| INL                                       | Integral nonlinearity               | F <sub>IN</sub> = 5 MHz | -7.5  | ± 2.6  | 7.5  | LSB    |

| V <sub>OS_ERR</sub>                       | Offset error                        |                         | -55   | ± 30   | 55   | LSB    |

| V <sub>OS_DRIFT</sub>                     | Offset drift over temperature       |                         |       | ± 0.06 |      | LSB/°C |

| GAIN <sub>ERR</sub>                       | Gain error                          | External 1.6V Reference |       | ± 2    |      | %FSR   |

| GAIN <sub>DRIFT</sub>                     | Gain drift over temperature         | External 1.6V Reference |       | ± 57   |      | ppm/°C |

| GAIN <sub>ERR</sub>                       | Gain error                          | Internal Reference      |       | ± 3    |      | %FSR   |

| GAIN <sub>DRIFT</sub>                     | Gain drift over temperature         | Internal Reference      |       | 106    |      | ppm/°C |

| Transition No                             | oise                                |                         |       | 0.7    |      | LSB    |

| ADC ANALO                                 | OG INPUT (AINP/M, BINP/M)           |                         |       |        |      |        |

| FS                                        | Input full scale                    | Differential            |       | 3.2    |      | Vpp    |

| V <sub>CM</sub>                           | Input common model voltage          |                         | 0.9   | 0.95   | 1.0  | V      |

| R <sub>IN</sub>                           | Input resistance                    | Differential at DC      |       | 8      |      | kΩ     |

| C <sub>IN</sub>                           | Input Capacitance                   | Differential at DC      |       | 5.4    |      | pF     |

| $V_{OCM}$                                 | Output common mode voltage          |                         |       | 0.95   |      | V      |

| BW                                        | Analog Input Bandwidth (-3dB)       |                         |       | 1.4    |      | GHz    |

| Internal Volt                             | age Reference                       |                         |       |        |      |        |

| $V_{REF}$                                 | Internal reference voltage          |                         |       | 1.6    |      | V      |

| V <sub>REF</sub> Output                   | Impedance                           |                         |       | 8      |      | Ω      |

| Reference I                               | nput Buffer (REFBUF)                |                         |       |        | ·    |        |

| External refe                             | rence voltage                       |                         |       | 1.2    |      | V      |

| External vol                              | tage reference (VREF)               |                         |       |        | ·    |        |

| $V_{REF}$                                 | External voltage reference          |                         |       | 1.6    |      | V      |

| Input Curren                              | t                                   |                         |       | 1      |      | mA     |

| Input impeda                              | ance                                |                         |       | 5.3    |      | kΩ     |

| Clock Input                               | (CLKP/M)                            |                         |       |        |      |        |

| Input clock fr                            | raguancy                            | External reference      | 0.5   |        | 125  | MHz    |

| iliput clock ii                           | equency                             | Internal reference      | 100   |        | 125  | MHz    |

| V <sub>ID</sub>                           | Differential input voltage          |                         |       | 1      | 3.6  | Vpp    |

| V <sub>CM</sub> Input common mode voltage |                                     |                         |       | 0.9    |      | V      |

| R <sub>IN</sub>                           | Single ended input resistance to co | mmon mode               |       | 5      |      | kΩ     |

| C <sub>IN</sub>                           | Single ended input capacitance      |                         |       | 1.5    |      | pF     |

| Clock duty c                              | ycle                                |                         | 45    | 50     | 60   | %      |

# **6.6 Electrical Characteristics - DC Specifications (continued)**

|                  | PARAMETER                          | TEST CONDITIONS               | MIN            | TYP   | MAX      | UNIT |

|------------------|------------------------------------|-------------------------------|----------------|-------|----------|------|

| Digital In       | puts (RESET, PDN, SCLK, SEN, SDIO) |                               |                |       | <u> </u> |      |

| V <sub>IH</sub>  | High level input voltage           |                               | 1.4            |       |          | V    |

| V <sub>IL</sub>  | Low level input voltage            |                               |                |       | 0.4      | V    |

| I <sub>IH</sub>  | High level input current           |                               |                | 90    | 150      | uA   |

| I <sub>IL</sub>  | Low level input current            |                               | -150           | -90   |          | uA   |

| Cı               | Input capacitance                  |                               |                | 1.5   |          | pF   |

| Digital O        | utput (SDOUT)                      |                               | <u>'</u>       |       |          |      |

| V <sub>OH</sub>  | High level output voltage          | I <sub>LOAD</sub> = -400 uA   | IOVDD<br>- 0.1 | IOVDD |          | V    |

| V <sub>OL</sub>  | Low level output voltage           | I <sub>LOAD</sub> = 400 uA    |                |       | 0.1      |      |

| SLVDS Ir         | nterface                           |                               |                |       |          |      |

| V <sub>ID</sub>  | Differential input voltage         | DCLKIN                        | 200            | 350   | 650      | mVpp |

| V <sub>CM</sub>  | Input common mode voltage          | DCLKIN                        | 1              | 1.2   | 1.3      | V    |

| Output data rate |                                    | per differential SLVDS output |                |       | 1        | Gbps |

| V <sub>OD</sub>  | Differential output voltage        |                               | 500            | 700   | 850      | mVpp |

| V <sub>CM</sub>  | Output common mode voltage         |                               |                | 1.0   |          | V    |

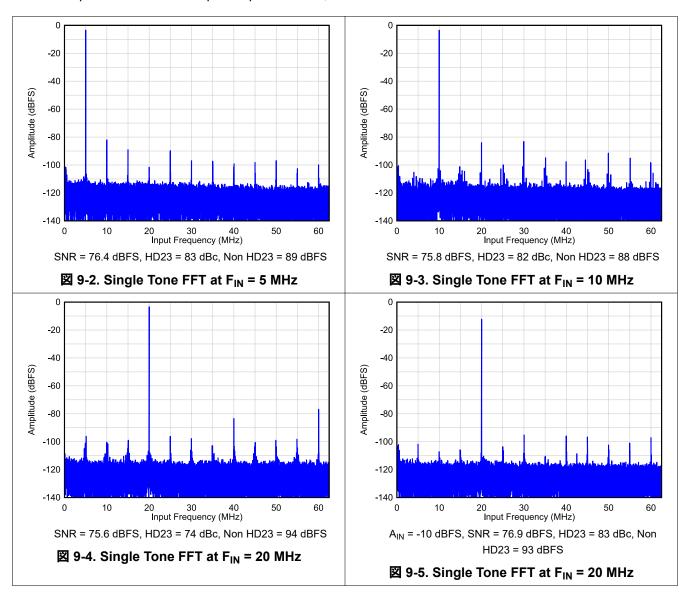

# 6.7 Electrical Characteristics - AC Specifications

|           | PARAMETER                                        | TEST CONDITIONS                                                                  | MIN  | TYP    | MAX | UNIT    |  |  |  |

|-----------|--------------------------------------------------|----------------------------------------------------------------------------------|------|--------|-----|---------|--|--|--|

| NSD       | Noise Spectral Density                           | f <sub>IN</sub> = 5 MHz, A <sub>IN</sub> = -20 dBFS                              |      | -156.9 |     | dBFS/Hz |  |  |  |

|           |                                                  | f <sub>IN</sub> = 5 MHz                                                          | 72   | 77.5   |     | dBFS    |  |  |  |

| SNR       |                                                  | f <sub>IN</sub> = 5 MHz, A <sub>IN</sub> = -20 dBFS                              |      | 78.9   |     |         |  |  |  |

|           |                                                  | f <sub>IN</sub> = 10 MHz                                                         |      | 77.6   |     |         |  |  |  |

|           | Signal to noise ratio                            | f <sub>IN</sub> = 40 MHz                                                         |      | 76.9   |     | dBFS    |  |  |  |

|           |                                                  | f <sub>IN</sub> = 70 MHz                                                         |      | 75.5   |     | ubi 3   |  |  |  |

|           |                                                  | f <sub>IN</sub> = 100 MHz                                                        |      | 74.1   |     | 1       |  |  |  |

|           |                                                  | f <sub>IN</sub> = 5 MHz                                                          |      | 75.7   |     |         |  |  |  |

|           |                                                  | f <sub>IN</sub> = 10 MHz                                                         |      | 74.2   |     |         |  |  |  |

| SINAD     | Signal to noise and distortion ratio             | f <sub>IN</sub> = 40 MHz                                                         |      | 72.6   |     | dBFS    |  |  |  |

|           |                                                  | f <sub>IN</sub> = 70 MHz                                                         |      | 71.3   |     |         |  |  |  |

|           |                                                  | f <sub>IN</sub> = 100 MHz                                                        |      | 72.4   |     |         |  |  |  |

|           |                                                  | f <sub>IN</sub> = 5 MHz                                                          |      | 12.6   |     |         |  |  |  |

|           |                                                  | f <sub>IN</sub> = 10 MHz                                                         |      | 12.6   |     |         |  |  |  |

| ENOB      | Effective number of bits                         | f <sub>IN</sub> = 40 MHz                                                         |      | 12.5   |     | bit     |  |  |  |

|           |                                                  | f <sub>IN</sub> = 70 MHz                                                         |      | 12.3   |     |         |  |  |  |

|           |                                                  | f <sub>IN</sub> = 100 MHz                                                        |      | 12.0   |     |         |  |  |  |

|           | Total Harmonic Distortion (First five harmonics) | f <sub>IN</sub> = 5 MHz                                                          | 71.5 | 80     |     | dBc     |  |  |  |

|           |                                                  | f <sub>IN</sub> = 10 MHz                                                         |      | 76     |     |         |  |  |  |

| HD        |                                                  | f <sub>IN</sub> = 40 MHz                                                         |      | 74     |     |         |  |  |  |

|           |                                                  | f <sub>IN</sub> = 70 MHz                                                         |      | 72     |     |         |  |  |  |

|           |                                                  | f <sub>IN</sub> = 100 MHz                                                        |      | 76     |     |         |  |  |  |

|           |                                                  | f <sub>IN</sub> = 5 MHz                                                          | 77   | 84     |     |         |  |  |  |

|           |                                                  | f <sub>IN</sub> = 10 MHz                                                         |      | 78     |     |         |  |  |  |

| HD2       | Second Harmonic Distortion                       | f <sub>IN</sub> = 40 MHz                                                         |      | 75     |     | dBc     |  |  |  |

|           |                                                  | f <sub>IN</sub> = 70 MHz                                                         |      | 77     |     |         |  |  |  |

|           |                                                  | f <sub>IN</sub> = 100 MHz                                                        |      | 79     |     |         |  |  |  |

|           |                                                  | f <sub>IN</sub> = 5 MHz                                                          | 73.5 | 84     |     |         |  |  |  |

|           |                                                  | f <sub>IN</sub> = 10 MHz                                                         |      | 81     |     |         |  |  |  |

| HD3       | Third Harmonic Distortion                        | f <sub>IN</sub> = 40 MHz                                                         |      | 88     |     | dBc     |  |  |  |

|           |                                                  | f <sub>IN</sub> = 70 MHz                                                         |      | 76     |     |         |  |  |  |

|           |                                                  | f <sub>IN</sub> = 100 MHz                                                        |      | 81     |     |         |  |  |  |

|           |                                                  | f <sub>IN</sub> = 5 MHz                                                          | 84   | 92     |     |         |  |  |  |

|           |                                                  | f <sub>IN</sub> = 10 MHz                                                         |      | 93     |     |         |  |  |  |

| Non HD2,3 | Spur free dynamic range (excluding HD2 and HD3)  | f <sub>IN</sub> = 40 MHz                                                         |      | 89     |     | dBFS    |  |  |  |

|           | TIDZ AIRI FIDS)                                  | f <sub>IN</sub> = 70 MHz                                                         |      | 84     |     |         |  |  |  |

|           |                                                  | f <sub>IN</sub> = 100 MHz                                                        |      | 86     |     |         |  |  |  |

| MD3       | Two tone inter-modulation distortion             | f <sub>1</sub> = 10 MHz, f <sub>2</sub> = 12 MHz, A <sub>IN</sub> = -7 dBFS/tone |      | 88     |     | dBc     |  |  |  |

# 6.8 Timing Requirements

Typical values are over the operating free-air temperature range, at  $T_A$  = 25°C, full temperature range is  $T_{MIN}$  = -40°C to  $T_{MAX}$  = 105°C, ADC sampling rate = 125 MSPS, 50% clock duty cycle, AVDD = IOVDD = 1.8 V, 1.6 V external reference, and -1-dBFS differential input, unless otherwise noted

|                                           | PARAMETER                                                                    | TEST CONDITIONS                                                                                                                                                                     | MIN NOM MAX                                           | UNIT                        |  |

|-------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------|--|

| ADC Timi                                  | ng Specifications                                                            |                                                                                                                                                                                     | <u>'</u>                                              |                             |  |

| t <sub>AD</sub>                           | Aperture Delay                                                               |                                                                                                                                                                                     | 0.85                                                  | ns                          |  |

| t <sub>A</sub>                            | Aperture Jitter                                                              | square wave clock with fast edges                                                                                                                                                   | 250                                                   | fs                          |  |

| t <sub>J</sub>                            | Jitter on DCLKIN                                                             |                                                                                                                                                                                     | ± 50                                                  | ps pk-pk                    |  |

| Recory time from +6 dB overload condition |                                                                              | SNR within 1 dB of expected value                                                                                                                                                   | 1                                                     | Clock<br>cycle              |  |

| t <sub>ACQ</sub>                          | Signal acquisition period                                                    | referenced to sampling clock falling edge                                                                                                                                           | -T <sub>S</sub> /4                                    | Sampling<br>clock<br>period |  |

| t <sub>CONV</sub>                         | Signal conversion period                                                     |                                                                                                                                                                                     | 6                                                     | ns                          |  |

|                                           |                                                                              | Bandgap reference enabled, single ended clock                                                                                                                                       | 13                                                    |                             |  |

| Wake up                                   | Time to valid data after coming out of                                       | Bandgap reference enabled, differential clock                                                                                                                                       | 15                                                    | us                          |  |

|                                           | power down. Internal reference.                                              | Bandgap reference disabled, single ended clock                                                                                                                                      | 2.4                                                   | mo                          |  |

|                                           |                                                                              | Bandgap reference disabled, differential clock                                                                                                                                      | 2.3                                                   | ms                          |  |

| time                                      |                                                                              | Bandgap reference enabled, single ended clock                                                                                                                                       | 13                                                    |                             |  |

|                                           | Time to valid data after coming out of power down.  External 1.6V reference. | Bandgap reference enabled, differential clock                                                                                                                                       | 14                                                    | us                          |  |

|                                           |                                                                              | Bandgap reference disabled, single ended clock                                                                                                                                      | 2.0                                                   |                             |  |

|                                           |                                                                              | Bandgap reference disabled, differential clock                                                                                                                                      | 2.2                                                   | ms                          |  |

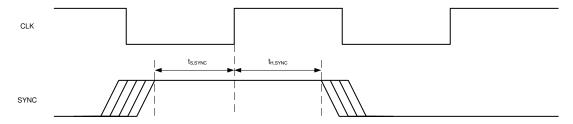

| t <sub>S,SYNC</sub>                       | Setup time for SYNC input signal                                             | Deferenced to compling clock rising adds                                                                                                                                            | 500                                                   |                             |  |

| t <sub>H,SYNC</sub>                       | Hold time for SYNC input signal                                              | Referenced to sampling clock rising edge                                                                                                                                            | 600                                                   | ps                          |  |

|                                           |                                                                              | 1/2-wire SLVDS                                                                                                                                                                      | 1                                                     |                             |  |

| ADC<br>Latency                            | Signal input to data output                                                  | 1-wire SLVDS                                                                                                                                                                        | 1                                                     | Clock<br>cycles             |  |

| Laterioy                                  |                                                                              | 2-wire SLVDS                                                                                                                                                                        | 2                                                     |                             |  |

|                                           | Real decimation by 2                                                         |                                                                                                                                                                                     | 21                                                    | _                           |  |

| Add.                                      | Complex decimation by 2                                                      |                                                                                                                                                                                     | 22                                                    | Output clock                |  |

| Latency                                   | Real or complex decimation by 4, 8, 16, 32                                   |                                                                                                                                                                                     | 23                                                    | cycles                      |  |

| Interface                                 | Timing: Serial LVDS Interface                                                |                                                                                                                                                                                     |                                                       |                             |  |

|                                           | Propagation delay: sampling clock falling edge to DCLK rising edge           | Delay between sampling clock falling edge to DCLKIN falling edge < 2.5ns.  T <sub>DCLK</sub> = DCLK period t <sub>CDCLK</sub> = Sampling clock falling edge to DCLKIN falling edge  | 2+ 3+ 4+ TDCLK TDCLK TDCLK + + + tCDCLK tCDCLK tCDCLK |                             |  |

| t <sub>PD</sub>                           |                                                                              | Delay between sampling clock falling edge to DCLKIN falling edge >= 2.5ns.  T <sub>DCLK</sub> = DCLK period t <sub>CDCLK</sub> = Sampling clock falling edge to DCLKIN falling edge | 2+ 3+ 4+ tcdclk tcdclk tcdclk                         | - ns                        |  |

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

# 6.8 Timing Requirements (continued)

|                       | PARAMETER                                                    | TEST CONDITIONS                                      | MIN  | NOM | MAX  | UNIT |  |

|-----------------------|--------------------------------------------------------------|------------------------------------------------------|------|-----|------|------|--|

|                       | DCLK rising edge to output data                              | Fout = 65 MSPS, DA/B0,1 = 455 MBPS                   | 0    | 0.1 |      |      |  |

|                       | delay,                                                       | Fout = 80 MSPS, DA/B0,1 = 560 MBPS                   | 0    | 0.1 |      |      |  |

|                       | 2-wire SLVDS, 14-bit                                         | Fout = 125 MSPS, DA/B0,1 = 875 MBPS                  | -0.2 | 0.1 |      |      |  |

|                       | DCLK rising edge to output data delay, 1-wire SLVDS, 14-bit  | Fout = 65 MSPS, DA/B0 = 910 MBPS                     | 0    | 0.1 |      |      |  |

| $t_{CD}$              | DCLK rising edge to output data                              | Fout = 10 MSPS, DA/B0 = 160 MBPS                     | 0    | 0.1 |      | ns   |  |

|                       | delay,                                                       | Fout = 25 MSPS, DA/B0 = 400 MBPS                     | 0    | 0.1 |      |      |  |

|                       | 1-wire SLVDS, 16-bit                                         | Fout = 62.5 MSPS, DA/B0= 1000 MBPS                   | -0.6 | 0.1 |      |      |  |

|                       | DCLK rising edge to output data                              | Fout = 5 MSPS, DA0 = 160 MBPS                        | 0    | 0.1 |      |      |  |

|                       | delay,                                                       | Fout = 10 MSPS, DA0 = 320 MBPS                       | 0    | 0.1 |      |      |  |

|                       | 1/2-wire SLVDS, 16-bit                                       | Fout = 25 MSPS, DA0 = 800 MBPS                       | 0    | 0.1 |      |      |  |

|                       |                                                              | Fout = 65 MSPS, DA/B0,1 = 455 MBPS                   | 1.8  | 1.9 |      |      |  |

|                       | Data valid, 2-wire SLVDS, 14-bit                             | Fout = 80 MSPS, DA/B0,1 = 560 MBPS                   | 1.4  | 1.5 |      |      |  |

|                       |                                                              | Fout = 125 MSPS, DA/B0,1 = 875 MBPS                  | 0.6  | 8.0 |      |      |  |

|                       | Data valid, 1-wire SLVDS, 14-bit                             | Fout = 65 MSPS, DA/B0 = 910 MBPS                     | 0.6  | 8.0 |      |      |  |

|                       | Data valid, 1-wire SLVDS, 16-bit                             | Fout = 10 MSPS, DA/B0 = 160 MBPS                     | 5.7  | 5.8 |      | ns   |  |

| $t_{DV}$              |                                                              | Fout = 25 MSPS, DA/B0 = 400 MBPS                     | 2.0  | 2.1 |      |      |  |

|                       |                                                              | Fout = 62.5 MSPS, DA/B0= 1000 MBPS                   | 0.5  | 0.6 |      |      |  |

|                       | Data valid, 1/2-wire SLVDS, 16-bit                           | Fout = 5 MSPS, DA0 = 160 MBPS                        | 5.7  | 5.8 |      |      |  |

|                       |                                                              | Fout = 10 MSPS, DA0 = 320 MBPS                       | 2.7  | 2.8 |      | l    |  |

|                       |                                                              | Fout = 25 MSPS, DA0 = 800 MBPS                       | 0.8  | 0.9 |      |      |  |

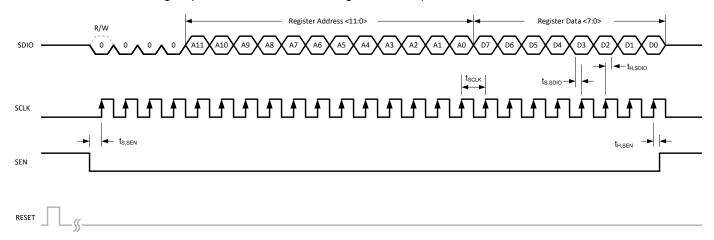

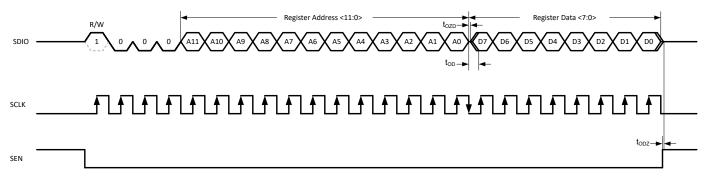

| SERIAL P              | ROGRAMMING INTERFACE (SCLK,                                  | SEN, SDIO) - Input                                   |      |     |      |      |  |

| f <sub>CLK,SCLK</sub> | Serial clock frequency                                       |                                                      |      |     | 20   | MHz  |  |

| t <sub>S,SEN</sub>    | SEN falling edge to SCLK rising edge                         |                                                      | 10   |     |      |      |  |

| t <sub>H,SEN</sub>    | SCLK rising edge to SEN rising edge                          |                                                      | 9    |     |      | ns   |  |

| t <sub>S,SDIO</sub>   | SDIO setup time from rising edge of SCLK                     |                                                      | 17   |     |      | 113  |  |

| t <sub>H,SDIO</sub>   | SDIO hold time from rising edge of SCLK                      |                                                      |      |     |      |      |  |

| SERIAL P              | ROGRAMMING INTERFACE (SDIO)                                  | Output                                               |      |     |      |      |  |

| t <sub>OZD</sub>      | Delay from falling edge of 16th SCLK tri-state to valid data | cycle during read operation for SDIO transition from | 3.9  |     | 10.8 |      |  |

| t <sub>ODZ</sub>      | Delay from SEN rising edge for SDIO                          | transition from valid data to tri-state              | 3.4  |     | 14   | ns   |  |

| t <sub>OD</sub>       | Delay from falling edge of 16th SCLK                         | cycle during read operation to SDIO valid            | 3.9  |     | 10.8 |      |  |

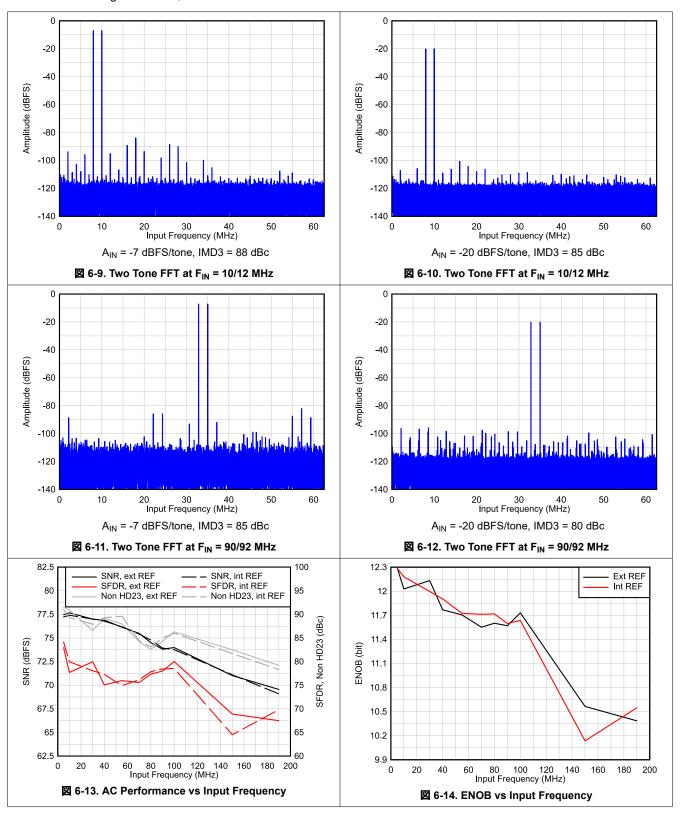

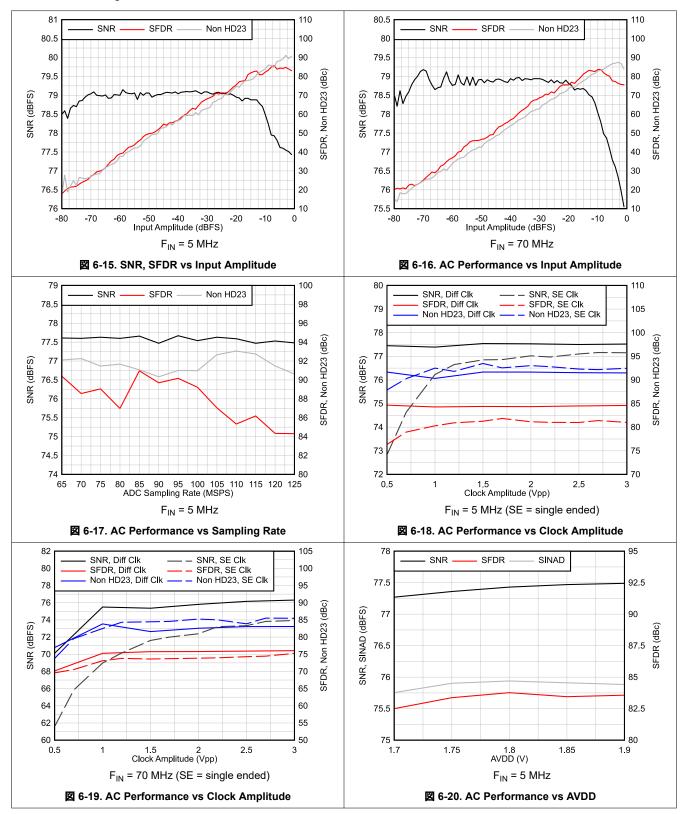

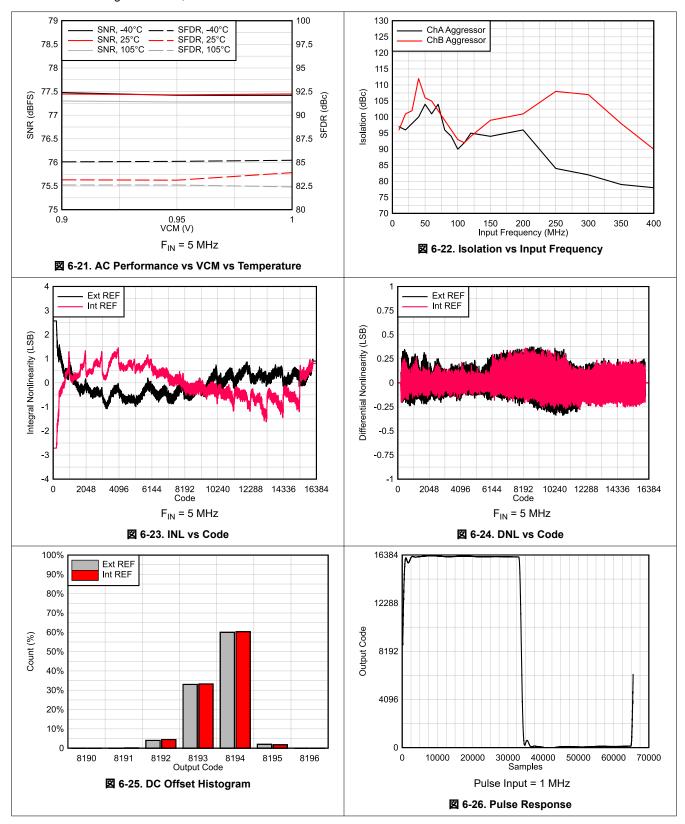

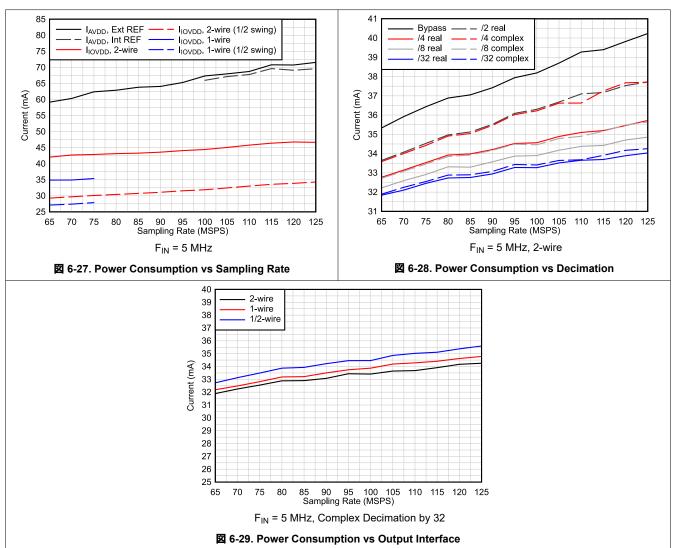

## **6.9 Typical Characteristics**

## 7 Parameter Measurement Information

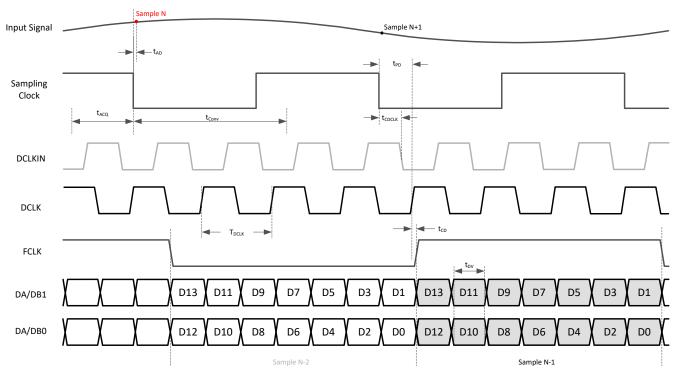

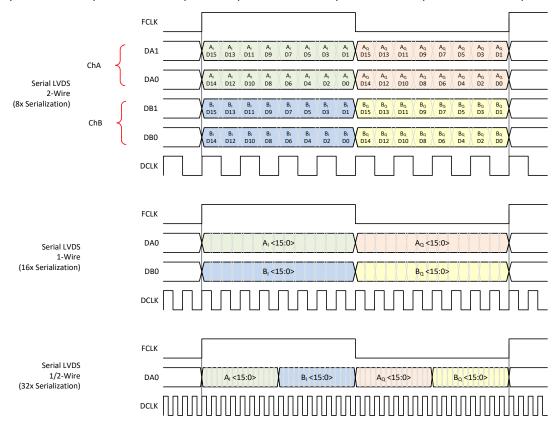

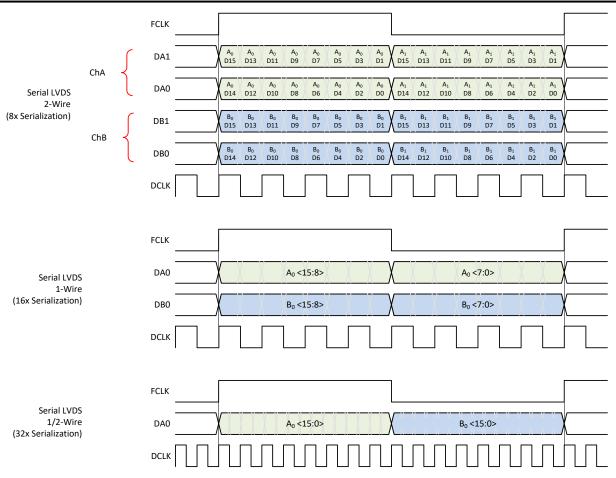

図 7-1. Timing diagram: 2-wire SLVDS

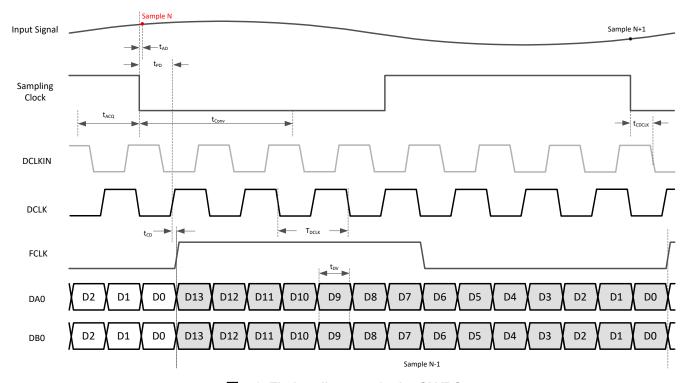

図 7-2. Timing diagram: 1-wire SLVDS

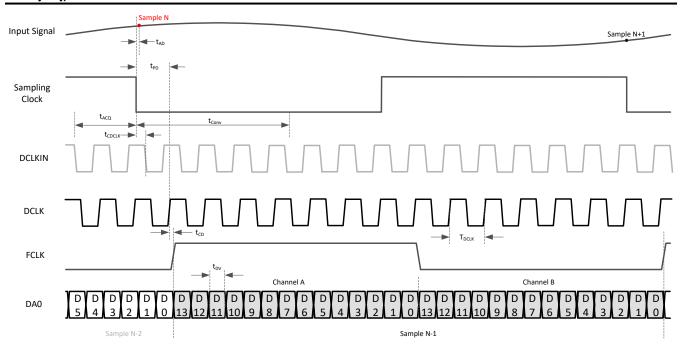

図 7-3. Timing diagram: 1/2-wire SLVDS

## 8 Detailed Description

## 8.1 Overview

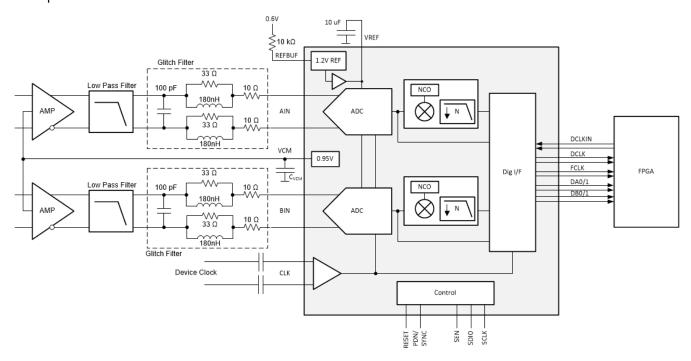

The ADC3664 is a low noise, ultra-low power 14-bit high-speed dual channel ADC supporting sampling rates up to 125 MSPS. It offers very good DC precision together with IF sampling support which makes it ideally suited for a wide range of applications. The ADC3664 is equipped with an on-chip internal reference option but it also supports the use of an external, high precision 1.6V voltage reference or an external 1.2V reference which is buffered and gained up internally. Because of the inherent low latency architecture, the digital output result is available after as low as one clock cycle on the digital output interface.

注

The ADC3664 supports the following sampling rates:

- External Reference: 65 to 125 MSPS

- Internal Reference: 100 to 125 MSPS

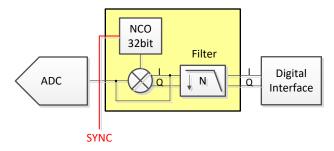

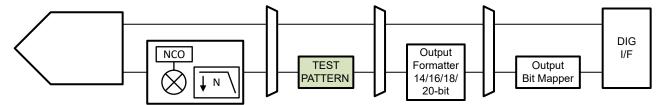

An optional programmable digital down converter enables external anti-alias filter relaxation as well as output data rate reduction. The digital filter provides a 32-bit programmable NCO and supports both real or complex decimation.

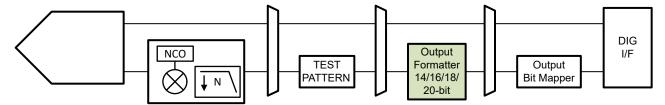

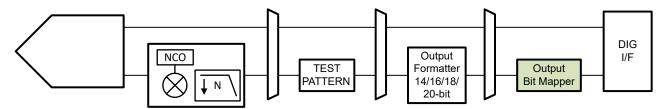

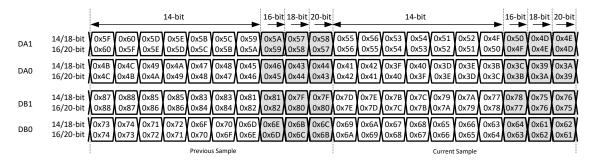

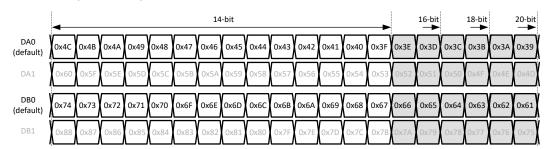

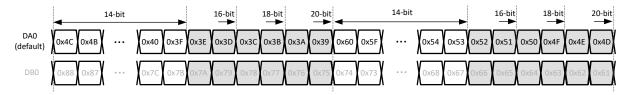

The ADC3664 uses a serial LVDS (SLVDS) interface to output the data which minimizes the number of digital interconnects. The device supports a two-lane (2-wire), a one-lane (1-wire) and a half-lane (1/2-wire) option. The ADC3664 includes a digital output formatter which supports output resolutions from 14 to 20-bit.

The device features and control options can be set up either through pin configurations or via SPI register writes.

## 8.2 Functional Block Diagram

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

## 8.3 Feature Description

### 8.3.1 Analog Input

The analog inputs of ADC3664 are intended to be driven differentially. Both AC coupling and DC coupling of the analog inputs is supported. The analog inputs are designed for an input common mode voltage of 0.95 V which must be provided externally on each input pin. DC-coupled input signals must have a common mode voltage that meets the device input common mode voltage range.

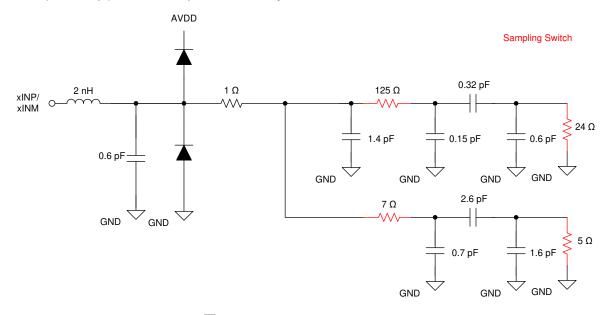

The equivalent input network diagram is shown in 🗵 8-1. All four sampling switches, on-resistance shown in red are in same position (open or closed) simultaneously.

図 8-1. Equivalent Input Network

## 8.3.1.1 Analog Input Bandwidth

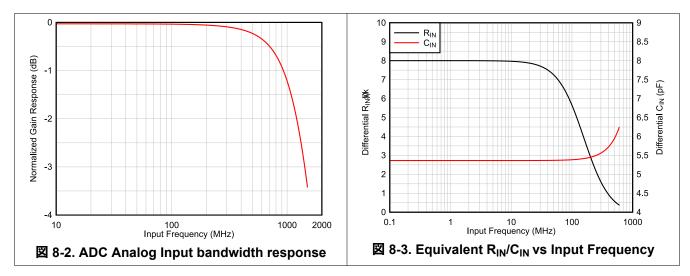

$\boxtimes$  8-2 shows the analog full power input bandwidth of the ADC3664 with a 50  $\Omega$  differential termination. The -3 dB bandwidth is approximately 1.4 GHz and the useful input bandwidth with good AC performance is approximately 200 MHz.

The equivalent differential input resistance  $R_{IN}$  and input capacitance  $C_{IN}$  vs frequency are shown in  $\boxtimes$  8-3.

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

### 8.3.1.2 Analog Front End Design

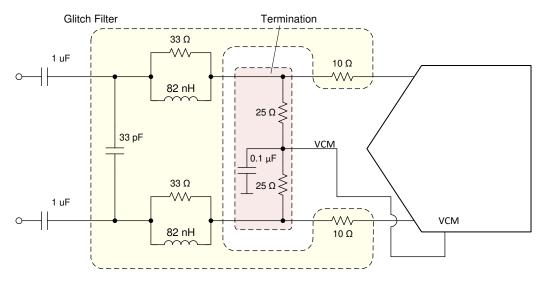

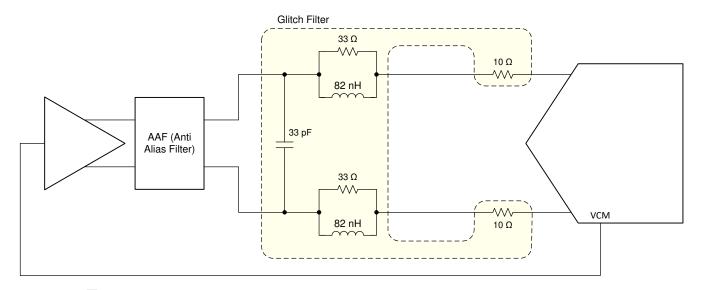

The ADC3664 is an unbuffered ADC and thus a passive kick-back filter is recommended to absorb the glitch from the sampling operation. Depending on if the input is driven by a balun or a differential amplifier with low output impedance, a termination network may be needed. Additionally a passive DC bias circuit is needed in AC-coupled applications which can be combined with the termination network.

## 8.3.1.2.1 Sampling Glitch Filter Design

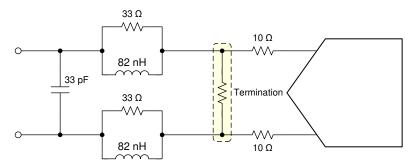

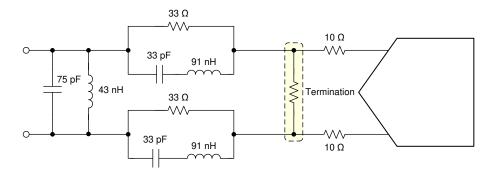

The front end sampling glitch filter is designed to optimize the SNR and HD3 performance of the ADC. The filter performance is dependent on input frequency and therefore the following filter designs are recommended for different input frequency ranges as shown in  $\boxtimes$  8-4 and  $\boxtimes$  8-5 (assuming 50  $\Omega$  source impedance).

図 8-4. Sampling glitch filter example for input frequencies from DC to 60 MHz

図 8-5. Sampling glitch filter example for input frequencies from 60 to 120 MHz

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

## 8.3.1.2.2 Analog Input Termination and DC Bias

Depending on the input drive circuitry, a termination network and/or DC biasing needs to be provided.

#### 8.3.1.2.2.1 AC-Coupling

The ADC3664 requires external DC bias using the common mode output voltage (VCM) of the ADC together with the termination network as shown in  $\boxtimes$  8-6. The termination is located within the glitch filter network. When using a balun on the input, the termination impedance has to be adjusted to account for the turns ratio of the transformer. When using an amplifier, the termination impedance can be adjusted to optimize the amplifier performance.

図 8-6. AC-Coupling: termination network provides DC bias (glitch filter example for up to 60 MHz)

## 8.3.1.2.2.2 DC-Coupling

In DC coupled applications the DC bias needs to be provided from the fully differential amplifier (FDA) using VCM output of the ADC as shown in 🗵 8-7. The glitch filter in this case is located between the anti-alias filter and the ADC. No termination may be needed if amplifier is located close to the ADC or if the termination is part of the anti-alias filter.

図 8-7. DC-Coupling: DC bias provided by FDA (glitch filter example for DC - 60 MHz)

### 8.3.2 Clock Input

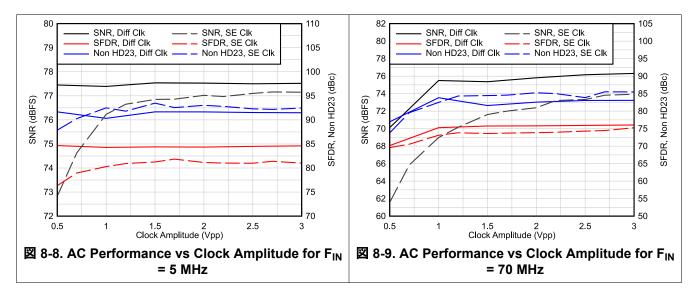

In order to maximize the ADC SNR performance, the external sampling clock should be low jitter and differential signaling with a high slew rate. This is especially important in IF sampling applications ( $\boxtimes$  8-8 and  $\boxtimes$  8-9). For less jitter sensitive applications, the ADC3664 provides the option to operate with single ended signaling which saves additional power consumption.

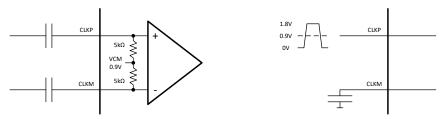

## 8.3.2.1 Single Ended vs Differential Clock Input

The ADC3664 can be operated using a differential or a single ended clock input where the single ended clock consumes less power consumption. However clock amplitude impacts the ADC aperture jitter and consequently the SNR. For maximum SNR performance, a large clock signal with fast slew rates needs to be provided.

- Differential Clock Input: The clock input can be AC coupled externally. The ADC3664 provides internal biasing for that use case.

- Single Ended Clock Input: This mode needs to be configured using SPI register (0x0E, D2 and D0) or with the REFBUF pin. In this mode there is no internal clock biasing and thus the clock input needs to be DC coupled around a 0.9V center. The unused input needs to be AC coupled to ground.

図 8-10. External and internal connection using differential (left) and single ended (right) clock input

## 8.3.3 Voltage Reference

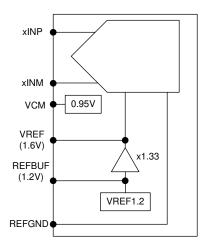

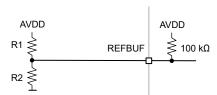

The ADC3664 provides three different options for supplying the voltage reference to the ADC. An external 1.6V reference can be directly connected to the VREF input; a voltage 1.2V reference can be connected to the REFBUF input using the internal gain buffer or the internal 1.2V reference can be enabled to generate a 1.6V reference voltage. For best performance, the reference noise should be filtered by connecting a 10 uF and a 0.1 uF ceramic bypass capacitor to the VREF pin. The internal reference circuitry of the ADC3664 is shown in  $\boxtimes$  8-11.

注

The voltage reference mode can be selected using SPI writes or by using the REFBUF pin (default) as a control pin (セクション 8.5.1). If the REFBUF pin is not used for configuration, the REFBUF pin should be connected to AVDD (even though the REFBUF pin has a weak internal pullup to AVDD) and the voltage reference option has to be selected using the SPI interface.

図 8-11. Different voltage reference options for ADC3664

#### 8.3.3.1 Internal voltage reference

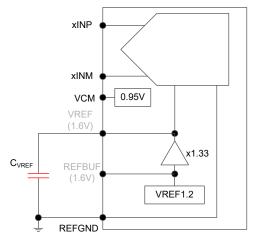

The 1.6V reference for the ADC can be generated internal using the on-chip 1.2V reference along with the internal gain buffer. A 10 uF and a 0.1 uF ceramic bypass capacitor ( $C_{VREF}$ ) should be connected between the VREF and REFGND pins as close to the pins as possible.

図 8-12. Internal reference

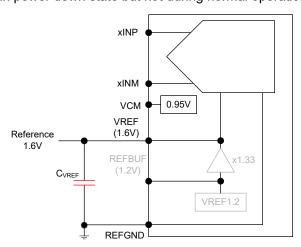

### 8.3.3.2 External voltage reference (VREF)

For highest accuracy and lowest temperature drift, the VREF input can be directly connected to an external 1.6V reference. A 10 uF and a 0.1 uF ceramic bypass capacitor ( $C_{VREF}$ ) should be connected between the VREF and REFGND pins and placed as close to the pins as possible is recommended. The load current from the external reference is about 1mA.

Note: The internal reference is also used for other functions inside the device, therefore the reference amplifier should only be powered down in power down state but not during normal operation.

図 8-13. External 1.6V reference

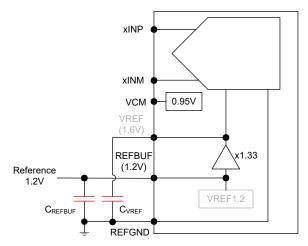

## 8.3.3.3 External voltage reference with internal buffer (REFBUF)

The ADC3664 is equipped with an on-chip reference buffer that also includes gain to generate the 1.6V reference voltage from an external 1.2V reference. A 10 uF and a 0.1 uF ceramic bypass capacitor ( $C_{VREF}$ ) between the VREF and REFGND pins and a 10 uF and a 0.1 uF ceramic bypass capacitor between the REFBUF and REFGND pins are recommended. Both capacitors should be placed as close to the pins as possible. The load current from the external reference is less than 100uA.

図 8-14. External 1.2V reference using internal reference buffer

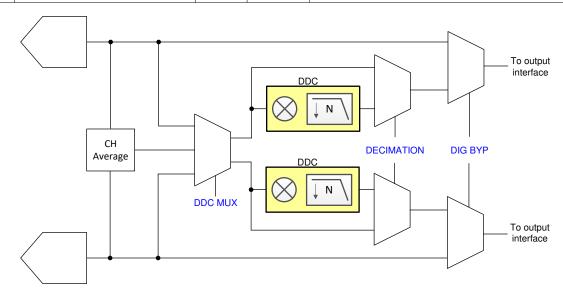

# 8.3.4 Digital Down Converter

The ADC3664 includes an optional on-chip digital down conversion (DDC) decimation filter that can be enabled via SPI register settings. It supports complex decimation by 2, 4, 8, 16 and 32 using a digital mixer and a 32-bit numerically controlled oscillator (NCO) as shown in 🗵 8-15. Furthermore it supports a mode with real decimation where the complex mixer is bypassed (NCO should be set to 0 for lowest power consumption) and the digital filter acts as a low pass filter.

Internally the decimation filter calculations are performed with a 20-bit resolution in order to avoid any SNR degradation due to quantization noise limitation. The Output Formatter truncates to the selected resolution prior to outputting the data on the digital interface.

図 8-15. Internal Digital Decimation Filter

#### 8.3.4.1 DDC MUX

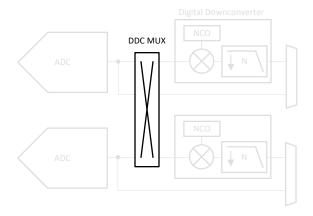

The ADC3664 contains a MUX in front of the digital decimation filter which allows the ADC channel A input to be connected to the DDC of channel B and vice versa.

図 8-16. DDC MUX

### 8.3.4.2 Digital Filter Operation

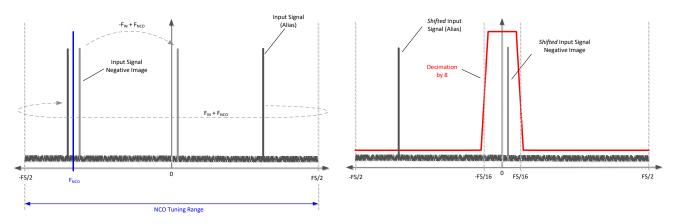

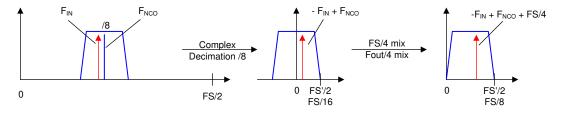

The complex decimation operation is illustrated with an example in  $\boxtimes$  8-17. First the input signal (and the negative image) are frequency shifted by the NCO frequency as shown on the left. Next a digital filter is applied (centered around 0 Hz) and the output data rate is decimated - in this example the output data rate  $F_{S,OUT} = F_S/8$  with a Nyquist zone of  $F_S/16$ . During the complex mixing the spectrum (signal and noise) is split into real and complex parts and thus the amplitude is reduced by 6-dB. In order to compensate this loss, there is a 6-dB digital gain option in the decimation filter block that can be enabled via SPI write.

図 8-17. Complex decimation illustration

The real decimation operation is illustrated with an example in  $\boxtimes$  8-18. There is no frequency shift happening and only the real portion of the complex digital filter is exercised. The output data rate is decimated - a decimation of 8 would result in an output data rate  $F_{S,OUT} = F_S/8$  with a Nyquist zone of  $F_S/16$ .

During the real mixing the spectrum (signal and noise) amplitude is reduced by 3-dB. In order to compensate this loss, there is a 3-dB digital gain option in the decimation filter block that can be enabled via SPI write.

図 8-18. Real decimation illustration

### 8.3.4.3 FS/4 Mixing with Real Output

In this mode, the output after complex decimation gets mixed with FS/4 (FS = output data rate in this case). Instead of a complex output with the input signal centered around 0 Hz, the output is transmitted as a real output at twice the data rate and the signal is centered around FS/4 (Fout/4) as illustrated in  $\boxtimes$  8-19.

In this example, complex decimation by 8 is used. The output data is transmitted as a real output with an output rate of Fout = FS'/4 (FS' = ADC sampling rate). The input signal is now centered around FS/4 (Fout/4) or FS'/16.

図 8-19. FS/4 Mixing with real output

### 8.3.4.4 Numerically Controlled Oscillator (NCO) and Digital Mixer

The decimation block is equipped with a 32-bit NCO and a digital mixer to fine tune the frequency placement prior to the digital filtering. The oscillator generates a complex exponential sequence of:

where: frequency ( $\omega$ ) is specified as a signed number by the 32-bit register setting

The complex exponential sequence is multiplied with the real input from the ADC to mix the desired carrier to a frequency equal to  $f_{\text{IN}}$  +  $f_{\text{NCO}}$ . The NCO frequency can be tuned from  $-F_{\text{S}}/2$  to  $+F_{\text{S}}/2$  and is processed as a signed, 2s complement number. After programming a new NCO frequency, the MIXER RESTART register bit or SYNC pin has to be toggled for the new frequency to get active. Additionally the ADC3664 provides the option via SPI to invert the mixer phase.

The NCO frequency setting is set by the 32-bit register value given and calculated as:

NCO frequency = 0 to +

$$F_S/2$$

: NCO =  $f_{NCO} \times 2^{32} / F_S$

NCO frequency =

$$-F_S/2$$

to 0: NCO =  $(f_{NCO} + F_S) \times 2^{32} / F_S$

#### where:

- NCO = NCO register setting (decimal value)

- f<sub>NCO</sub> = Desired NCO frequency (MHz)

- F<sub>S</sub> = ADC sampling rate (MSPS)

The NCO programming is further illustrated with this example:

$f_{NCO} = -10 \text{ MHz}$

- ADC sampling rate F<sub>S</sub> = 125 MSPS

- Input signal f<sub>IN</sub> = 10 MHz

- Desired output frequency f<sub>OUT</sub> = 0 MHz

For this example there are actually four ways to program the NCO and achieve the desired output frequency as shown in  $\frac{1}{2}$  8-1.

| Alias or negative image   | f <sub>NCO</sub>            | NCO Value  | Mixer Phase | Frequency translation for f <sub>OUT</sub>                                        |

|---------------------------|-----------------------------|------------|-------------|-----------------------------------------------------------------------------------|

| f <sub>IN</sub> = -10 MHz | f <sub>NCO</sub> = 10 MHz   | 343597384  | as is       | $f_{OUT} = f_{IN} + f_{NCO} = -10 \text{ MHz} + 10 \text{ MHz} = 0 \text{ MHz}$   |

| f <sub>IN</sub> = 10 MHz  | $f_{NCO} = -10 \text{ MHz}$ | 4638564680 | 45 15       | $f_{OUT} = f_{IN} + f_{NCO} = 10 \text{ MHz} + (-10 \text{ MHz}) = 0 \text{ MHz}$ |

| f <sub>IN</sub> = 10 MHz  | f <sub>NCO</sub> = 10 MHz   | 343597384  |             | f <sub>OUT</sub> = f <sub>IN</sub> – f <sub>NCO</sub> = 10 MHz – 10 MHz = 0 MHz   |

4638564680

表 8-1. NCO value calculations example

inverted

$f_{IN} = -10 \text{ MHz}$

$f_{OUT} = f_{IN} - f_{NCO} = -10 \text{ MHz} - (-10 \text{ MHz}) = 0 \text{ MHz}$

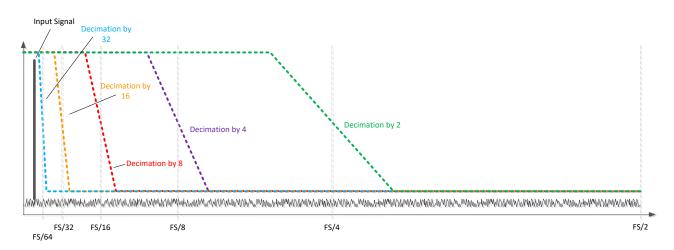

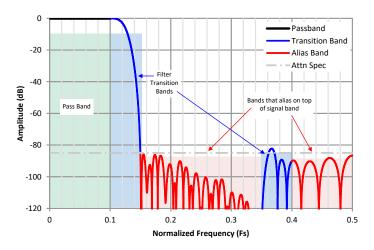

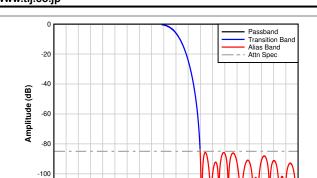

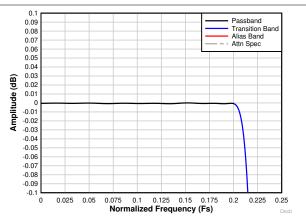

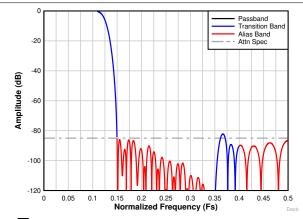

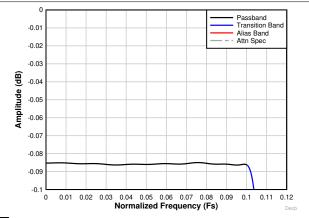

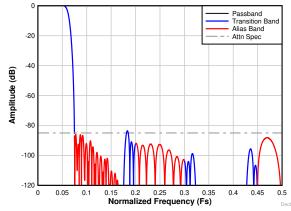

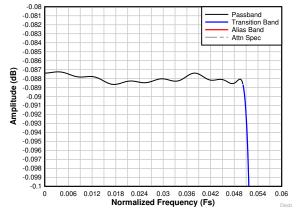

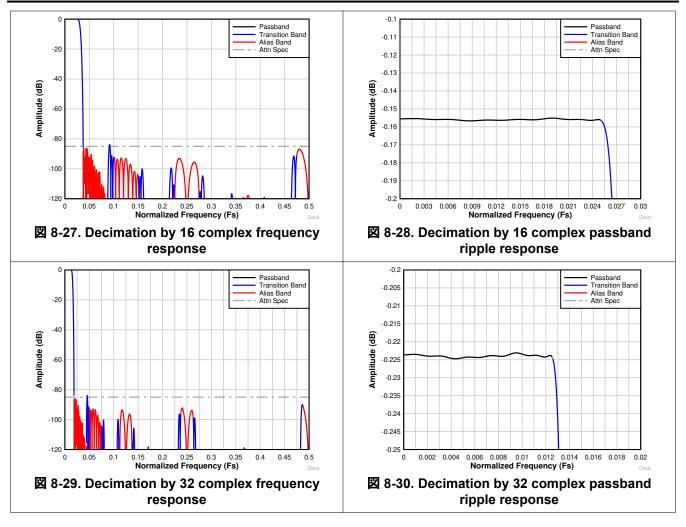

#### 8.3.4.5 Decimation Filter

The ADC3664 supports complex decimation by 2, 4, 8, 16 and 32 with a pass-band bandwidth of  $\sim$  80% and a stopband rejection of at least 85 dB.  $\gtrsim$  8-2 gives an overview of the pass-band bandwidth of the different decimation settings with respect to ADC sampling rate  $F_S$ . In real decimation mode the output bandwidth is half of the complex bandwidth.

| REAL/COMPLEX DECIMATION | DECIMATION<br>SETTING N | OUTPUT RATE                 | OUTPUT<br>BANDWIDTH       | OUTPUT RATE<br>(F <sub>S</sub> = 125 MSPS) | OUTPUT BANDWIDTH<br>(F <sub>S</sub> = 125 MSPS) |

|-------------------------|-------------------------|-----------------------------|---------------------------|--------------------------------------------|-------------------------------------------------|

|                         | 2                       | F <sub>S</sub> / 2 complex  | 0.8 × F <sub>S</sub> / 2  | 62.5 MSPS complex                          | 50 MHz                                          |

|                         | 4                       | F <sub>S</sub> / 4 complex  | 0.8 × F <sub>S</sub> / 4  | 31.25 MSPS complex                         | 25 MHz                                          |

| Complex                 | 8                       | F <sub>S</sub> / 8 complex  | 0.8 × F <sub>S</sub> / 8  | 15.625 MSPS complex                        | 12.5 MHz                                        |

|                         | 16                      | F <sub>S</sub> / 16 complex | 0.8 × F <sub>S</sub> / 16 | 7.8125 MSPS complex                        | 6.25 MHz                                        |

|                         | 32                      | F <sub>S</sub> / 32 complex | 0.8 × F <sub>S</sub> / 32 | 3.90625 MSPS complex                       | 3.125 MHz                                       |

|                         | 2                       | F <sub>S</sub> / 2 real     | 0.4 × F <sub>S</sub> / 2  | 62.5 MSPS                                  | 25 MHz                                          |

|                         | 4                       | F <sub>S</sub> / 4 real     | 0.4 × F <sub>S</sub> / 4  | 31.25 MSPS                                 | 12.5 MHz                                        |

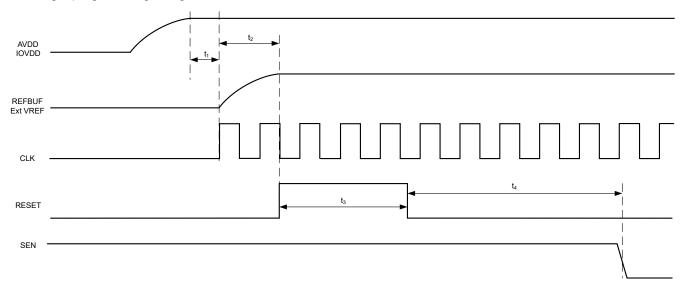

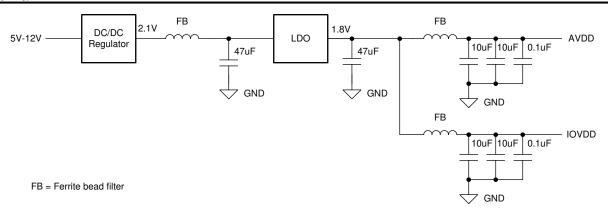

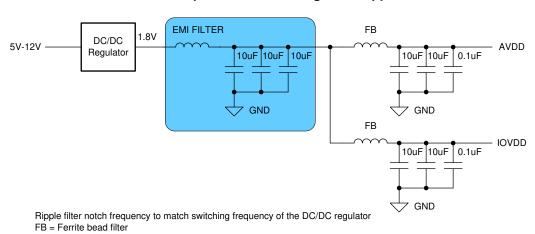

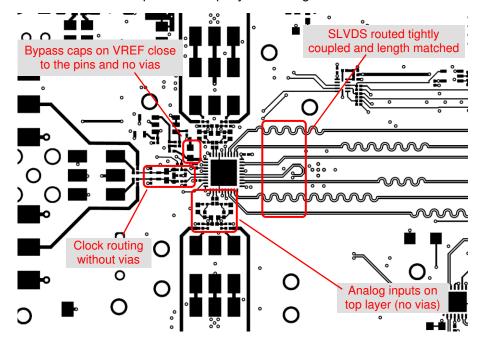

| Real                    | 8                       | F <sub>S</sub> / 8 real     | 0.4 × F <sub>S</sub> / 8  | 15.625 MSPS                                | 6.25 MHz                                        |