UCC28C40-Q1, UCC28C41-Q1, UCC28C42-Q1, UCC28C43-Q1, UCC28C44-Q1, UCC28C45-Q1

JAJSHT1G - DECEMBER 2009 - REVISED NOVEMBER 2022

# UCC28C4x-Q1 車載用 BiCMOS 低消費電力電流モード PWM コントローラ

# 1 特長

- 下記内容で AEC-Q100 認定済み:

- デバイス温度グレード 1:-40℃~125℃

- デバイス HBM 分類レベル 2:±2kV

- デバイス CDM 分類レベル C4B:750V

- 機能安全対応

- 機能安全システムの設計に役立つ資料を利用可 能

- 動作周波数:1MHz(最大)

- スタンバイ電流:50µA (標準値)、100µA (最大値)

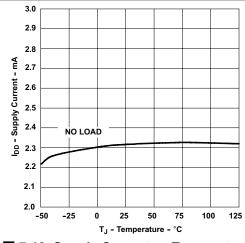

- 低い動作電流:52kHz で 2.3mA

- 高速な 35ns のサイクル単位の過電流制限

- ±1A のピーク出力電流

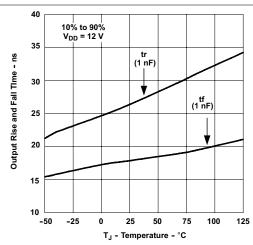

- レール・ツー・レール出力、立ち上がり時間 25ns、立ち 下がり時間 20ns

- ±1% の初期トリムされた 2.5V の誤差増幅器基準電圧

- トリムされた発振器放電電流

- 新しい低電圧誤動作防止バージョン

- WEBENCH® Power Designer により、UCC28C4x-Q1 を使用するカスタム設計を作成

# 2 アプリケーション

- OBC および DC/DC コンバータの絶縁型バイアス電

- トラクション・インバータの HV から LV へのバックアッ プ電源

- HVAC コンプレッサの HV 絶縁型電源

- EV 用充電機器の AC および DC 絶縁型電源

# 3 概要

UCC28C4x-Q1 ファミリのデバイスは、高性能の電流モー ドPWMコントローラです。

UCC28C4x-Q1 ファミリは、UVLO および最大デューテ ィ・サイクル制限オプション付きの固定周波数ピーク電流 モード・フライバック実装をサポートしています。 UCC28C4X-Q1 は 1 次側レギュレーション (補助巻線を 使用) にも 2 次側レギュレーション (フォトカプラを使用) に も構成できます。このファミリのデバイスは最高 1MHz の 高い周波数で動作し、起動および動作時の電流が小さい ため、起動時の損失と消費電力の最小化により効率を向 上できます。これらのデバイスは、出力遅延時間 35ns の 高速電流検出機能と、大型の外付け MOSFET を直接駆 動できる ±1A (ピーク) の出力電流能力も備えています。

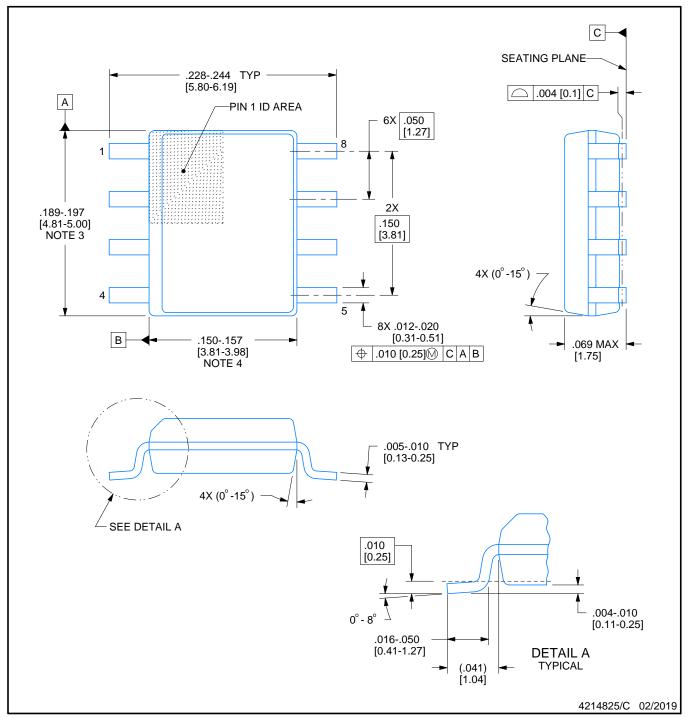

UCC28C4x-Q1 ファミリは、8 ピンの SOIC (D) パッケー ジで供給されます。

### デバイス情報<sup>(1)</sup>

| パッケージ    | 本体サイズ (公称)                    |

|----------|-------------------------------|

|          |                               |

|          |                               |

| SOIC (8) | 4.90mm × 3.91mm               |

| 3010 (0) | 4.9011111 ^ 3.9111111         |

|          |                               |

|          |                               |

|          | パッケージ<br>-<br>-<br>- SOIC (8) |

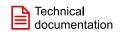

1. 利用可能なすべてのパッケージについては、このデ ータシートの末尾にある注文情報を参照してくださ

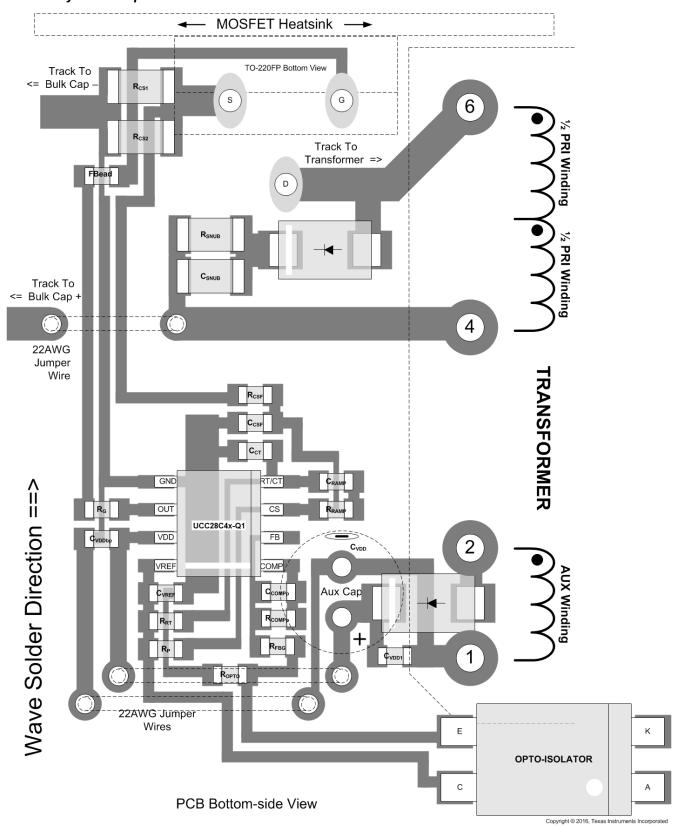

標準的な車載アプリケーションの例

# **Table of Contents**

| 1 特長                                 | 1  | 8.3 Feature Description                 | 13               |

|--------------------------------------|----|-----------------------------------------|------------------|

| 2 アプリケーション                           |    | 8.4 Device Functional Modes             | <mark>2</mark> 1 |

| 3 概要                                 |    | 9 Application and Implementation        | 22               |

| 4 Revision History                   |    | 9.1 Application Information             | <mark>22</mark>  |

| 5 Device Comparison Table            |    | 9.2 Typical Application                 |                  |

| 6 Pin Configuration and Functions    |    | 10 Device and Documentation Support     | <mark>39</mark>  |

| 7 Specifications                     |    | 10.1 Device Support                     | <mark>39</mark>  |

| 7.1 Absolute Maximum Ratings         |    | 10.2 Documentation Support              | 39               |

| 7.2 ESD Ratings                      |    | 10.3 Related Links                      | 39               |

| 7.3 Recommended Operating Conditions |    | 10.4 サポート・リソース                          | 39               |

| 7.4 Thermal Information              |    | 10.5 Trademarks                         | 39               |

| 7.5 Electrical Characteristics       |    | 10.6 Electrostatic Discharge Caution    | 40               |

| 7.6 Typical Characteristics          |    | 10.7 Glossary                           | 40               |

| 8 Detailed Description               | 12 | 11 Mechanical, Packaging, and Orderable |                  |

| 8.1 Overview                         |    | Information                             | 40               |

| 8.2 Functional Block Diagram         |    |                                         |                  |

| ŭ                                    |    |                                         |                  |

# **4 Revision History**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision F (October, 2020) to Revision G (November, 2022)                                    | Page                      |

|-----------------------------------------------------------------------------------------------------------|---------------------------|

| Updated Total Power Dissipation value in Absolute Maximum Table                                           |                           |

| <ul> <li>Added V<sub>REF</sub> maximum continuous voltage from external circuitry in Recommend</li> </ul> | ded Operating Conditions5 |

| <ul> <li>Updated T<sub>J</sub> max values in Recommended Operating Conditions Table</li> </ul>            | 5                         |

| Updated all Thermal Resistance Numbers in Thermal Information                                             | 6                         |

| Updated Electrical Characteristics section                                                                | 6                         |

| Changes from Revision E (June, 2020) to Revision F (October, 2020)                                        | Page                      |

| <ul><li>機能安全対応の情報を追加</li></ul>                                                                            | 1                         |

| Added Thermal Information table                                                                           | 6                         |

# **5 Device Comparison Table**

|                                                                               | UVLO                                                                        |                                                                    |                          |                               |

|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------|-------------------------------|

| TURN ON AT 14.5 V<br>TURN OFF AT 9 V<br>SUITABLE FOR OFF-LINE<br>APPLICATIONS | TURN ON AT 8.4 V<br>TURN OFF AT 7.6 V<br>SUITABLE FOR DC/DC<br>APPLICATIONS | TURN ON AT 7 V TURN OFF AT 6.6 V SUITABLE FOR BATTERY APPLICATIONS | MAXIMUM<br>DUTY<br>CYCLE | TEMPERATURE (T <sub>A</sub> ) |

| UCC28C42QDRQ1                                                                 | UCC28C43QDRQ1                                                               | UCC28C40QDRQ1                                                      | 100%                     | -40°C to 125°C                |

| UCC28C44QDRQ1                                                                 | UCC28C45QDRQ1                                                               | UCC28C41QDRQ1                                                      | 50%                      | -40 C to 125 C                |

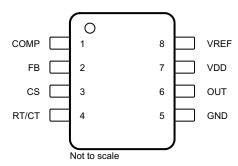

# **6 Pin Configuration and Functions**

図 6-1. D Package 8-Pin SOIC Top View

表 6-1. Pin Functions

| PIN                                                                                                                                                                                           | ı                                                                                                                                                                                                                                                                                                                                                                                                     | I/O                                                                                                                                                                                                                                                                                                                                                                                                                              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME                                                                                                                                                                                          | NO.                                                                                                                                                                                                                                                                                                                                                                                                   | 1/0                                                                                                                                                                                                                                                                                                                                                                                                                              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| СОМР                                                                                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                | This pin provides the output of the error amplifier for compensation. In addition, the COMP pin is frequently used as a control port, by utilizing a secondary-side error amplifier to send an error signal across the secondary-primary isolation boundary through an opto-isolator. The error amplifier is internally current limited so the user can command zero duty cycle by externally forcing COMP to GND.                                                                                                                                                                                                |  |

| cs                                                                                                                                                                                            | Primary-side current sense pin. The current sense pin is the noninverting input to the PWM comparator.  Connect to current sensing resistor. This signal is compared to a signal proportional to the error amplifier output voltage. The PWM uses this to terminate the OUT switch conduction. A voltage ramp can be applied to this pin to run the device with a voltage mode control configuration. |                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| FB                                                                                                                                                                                            | 2                                                                                                                                                                                                                                                                                                                                                                                                     | ı                                                                                                                                                                                                                                                                                                                                                                                                                                | his pin is the inverting input to the error amplifier. FB is used to control the power converter voltage-feedback pop for stability. The noninverting input to the error amplifier is internally trimmed to $2.5 \text{ V} \pm 1\%$ .                                                                                                                                                                                                                                                                                                                                                                             |  |

| GND                                                                                                                                                                                           | 5                                                                                                                                                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                | Ground return pin for the output driver stage and the logic level controller section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| OUT                                                                                                                                                                                           | 6                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                | The output of the on-chip drive stage. OUT is intended to directly drive a MOSFET. The OUT pin in the UCC28C40-Q1, UCC28C42-Q1, and UCC28C43-Q1 is the same frequency as the oscillator, and can operate near 100% duty cycle. In the UCC28C41-Q1, UCC28C44-Q1, and UCC28C45-Q1, the frequency of OUT is one-half that of the oscillator due to an internal T flipflop. This limits the maximum duty cycle to < 50%. Peak currents of up to 1 A are sourced and sunk by this pin. OUT is actively held low when VDD is below the turnon threshold.                                                                |  |

| RT/CT                                                                                                                                                                                         | 4                                                                                                                                                                                                                                                                                                                                                                                                     | I/O                                                                                                                                                                                                                                                                                                                                                                                                                              | Fixed frequency oscillator set point. Connect timing resistor ( $R_{RT}$ ) to VREF and timing capacitor ( $C_{CT}$ ) to GND from this pin to set the switching frequency. For best performance, keep the timing capacitor lead to the device GND as short and direct as possible. If possible, use separate ground traces for the timing capacitor and all other functions. The switching frequency ( $f_{SW}$ ) of the UCC28C40-Q1, UCC28C42-Q1, and UCC28C43-Q1 gate drive is equal to $f_{OSC}$ ; the switching frequency of the UCC28C41-Q1, UCC28C44-Q1, and UCC28C45-Q1 is equal to half of the $f_{OSC}$ . |  |

| Analog controller bias input that provides power to the device. Total VDD current is the sum of VDD current and the average OUT current. A bypass capacitor, typically 0.1 μF, connected dire |                                                                                                                                                                                                                                                                                                                                                                                                       | Analog controller bias input that provides power to the device. Total VDD current is the sum of the quiescent VDD current and the average OUT current. A bypass capacitor, typically 0.1 $\mu$ F, connected directly to GND with minimal trace length, is required on this pin. Additional capacitance at least 10 times greater than the gate capacitance of the main switching FET used in the design is also required on VDD. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

### 表 6-1. Pin Functions (continued)

| PIN NAME NO. |                                                                                                                                                                                                                                                                                                                                                                                           | I/O | DESCRIPTION |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|

|              |                                                                                                                                                                                                                                                                                                                                                                                           |     | DESCRIP HON |

| VREF 8 0     | 5-V reference voltage. VREF is used to provide charging current to the oscillator timing capacitor through the timing resistor. It is important for reference stability that VREF is bypassed to GND with a ceramic capacitor connected as close to the pin as possible. A minimum value of 0.1 µF ceramic is required. Additional VREF bypassing is required for external loads on VREF. |     |             |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)(1) (2)

|                                                       |                     | MIN  | MAX  | UNIT |

|-------------------------------------------------------|---------------------|------|------|------|

| Input voltage                                         | VDD                 |      | 20   | V    |

| Input current                                         | I <sub>VDD</sub>    |      | 30   | mA   |

| utput drive current (peak)                            |                     |      | ±1   | Α    |

| Output energy (capacitive load), E <sub>OUT</sub>     |                     |      | 5    | μJ   |

| Analog input voltage                                  | COMP, CS, FB, RT/CT | -0.3 | 6.3  |      |

| Output driver voltage                                 | OUT                 | -0.3 | 20   | V    |

| Reference voltage                                     | VREF                |      | 7    |      |

| Error amplifier output sink current                   | COMP                |      | 10   | mA   |

| Total power dissipation at T <sub>A</sub> = 25°C      | D package           |      | 72.3 | °C/W |

| Lead temperature (soldering, 10 s), T <sub>LEAD</sub> |                     |      | 300  | °C   |

| Operating junction temperature, T <sub>J</sub>        |                     | -40  | 150  | °C   |

| Storage temperature, T <sub>stg</sub>                 |                     | -65  | 150  | °C   |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under セクション 7.3. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|                                            |                                                        |                                                         | VALUE    | UNIT |

|--------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|----------|------|

| V                                          |                                                        | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> | ±2000    | V    |

| V <sub>(ESD)</sub> Electrostatic discharge | Charged-device model (CDM), per AEC Q100-011 セクション 7.2 | ±750                                                    | <b>V</b> |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 7.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted)

|                        |                                                          |             | MIN | MAX | UNIT |

|------------------------|----------------------------------------------------------|-------------|-----|-----|------|

| $V_{VDD}$              | Input voltage                                            |             |     | 18  | V    |

| V <sub>OUT</sub>       | Output driver voltage                                    |             |     | 18  | V    |

| V <sub>REF</sub>       | Maximum continuous voltage from external circuitry       |             |     | 5.5 | V    |

| I <sub>OUT</sub>       | Average output driver current <sup>(1)</sup>             |             |     | 200 | mA   |

| I <sub>OUT(VREF)</sub> | Reference output current <sup>(1)</sup>                  |             |     | -20 | mA   |

| T <sub>A</sub>         | Operating ambient temperature <sup>(1)</sup> UCC28C4x-Q1 |             | -40 | 125 | °C   |

| T <sub>J</sub>         | Operating junction temperature <sup>(1)</sup>            | UCC28C4x-Q1 | -40 | 150 | °C   |

<sup>(1)</sup> TI recommends against operating the device under conditions beyond those specified in this table for extended periods of time.

<sup>(2)</sup> All voltages are with respect to GND pin. Currents are positive into and negative out of the specified terminals.

### 7.4 Thermal Information

|                       | THERMAL METRIC <sup>(1)</sup>                | UCC28C4x-Q1     | UNIT |

|-----------------------|----------------------------------------------|-----------------|------|

|                       | THERMAL WETRIC                               | D (SOIC) 8 PINS | ONII |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 128.9           | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 71.7            | °C/W |

| R <sub>0JB</sub>      | Junction-to-board thermal resistance         | 72.3            | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 23.4            | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 71.5            | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor anddevicePackage Thermal Metrics application report.

### 7.5 Electrical Characteristics

$V_{VDD}$  = 15  $V^{(1)}$ ,  $R_{RT}$  = 10  $k\Omega$ ,  $C_{CT}$  = 3.3 nF,  $C_{VDD}$  = 0.1  $\mu$ F and no load on the outputs,  $T_J$  =  $-40^{\circ}$ C to 150 $^{\circ}$ C (unless otherwise noted).

| ,                 | PARAMETER                                | TEST CONDITIONS                                                           | MIN        | TYP  | MAX   | UNIT  |

|-------------------|------------------------------------------|---------------------------------------------------------------------------|------------|------|-------|-------|

| REFERE            | ENCE                                     |                                                                           |            |      |       |       |

| $V_{VREF}$        | VREF voltage, initial accuracy           | I <sub>OUT</sub> = 1 mA                                                   | 4.9        | 5    | 5.1   | V     |

|                   | Line regulation                          | V <sub>VDD</sub> = 12 V to 18 V                                           |            | 0.2  | 20    | mV    |

|                   | Load regulation                          | 1 mA to 20 mA                                                             |            | 3    | 25    | mV    |

|                   | Temperature stability                    | See <sup>(2)</sup>                                                        |            | 0.2  | 0.4   | mV/°C |

|                   | Total output variation                   | See <sup>(2)</sup>                                                        | 4.82       |      | 5.18  | V     |

|                   | VREF noise voltage                       | 10 Hz to 10 kHz, T <sub>J</sub> = 25°C, see <sup>(2)</sup>                |            | 50   |       | μV    |

|                   | Long term stability                      | 1000 hours, T <sub>J</sub> = 125°C, see <sup>(2)</sup>                    |            | 5    | 25    | mV    |

| I <sub>VREF</sub> | Output short circuit (source current)    |                                                                           | 30         | 45   | 55    | mA    |

| OSCILL            | ATOR                                     |                                                                           |            |      |       |       |

| f                 | In Mind and a second and                 | $T_J = 25^{\circ}C$ , see <sup>(3)</sup>                                  | 50.5       | 53   | 55    | kHz   |

| f <sub>OSC</sub>  | Initial accuracy                         | T <sub>J</sub> = Full Range, see <sup>(3)</sup>                           | 50.5       |      | 57    | kHz   |

|                   | Voltage stability                        | 12 V ≤ V <sub>VDD</sub> ≤ 18 V                                            |            | 0.2% | 1%    |       |

|                   | Temperature stability                    | T <sub>J(MIN)</sub> to T <sub>J(MAX)</sub> , see <sup>(2)</sup>           |            | 1%   | 2.5%  |       |

|                   | Amplitude                                | RT/CT pin peak-to-peak voltage                                            |            | 1.9  |       | V     |

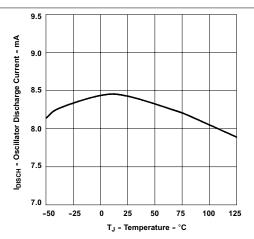

|                   | Dischaums summent                        | T <sub>J</sub> = 25°C, V <sub>RT/CT</sub> = 2 V, see <sup>(4)</sup>       | 7.7        | 8.4  | 9     | Л     |

|                   | Discharge current                        | T <sub>J</sub> = Full Range, V <sub>RT/CT</sub> = 2 V, see <sup>(4)</sup> | 7.2        | 8.4  | 9.5   | mA    |

| ERROR             | AMPLIFIER                                | 1                                                                         |            |      |       |       |

| $V_{FB}$          | Feedback input voltage, initial accuracy | T <sub>J</sub> = 25°C, V <sub>COMP</sub> = 2.5 V                          | 2.475      | 2.5  | 2.525 | V     |

|                   | Feedback input voltage, total variation  | T <sub>J</sub> = Full Range, V <sub>COMP</sub> = 2.5 V                    | 2.45       | 2.5  | 2.55  | V     |

| I <sub>FB</sub>   | Input bias current (source current)      | V <sub>FB</sub> = 5 V                                                     |            | 0.1  | 2     | μA    |

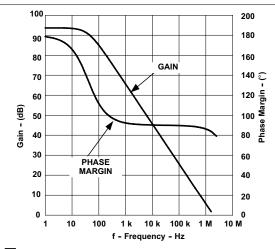

| A <sub>VOL</sub>  | Open-loop voltage gain                   | 2 V ≤ V <sub>OUT</sub> ≤ 4 V                                              | 65         | 90   |       | dB    |

|                   | Unity gain bandwidth                     | See <sup>(2)</sup>                                                        | 1          | 1.5  |       | MHz   |

| PSRR              | Power supply rejection ratio             | 12 V ≤ V <sub>VDD</sub> ≤ 18 V                                            | 60         |      |       | dB    |

|                   | Output sink current                      | V <sub>FB</sub> = 2.7 V, V <sub>COMP</sub> = 1.1 V                        | 2          | 14   |       | mA    |

|                   | Output source current                    | V <sub>FB</sub> = 2.3 V, V <sub>COMP</sub> = 5 V                          | 0.5        | 1    |       | mA    |

| VOH               | High-level COMP voltage                  | $V_{FB}$ = 2.7 V, R <sub>COMP</sub> = 15 kΩ COMP to GND                   | VREF - 0.2 |      |       | ٧     |

| VOL               | Low-level COMP voltage                   | $V_{FB}$ = 2.7 V, $R_{COMP}$ = 15 kΩ COMP to VREF                         |            | 0.1  | 1.1   | V     |

$V_{VDD} = 15 \ V^{(1)}, \ R_{RT} = 10 \ k\Omega, \ C_{CT} = 3.3 \ nF, \ C_{VDD} = 0.1 \ \mu F \ and \ no \ load \ on \ the \ outputs, \ T_{J} = -40 ^{\circ}C \ to \ 150 ^{\circ}C \ (unless \ otherwise)$ noted).

|                        | PARAMETER                           | TEST CONDITIONS                                                | MIN  | TYP  | MAX  | UNIT |

|------------------------|-------------------------------------|----------------------------------------------------------------|------|------|------|------|

| CURREN <sup>-</sup>    | T SENSE                             |                                                                |      |      |      |      |

| Δ.                     | Cain                                | T <sub>J</sub> = 25°C, See <sup>(5)</sup> (6)                  | 2.85 | 3    | 3.15 | V/V  |

| A <sub>CS</sub>        | Gain                                | T <sub>J</sub> = Full Range, See <sup>(5)</sup> <sup>(6)</sup> | 2.75 | 3    | 3.15 | V/V  |

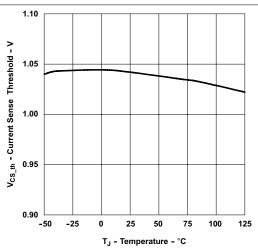

| V <sub>CS</sub>        | Maximum input signal                | V <sub>FB</sub> < 2.4 V                                        | 0.9  | 1    | 1.1  | V    |

| PSRR                   | Power supply rejection ratio        | V <sub>VDD</sub> = 12 V to 18 V <sup>(2) (5)</sup>             |      | 70   |      | dB   |

| I <sub>CS</sub>        | Input bias current (source current) |                                                                |      | 0.1  | 2    | μΑ   |

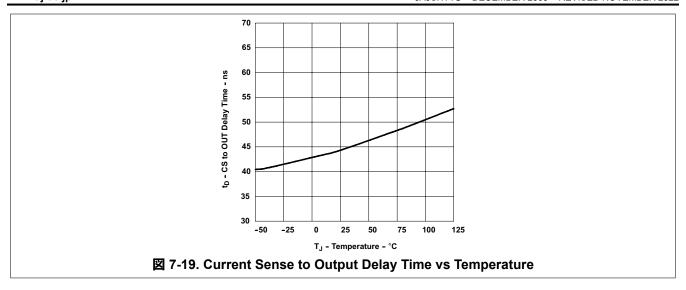

| t <sub>D</sub>         | CS to output delay                  |                                                                |      | 35   | 70   | ns   |

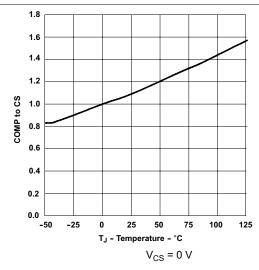

|                        | COMP to CS offset                   | V <sub>CS</sub> = 0 V                                          |      | 1.15 |      | V    |

| OUTPUT                 |                                     |                                                                |      |      |      |      |

| V <sub>OUT(low)</sub>  | R <sub>DS(on)</sub> pulldown        | I <sub>SINK</sub> = 200 mA                                     |      | 5.5  | 15   | Ω    |

| V <sub>OUT(high)</sub> | R <sub>DS(on)</sub> pullup          | I <sub>SOURCE</sub> = 200 mA                                   |      | 10   | 25   | Ω    |

| t <sub>RISE</sub>      | Rise tIme                           | C <sub>OUT</sub> = 1 nF                                        |      | 25   | 50   | ns   |

| t <sub>FALL</sub>      | Fall time                           | C <sub>OUT</sub> = 1 nF                                        |      | 20   | 40   | ns   |

| UNDERV                 | OLTAGE LOCKOUT                      |                                                                |      |      |      |      |

|                        |                                     | UCC28C42-Q1, UCC28C44-Q1                                       | 13.5 | 14.5 | 15.5 |      |

| $VDD_{ON}$             | Start threshold                     | UCC28C43-Q1, UCC28C45-Q1                                       | 7.8  | 8.4  | 9    | V    |

|                        |                                     | UCC28C40-Q1, UCC28C41-Q1                                       | 6.5  | 7    | 7.5  |      |

|                        |                                     | UCC28C42-Q1, UCC28C44-Q1                                       | 8    | 9    | 10   |      |

| $VDD_OFF$              | Minimum operating voltage           | UCC28C43-Q1, UCC28C45-Q1                                       | 7    | 7.6  | 8.2  | V    |

|                        |                                     | UCC28C40-Q1, UCC28C41-Q1                                       | 6.1  | 6.6  | 7.1  |      |

| PWM                    |                                     |                                                                |      |      |      |      |

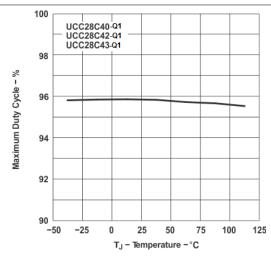

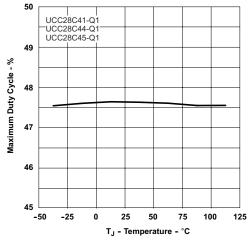

| D                      | Maximum duto anala                  | UCC28C42-Q1, UCC28C43-Q1, UCC28C40-Q1, V <sub>FB</sub> < 2.4 V | 94%  | 96%  |      |      |

| D <sub>MAX</sub>       | Maximum duty cycle                  | UCC28C44-Q1, UCC28C45-Q1, UCC28C41-Q1, V <sub>FB</sub> < 2.4 V | 47%  | 48%  |      |      |

| D <sub>MIN</sub>       | Minimum duty cycle                  | V <sub>FB</sub> > 2.6 V                                        |      |      | 0%   |      |

| CURREN <sup>-</sup>    | T SUPPLY                            | <u>'</u>                                                       |      |      |      |      |

| I <sub>START-UP</sub>  | Start-up current                    | $V_{VDD} = VDD_{ON} - 0.5 V$                                   |      | 50   | 100  | μA   |

| I <sub>VDD</sub>       | Operating supply current            | $V_{FB} = V_{CS} = 0 V$                                        |      | 2.3  | 3    | mA   |

|                        |                                     |                                                                |      |      |      |      |

- Adjust  $V_{VDD}$  above the start threshold before setting at 15.5 V. (1)

- Ensured by design. Not production tested.

- (2) (3) Output frequencies of the UCC28C41-Q1, UCC28C44-Q1, and the UCC28C45-Q1 are half the oscillator frequency.

- Oscillator discharge current is measured with R<sub>RT</sub> = 10 k $\Omega$  to VREF. Parameter measured at trip point of latch with V<sub>FB</sub> = 0 V. (4)

- (5)

- Gain is defined as  $A_{CS} = \Delta V_{COMP} / \Delta V_{CS}$ ,  $0 \text{ V} \leq V_{CS} \leq 900 \text{ mV}$

## 7.6 Typical Characteristics

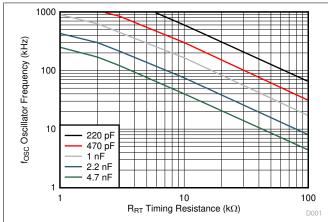

図 7-1. Oscillator Frequency vs Timing Resistance and Capacitance

☑ 7-2. Oscillator Discharge Current vs Temperature

図 7-3. Error Amplifier Frequency Response

図 7-4. COMP to CS Offset Voltage vs Temperature

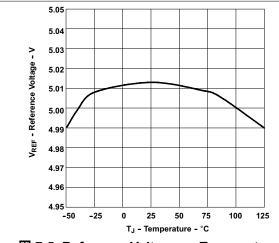

☑ 7-5. Reference Voltage vs Temperature

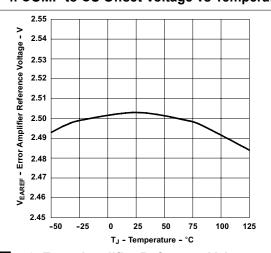

図 7-6. Error Amplifier Reference Voltage vs Temperature

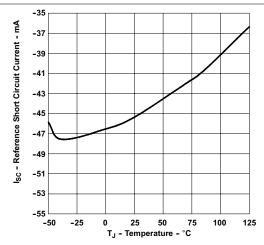

図 7-7. Reference Short-Circuit Current vs Temperature

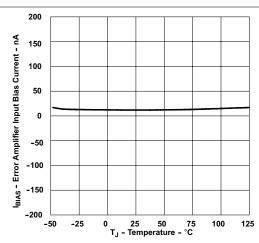

☑ 7-8. Error Amplifier Input Bias Current vs

Temperature

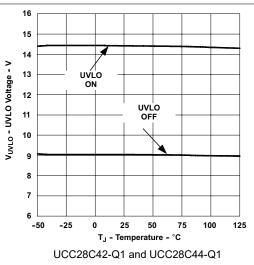

図 7-9. Undervoltage Lockout vs Temperature

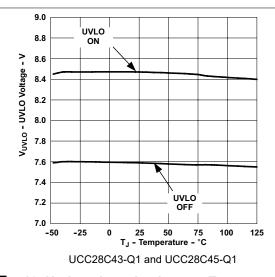

図 7-10. Undervoltage Lockout vs Temperature

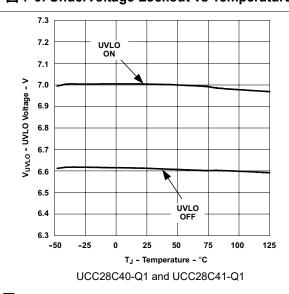

☑ 7-11. Undervoltage Lockout vs Temperature

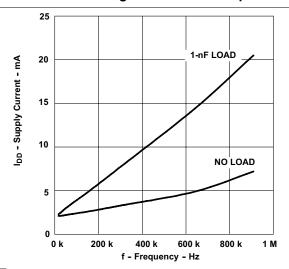

図 7-12. Supply Current vs Oscillator Frequency

図 7-13. Supply Current vs Temperature

☑ 7-14. Output Rise Time and Fall Time vs

Temperature

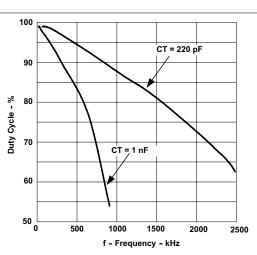

図 7-15. Maximum Duty Cycle vs Oscillator Frequency

図 7-16. Maximum Duty Cycle vs Temperature

図 7-17. Maximum Duty Cycle vs Temperature

☑ 7-18. Current Sense Threshold Voltage vs

Temperature

## 8 Detailed Description

### 8.1 Overview

The UCC28C4x-Q1 series of control integrated circuits provide the features necessary to implement AC-DC or DC-to-DC fixed-frequency current-mode control schemes with a minimum number of external components. Protection circuitry includes undervoltage lockout (UVLO) and current limiting. Internally implemented circuits include a start-up current of less than 100  $\mu$ A, a precision reference trimmed for accuracy at the error amplifier input, logic to ensure latched operation, a pulse-width modulation (PWM) comparator that also provides current-limit control, and an output stage designed to source or sink high-peak current. The output stage, suitable for driving N-channel MOSFETs, is low when it is in the OFF state. The oscillator contains a trimmed discharge current that enables accurate programming of the maximum duty cycle and dead time limit, making this device suitable for high-speed applications.

Major differences between members of this series are the UVLO thresholds, acceptable ambient temperature range, and maximum duty cycle. Typical UVLO thresholds of 14.5 V (ON) and 9 V (OFF) on the UCC28C42-Q1 and UCC28C44-Q1 devices make them ideally suited to off-line AC-DC applications. The corresponding typical thresholds for the UCC28C43-Q1 and UCC28C45-Q1 devices are 8.4 V (ON) and 7.6 V (OFF), making them ideal for use with regulated input voltages used in DC-DC applications. The UCC28C40-Q1 and UCC28C41-Q1 feature a start-up threshold of 7 V and a turnoff threshold of 6.6 V (OFF), which makes them suitable for battery-powered applications. The UCC28C40-Q1, UCC28C42-Q1, and UCC28C43-Q1 devices operate to duty cycles approaching 100%. The UCC28C41-Q1, UCC28C44-Q1, and UCC28C45-Q1 obtain a duty cycle from 0% to 50% by the addition of an internal toggle flip-flop, which blanks the output off every other clock cycle. The UCC28C4x-Q1 series is specified for operation ambient temperature from -40°C to 125°C.

The UCC28C4x-Q1 series are an enhanced replacement with pin-to-pin compatibility to the bipolar UC284x, UC384x, UC284xA, and UC384xA families. The new series offers improved performance when compared to older bipolar devices and other competitive BiCMOS devices with similar functionality. These improvements generally consist of tighter specification limits that are a subset of the older product ratings, maintaining drop-in capability. In new designs, these improvements can reduce the component count or enhance circuit performance when compared to the previously available devices.

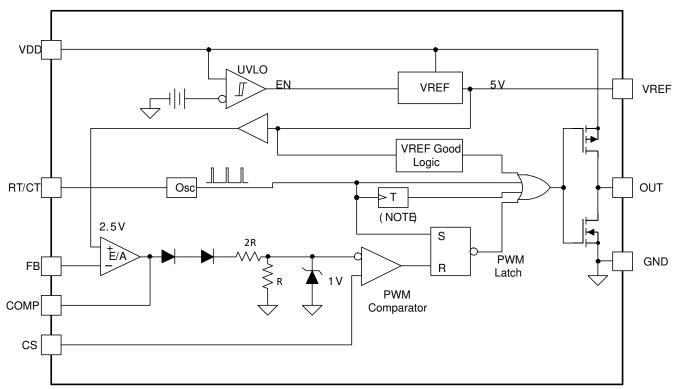

### 8.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

Toggle flip-flop used only in UCC28C41-Q1, UCC28C44-Q1, and UCCx8C45-Q1

### 8.3 Feature Description

The BiCMOS design allows operation at high frequencies that were not feasible in the predecessor bipolar devices. First, the output stage has been redesigned to drive the external power switch in approximately half the time of the earlier devices. Second, the internal oscillator is more robust, with less variation as frequency increases. This faster oscillator makes this device suitable for high speed applications and the trimmed discharge current enables precise programming of the maximum duty cycle and dead-time limit. In addition, the current sense to output delay has been reduced by a factor of three, to 45 ns (typical). The reduced delay times in the current sense results in superior overload protection at the power switch. The reduced start-up current of this device minimizes steady state power dissipation in the startup resistor, and the low operating current maximizes efficiency while running, increasing the total circuit efficiency, whether operating off-line, DC input, or battery operated circuits. These features combine to provide a device capable of reliable, high-frequency operation.

表 8-1. Key Parameters

| PARAMETER                                  | UCC28C4x-Q1    | UCC28C4x       |  |  |  |  |

|--------------------------------------------|----------------|----------------|--|--|--|--|

| Supply current at 50 kHz                   | 2.3 mA         | 2.3 mA         |  |  |  |  |

| Start-up current                           | 50 μA          | 50 μA          |  |  |  |  |

| Overcurrent propagation delay              | 50 ns          | 50 ns          |  |  |  |  |

| Reference voltage accuracy                 | ± 1%           | ± 1%           |  |  |  |  |

| Error amplifier reference voltage accuracy | ± 25 mV        | ± 25mV         |  |  |  |  |

| Maximum oscillator frequency               | 1 MHz          | 1 MHz          |  |  |  |  |

| Output rise/fall times                     | 25 ns          | 25 ns          |  |  |  |  |

| UVLO turnon accuracy                       | ± 1 V          | ± 1 V          |  |  |  |  |

| Junction Temperature                       | -40°C TO 150°C | -40°C TO 125°C |  |  |  |  |

#### 8.3.1 Detailed Pin Description

#### 8.3.1.1 COMP

The error amplifier in the UCC28C4x-Q1 family has a unity-gain bandwidth of 1.5 MHz. The COMP terminal can both source and sink current. The error amplifier is internally current-limited, so that one can command zero duty cycle by externally forcing COMP to GND.

#### 8.3.1.2 FB

FB is the inverting input of the error amplifier. The noninverting input to the error amplifier is internally trimmed to 2.5 V ± 1%. FB is used to control the power converter voltage-feedback loop for stability. For best stability, keep FB lead length as short as possible and FB stray capacitance as small as possible.

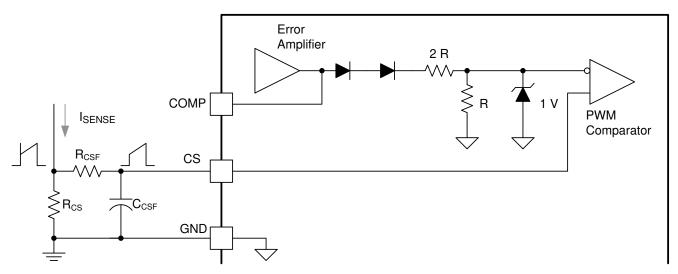

#### 8.3.1.3 CS

The UCC28C4x-Q1 current sense input connects directly to the PWM comparator. Connect CS to the MOSFET source current sense resistor. The PWM uses this signal to terminate the OUT switch conduction. A voltage ramp can be applied to this pin to run the device with a voltage mode control configuration or to add slope compensation. To prevent false triggering due to leading edge noises, an RC current sense filter may be required. The gain of the current sense amplifier is typically 3 V/V.

#### 8.3.1.4 RT/CT

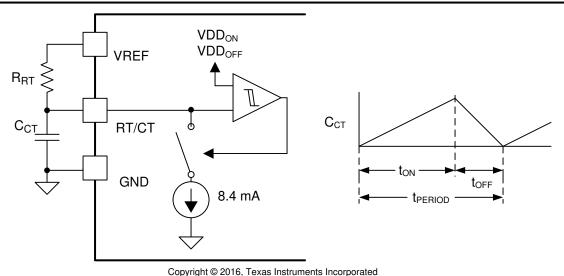

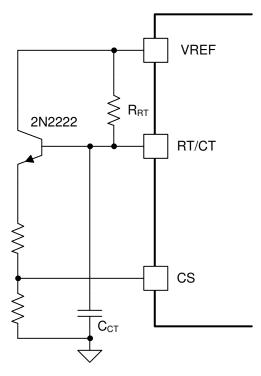

RT/CT is the oscillator timing pin. For fixed frequency operation, set the timing capacitor charging current by connecting a resistor from VREF to RT/CT. Set the frequency by connecting timing capacitor from RT/CT to GND. For the best performance, keep the timing capacitor lead to GND as short and direct as possible. If possible, use separate ground traces for the timing capacitor and all other functions.

The UCC28C4x-Q1's oscillator allows for operation to 1 MHz. The device uses an external resistor to set the charging current for the external capacitor, which determines the oscillator frequency. TI recommends timing resistor values from 1 k $\Omega$  to 100 k $\Omega$  and timing capacitor values from 220 pF to 4.7 nF. The UCC28C4x-Q1 oscillator is true to the curves of the original bipolar devices at lower frequencies, yet extends the frequency programmability range to at least 1 MHz. This allows the device to offer pin-to-pin capability where required, yet capable of extending the operational range to the higher frequencies. See  $\boxtimes$  7-1 for component values for setting the oscillator frequency.

#### 8.3.1.5 GND

GND is the signal and power returning ground. TI recommends separating the signal return path and the high current gate driver path so that the signal is not affected by the switching current.

### 8.3.1.6 OUT

The high-current output stage of the UCC28C4x-Q1 has been redesigned to drive the external power switch in approximately half the time of the earlier devices. To drive a power MOSFET directly, the totem-pole OUT driver sinks or source up to 1 A peak of current. The OUT of the UCC28C40-Q1, UCC28C42-Q1, and UCC28C43-Q1 devices switch at the same frequency as the oscillator and can operate near 100% duty cycle. In the UCC28C41-Q1, UCC28C44-Q1, and UCC28C45-Q1, the switching frequency of OUT is one-half that of the oscillator due to an internal T flip-flop. This limits the maximum duty cycle in the UCC28C41-Q1, UCC28C44-Q1, and UCC28C45-Q1 to < 50%.

The UCC28C4x-Q1 family houses unique totem pole drivers exhibiting a  $10-\Omega$  impedance to the upper rail and a  $5.5-\Omega$  impedance to ground, typically. This reduced impedance on the low-side switch helps minimize turnoff losses at the power MOSFET, whereas the higher turnon impedance of the high-side is intended to better match the reverse recovery characteristics of many high-speed output rectifiers. Transition times, rising and falling edges, are typically 25 nanoseconds and 20 nanoseconds, respectively, for a 10% to 90% change in voltage.

A low impedance MOS structure in parallel with a bipolar transistor, or BiCMOS construction, comprises the totem-pole output structure. This more efficient utilization of silicon delivers the high peak current required along with sharp transitions and full rail-to-rail voltage swings. Furthermore, the output stage is self-biasing, active low during under-voltage lockout type. With no VDD supply voltage present, the output actively pulls low if an

attempt is made to pull the output high. This condition frequently occurs at initial power-up with a power MOSFET as the driver load.

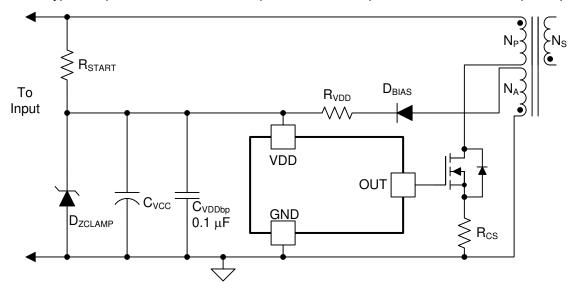

#### 8.3.1.7 VDD

VDD is the power input connection for this device. In normal operation, power VDD through a current limiting resistor. The absolute maximum supply voltage is 20 V, including any transients that may be present. If this voltage is exceeded, device damage is likely. This is in contrast to the predecessor bipolar devices, which could survive up to 30 V on the input bias pin. Also, because no internal clamp is included in the device, the VDD pin must be protected from external sources which could exceed the 20 V level. If containing the start-up and bootstrap supply voltage from the auxiliary winding  $N_A$  below 20 V under all line and load conditions can not be achieved, use a zener protection diode from VDD to GND. Depending on the impedance and arrangement of the bootstrap supply, this may require adding a resistor,  $R_{VDD}$ , in series with the auxiliary winding to limit the current into the zener as shown in  $\boxtimes$  8-1. Insure that over all tolerances and temperatures, the minimum zener voltage is higher than the highest UVLO upper turnon threshold. To ensure against noise related problems, filter VDD with a ceramic bypass capacitor to GND. The VDD pin must be decoupled as close to the GND pin as possible.

図 8-1. VDD Protection

Although quiescent VDD current is only 2.3 mA, the total supply current is higher, depending on the OUT current. Total VDD current is the sum of quiescent VDD current and the average OUT current. Knowing the operating frequency and the MOSFET gate charge  $(Q_q)$ , average OUT current can be calculated from  $\not\equiv$  1.

$$I_{OUT} = Q_g \times f_{SW} \tag{1}$$

### 8.3.1.8 VREF

VREF is the voltage reference for the error amplifier and also for many other internal circuits in the device. The 5-V reference tolerance is  $\pm 1\%$  for the UCC28C4x-Q1 family. The high-speed switching logic uses VREF as the logic power supply. The reference voltage is divided down internally to 2.5 V  $\pm 1\%$  and connected to the error amplifier's noninverting input for accurate output voltage regulation. The reference voltage sets the internal bias currents and thresholds for functions such as the oscillator upper and lower thresholds along with the overcurrent limiting threshold. The output short-circuit current is 55 mA (maximum). To avoid device over-heating and damage, do not pull VREF to ground as a means to terminate switching. For reference stability and to prevent noise problems with high-speed switching transients, bypass VREF to GND with a ceramic capacitor close to thedevicepackage. A minimum of 0.1- $\mu$ F ceramic capacitor is required. Additional VREF bypassing is required for external loads on the reference. An electrolytic capacitor may also be used in addition to the ceramic capacitor.

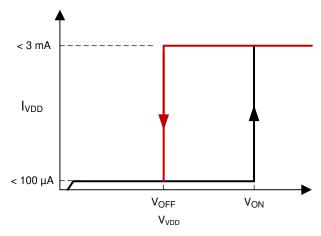

### 8.3.2 Undervoltage Lockout

Three sets of UVLO thresholds are available with turnon and turnoff thresholds of: (14.5 V and 9 V), (8.4 V and 7.6 V), and (7 V and 6.6 V) respectively. The first set is primarily intended for off-line and 48-V distributed power applications, where the wider hysteresis allows for lower frequency operation and longer soft-starting time of the converter. The second group of UVLO options is ideal for high frequency DC-DC converters typically running from a 12-VDC input. The third, and newest, set has been added to address battery powered and portable applications. 表 8-2 shows the maximum duty cycle and UVLO thresholds by device.

| MAXIMUM DUTY CYCLE | UVLO ON | UVLO OFF | PART NUMBER |  |  |  |  |  |

|--------------------|---------|----------|-------------|--|--|--|--|--|

| 100%               | 14.5 V  | 9 V      | UCC28C42-Q1 |  |  |  |  |  |

| 100%               | 8.4 V   | 7.6 V    | UCC28C43-Q1 |  |  |  |  |  |

| 100%               | 7 V     | 6.6 V    | UCC28C40-Q1 |  |  |  |  |  |

| 50%                | 14.5 V  | 9 V      | UCC28C44-Q1 |  |  |  |  |  |

| 50%                | 8.4 V   | 7.6 V    | UCC28C45-Q1 |  |  |  |  |  |

| 50%                | 7 V     | 6.6 V    | UCC28C41-Q1 |  |  |  |  |  |

表 8-2. UVLO Options

During UVLO thedevicedraws less than 100  $\mu$ A of supply current. Once crossing the turnon threshold thedevicesupply current increases to a maximum of 3 mA, typically 2.3 mA. This low start-up current allows the power supply designer to optimize the selection of the startup resistor value to provide a more efficient design. In applications where low component cost overrides maximum efficiency, the low run current of 2.3 mA (typical) allows the control device to run directly through the single resistor to (+) rail, rather than requiring a bootstrap winding on the power transformer, along with a rectifier. The start and run resistor for this case must also pass enough current to allow driving the primary switching MOSFET, which may be a few milliamps in small devices.

図 8-2. UVLO ON and OFF Profile

### 8.3.3 ±1% Internal Reference Voltage

The BiCMOS internal reference of 2.5 V has an enhanced design, and uses production trim to allow initial accuracy of  $\pm 1\%$  at room temperature and  $\pm 2\%$  over the full temperature range. This can be used to eliminate an external reference in applications that do not require the extreme accuracy afforded by the additional device. This is useful for nonisolated DC-DC applications, where the control device is referenced to the same common as the output. It is also applicable in off-line designs that regulate on the primary side of the isolation boundary by looking at a primary bias winding, or from a winding on the output inductor of a buck-derived circuit.

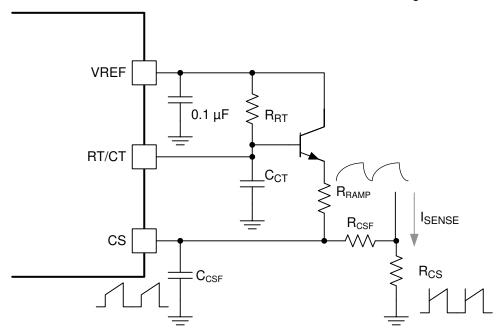

### 8.3.4 Current Sense and Overcurrent Limit

An external series resistor ( $R_{CS}$ ) senses the current and converts this current into a voltage that becomes the input to the CS pin. The CS pin is the noninverting input to the PWM comparator. The CS input is compared to a

signal proportional to the error amplifier output voltage; the gain of the current sense amplifier is typically 3 V/V. The peak  $I_{SENSE}$  current is determined using  $\gtrsim 2$

$$I_{SENSE} = \frac{V_{CS}}{R_{CS}} \tag{2}$$

The typical value for  $V_{CS}$  is 1 V. A small RC filter ( $R_{CSF}$  and  $C_{CSF}$ ) may be required to suppress switch transients caused by the reverse recovery of a secondary side diode or equivalent capacitive loading in addition to parasitic circuit impedances. The time constant of this filter should be considerably less than the switching period of the converter.

Copyright © 2016, Texas Instruments Incorporated

#### ☑ 8-3. Current-Sense Circuit Schematic

Cycle-by-cycle pulse width modulation performed at the PWM comparator essentially compares the error amplifier output to the current sense input. This is not a direct volt-to-volt comparison, as the error amplifier output network incorporates two diodes in series with a resistive divider network before connecting to the PWM comparator. The two-diode drop adds an offset voltage that enables zero duty cycle to be achieved with a low amplifier output. The 2R/R resistive divider facilitates the use of a wider error amplifier output swing that can be more symmetrically centered on the 2.5-V noninverting input voltage.

The 1-V zener diode associated with the PWM comparator's input from the error amplifier is not an actual diode in the device's design, but an indication that the maximum current sense input amplitude is 1 V (typical). When this threshold is reached, regardless of the error amplifier output voltage, cycle-by-cycle current limiting occurs, and the output pulse width is terminated within 35 ns (typical). The minimum value for this current limit threshold is 0.9 V with a 1.1-V maximum. In addition to the tolerance of this parameter, the accuracy of the current sense resistor, or current sense circuitry, must be taken into account. It is advised to factor in the worst case of primary and secondary currents when sizing the ratings and worst-case conditions in all power semiconductors and magnetic components.

### 8.3.5 Reduced-Discharge Current Variation

The UCC28C4x-Q1 oscillator design incorporates a trimmed discharge current to accurately program maximum duty cycle and operating frequency. In its basic operation, a timing capacitor ( $C_{CT}$ ) is charged by a current source, formed by the timing resistor ( $R_{RT}$ ) connected to the device's reference voltage (VREF). The oscillator design incorporates comparators to monitor the amplitude of the timing capacitor's voltage. The exponentially shaped waveform charges up to a specific amplitude representing the oscillator's upper threshold of 2.5 V. Once reached, an internal current sink to ground is turned on and the capacitor begins discharging. This discharge continues until the oscillator's lower threshold has reached 0.7 V at which point the current sink is turned off. Next, the timing capacitor starts charging again and a new switching cycle begins.

図 8-4. Oscillator Circuit

While the device is discharging the timing capacitor, resistor  $R_{RT}$  is also still trying to charge  $C_{CT}$ . It is the exact ratio of these two currents, the discharging versus the charging current, which specifies the maximum duty cycle. During the discharge time of  $C_{CT}$ , the device's output is always off. This represents an ensured minimum off time of the switch, commonly referred to as dead-time. To program an accurate maximum duty cycle, use the information provided in  $\boxtimes$  7-15 for maximum duty cycle versus oscillator frequency. Any number of maximum duty cycles can be programmed for a given frequency by adjusting the values of  $R_{RT}$  and  $C_{CT}$ . Once  $R_{RT}$  is selected, the oscillator timing capacitor can be found using the curves in  $\boxtimes$  7-1. However, because resistors are available in more precise increments, typically 1%, and capacitors are only available in 5% accuracy, it might be more practical to select the closest capacitor value first and then calculate the timing resistor value next.

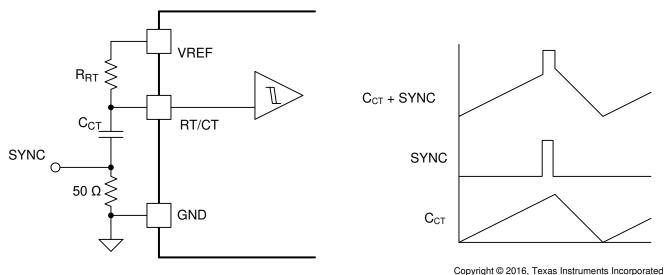

### 8.3.6 Oscillator Synchronization

Submit Document Feedback

Synchronization is best achieved by forcing the timing capacitor voltage above the oscillator's internal upper threshold. A small resistor is placed in series with  $C_{CT}$  to GND. This resistor serves as the input for the sync pulse which raises the  $C_{CT}$  voltage above the oscillator's internal upper threshold. The PWM is allowed to run at the frequency set by  $R_{RT}$  and  $C_{CT}$  until the sync pulse appears. This scheme offers several advantages including having the local ramp available for slope compensation. The UCC28C4x-Q1 oscillator must be set to a lower frequency than the sync pulse stream, typically 20 percent with a 0.5-V pulse applied across the resistor.

図 8-5. Oscillator Synchronization Circuit

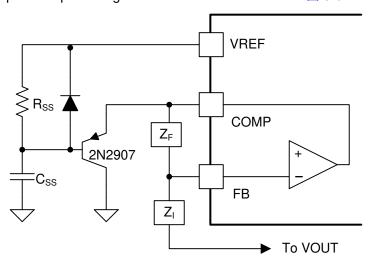

#### 8.3.7 Soft Start

Soft start is the technique to gradually power up the converter in a well-controlled fashion by slowly increasing the effective duty cycle starting at zero and gradually rising. Following start-up of the PWM, the error amplifier inverting input is low, commanding the error amplifier's output to go high. The output stage of the amplifier can source 1 mA typically, which is enough to drive most high impedance compensation networks, but not enough for driving large loads quickly. Soft start is achieved by charging a fairly large value, >1- $\mu$ F, capacitor (C<sub>SS</sub>) connected to the error amplifier output through a PNP transistor as shown in  $\boxtimes$  8-6

図 8-6. Soft-Start Implementation

The limited charging current of the amplifier into the capacitor translates into a dv/dt limitation on the error amplifier output. This directly corresponds to some maximum rate of change of primary current in a current mode controlled system as one of the PWM comparator's inputs gradually rises. The values of  $R_{SS}$  and  $C_{SS}$  must be selected to bring the COMP pin up at a controlled rate, limiting the peak current supplied by the power stage. After the soft-start interval is complete, the capacitor continues to charge to VREF, effectively removing the PNP transistor from the circuit consideration. Soft start performs a different, frequently preferred function in current mode controlled systems than it does in voltage mode control. In current mode, soft start controls the rising of the peak switch current. In voltage mode control, soft start gradually widens the duty cycle, regardless of the primary current or rate of ramp-up.

The purpose of the resistor R<sub>SS</sub> and diode is to take the soft-start capacitor out of the error amplifier's path during normal operation, once soft start is complete and the capacitor is fully charged. The optional diode in parallel with the resistor forces a soft start each time the PWM goes through UVLO condition that forces VREF to go low. Without the diode, the capacitor remains charged during a brief loss of supply or brown-out, and no soft start is enabled upon re-application of VDD.

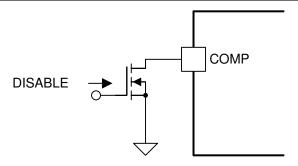

### 8.3.8 Enable and Disable

There are a few ways to enable or disable the UCC28C4x-Q1 devices, depending on which type of restart is required. The two basic techniques use external transistors to either pull the error amplifier output low ( $< 2 V_{BE}$ ) or pull the current sense input high (> 1.1 V). Application of the disable signal causes the output of the PWM comparator to be high. The PWM latch is reset dominant so that the output remains low until the next clock cycle after the shutdown condition at the COMP or CS pin is removed. Another choice for restart without a soft start is to pull the current sense input above the cycle-by-cycle current limiting threshold. A logic level P-channel FET from the reference voltage to the current sense input can be used.

図 8-7. Disable Circuit

### 8.3.9 Slope Compensation

With current mode control, slope compensation is required to stabilize the overall loop with duty cycles exceeding 50%. Although not required, slope compensation also improves stability in applications using below a 50% maximum duty cycle. Slope compensation is introduced by injecting a portion of the oscillator waveform to the actual sensed primary current. The two signals are summed together at the current sense input (CS) connection at the filter capacitor. To minimize loading on the oscillator, it is best to buffer the timing capacitor waveform with a small transistor whose collector is connected to the reference voltage.

Copyright © 2016, Texas Instruments Incorporated

図 8-8. Slope Compensation Circuit

#### 8.3.10 Voltage Mode

In certain applications, voltage mode control may be a preferred control strategy for a variety of reasons. Voltage mode control is easily executable with any current mode controller, especially the UCC28C4x-Q1 family members. Implementation requires generating a 0-V to 0.9-V sawtooth shaped signal to input to the current sense pin (CS) which is also one input to the PWM comparator. This is compared to the divided down error amplifier output voltage at the other input of the PWM comparator. As the error amplifier output is varied, it intersects the sawtooth waveform at different points in time, thereby generating different pulse widths. This is a straightforward method of linearly generating a pulse whose width is proportional to the error voltage.

Implementation of voltage mode control is possible by using a fraction of the oscillator timing capacitor ( $C_{CT}$ ) waveform. This can be divided down and fed to the current sense pin as shown in  $\boxtimes$  8-9. The oscillator timing components must be selected to approximate as close to a linear sawtooth waveform as possible. Although

exponentially charged, large values of timing resistance and small values of timing capacitance help approximate a more linear shaped waveform. A small transistor is used to buffer the oscillator timing components from the loading of the resistive divider network.

図 8-9. Current Mode PWM Used as a Voltage Mode PWM

### 8.4 Device Functional Modes

#### 8.4.1 Normal Operation

During normal operating mode, the controller can be used in peak current mode or voltage mode control. When the converter is operating in peak current mode, the controller regulates the converter's peak current and duty cycle. When used in voltage mode control, the controller regulates the power converter's duty cycle. The regulation of the system's peak current and duty cycle can be achieved with the use of the integrated error amplifier and external feedback circuitry.

### 8.4.2 UVLO Mode

During the system start-up, VDD voltage starts to rise from 0 V. Before the VDD voltage reaches its corresponding turnon threshold, thedeviceis operating in UVLO mode. In this mode, the VREF pin voltage is not generated. When VDD is above 1 V and below the turnon threshold, the VREF pin is actively pulled low. This way, VREF can be used as a logic signal to indicate UVLO mode. If the bias voltage to VDD drops below the UVLO-OFF threshold, the PWM switching stops and VREF returns to 0 V. The device can be restarted by applying a voltage greater than the UVLO-ON threshold to the VDD pin.

# 9 Application and Implementation

注

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 9.1 Application Information

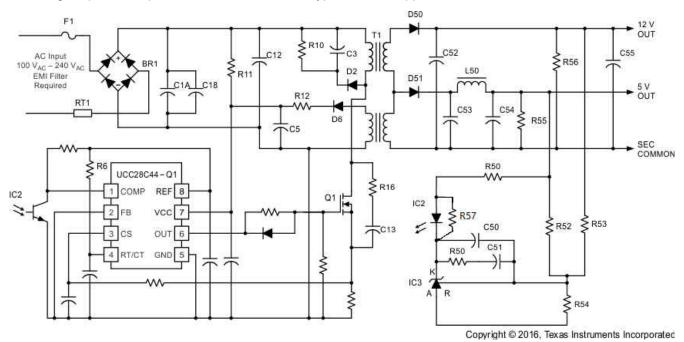

The UCC28C4x-Q1 controllers are peak current mode pulse width modulators. These controllers have an onboard amplifier and can be used in isolated and nonisolated power supply designs. There is an onboard totem pole gate driver capable of delivering 1 A of peak current. This is a high-speed PWM capable of operating at switching frequencies up to 1 MHz.  $\boxtimes$  9-1 shows a typical off-line application.

図 9-1. Typical Off-Line Application

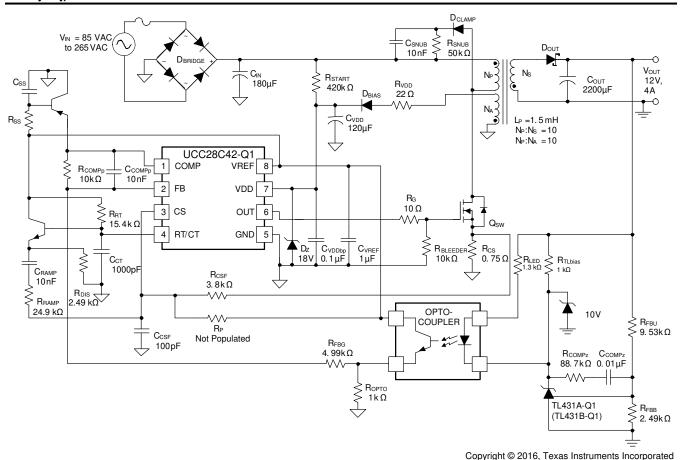

### 9.2 Typical Application

A typical application for the UCC28C42-Q1 in an off-line flyback converter is shown in  $\boxtimes$  9-2. The UCC28C42-Q1 uses an inner current control loop that contains a small current sense resistor which senses the primary inductor current ramp. This current sense resistor transforms the inductor current waveform to a voltage signal that is input directly into the primary side PWM comparator. This inner loop determines the response to input voltage changes. An outer voltage control loop involves comparing a portion of the output voltage to a reference voltage at the input of an error amplifier. When used in an off-line isolated application, the voltage feedback of the isolated output is accomplished using a secondary-side error amplifier and adjustable voltage reference, such as the TL431A-Q1 or TL431B-Q1. The error signal crosses the primary to secondary isolation boundary using an opto-isolator whose collector is connected to the VREF pin and the emitter is connected to FB. The outer voltage control loop determines the response to load changes.

図 9-2. Typical Application Design Schematic

### 9.2.1 Design Requirements

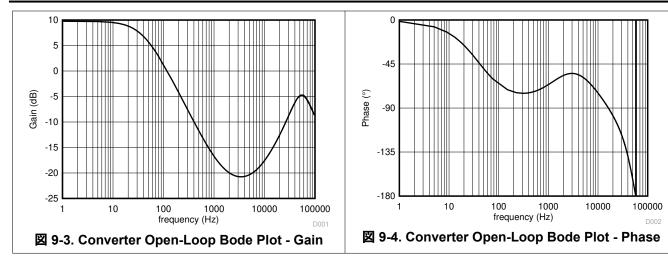

表 9-1 shows a typical set of performance requirements for an off-line flyback converter capable of providing 48 W at 12-V output voltage from a universal AC input. The design uses peak primary current control in a continuous current mode PWM converter.

表 9-1. Design Parameters

|                     | PARAMETER             | TEST CONDITIONS                                | MIN   | NOM     | MAX   | UNIT             |

|---------------------|-----------------------|------------------------------------------------|-------|---------|-------|------------------|

| V <sub>IN</sub>     | Input Voltage         |                                                | 85    | 115/230 | 265   | V <sub>RMS</sub> |

| f <sub>LINE</sub>   | Line Frequency        |                                                | 47    | 50/60   | 63    | Hz               |

| V <sub>OUT</sub>    | Output Voltage        | $I_{VOUT(min)} \le I_{VOUT} \le I_{VOUT(max)}$ | 11.75 | 12      | 12.25 | V                |

| V <sub>RIPPLE</sub> | Output Ripple Voltage | $I_{VOUT(min)} \le I_{VOUT} \le I_{VOUT(max)}$ |       |         | 100   | mVpp             |

| I <sub>VOUT</sub>   | Output Current        |                                                | 0     | 4       |       | Α                |

| f <sub>SW</sub>     | Switching Frequency   |                                                |       | 110     |       | kHz              |

| η                   | Efficiency            |                                                |       | 85%     |       |                  |

### 9.2.2 Detailed Design Procedure

This procedure outlines the steps to design an off-line universal input continuous current mode (CCM) flyback converter using the UCC28C42-Q1. See  $\boxtimes$  9-2 for component names referred to in the design procedure.

### 9.2.2.1 Custom Design With WEBENCH® Tools

Click here to create a custom design using the UCC28C4x-Q1 device with the WEBENCH® Power Designer.

- 1. Start by entering the input voltage (V<sub>IN</sub>), output voltage (V<sub>OUT</sub>), and output current (I<sub>OUT</sub>) requirements.

- 2. Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

- 3. Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time pricing and component availability.

In most cases, these actions are available:

- Run electrical simulations to see important waveforms and circuit performance

- Run thermal simulations to understand board thermal performance

- · Export customized schematic and layout into popular CAD formats

- Print PDF reports for the design, and share the design with colleagues

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

#### 9.2.2.2 Input Bulk Capacitor and Minimum Bulk Voltage

Bulk capacitance may consist of one or more capacitors connected in parallel, often with some inductance between them to suppress differential-mode conducted noise. The value of the input capacitor sets the minimum bulk voltage; setting the bulk voltage lower by using minimal input capacitance results in higher peak primary currents leading to more stress on the MOSFET switch, the transformer, and the output capacitors. Setting the bulk voltage higher by using a larger input capacitor results in higher peak current from the input source and the capacitor itself is physically larger. Compromising between size and component stresses determines the acceptable minimum input voltage. The total required value for the primary-side bulk capacitance ( $C_{IN}$ ) is selected based upon the power level of the converter ( $P_{OUT}$ ), the efficiency target ( $\eta$ ), the minimum input voltage ( $V_{IN(min)}$ ), and is chosen to maintain an acceptable minimum bulk voltage level ( $V_{BULK(min)}$ ), using  $\not \equiv 3$ .

$$C_{IN} = \frac{2 \times P_{IN} \times \left(0.25 + \frac{1}{\pi} \times \arcsin\left(\frac{V_{BULK \text{ (min)}}}{\sqrt{2} \times V_{IN \text{ (min)}}}\right)\right)}{\left(2 \times V_{IN \text{ (min)}}^2 - V_{BULK \text{ (min)}}^2\right) \times f_{LINE \text{ (min)}}}$$

(3)

where

V<sub>IN(min)</sub> is the RMS value of the minimum AC input voltage (85 VRMS) whose minimum line frequency is denoted as f<sub>LINE(min)</sub>, equal to 47 Hz

Based on 式 3, to achieve a minimum bulk voltage of 75 V, assuming 85% converter efficiency, the bulk capacitor must be larger than 126 μF; 180 μF was chosen for the design, taking into consideration component tolerances and efficiency estimation.

### 9.2.2.3 Transformer Turns Ratio and Maximum Duty CycleG

The transformer design starts with selecting a suitable switching frequency for the given application. The UCC28C42 is capable of switching up to 1 MHz but considerations such as overall converter size, switching losses, core loss, system compatibility, and interference with communication frequency bands generally determine an optimum frequency that should be used. For this off-line converter, the switching frequency (f<sub>SW</sub>) is selected to be 110 kHz as a compromise to minimize the transformer size and the EMI filter size, and still have acceptable losses.

The transformer primary to secondary turns ratio (N<sub>PS</sub>) can be selected based on the desired MOSFET voltage rating and the secondary diode voltage rating. Because the maximum input voltage is 265 VRMS, the peak bulk input voltage can be calculated as shown in 3 4.

$$V_{\text{BULK (max)}} = \sqrt{2} \times V_{\text{IN (max)}} \approx 375 \text{ V}$$

(4)

To minimize the cost of the system, a readily available 650V MOSFET is selected. Derating the maximum voltage stress on the drain to 80% of its rated value and allowing for a leakage inductance voltage spike of up to 30% of the maximum bulk input voltage, the reflected output voltage must be less than 130 V as shown in 式 5.

$$V_{REFLECTED} = 0.8 \times \left(V_{DS(rated)} - 1.3 \times V_{BULK(max)}\right) = 130.2 \text{ V}$$

(5)

The maximum primary to secondary transformer turns ratio (N<sub>PS</sub>) for a 12 V output can be selected as

$$N_{PS} = \frac{V_{REFLECTED}}{V_{OUT}} = 10.85 \tag{6}$$

A turns ratio of  $N_{PS}$  = 10 is used in the design example.

The auxiliary winding is used to supply bias voltage to the UCC28C42-Q1. Maintaining the bias voltage above the VDD minimum operating voltage after turnon is required for stable operation. The minimum VDD operating voltage for the UCC28C42-Q1 version of the controller is 10 V. The auxiliary winding is selected to support a 12 V bias voltage so that it is above the minimum operating level but still keeps the losses low in the IC. The primary to auxiliary turns ratio  $(N_{PA})$  can be calculated from  $\pm 7$ :

$$N_{PA} = N_{PS} \times \frac{V_{OUT}}{V_{BIAS}} = 10 \tag{7}$$

The output diode experiences a voltage stress that is equal to the output voltage plus the reflected input voltage:

$$V_{\text{DIODE}} = \frac{V_{\text{BULK (max)}}}{N_{\text{PS}}} + V_{\text{OUT}} = 49.5 \text{ V}$$

(8)

TI recommends a Schottky diode with a rated blocking voltage greater than 60 V to allow for voltage spikes due to ringing. The forward voltage drop (V<sub>F</sub>) of this diode is estimated to be equal to 0.6 V

To avoid high peak currents, the flyback converter in this design operates in continuous conduction mode. Once N<sub>PS</sub> is determined, the maximum duty cycle (D<sub>MAX</sub>) can be calculated using the transfer function for a CCM flyback converter:

$$\frac{V_{OUT} + V_F}{V_{BULK \text{ (min )}}} = \left(\frac{1}{N_{PS}}\right) \times \left(\frac{D_{MAX}}{1 - D_{MAX}}\right) \tag{9}$$

$$D_{MAX} = \frac{N_{PS} \times (V_{OUT} + V_F)}{V_{BULK(min)} + N_{PS} \times (V_{OUT} + V_F)} = 0.627$$

(10)

Because the maximum duty cycle exceeds 50%, and the design is an off-line (AC-input) application, the UCC28C42-Q1 is best suited for this application.

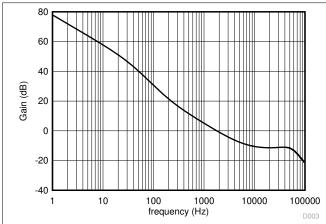

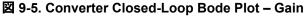

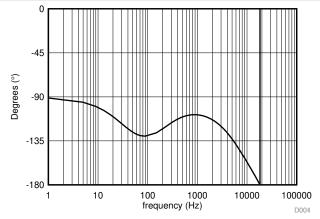

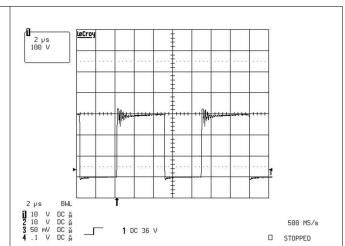

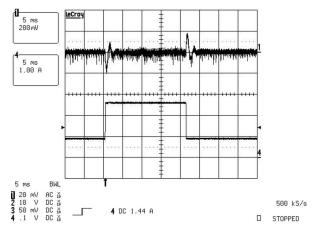

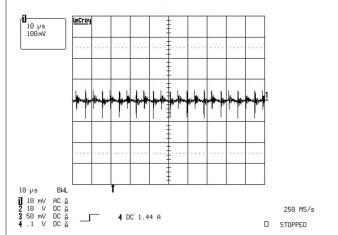

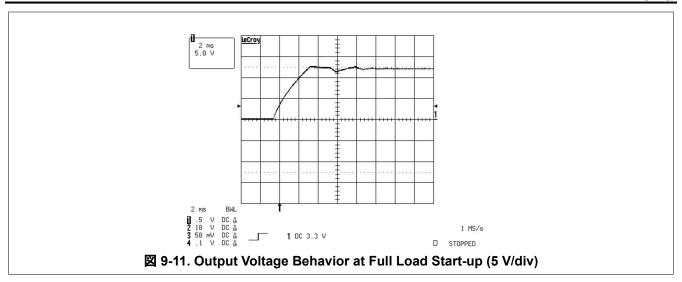

#### 9.2.2.4 Transformer Inductance and Peak Currents