**TUSS4440** JAJSIA9A – DECEMBER 2019 – REVISED MAY 2022

# TUSS4440 対数アンプを内蔵した変圧器駆動超音波センサ IC

# 1 特長

- 超音波アプリケーションのための変圧器駆動トランスデ ューサ用ドライバとアナログ出力付きレシーバ段を内蔵

- 入力ダイナミック・レンジが 86dB のアナログ・フロント エンド

- ゲインを 10、12.5、15、20V/V に調整可能な初段 低ノイズ・アンプ

- 40kHz~500kHz の構成可能なバンドパス・フィル

- 広帯域の対数アンプ

- サポートするトランスデューサ周波数 (外部クロックで制 御)

- $-40kHz\sim400kHz$

- 低消費電力アプリケーションに対応

- スタンバイ・モード: 1.7mA (標準値)

- スリープ・モード:220µA (標準値)

- 構成可能な駆動段

- 変圧器を使用してトランスデューサを励起するため の電流制限機能を備えた相補型ローサイド・ドライ バ

- IO1 および IO2 ピンを使用してバースト・パターン を構成可能

- 出力

- VOUT:復調済みエコー・エンベロープの電圧出力

- OUT3 ピン: 入力信号のゼロクロス・コンパレータ出

- OUT4 ピン:プログラム可能な VOUT スレッショル ドとの交差

- マイクロコントローラ (MCU) を使用して構成するため のシリアル・ペリフェラル・インターフェイス (SPI)

# 2 アプリケーション

- 位置センサ

- レベル・トランスミッタ

- 近接センサ

# 3 概要

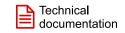

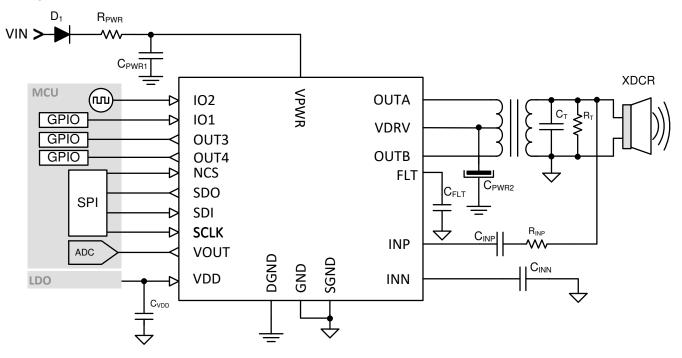

TUSS4440 は、産業用超音波アプリケーション向けの変 圧器駆動高集積アナログ・フロント・エンドです。トランスデ ューサ駆動段は、昇圧変圧器を使用して超音波トランスデ ューサを駆動するように構成できるローサイド相補型ドライ バで構成されています。このデバイスは、変圧器の 1 次側 に定電流を供給します。

受信信号パスには、低ノイズ・リニア・アンプ、バンドパス・ フィルタに続いて対数ゲイン・アンプが備わっているため、 入力に応じた適切な増幅が可能です。この対数アンプの おかげで、弱いエコー信号に対して感度を高めることがで き、反射エコーの全範囲にわたって優れた入力ダイナミッ ク・レンジが得られます。

これらのドライバは、マイクロコントローラで直接制御してバ ースト信号を完全にカスタマイズすることも、カスタマイズ 可能なバースト長を使用して SPI 経由でプログラムするこ ともできます。TUSS4440 は、バースト信号を送受信する 1 つのトランスデューサをサポートすることも、送信と受信 の機能を分離する2つのトランスデューサを構成すること もできます。

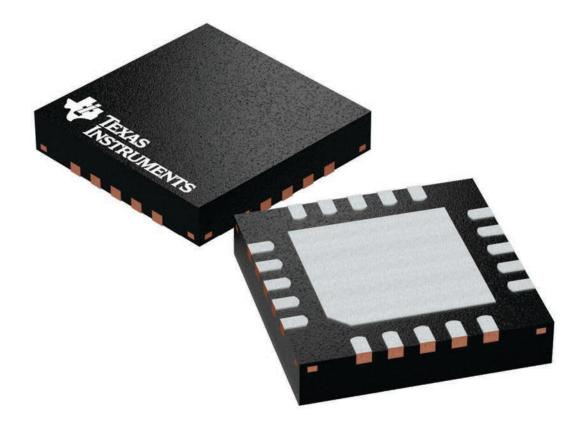

#### 製品情報 (1)

| 部品番号     | パッケージ     | 本体サイズ (公称)      |

|----------|-----------|-----------------|

| TUSS4440 | WQFN (20) | 4.00mm × 4.00mm |

(1) 利用可能なパッケージについては、このデータシートの末尾にあ る注文情報を参照してください。

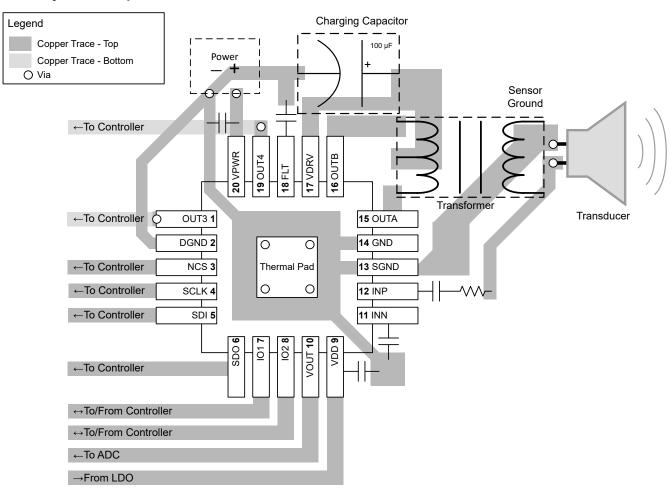

TUSS4440 アプリケーション図

# **Table of Contents**

| 1 特長                                          | 1 | 7.3 Feature Description                              | <b>1</b> 1        |

|-----------------------------------------------|---|------------------------------------------------------|-------------------|

| 2 アプリケーション                                    |   | 7.4 Device Functional Modes                          | 20                |

| 3 概要                                          |   | 7.5 Programming                                      | <mark>2</mark> 1  |

| 4 Revision History                            |   | 7.6 Register Maps                                    |                   |

| 5 Pin Configuration and Functions             |   | 8 Application and Implementation                     | 29                |

| 6 Specifications                              |   | 8.1 Application Information                          | 29                |

| 6.1 Absolute Maximum Ratings                  |   | 8.2 Typical Application                              | 29                |

| 6.2 ESD Ratings                               |   | 9 Power Supply Recommendations                       | 36                |

| 6.3 Recommended Operating Conditions          |   | 10 Layout                                            | 37                |

| 6.4 Thermal Information                       |   | 10.1 Layout Guidelines                               | 37                |

| 6.5 Power-Up Characteristics                  |   | 10.2 Layout Example                                  | 38                |

| 6.6 Transducer Drive                          |   | 11 Device and Documentation Support                  |                   |

| 6.7 Receiver Characteristics                  |   | 11.1 Receiving Notification of Documentation Updates | s <mark>39</mark> |

| 6.8 Echo Interrupt Comparator Characteristics |   | 11.2 サポート・リソース                                       | 39                |

| 6.9 Digital I/O Characteristics               |   | 11.3 Trademarks                                      | 39                |

| 6.10 Switching Characteristics                |   | 11.4 Electrostatic Discharge Caution                 | 39                |

| 6.11 Typical Characteristics                  |   | 11.5 Glossary                                        |                   |

| 7 Detailed Description                        |   | 12 Mechanical, Packaging, and Orderable              |                   |

| 7.1 Overview                                  |   | Information                                          | 39                |

| 7.2 Functional Block Diagram                  |   |                                                      |                   |

# **4 Revision History**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| C | changes from Revision * (April 2018) to Revision A (May 2022)        | Page |

|---|----------------------------------------------------------------------|------|

| • | 文書全体にわたって表、図、相互参照の採番方法を更新                                            | 1    |

| • | SPI に言及している場合、すべての旧式の用語をコントローラおよびペリフェラルに変更                           | 1    |

| • | Changed operating free-air temperature minimum from: –25°C to: –40°C | 4    |

# **5 Pin Configuration and Functions**

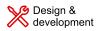

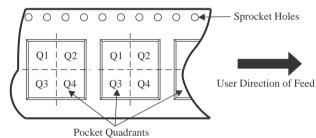

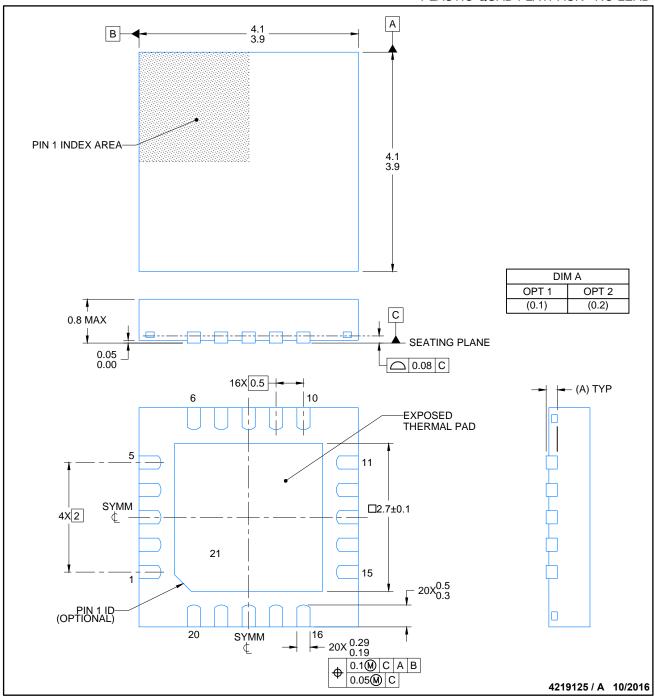

図 5-1. RTJ Package 20-Pin WQFN With Exposed Thermal Pad (Top View)

表 5-1. Pin Functions

|     | PIN  | TYPE <sup>(1)</sup> | DECODIDATION                   |

|-----|------|---------------------|--------------------------------|

| NO. | NAME | IYPE                | DESCRIPTION                    |

| 1   | OUT3 | ļ                   | General-purpose digital output |

| 2   | DGND | G                   | Digital ground                 |

| 3   | NCS  | I                   | SPI negative chip select       |

| 4   | SCLK | I                   | SPI CLK                        |

| 5   | SDI  | I                   | SPI data input                 |

| 6   | SDO  | 0                   | SPI data output                |

| 7   | IO1  | I                   | General-purpose digital input  |

| 8   | IO2  | I                   | General-purpose digital input  |

| 9   | VOUT | 0                   | Demodulated echo analog output |

| 10  | VDD  | Р                   | Voltage regulator input        |

| 11  | INN  | I                   | Negative transducer receive    |

| 12  | INP  | I                   | Positive transducer receive    |

| 13  | SGND | G                   | Sensor ground (quiet)          |

| 14  | GND  | G                   | Ground                         |

| 15  | OUTA | 0                   | Transducer driver output A     |

| 16  | OUTB | 0                   | Transducer driver output B     |

| 17  | VDRV | Р                   | Center tap for transformer     |

| 18  | FLT  | I/O                 | Filter components              |

| 19  | OUT4 | 0                   | General-purpose digital output |

| 20  | VPWR | Р                   | Input supply voltage           |

(1) I = input, O = output, I/O = input and output, G = ground, P = power

# **6 Specifications**

# **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1)

|                      |                                       | MIN  | MAX                     | UNIT |

|----------------------|---------------------------------------|------|-------------------------|------|

| V <sub>VPWR</sub>    | Supply voltage range                  | -0.3 | 40                      | V    |

| $V_{VDD}$            | Voltage regulator input voltage       | -0.3 | 5.5                     | V    |

| $V_{VDRV}$           | Transformer center-tap voltage        | -0.3 | V <sub>VPWR</sub> + 0.3 | V    |

| $V_{FLT}$            | Filter component pin                  | -0.3 | V <sub>VDD</sub> + 0.3  | V    |

| V <sub>INX</sub>     | INP, INN pins input voltage           | 0.5  | 1.3                     | V    |

| V <sub>DIG_IN</sub>  | SCLK, SDI, NCS, IOx pin input voltage | -0.3 | V <sub>VDD</sub> + 0.3  | V    |

| V <sub>VOUT</sub>    | Analog output voltage                 | -0.3 | V <sub>VDD</sub> + 0.3  | V    |

| V <sub>DIG_OUT</sub> | SDO, OUTx, IOx pin output voltage     | -0.3 | V <sub>VDD</sub> + 0.3  | V    |

| V <sub>OUTA_B</sub>  | OUTA, OUTB pins output voltage        | -0.3 | 50                      | V    |

| T <sub>A</sub>       | Ambient temperature                   | -40  | 105                     |      |

| T <sub>J</sub>       | Junction temperature                  | -40  | 125                     | °C   |

| T <sub>stg</sub>     | Storage temperature                   | -40  | 125                     |      |

Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                         |                                                                                          | VALUE | UNIT     |

|--------------------|-------------------------|------------------------------------------------------------------------------------------|-------|----------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001, all pins <sup>(1)</sup>          |       |          |

|                    |                         | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±500  | <b>v</b> |

- JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                         |                                                                                                                                                    | MIN  | NOM  | MAX       | UNIT |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----------|------|

|                         | Supply voltage on VPWR pin, internal regulation on VDRV enabled (VDRV_HI_Z=0)                                                                      | 5    |      | 36        | V    |

| $V_{VPWR}$              | Supply voltage on VPWR pin, internal regulation on VDRV disabled (VDRV_HI_Z=1), VPWR connected to the center tap of the transformer <sup>(1)</sup> | 5    |      | 24        | V    |

| V <sub>VDIG_IO</sub>    | Digital I/O pins                                                                                                                                   | -0.1 |      | $V_{VDD}$ | V    |

| $V_{VDD}$               | Regulated voltage Input                                                                                                                            | 3.1  |      | 5.5       | V    |

| I <sub>VPWR_INDIR</sub> | Current consumption at VPWR pin during ranging                                                                                                     | 150  | 240  | 340       | μΑ   |

| I <sub>VPWR_STDBY</sub> | Current consumption at VPWR in standby mode                                                                                                        | 50   | 110  | 200       | μΑ   |

| I <sub>VDD_INDIR</sub>  | Current consumption at VDD pin during ranging                                                                                                      | 7    | 11.5 | 13        | mA   |

| I <sub>VDD_STDBY</sub>  | Current consumption at VDD in standby mode                                                                                                         | 1.2  | 1.5  | 2.5       | mA   |

| I <sub>VDD_SLEEP</sub>  | Current consumption in sleep mode                                                                                                                  |      |      | 350       | μA   |

| T <sub>A</sub>          | Operating free-air temperature                                                                                                                     | -40  |      | 105       | °C   |

| T <sub>J</sub>          | Operating junction temperature                                                                                                                     | -40  |      | 125       | °C   |

Product Folder Links: TUSS4440

(1) Always  $V_{VPWR} > V_{VDRV} + 0.3 \text{ V}$  to prevent reverse current from VDRV pin to VPWR pin

# **6.4 Thermal Information**

|                       |                                              | TUSS4440   |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RTJ (WQFN) | UNIT |

|                       |                                              | 20 PINS    |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 36.3       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 29.4       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 14.7       | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.4        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 14.7       | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 4.7        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

# 6.5 Power-Up Characteristics

over operating free-air temperature range,  $V_{VDRV}$ ,  $V_{VDRV}$  and  $V_{VDD}$  recommended voltage range (unless otherwise noted)

| F                   | PARAMETER                                           | TEST CONDITIONS                                                          | MIN   | TYP | MAX   | UNIT |

|---------------------|-----------------------------------------------------|--------------------------------------------------------------------------|-------|-----|-------|------|

| t <sub>PWR_ON</sub> | Time to power up when SPI communication is possible |                                                                          |       |     | 10    | ms   |

|                     |                                                     | VDRV_VOLTAGE_LEVEL = 0x0; V <sub>VPWR</sub> > V <sub>VDRV</sub> + 100 mV | 4.5   | 5   | 5.3   |      |

|                     | Regulated voltage on VDRV pin <sup>(1)</sup>        | VDRV_VOLTAGE_LEVEL = 0x4; V <sub>VPWR</sub> > V <sub>VDRV</sub> + 100 mV | 8.1   | 9   | 9.9   | V    |

|                     |                                                     | VDRV_VOLTAGE_LEVEL = 0x7; V <sub>VPWR</sub> > V <sub>VDRV</sub> + 100 mV | 11.5  | 12  | 12.6  |      |

|                     |                                                     | VDRV_VOLTAGE_LEVEL = 0x8; V <sub>VPWR</sub> > V <sub>VDRV</sub> + 100 mV | 12.09 | 13  | 13.91 |      |

| $V_{VDRV}$          |                                                     | VDRV_VOLTAGE_LEVEL = 0xC; V <sub>VPWR</sub> > V <sub>VDRV</sub> + 100 mV | 15.81 | 17  | 18.9  |      |

|                     |                                                     | VDRV_VOLTAGE_LEVEL = 0xD; V <sub>VPWR</sub> > V <sub>VDRV</sub> + 100 mV | 16.74 | 18  | 19.26 |      |

|                     |                                                     | VDRV_VOLTAGE_LEVEL = 0xE; V <sub>VPWR</sub> > V <sub>VDRV</sub> + 100 mV | 17.67 | 19  | 20.33 |      |

|                     |                                                     | VDRV_VOLTAGE_LEVEL = 0xF; V <sub>VPWR</sub> > V <sub>VDRV</sub> + 100 mV | 19.0  | 20  | 21.4  |      |

|                     | VDRV capacitor                                      | VDRV_CURRENT_LEVEL = 0x0; V <sub>VPWR</sub> > V <sub>VDRV</sub> + 1 V    | 8.5   | 10  | 11.5  | mA   |

| I <sub>VDRV</sub>   | charging current                                    | VDRV_CURRENT_LEVEL = 0x1; V <sub>VPWR</sub> > V <sub>VDRV</sub> + 1 V    | 17    | 20  | 23    |      |

<sup>(1)</sup> Other VDRV voltage levels possible.

## 6.6 Transducer Drive

over operating free-air temperature range, V<sub>VPWR</sub>, V<sub>VDRV</sub> and V<sub>VDD</sub> recommended voltage range (unless otherwise noted)

|                        | PARAMETER                                                                                   | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|------------------------|---------------------------------------------------------------------------------------------|-----------------|-----|-----|-----|------|

| I <sub>CLAMP</sub>     | Current clamping range                                                                      |                 | 50  |     | 500 | mA   |

| I <sub>LIMIT_LOW</sub> | Minimum value on OUTA/OUTB during bursting for linear operation of current limit (headroom) |                 | 2   |     |     | V    |

| I <sub>CLAMP_ADJ</sub> | Current clamping adjustment steps                                                           |                 |     | 64  |     |      |

Copyright © 2022 Texas Instruments Incorporated

# **6.7 Receiver Characteristics**

over operating free-air temperature range,  $V_{VDWR}$ ,  $V_{VDRV}$  and  $V_{VDD}$  recommended voltage range (unless otherwise noted)

|                       | AMETER                                                                 | TEST CONDITIONS                                                                                                               | MIN  | TYP  | MAX   | UNIT   |

|-----------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------|------|-------|--------|

| G <sub>LNA</sub>      |                                                                        | LNA_GAIN = 0x00; f <sub>DRV_CLK</sub> = 58 KHz                                                                                | 13.7 | 15   | 16.8  |        |

| G <sub>LNA</sub>      | Low-noise<br>amplifier fixed<br>gain                                   | LNA_GAIN = 0x01; f <sub>DRV_CLK</sub> = 58 KHz                                                                                | 9.4  | 10   | 12    | \      |

| G <sub>LNA</sub>      |                                                                        | LNA_GAIN = 0x10; f <sub>DRV_CLK</sub> = 58 KHz                                                                                | 17.6 | 20   | 21.8  | V/V    |

| G <sub>LNA</sub>      |                                                                        | LNA_GAIN = 0x11; f <sub>DRV_CLK</sub> = 58 KHz                                                                                | 11.6 | 12.5 | 14.2  |        |

| DR <sub>VIN_MIN</sub> | Minimum receive input <sup>(2)</sup>                                   | LOGAMP_DIS_FIRST=0x0;LOGAMP_DIS_LAST=0x0                                                                                      |      | 2.4  |       | μVrms  |

| DR <sub>VIN_MAX</sub> | Maximum receive input <sup>(2)</sup>                                   | LNA_GAIN=0x00; ERR <sub>LOG</sub> < ± 3dB; f <sub>DRV_CLK</sub> < 500KHz                                                      |      | 48   |       | mVrms  |

| CI                    | Slope of analog                                                        | VOUT_SCALE_SEL = 0x0; f <sub>DRV_CLK</sub> = 58 KHz                                                                           | 25   | 29.7 | 33    | \//-ID |

| SL <sub>AFE</sub>     | front end <sup>(4)</sup>                                               | VOUT_SCALE_SEL = 0x1; f <sub>DRV_CLK</sub> = 58 KHz                                                                           | 38   | 45.1 | 46    | mV/dB  |

|                       | Receiver path                                                          | LOGAMP_DIS_FIRST = 0x0; LOGAMP_DIS_LAST = 0x0<br>ERR <sub>LOG</sub> < ± 3 dB; f <sub>DRV_CLK</sub> < 500 KHz                  | 82   |      | 92    |        |

|                       | dynamic range<br>(minimum to<br>maximum input)                         | LOGAMP_DIS_FIRST = 0x0; LOGAMP_DIS_LAST = 0x1<br>ERR <sub>LOG</sub> < ± 3 dB; f <sub>DRV_CLK</sub> < 500 KHz                  | 74   |      | 86    |        |

| DR <sub>AFE</sub>     | (2)                                                                    | LOGAMP_DIS_FIRST = 0x1; LOGAMP_DIS_LAST=0x1<br>ERR <sub>LOG</sub> < ± 3dB; f <sub>DRV_CLK</sub> < 500 KHz                     | 59   |      | 70    | dB     |

|                       | Receiver path<br>dynamic<br>Range (noise<br>floor to<br>maximum input) | LOGAMP_DIS_FIRST = 0x0; LOGAMP_DIS_LAST = 0x0<br>ERR <sub>LOG</sub> < ± 3 dB; f <sub>DRV_CLK</sub> < 500 KHz                  | 74   |      | 84    |        |

| BW <sub>LOG</sub>     | Logamp<br>bandwidth                                                    | Information only                                                                                                              | 40   |      | 1000  | KHz    |

|                       | Intercept point in dBV                                                 | LOGAMP_DIS_FIRST=0x0; LOGAMP_DIS_LAST=0x0; f <sub>DRV_CLK</sub> = 40 KHz                                                      | -108 |      | -97   |        |

| INT <sub>LOG</sub>    |                                                                        | LOGAMP_DIS_FIRST = 0x0; LOGAMP_DIS_LAST=0x1;<br>f <sub>DRV_CLK</sub> = 40 KHz                                                 | -94  |      | -86   | dBV    |

|                       |                                                                        | LOGAMP_DIS_FIRST = 0x1; LOGAMP_DIS_LAST=0x1; f <sub>DRV_CLK</sub> = 40 KHz                                                    | -80  |      | -70   |        |

| ERR <sub>LOG</sub>    | Log<br>conformance<br>error                                            | Information only                                                                                                              | -3   |      | 3     | dB     |

| f <sub>BPF</sub>      | Configurable range of center frequency of BPF                          | BPF_BYPASS = 0x0; BPF_FC_TRIM = 0x0; set by different values of BPF_HPF_FREQ                                                  | 40   |      | 500   | KHz    |

| Q <sub>BPF</sub>      | Q of bandpass filter                                                   | BPF_BYPASS = 0x0; BPF_Q_SEL = 0x0 <sup>(1)</sup>                                                                              | 3    | 4    | 5.2   |        |

| R <sub>LPF</sub>      | Internal resistor on FLT pin to ground                                 |                                                                                                                               |      | 6.25 |       | ΚΩ     |

| V                     | Output pedestal                                                        | $V_{VDD}$ = 3.3 V; $f_{DRV\_CLK}$ = 40 KHz; VOUT_SCALE_SEL = 0x0 LOGAMP_DIS_FIRST = 0x0; LOGAMP_DIS_LAST = 0x0                | 0.3  |      | 0.45  | V      |

| V <sub>O_PDSTL</sub>  | level <sup>(2)</sup>                                                   | V <sub>VDD</sub> = 5.0 V; f <sub>DRV_CLK</sub> = 40 KHz; VOUT_SCALE_SEL = 0x1<br>LOGAMP_DIS_FIRST = 0x0;LOGAMP_DIS_LAST = 0x0 | 0.45 |      | 0.675 | V      |

www.tij.co.jp

over operating free-air temperature range, V<sub>VPWR</sub>, V<sub>VDRV</sub> and V<sub>VDD</sub> recommended voltage range (unless otherwise noted)

|                      | · .             | O TIME VEE                                                                                                                             | <u> </u> |         |      |

|----------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------|----------|---------|------|

| PARA                 | AMETER          | TEST CONDITIONS                                                                                                                        | MIN      | TYP MAX | UNIT |

| V <sub>N_pk_pk</sub> | Output peak-to- | $V_{VDD}$ =3.3 V; $f_{DRV\_CLK}$ = 40 KHz; $C_{FLT}$ = 15 nF; $VOUT\_SCALE\_SEL$ = 0x0 LOGAMP_DIS_FIRST = 0x0; LOGAMP_DIS_LAST=0x0     | 50       | 200     | mVpp |

|                      | peak noise      | $V_{VDD}$ =5.0 V; $f_{DRV\_CLK}$ = 40 KHz; $C_{FLT}$ = 15<br>nF; VOUT_SCALE_SEL = 0x1<br>LOGAMP_DIS_FIRST = 0x0; LOGAMP_DIS_LAST = 0x0 | 75       | 300     | ШУРР |

- (1) Other choices of Q possible.

- $\label{eq:continuous} \text{Measured with effectively very large $C_{FLT}$. Actual minimum signal detectable will depend on $V_{N\_pk\_pk}$. Minimum and maximum input}$ levels are defined by  $\mathsf{ERR}_{\mathsf{LOG}}$ .

- Measured with different C<sub>FLT</sub> values according to 式 3. Noise floor is set by V<sub>N PK PK</sub> in addition to V<sub>O PDSTL</sub>.

- Slope measured with factory trim at f<sub>DRV CLK</sub> = 58 KHz. Slope can be adjusted with LOGAMP\_SLOPE\_ADJ bits for different f<sub>DRV CLK</sub>

# 6.8 Echo Interrupt Comparator Characteristics

over operating free-air temperature range (unless otherwise noted)

|                          | PARAMETER                                          | TEST CONDITIONS        | MIN  | TYP | MAX  | UNIT |  |

|--------------------------|----------------------------------------------------|------------------------|------|-----|------|------|--|

| VOUT_SCALI               | _SEL = 0x0                                         |                        |      |     |      |      |  |

|                          |                                                    | ECHO_INT_THR_SEL = 0x0 | 0.37 | 0.4 | 0.43 |      |  |

| \ <i>/</i>               | Echo interrupt comparator                          | ECHO_INT_THR_SEL = 0x5 | 0.56 | 0.6 | 0.64 | \ /  |  |

| V <sub>ECMP_THR_0</sub>  | threshold <sup>(1)</sup>                           | ECHO_INT_THR_SEL = 0xA | 0.75 | 0.8 | 0.85 | V    |  |

|                          |                                                    | ECHO_INT_THR_SEL = 0xF | 0.94 | 1   | 1.06 |      |  |

| V <sub>ECMP_HYS_0</sub>  | Echo interrupt comparator hysteresis               |                        | 7    |     | 68   | mV   |  |

| VOUT_SCALI               |                                                    |                        | ·    |     |      |      |  |

|                          | Echo interrupt comparator threshold <sup>(1)</sup> | ECHO_INT_THR_SEL = 0x0 | 0.56 | 0.6 | 0.64 | V    |  |

| \/                       |                                                    | ECHO_INT_THR_SEL = 0x5 | 0.84 | 0.9 | 0.96 |      |  |

| V <sub>E_CMP_THR_1</sub> |                                                    | ECHO_INT_THR_SEL = 0xA | 1.13 | 1.2 | 1.27 |      |  |

|                          |                                                    | ECHO_INT_THR_SEL = 0xF | 1.41 | 1.5 | 1.59 |      |  |

| V <sub>ECMP_HYS_1</sub>  | Echo interrupt output threshold level hysteresis   |                        | 7    |     | 68   | mV   |  |

<sup>(1)</sup> Other thresholds possible.

## 6.9 Digital I/O Characteristics

over operating free-air temperature range, V<sub>VPWR</sub>, V<sub>VDRV</sub> and V<sub>VDD</sub> recommended voltage range (unless otherwise noted)

|                        | PARAMETER                                | TEST CONDITIONS                                 | MIN                    | TYP | MAX | UNIT      |

|------------------------|------------------------------------------|-------------------------------------------------|------------------------|-----|-----|-----------|

| V <sub>IH_DIGIO</sub>  | Digital input high-level                 |                                                 | 0.7                    |     |     | $V_{VDD}$ |

| V <sub>IL_DIGIO</sub>  | Digital input low-level                  | NCS, SDI, SCLK and IOx pins                     |                        |     | 0.3 | $V_{VDD}$ |

| V <sub>HYS_DIGIO</sub> | Digital input hysteresis                 |                                                 | 100                    |     |     | mV        |

| V <sub>OH_DIGIO</sub>  | Digital output high-level <sup>(1)</sup> | SDO, OUTx pins; I <sub>DIGIO_OUT</sub> = – 1 mA | V <sub>VDD</sub> – 0.1 |     |     | V         |

| V <sub>OL_DIGIO</sub>  | Digital output low-level <sup>(1)</sup>  | SDO, OUTx pins; I <sub>DIGIO_OUT</sub> = 1 mA   |                        |     | 0.1 | V         |

| V <sub>O_CAP</sub>     | Maximum output load capacitance          | SDO pin. Information Only                       |                        |     | 10  | pF        |

| R <sub>PU_DIGIO</sub>  | Digital input pullup resistance to VDD   | NCS, IO1, IO2 pins                              | 80                     | 100 | 130 | kΩ        |

| R <sub>PD_DIGIO</sub>  | Digital Input pulldown resistance to GND | SCLK, SDI pins                                  | 80                     | 100 | 130 | kΩ        |

<sup>(1)</sup> No short-circuit protection on output pins. Damage may occur for currents higher than specified.

# 6.10 Switching Characteristics

over operating free-air temperature range, V<sub>VPWR</sub>, V<sub>VDRV</sub> and V<sub>VDD</sub> recommended voltage range (unless otherwise noted)

|                      | PARAMETER                                   | TEST CONDITIONS         | MIN | TYP MAX | UNIT |

|----------------------|---------------------------------------------|-------------------------|-----|---------|------|

| f <sub>DRV_CLK</sub> | Frequency of drive clock on IO1 and IO2 pin | Used as burst frequency | 40  | 400     | KHz  |

| SPI <sub>RATE</sub>  | SPI bit rate                                |                         |     | 500     | KHz  |

# **6.11 Typical Characteristics**

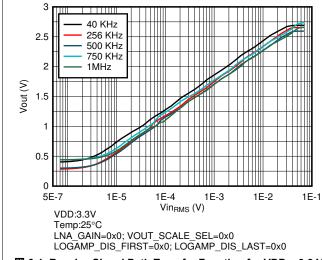

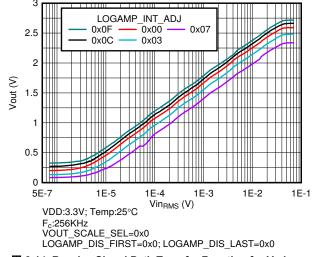

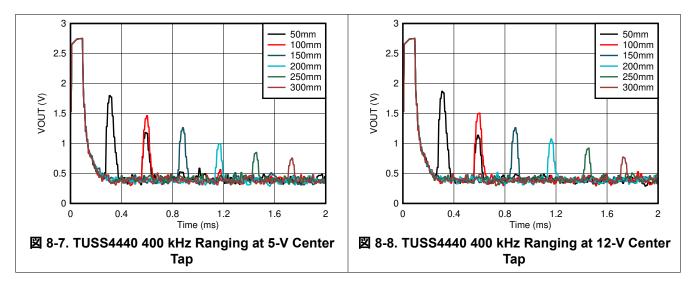

図 6-1. Receive Signal Path Transfer Function for VDD = 3.3 V

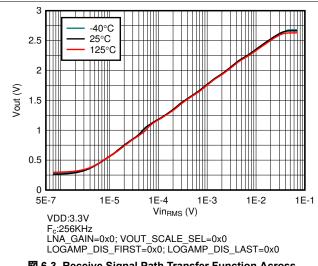

図 6-3. Receive Signal Path Transfer Function Across Temperature

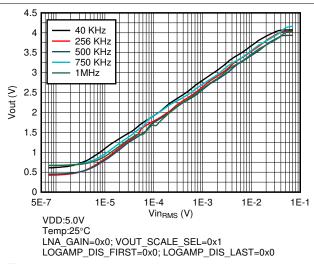

図 6-2. Receive Signal Path Transfer Function for VDD = 5 V

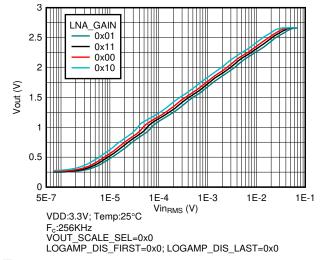

図 6-4. Receive Signal Path Transfer Function Across LNA Gain

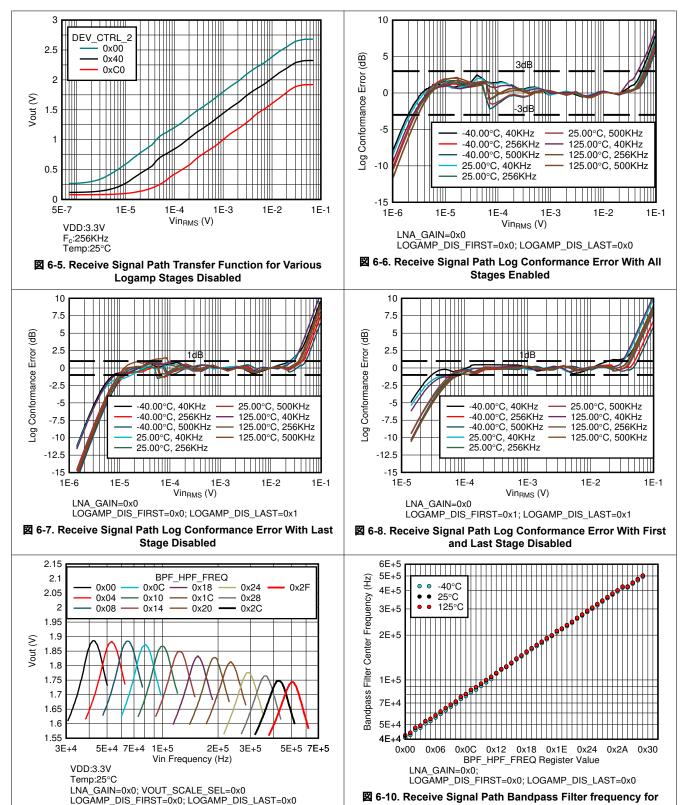

# **6.11 Typical Characteristics (continued)**

図 6-9. Receive Signal Path Bandpass Filter Transfer Function

Various Register Settings

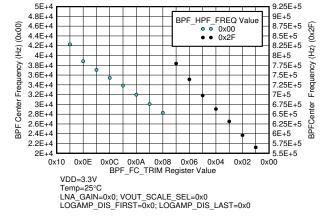

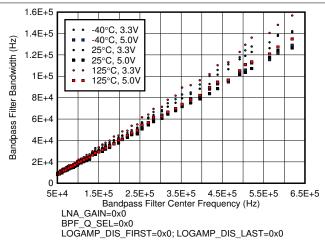

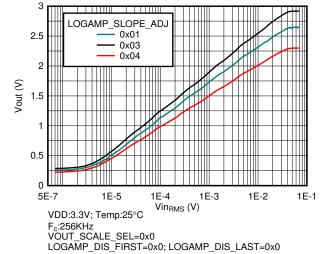

# 6.11 Typical Characteristics (continued)

図 6-11. Receive Signal Path Bandpass Filter Center Frequency

Trim

図 6-12. Receive Signal Path Bandpass Filter Bandwidth for Various Center Frequency Settings

図 6-13. Receive Signal Path Transfer Function for Various Slope Adjustments

図 6-14. Receive Signal Path Transfer Function for Various Intercept Adjustments

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

# 7 Detailed Description

## 7.1 Overview

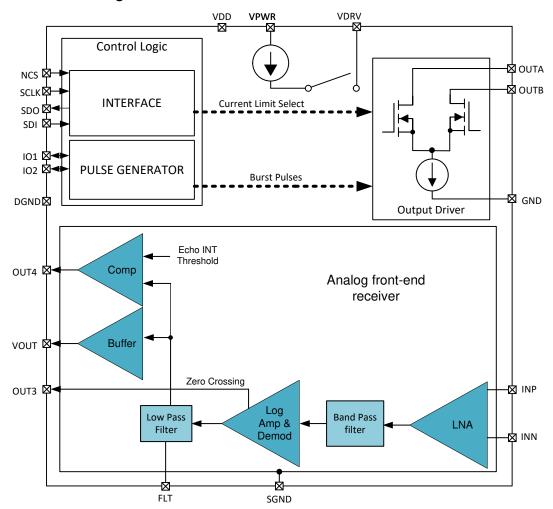

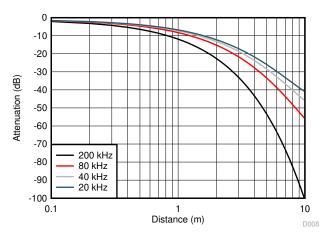

The TUSS4440 is a highly integrated driver and receiver IC designed especially for ultrasonic transducers operating between the range of 40 KHz to 1 MHz. The TUSS4440 integrates low-side complimentary FETs that can excite a ultrasonic transducer through a transformer. The transformer allows the user to step up the driving voltage to get higher sound pressure level. The The driver stage has flexible and configurable controls set through the SPI interface or through digital input pins that can be driven by an external MCU. The receive stage consists of a logarithmic amplifier receive chain. The logamp enables the TUSS4440 to have a wide dynamic input range. This enables applications where objects with different physical properties must be detected with the same sensor. A key advantage of the TUSS4440 is that it integrates a bandpass filter that can be tuned to the center frequency of the transducer. A demodulated analog output representing the receive echo, the zero crossing of the input signal, and a simple threshold crossing indicator enable a variety of end applications from complex object detection to simple presence detection.

## 7.2 Functional Block Diagram

## 7.3 Feature Description

# 7.3.1 Excitation Power Supply (VDRV)

The TUSS4440 device includes a current source which charges a capacitor connected to the VDRV pin. The VDRV pin serves as the power supply for the center tap of the transformer. The voltage on the VDRV pin  $(V_{VDRV})$  is controlled by an internal voltage monitor which can be configured by the VDRV\_VOLTAGE\_LEVEL

bits. The current source is switched off after VDRV pin voltage crosses the configured  $V_{VDRV}$  value. The charging current ( $I_{VDRV}$ ) can be configured using VDRV CURRENT LEVEL bits.

The use of VDRV pin has two advantages:

- It allows device to be used in applications where VPWR values can violate absolute maximum parameter for the OUTA / OUTB pins.

- In applications where VPWR can vary over a wide range, this allows the transducer drive voltage to be fixed

for every burst for a deterministic sound pressure level created by the transducer. This is possible only when

the minimum supply voltage on the VPWR pin is greater than the configured value of V<sub>VDRV</sub>

The VDRV regulation is disabled at device power up indicated by VDRV\_HI\_Z bit being set. To enable VDRV this bit must be cleared. This feature enables applications where the center tap of transformer is connected to a separate power supply source.

#### Note

- Very fast ramp-up rate on VPWR pin should be avoided to prevent damage to the device. If fast

ramp rates are possible, a series resistor between power supply and VPWR pin as shown in ⋈ 8-1

(R<sub>PWR</sub>) is recommended.

After a burst is completed and during the long receive time (listen mode), the capacitor on VDRV pin will discharge causing the charging current to turn on intermittently. This can inject switching noise which can be picked by the analog front end as a spurious echo. To eliminate this noise, the DIS\_VDRV\_REG\_LSTN bit can be set. This disables charging of VDRV automatically after the burst is done. The VDRV charging current can be turned on again by setting the VDRV\_TRIGGER bit. Setting this bit may create a spurious echo which can be ignored by the echo processing in the MCU. The VDRV\_READY bit in DEV\_STAT register can be monitored to know when the required voltage level has been reached and the device is ready to generate a new burst. The VDRV\_TRIGGER bit must be un-set through SPI just before the start of burst and will have to be set again for next charging cycle. If the VDRV\_TRIGGER bit is not un-set before next burst cycle, the VDRV charging current will not be automatically disabled after the burst even when DIS\_VDRV\_REG\_LSTN is set. This functionality is ignored when the VDRV\_HI\_Z bit is set.

## 7.3.2 Burst Generation

TUSS4440 has multiple modes to excite the transducer through OUTA and OUTB pins. For each of the modes, the desired frequency of burst is supplied through an external clock on the IOx pins. This enables the user to supply a highly precise clock calibrated to the center frequency of transducer to enable the highest sound pressure level generation. These modes can be selected by the IO MODE bits in the DEV CTRL 3 register.

The burst mode is enabled first, then the start of burst (OUTA/OUTB changing states) happens at the next falling edge of IO1 or IO2, depending on the mode selected. These modes are described below.

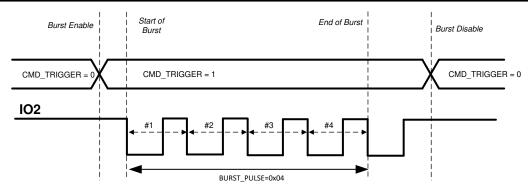

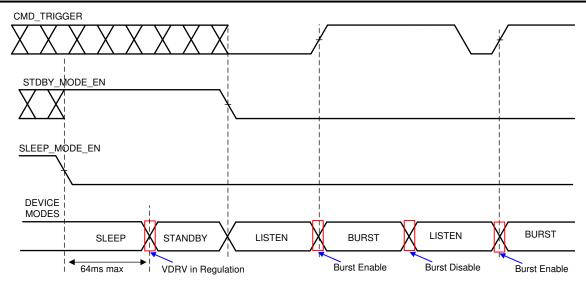

• IO\_MODE = 0: In this mode, the external clock for the transducer is applied at the IO2 pin and the burst mode is enabled by setting the CMD\_TRIGGER in the TOF\_CONFIG register through SPI, as shown in IMT-1. The device then expects a clock at IO2 pin to generate pulses on the OUTA/OUTB pins. The start of burst happens from the first falling edge of IO2. The number of pulses are counted by counting falling edge to next falling edge transitions on IO2 once the start of burst is triggered. The end of burst sequence is signaled when the number of pulses defined in BURST\_PULSE are sent, or when the CMD\_TRIGGER = 0 is set through SPI, whichever occurs earlier. TI recommends that IO2 is held high before burst enable to count the number of pulses correctly. After the start of burst, the state of OUTA and OUTB pins are determined by IO1 and IO2 pins. A transition of CMD\_TRIGGER from high to low to high again is required to initiate a new burst sequence.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

図 7-1. IO MODE 0 Description

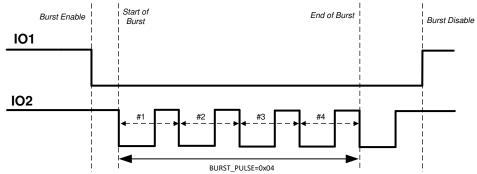

• IO\_MODE = 1: In this mode, the external clock for the transducer is applied at the IO2 pin and the burst mode is enabled when IO1 pin transitions low (see ☒ 7-2). The device then expects a clock at IO2 pin to generate pulses on the OUTA/OUTB pins. The start of burst happens from the first falling edge of IO2. The number of pulses are counted by counting falling edge to next falling edge transitions on IO2 once the start of burst is triggered. End of burst sequence is signaled when the number of pulses defined in BURST\_PULSE are sent or IO1 transitions high, whichever occurs earlier. TI recommends that IO2 is held high before start of burst to count the number of pulse correctly. After the start of burst, the state of OUTA and OUTB pins are determined by IO1 and IO2 pins. A transition of IO1 from low to high to low again is required to initiate a new burst sequence.

図 7-2. IO MODE 1 Description

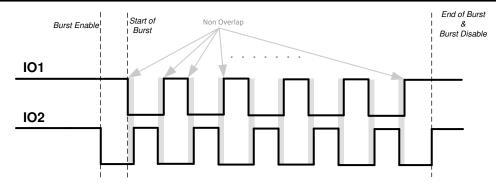

• IO\_MODE = 2: In this mode both IO1 and IO2 are used to control OUTA and OUTB. The burst enable is triggered when either IO1 or IO2 transitions from high to low. Start of burst (OUTA and OUTB changing state) happens only at the next falling edge of IO1. ☑ 7-3 shows the case where a high-to-low transition on IO2 is used to enable the burst. A burst is emulated when IO1 and IO2 are toggled in a non-overlapping sequence. After the start of burst, the state of OUTA and OUTB pins are determined by IO1 and IO2 pins. During a burst, if there is a condition where both IO1 and IO2 are high for more than half period of the internal clock f<sub>INT\_CLK</sub> (caused by differential delays due to PCB parasitics or MCU code), an end of burst and burst mode disable will be triggered. Any falling edge just after this condition will be ignored to toggle OUTA and OUTB as it would be considered as a new burst enable signal. A systematic condition of overlap can cause a continuous end of burst trigger such that OUTA and OUTB do not toggle even though IO1 and IO2 are toggling. TI recommends no overlap or minimum non-overlap between the IO1 and IO2 signals when measured at the pins. BURST\_PULSE has no effect in this mode.

# 図 7-3. IO\_MODE 2 Description

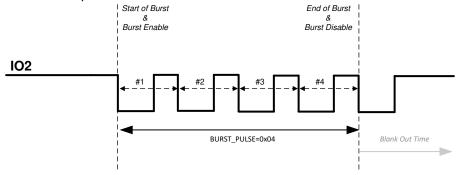

• IO\_MODE = 3: In this mode, burst enable and start of burst are both triggered by the falling edge of IO2. TI recommends that IO2 pin is kept pulled up to VDD for this mode. The device then expects a clock at IO2 pin to generate pulses on the OUTA/OUTB pins (see ☒ 7-4). The number of pulses are counted by counting falling edge to next falling edge transitions on IO2 once the start of burst is triggered. End of burst sequence is signaled when the number of pulses defined in BURST\_PULSE are sent. After end of burst, a blank-out timer interval defined by the DRV\_PLS\_FLT\_DT register is started to prevent triggering of a new start of burst in the event if the IO2 pin is still toggling. After the start of burst, the state of OUTA and OUTB pins are determined by IO1 and IO2 pins.

図 7-4. IO MODE 3 Description

#### Note

- For IO\_MODE 0 and 1, by setting BURST\_PULSE = 0, the device will generate continuous burst pulses on OUTA and OUTB until the end of burst is signaled through SPI or the IO1 pin, respectively. Continuous bursting is not available for IO\_MODE=3.

- A higher noise floor at the VOUT pin is expected in continuous mode where one transducer is used

to transmit burst signals and another transducer is used to receive, as the switching noise of the

digital IO pins can couple into the highly sensitive analog front end for the receive channel. This

also applies to the single transducer use case where a continuous clock is applied on IO2 pin when

the device is in indirect or listening mode.

- The range for frequency of switching for the output drivers is given by f<sub>DRV\_CLK</sub> parameter in the Switching Characteristics table.

- When the device is not in direct sensing or bursting mode, the device is always in indirect sensing or listening mode.

#### 7.3.2.1 Burst Generation Diagnostics

In IO\_MODE 0, 1 and 3, a pulse number diagnostic is active after start of burst (not when the burst is enabled) to monitor if the correct number of pulses (as set in BURST\_PULSE) were generated before the end of burst was signaled through SPI or the IO1 pin. A fault, if detected, is then reported through the PULSE\_NUM\_FLT bit.

The pulse duration after start of burst (not when the burst is enabled) is monitored to detect a stuck condition, which will keep the FETs on OUTA or OUTB turned on. This can happen because of loss of external clock or the

driving signal on IO1 and IO2 pins being stuck in one state. The device expects to see a toggle on IOx pins (based on IO\_MODE) within the time period as defined in the DRV\_PLS\_FLT\_DT register. If this diagnostic triggers, it will force an end of burst. The fault is reported by setting the DRV\_PULSE\_FLT bit. If a DRV\_PULSE\_FLT is set in IO\_MODE 0, 1 and 3—and the programmed number of pulses were not sent before end of burst—the PULSE\_NUM\_FLT will also be set.

#### Note

- The DRV\_PULSE\_FLT bit is cleared when a new start of burst is triggered, when DRV\_PLS\_FLT\_DT = 0x7 is set, or if the device is put into Standby or Sleep mode.

- The PULSE\_NUM\_FLT bit is cleared when a new start of burst is triggered, or if the device is put into Standby or Sleep mode.

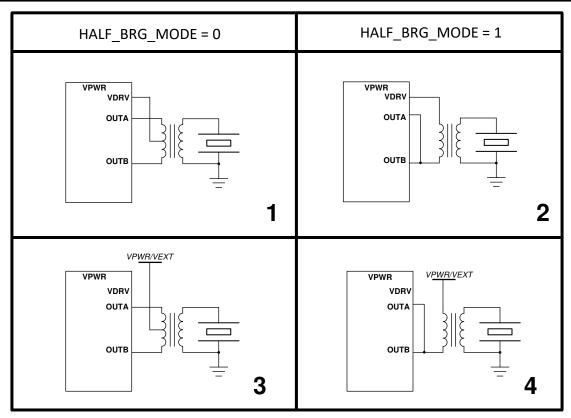

#### 7.3.3 Transformer Transducer Drive

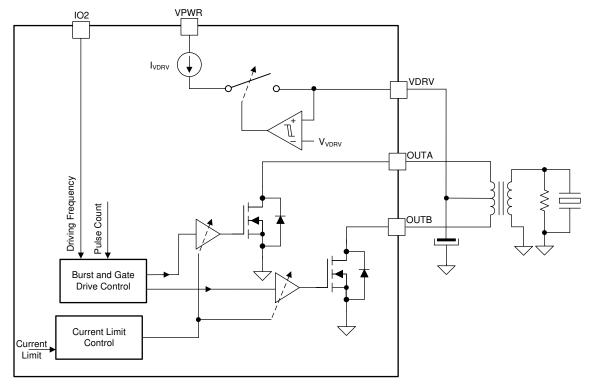

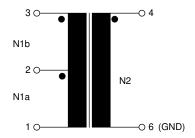

The device provides burst generation by exciting the primary side of a step-up transformer connected at the OUTA / OUTB pins. The VDRV pin is used as the power supply source. Z 7-5 shows the TUSS4440 device transformer drive block diagram when using a center-tap transformer. The drive stage in the TUSS4440 is realized as two low-side N-Channel power FETs. The current limit control block tries to drive current efficiently into the primary side of the transformer to achieve the maximum swing (set by voltage on the center tap and turn ratio of the transformer) on the secondary side. The secondary side total resistance, turn ratio, and the required peak-to-peak voltage will set the minimum value that will drive the OUTA/OUTB pin for a given set current limit. The current limit block supports multiple current levels selected by the XFMR\_DRV\_ILIM bits. The voltage on VDRV pin can be set as described in the *Excitation Power Supply (VDRV)* section.

図 7-5. TUSS4440 Center-Tap transformer drive.

For a center-tap transformer configuration, the TUSS4440 will drive the low-side FETs in an out-of-phase manner. The device also supports a single primary coil transformer configuration where the FETs are driven in-phase. This is done by setting the HALF\_BRG\_MODE bit. In this mode, the effective current limit remains the same as set in XFMR\_DRV\_ILIM. Refer to *Application and Implementation* for an application diagram and information on how the polarity and state of the OUTA and OUTB pins are defined with respect to the IO1 and IO2 pin states and other register settings.

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

#### Note

For a center-tap transformer, the voltage swing on OUTA and OUTB can be as high as  $2 \times V_{VDRV}$ . If the center tap of the transformer is connected directly to VPWR, then it must be ensured that the maximum voltage on OUTA and OUTB pins do not go above the absolute maximum limits.

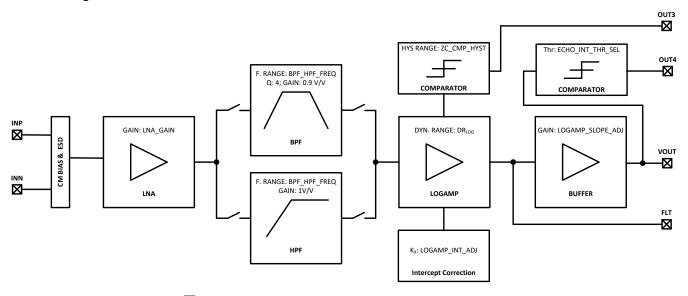

### 7.3.4 Analog Front End

図 7-6. TUSS4440 Analog Front-End Block Diagram

$\boxtimes$  7-6 shows the analog front-end block diagram that can receive and condition the signals from the transducer during listen mode. The received echo is first amplified with a fixed linear low-noise amplifier, followed by either a bandpass filter or a high-pass filter to remove noise out of the expected signal band. After filtering the signal, the signal is fed into a logarithmic amplifier. The output of the logarithmic amplifier is then buffered to the VOUT pin. In  $\boxtimes$  7-6, every block has the register name associated with it that can be used to configure the signal path. The final equation for the signal path is given by  $\npreceq$  2:

$$V_{OUT} = G_{VOUT} \cdot SL_{LOG} \cdot 20 \log_{10} \left( \frac{G_{LNA} \cdot G_{BPF} \cdot V_{IN}}{INT_{LOG} \cdot K_X} \right)$$

(1)

#### where

- G<sub>VOUT</sub> is set by the LOGAMP\_SLOPE\_ADJ bits.

- SL<sub>LOG</sub> is slope of logarithmic amplifier as specified in the *Receiver Characteristics* table.

- G<sub>LNA</sub> is set by the LNA\_GAIN bits.

- G<sub>BPF</sub> is typically 0.9V/V.

- V<sub>IN</sub> is the input V<sub>INP</sub>

- INT<sub>LOG</sub> is logarithmic amplifier intercept specified in the *Receiver Characteristics* table.

- K<sub>X</sub> is the log intercept adjustment set by the LOGAMP\_INT\_ADJ bits.

The bandpass filter is critical for reducing noise to allow utilization of the complete dynamic range of the logarithmic amplifier. The center frequency of the bandpass filter can be configured to be close the transducer frequency which is set by the BPF\_HPF\_FREQ bits. 表 7-1 shows the nominal values for the BPF center frequency corresponding to the BPF\_HPF\_FREQ register value. The TUSS4440 supports a wide range of frequencies, therefore a factory trim is used to remove process variation for a particular pre-determined frequency. It is possible that all other frequencies listed in 表 7-1 do not correspond exactly to value of BPF\_HPF\_FREQ in a factory trim. The user can vary the value of the BPF\_HPF\_FREQ register around the

desired center frequency while actively bursting and observing the VOUT signal. The value with maximum voltage at VOUT pin will the desired setting for the BPF\_HPF\_FREQ register.

表 7-1. Bandpass Filter Center Frequency Configuration

| 表 7-1. Bandpass Filter Center Frequency Configuration |                          |  |  |  |  |

|-------------------------------------------------------|--------------------------|--|--|--|--|

| BPF_HPF_FREQ (HEX)<br>(BPF_FC_TRIM_FRC = 0)           | BPF_F <sub>c</sub> (KHz) |  |  |  |  |

| 0x00                                                  | 40.64                    |  |  |  |  |

| 0x01                                                  | 44.05                    |  |  |  |  |

| 0x02                                                  | 45.6                     |  |  |  |  |

| 0x03                                                  | 48.86                    |  |  |  |  |

| 0x04                                                  | 50.58                    |  |  |  |  |

| 0x05                                                  | 52.96                    |  |  |  |  |

| 0x06                                                  | 56.75                    |  |  |  |  |

| 0x07                                                  | 60.11                    |  |  |  |  |

| 0x08                                                  | 62.95                    |  |  |  |  |

| 0x09                                                  | 66.68                    |  |  |  |  |

| 0x0A                                                  | 71.44                    |  |  |  |  |

| 0x0B                                                  | 74.81                    |  |  |  |  |

| 0x0C                                                  | 79.24                    |  |  |  |  |

| 0x0D                                                  | 82.03                    |  |  |  |  |

| 0x0E                                                  | 86.89                    |  |  |  |  |

| 0x0F                                                  | 92.04                    |  |  |  |  |

| 0x10                                                  | 97.49                    |  |  |  |  |

| 0x11                                                  | 103.27                   |  |  |  |  |

| 0x12                                                  | 109.4                    |  |  |  |  |

| 0x13                                                  | 114.54                   |  |  |  |  |

| 0x14                                                  | 121.33                   |  |  |  |  |

| 0x15                                                  | 128.52                   |  |  |  |  |

| 0x16                                                  | 134.58                   |  |  |  |  |

| 0x17                                                  | 142.55                   |  |  |  |  |

| 0x18                                                  | 151.01                   |  |  |  |  |

| 0x19                                                  | 159.94                   |  |  |  |  |

| 0x1A                                                  | 167.48                   |  |  |  |  |

| 0x1B                                                  | 177.41                   |  |  |  |  |

| 0x1C                                                  | 185.77                   |  |  |  |  |

| 0x1D                                                  | 196.78                   |  |  |  |  |

| 0x1E                                                  | 206.05                   |  |  |  |  |

| 0x1F                                                  | 218.26                   |  |  |  |  |

| 0x20                                                  | 228.54                   |  |  |  |  |

| 0x21                                                  | 244.89                   |  |  |  |  |

| 0x22                                                  | 256.43                   |  |  |  |  |

| 0x23                                                  | 271.63                   |  |  |  |  |

| 0x24                                                  | 284.43                   |  |  |  |  |

| 0x25                                                  | 301.28                   |  |  |  |  |

| 0x26                                                  | 319.13                   |  |  |  |  |

| 0x27                                                  | 338.14                   |  |  |  |  |

| 0x28                                                  | 353.97                   |  |  |  |  |

| 0x29                                                  | 374.95                   |  |  |  |  |

|                                                       |                          |  |  |  |  |

表 7-1. Bandpass Filter Center Frequency Configuration (continued)

| BPF_HPF_FREQ (HEX)<br>(BPF_FC_TRIM_FRC = 0) | BPF_F <sub>c</sub> (KHz) |

|---------------------------------------------|--------------------------|

| 0x2A                                        | 397.16                   |

| 0x2B                                        | 408.17                   |

| 0x2C                                        | 420.7                    |

| 0x2D                                        | 455.63                   |

| 0x2E                                        | 472.03                   |

| 0x2F                                        | 500                      |

The factory trim can be overridden by setting the BPF\_FC\_TRIM\_FRC bit first and varying the BPF\_FC\_TRIM bit after. This is useful in two ways:

- If the factory trimmed bandpass filter center frequency is higher than the desired value for BPF\_HPF\_FREQ = 0x00, or lower than desired value for BPF\_HPF\_FREQ = 0x2F, then BPF\_FC\_TRIM can be used to recover the range.

- This setting can also be used to extend the frequency range of the bandpass filter center frequency.

The BPF\_FC\_TRIM acts like an offset on top of the BPF\_HPF\_FREQ setting. ₹ 7-2 shows the nominal value of center frequency when this offset is added to the minimum and maximum BPF\_HPF\_FREQ code. ☑ 6-11 shows the measured data. For BPF\_HPF\_FREQ values greater than 0x08 and less than 0x27, varying BPF\_FC\_TRIM keeping BPF\_HPF\_FREQ fixed is the same as setting BPF\_FC\_TRIM = 0x00 and varying BPF\_HPF\_FREQ to find the optimum setting.

表 7-2. Bandpass Filter Center Frequency Range Extension

| 2. 7 2. Banapass I not some i requently range Extension         |                          |  |  |  |  |  |

|-----------------------------------------------------------------|--------------------------|--|--|--|--|--|

| BPF_HPF_FREQ (hex) + BPF_FC_TRIM (hex)<br>(BPF_FC_TRIM_FRC = 1) | BPF_F <sub>c</sub> (KHz) |  |  |  |  |  |

| 0x00 + 0x8                                                      | 27.48                    |  |  |  |  |  |

| 0x00 + 0x9                                                      | 29.44                    |  |  |  |  |  |

| 0x00 + 0xA                                                      | 30.83                    |  |  |  |  |  |

| 0x00 + 0xB                                                      | 31.19                    |  |  |  |  |  |

| 0x00 + 0xC                                                      | 32.65                    |  |  |  |  |  |

| 0x00 + 0xD                                                      | 34.19                    |  |  |  |  |  |

| 0x00 + 0xE                                                      | 35.8                     |  |  |  |  |  |

| 0x00 + 0xF                                                      | 38.81                    |  |  |  |  |  |

| 0x2F + 0x1                                                      | 523.56                   |  |  |  |  |  |

| 0x2F + 0x2                                                      | 554.59                   |  |  |  |  |  |

| 0x2F + 0x3                                                      | 587.45                   |  |  |  |  |  |

| 0x2F + 0x4                                                      | 622.23                   |  |  |  |  |  |

| 0x2F + 0x5                                                      | 651.58                   |  |  |  |  |  |

| 0x2F + 0x6                                                      | 690.19                   |  |  |  |  |  |

| 0x2F + 0x7                                                      | 731.09                   |  |  |  |  |  |

|                                                                 |                          |  |  |  |  |  |

#### Note

- The Q factor of the filter is specified in the Receiver Characteristics table, and can be selected by the BPF Q SEL bits.

- The bandpass filter can also be converted into a high-pass filter by setting the BPF\_BYPASS bit for transducer frequencies in the range above what is shown in 表 7-1. The corner frequency for highpass filter is also controlled by the BPF\_HPF\_FREQ bits.

- BPF Q SEL and BPF FC TRIM have no effect when BPF BYPASS = 1.

The logamp provides compression for large signal inputs and amplifies linearly small signal inputs. Logamp simplifies system design to detect varying strengths of echoes that happens because of difference in reflectivity of different types of objects and objects at different distances. It automatically adjusts its gain based on the input signal level. The logamp also demodulates the incoming signal.

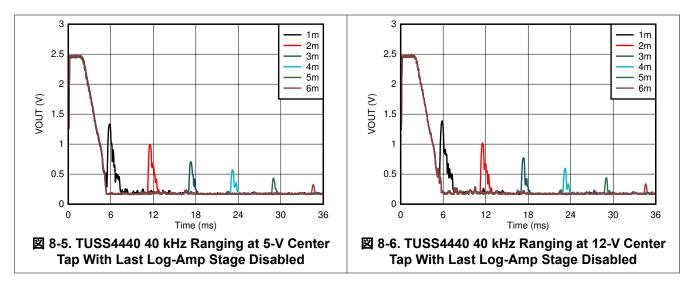

The logamp consists of multiple gain stages and range extension stages that are combined to give a logarithmic response. The current consumption of the device can be reduced by turning off the either the first stage, the last stage of the logamp, or both, by setting the LOGAMP\_DIS\_FIRST and LOGAMP\_DIS\_LAST bits. Disabling the stages will reduce the input dynamic range on the lower side of the range (see  $\boxtimes$  6-4). The pedestal noise floor will be lower because the gain stages are disabled, but the minimum detectable signal value becomes higher due to the reduced dynamic range. Depending on the received input signal strength, stages can be disabled to get optimum object detection. For very small inputs, all stages should be enabled to get maximum input dynamic range even though the noise floor is higher.  $\boxtimes$  6-6,  $\boxtimes$  6-7, and  $\boxtimes$  6-8 show the effect on the log conformance error when all stages are enabled, when the last stage is disabled, and when both first and last stages are disabled. When stages are disabled, a lower error is obtained with a lower noise floor, but the input dynamic range is reduced.

At the output of the logamp, the user can apply an adjustment to the intercept of the logamp curve. This is denoted by the  $K_X$  factor in  $\not \equiv 1$ . The intercept adjustment is controlled by the LOGAMP\_INT\_ADJ bits.  $\not \equiv 7-3$  shows the nominal values of  $K_X$  factor corresponding to register values, and  $\not \equiv 6-14$  shows its effect on the transfer function.

LOGAMP\_INT\_ADJ  $K_X$ 0x00 1 0x01 1.155 0x02 1.334 0x03 1.54 0x04 1.778 2.054 0x05 0x06 2.371 0x07 2.738 80x0 1 0x09 0.931 0.866 0x0A 0x0B 0.806 0x0C 0.75 0x0D 0.698 0x0E 0.649 0x0F 0.604

表 7-3. Logamp Intercept Adjustment

The output of the logamp is filtered using a low-pass filter to remove the high-frequency components and provide a sufficient peak hold time for the demodulated envelope signal. The cut-off frequency of the low-pass filter is set by the internal impedance of the FLT pin and the value of an external capacitor connected to the pin. As this filter capacitance ( $C_{FLT}$ ) suppresses the high frequency fluctuations, it also slows down the response time of the logamp. Higher  $C_{FLT}$  capacitance will result in lower peak-to-peak voltage variations at VOUT, and slower rise and fall times for the VOUT voltage to reach its maximum value for a given input signal. A nominal value can be calculated using  $\frac{1}{5}$ , and must be optimized depending on the application.

The output of the low-pass filter is buffered to the VOUT pin using an internal buffer. The buffer is designed to support an ADC input of a MCU. It is possible to change output dynamic range of the VOUT buffer using the VOUT\_SCALE\_SEL bit. Once the range is set, the gain of the VOUT buffer can be set by the LOGAMP\_SLOPE\_ADJ bits. The slope variation of the receiver analog front end is show in  $\boxtimes$  6-13.

Echo interrupt signal is available on the OUT4 pin that goes high when the signal on the VOUT pin crosses a threshold as defined by the ECHO\_INT\_THR\_SEL bits. As long as the VOUT signal is higher than this threshold, the echo interrupt signal is held high. The signal goes low asynchronously when the VOUT signal drops below the programmed threshold. This signal can be used to interrupt a MCU when an object has been detected. The threshold value is also dependent on the setting of the VOUT\_SCALE\_SEL bit.

A zero-crossing signal is output at the OUT3 pin which can be used to validate the frequency of the received echo signal to provide robustness against interference from other signals. This zero-crossing signal is derived from the raw amplified input signal from a particular stage as it is being demodulated in the logamp block. This function is disabled at device power up. but can be enabled by setting the ZC\_CMP\_EN bit. When enabled, the ZC\_CMP\_STG\_SEL bits are used to select which logamp gain stage is used to generate the zero crossing signal while the ZC\_CMP\_HYST bits control the hysteresis of the zero-crossing comparator. The stage selection to see the OUT3 pin toggling depends on the strength of signal received by the logamp and has to be configured depending on the application. For large amplitude of input signal, a lower stage of the logamp should be selected, whereas for lower amplitude signal, a higher stage should be selected. To avoid switching noise generated by the toggling of the zero-crossing comparator when the ZC\_EN\_ECHO\_INT bit is set, the zero-crossing output will be only enabled while the echo interrupt signal is high.

#### 7.4 Device Functional Modes

The device has four functional modes:

## Sleep Mode

Ultra-low current consumption sleep mode

In this mode, all major blocks of the device are disabled, including VDRV regulation. The SPI interface is still active. This transition into and out of this mode is done using the SLEEP\_MODE\_EN register bit. Upon issuing a command to exit this mode, the device transitions to other modes only when the VDRV pin reaches the programmed regulation voltage.

# Standby Mode

Low current standby mode

In this state, the VDRV regulation is active, but other analog blocks are shut down to reduce quiescent current consumption. The STDBY\_MODE\_EN bit is used to enter and exit this mode through SPI. The device can transition very quickly from this state to one of the active states for bursting and listening.

## Listen Mode

Default mode of the device

This is the default mode of

This is the default mode of the device when it is not in Sleep mode or Standby mode. In this mode, there is no activity on the transmitter block and the device is actively listening for any ultrasonic signals.

## Burst Mode

Mode in which the device is enabled to start a burst to drive the transducer

In this mode, the transmitter blocks are active and enabled to drive the transducer depending on when the start of burst occurs. The receiving path is also active at the same time listening for signals at the input. This mode is entered when a burst enable event occurs and exited when an end of burst occurs as described in *Burst Generation* section.

☑ 7-7 shows an example of the transitions between the different modes of the device for IO\_MODE = 0, where the burst is activated through a SPI command and end of burst occurs as the number of programmed pulses are sent.

☑ 7-7. Device Modes Timing Diagram

#### Note

- The transition to standby or active mode (listen or burst) from power-up or sleep mode is done only once the VDRV voltage crosses the programmed VDRV VOLTAGE LEVEL bit, or is higher 64 ms, whichever occurs earlier.

- In the case when VDRV is disabled, the device immediately transitions from power or sleep mode to standby and active modes.

## 7.5 Programming

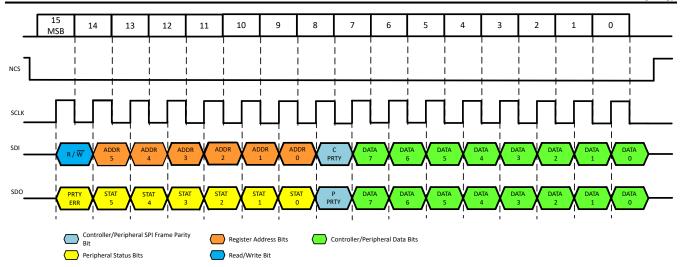

The primary communication between the IC and the external MCU is through an SPI bus that provides fullduplex communications in a controller-peripheral configuration. The external MCU is always a SPI controller that sends command requests on the SDI pin and receives device responses on the SDO pin. The device is always a SPI peripheral device that receives command requests and sends responses to the external MCU over the SDO line. The following lists the characteristics of the SPI:

- The SPI is a 4-pin interface.

- The frame size is 16 bits and is assigned as follows:

Controller-to-peripheral (MCU to TUSS4440 over the SDI line)

1 RW bit, 6 bits for the register address, 1 ODD parity bit for entire SPI frame, 8 bits for data

to MCU over the SDO line)

Peripheral-to-controller (TUSS4440 1 bit for Controller Parity error reporting during previous frame reception, 6 bits for the status, 1 bit for ODD parity for entire SPI frame. 8 bits for data

- SPI commands and data are shifted with the MSB first and the LSB last.

- The SDO line is sampled on the falling edge of the SCLK pin.

- The SDI line is shifted out on the rising edge of the SCLK pin.

The SPI communication begins with the NCS falling edge and ends with the NCS rising edge. The NCS highlevel maintains the SPI peripheral-interface in the RESET state. The SDO output is in the tri-state condition.

The SPI does not support back-to-back SPI frame operation. After each SPI transfer the NCS pin must go from low to high before the next SPI transfer can begin.

図 7-8. 16-Bit SPI Frame

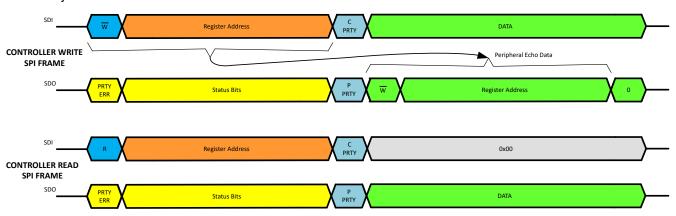

☑ 7-9 shows a SPI transfer sequence between the controller and the peripheral TUSS4440 device. When the controller is writing a SPI frame, the parity error bit indicates if there was a parity error for the previous frame. When the controller is transmitting the data for the SPI write, the peripheral echoes back register address that was sent just before in the command.

図 7-9. SPI Transfer Sequence

The status bits are defined in 表 7-4:

表 7-4. SPI Interface Status Bits Description

| STATUS BIT             | DESCRIPTION                                                                                                                        |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| STAT 5 - VDRV_READY    | Set when VDRV power regulator has reached the programmed voltage level. This is also indicated by VDRV_READY bit.                  |

| STAT 4- PULSE_NUM_FLT  | Set if the burst sequence was terminated before completing the pulse number selected. This is also indicated by PULSE_NUM_FLT bit. |

| STAT 3 - DRV_PULSE_FLT | Set if there is a "stuck" fault detected during pulsing in a burst sequence. This is also indicated by DRV_PULSE_FLT               |

| STAT 2 - EE_CRC_FLT    | Set if there is a CRC Error when loading internal EEPROM memory. This is also indicated by EE_CRC_FLT bit.                         |

| STAT <1:0> - DEV_STATE | Device State:<br>00 - LISTEN<br>01 - BURST<br>10 - STANDBY<br>11 - SLEEP                                                           |

# 7.6 Register Maps

This section lists the REG\_USER registers that are part of the volatile memory that can be configured by the MCU at power up or any time during the operation of the device. For register bits that are marked reserved, their reset value should not be changed.

# 7.6.1 REG\_USER Registers

表 7-5 lists the REG\_USER registers. All register offset addresses not listed in 表 7-5 should be considered as reserved locations and the register contents should not be modified.

表 7-5. REG USER Registers

|      |                 | Register Name               | Section |

|------|-----------------|-----------------------------|---------|

| 0x10 | BPF_CONFIG_1    | Bandpass filter settings    | Go      |

| 0x11 | BPF_CONFIG_2    | Bandpass filter settings    | Go      |

| 0x12 | DEV_CTRL_1      | Log-amp configuration       | Go      |

| 0x13 | DEV_CTRL_2      | Log-amp configuration       | Go      |

| 0x14 | DEV_CTRL_3      | Device Configuration        | Go      |

| 0x16 | VDRV_CTRL       | VDRV Regulator Control      | Go      |

| 0x17 | ECHO_INT_CONFIG | Echo Interrupt Control      | Go      |

| 0x18 | ZC_CONFIG       | Zero Crossing configuration | Go      |

| 0x19 | XFMR_DRV_LIM    | Transformer drive config    | Go      |

| 0x1A | BURST_PULSE     | Burst pulse configuration   | Go      |

| 0x1B | TOF_CONFIG      | Time of Flight Config       | Go      |

| 0x1C | DEV_STAT        | Fault status bits           | Go      |

| 0x1D | DEVICE_ID       | Device ID                   | Go      |

| 0x1E | REV_ID          | Revision ID                 | Go      |

Complex bit access types are encoded to fit into small table cells.  $\frac{1}{2}$  7-6 shows the codes that are used for access types in this section.

表 7-6. REG\_USER Access Type Codes

| Access Type            | Code | Description                            |  |  |  |  |

|------------------------|------|----------------------------------------|--|--|--|--|

| Read Type              |      |                                        |  |  |  |  |

| R                      | R    | Read                                   |  |  |  |  |

| Write Type             |      |                                        |  |  |  |  |

| W                      | W    | Write                                  |  |  |  |  |

| Reset or Default Value |      |                                        |  |  |  |  |

| -n                     |      | Value after reset or the default value |  |  |  |  |

#### 7.6.1.1 BPF\_CONFIG\_1 Register (Address = 0x10) [reset = 0x0]

BPF\_CONFIG\_1 is shown in 表 7-7.

Return to the Summary Table.

表 7-7. BPF\_CONFIG\_1 Register Field Descriptions

| _ |     |                 |      |       | <u> </u>                                                                                                                                                              |

|---|-----|-----------------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Bit | Field           | Туре | Reset | Description                                                                                                                                                           |

|   | 7   | BPF_FC_TRIM_FRC | R/W  |       | Override factor settings for Bandpass filter trim and control via BPF_FC_TRIM register. Valid only when BPF_BYPASS = 0 0x0 = Factory trim 0x1 = Override Factory trim |

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

表 7-7. BPF\_CONFIG\_1 Register Field Descriptions (continued)

| Bit | Field        | Туре | Reset | Description                                                                                                                                                                                                                                              |

|-----|--------------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6   | BPF_BYPASS   | R/W  | 0x0   | Select between Bandpass filter or high pass filter  0x0 = BPF Enabled  0x1 = HPF Enabled (BPF Bypass)                                                                                                                                                    |

| 5:0 | BPF_HPF_FREQ | R/W  | 0x0   | If BPF_BYPASS = 0: Band pass filter center frequency. See "Bandpass filter center frequency configuration" table If BPF_BYPASS = 1: High pass filter corner frequency 0x00 - 0x0F - 200kHz 0x10 - 0x1F - 400kHz 0x20 - 0x2F - 50kHz 0x30 - 0x3F - 100kHz |

# 7.6.1.2 BPF\_CONFIG\_2 Register (Address = 0x11) [reset = 0x0]

BPF\_CONFIG\_2 is shown in 表 7-8.

Return to the Summary Table.

# 表 7-8. BPF\_CONFIG\_2 Register Field Descriptions

| Bit | Field       | Туре | Reset | Description                                                                                                                                           |

|-----|-------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | RESERVED    | R    | 0x0   | Reserved                                                                                                                                              |

| 5:4 | BPF_Q_SEL   | R/W  | 0x0   | Bandpass filter Q factor. Valid only when BPF_BYPASS = 0 0x0 = 4                                                                                      |

|     |             |      |       | 0x1 = 5                                                                                                                                               |

|     |             |      |       | 0x2 = 2                                                                                                                                               |

|     |             |      |       | 0x3 = 3                                                                                                                                               |

| 3:0 | BPF_FC_TRIM | R/W  | 0x0   | Offset BPF_HPF_FREQ when BPF_FC_TRIM_FRC = 1: BPF_HPF_FREQ = BPF_HPF_FREQ + BPF_FC_TRIM See "Bandpass filter center frequency range extension" table. |

# 7.6.1.3 DEV\_CTRL\_1 Register (Address = 0x12) [reset = 0x0]

DEV\_CTRL\_1 is shown in 表 7-9.

Return to the Summary Table.

# 表 7-9. DEV\_CTRL\_1 Register Field Descriptions

| Bit | Field            | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|------------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | LOGAMP_FRC       | R/W  | 0x0   | Override for factory settings for LOGAMP_SLOPE_ADJ and LOGAMP_INT_ADJ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6:4 | LOGAMP_SLOPE_ADJ | R/W  | 0x0   | Slope or gain adjustment at the final output on VOUT pin. Slope adjustment depends on the setting of VOUT_SCALE_SEL.  0x0 = 3.0 × VOUT_SCALE_SEL+4.56 × VOUT_SCALE_SEL V/V  0x1 = 3.1 × VOUT_SCALE_SEL+4.71 × VOUT_SCALE_SEL V/V  0x2 = 3.2 × VOUT_SCALE_SEL+4.86 × VOUT_SCALE_SEL V/V  0x3 = 3.3 × VOUT_SCALE_SEL+5.01 × VOUT_SCALE_SEL V/V  0x4 = 2.6 × VOUT_SCALE_SEL+3.94 × VOUT_SCALE_SEL V/V  0x5 = 2.7 × VOUT_SCALE_SEL+4.10 × VOUT_SCALE_SEL V/V  0x6 = 2.8 × VOUT_SCALE_SEL+4.25 × VOUT_SCALE_SEL V/V  0x7 = 2.9 × VOUT_SCALE_SEL+4.4 × VOUT_SCALE_SEL V/V |

| 3:0 | LOGAMP_INT_ADJ   | R/W  | 0x0   | Logamp Intercept adjustment. See "Logamp intercept adjustment" table in specification for values.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Product Folder Links: TUSS4440

# 7.6.1.4 DEV\_CTRL\_2 Register (Address = 0x13) [reset = 0x0]

DEV\_CTRL\_2 is shown in 表 7-10.

Return to the Summary Table.

# 表 7-10. DEV\_CTRL\_2 Register Field Descriptions

| Bit | Field            | Туре | Reset | Description                                                                                                       |

|-----|------------------|------|-------|-------------------------------------------------------------------------------------------------------------------|

| 7   | LOGAMP_DIS_FIRST | R/W  | 0x0   | Disable first logamp stage to reduce quiescent current                                                            |

| 6   | LOGAMP_DIS_LAST  | R/W  | 0x0   | Disable last logamp stage quiescent current                                                                       |

| 3   | RESERVED         | R    | 0x0   | Reserved                                                                                                          |

| 2   | VOUT_SCALE_SEL   | R/W  | 0x0   | Select VOUT scaling  0x0 = Select Vout gain to map output to 3.3 V  0x1 = Select Vout gain to map output to 5.0 V |

| 1:0 | LNA_GAIN         | R/W  | 0x0   | Adjust LNA Gain in V/V 0x0 = 15 V/V 0x1 = 10 V/V 0x2 = 20 V/V 0x3 = 12.5 V/V                                      |

# 7.6.1.5 DEV\_CTRL\_3 Register (Address = 0x14) [reset = 0x0]

DEV\_CTRL\_3 is shown in 表 7-11.

Return to the Summary Table.

表 7-11. DEV\_CTRL\_3 Register Field Descriptions

| SC / 11. DEV_OTTLE_0 Tregister Field Descriptions |                |      |       |                                                                                                                                                                                                                                                                                                                                                                                        |  |  |