# MCPC Compatible USB Port Multimedia Switch Supports USB, UART, Audio, ID, MIC, and Load Switch

Check for Samples: TSU6721YFF

## FEATURES

- Switch Matrix

- USB and UART Switch support USB 2.0 HS

- Audio Switch with Negative Signal Capability

- ID Bypass Switch

- VBUS to MIC Switch

- DP to MIC Switch to Support MCPC

- Load Switch

- 100 mΩ Load Switch

- OTG Support

- 28 V VBUS Rating with Over-voltage Protection

- Programmable Overcurrent Limiter/Protection

- Charger Detection

- USB BCDv1.2 compliant

- VBUS Detection

- Data Contact Detection

- Primary and Secondary Detection

- Compatible Accessories

- USB Chargers (DCP, CDP)

- Apple Charger

- USB Data Port

- Audio Headset with MIC and Remote

- Docking Support

- Factory Cable

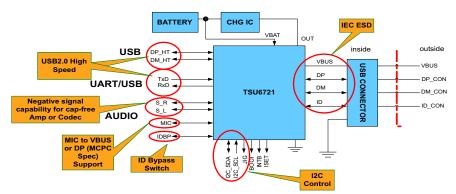

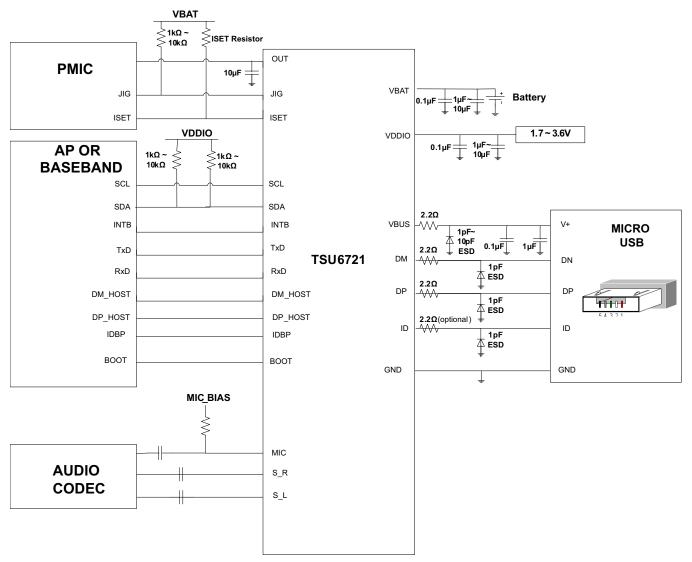

## **APPLICATION DIAGRAM**

- Additional Features

- I2C Interface with Host Processor

- Switches Controlled by Automatic Detection or Manual Control

- Interrupts Generated for Plug/Unplug

- Decoupling FET Switch to VBUS Added to Reduce Degradation on MIC Line

- Support Control Signals used In Manufacturing (JIG, BOOT)

- ESD Performance Tested Per JESD 22

- 4000-V Human-Body Model (A114-B, Class II)

- 1500-V Charged-Device Model (C101)

- IEC ESD Performance

- ±8 kV Contact Discharge (IEC 61000-4-2) for VBUS/DP/DM/ID to GND

## APPLICATIONS

- Cell Phones and Smart Phones

- Tablet PCs

- Digital Cameras and Camcorders

- GPS Navigation Systems

- Micro USB Interface with USB/UART/AUDIO

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### **ORDERING INFORMATION**

For package and ordering information, see the Package Option Addendum at the end of this document.

#### DESCRIPTION

TSU6721 is a high performance USB port multimedia switch featuring automatic switching and accessory detection. The device connects a common USB port to pass audio, USB data, charging, On The Go (OTG) and factory mode signals. The audio path has negative signal capability includes left (mono/stereo), right (stereo) as well as microphone signals. Furthermore, TSU6721 is compatible with the MCPC specification.

TSU6721 features impedance detection which supports the detection of various accessories that are attached through DP, DM and ID pins of the USB connector. The switch is controlled by automatic switching or manually through I<sup>2</sup>C.

TSU6721 has an integrated low resistive Load Switch that is used to isolate the charger from the external connector. OverVoltage Protection and programmable OverCurrent Limiter/Protection are additional features included to the Load Switch.

The charger detection satisfies USB charger specification v1.2. In addition to DCP, CDP and SDP, the device also detects Apple Chargers.

Power for this device is supplied through VBAT of the system or through VBUS when attached. TSU6721 supports factory mode testing when a USB/UART JIG cable is used in development and manufacturing.

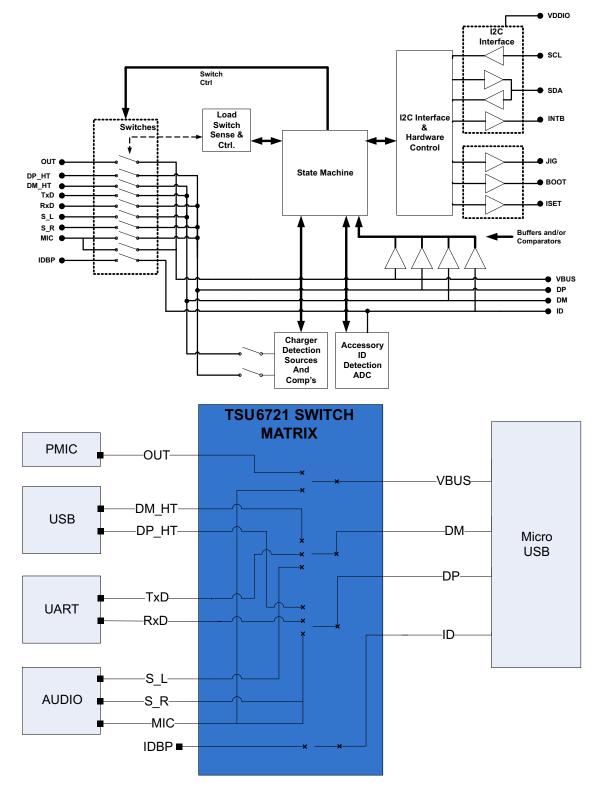

#### **BLOCK DIAGRAM**

# TSU6721YFF

SCDS345-JUNE 2013

www.ti.com

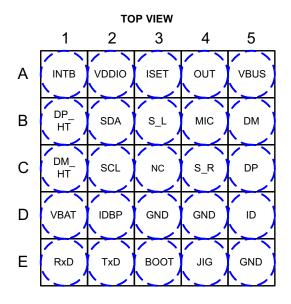

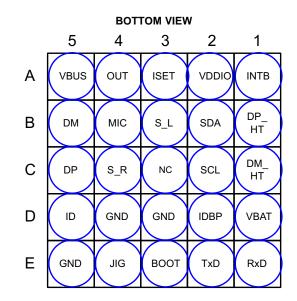

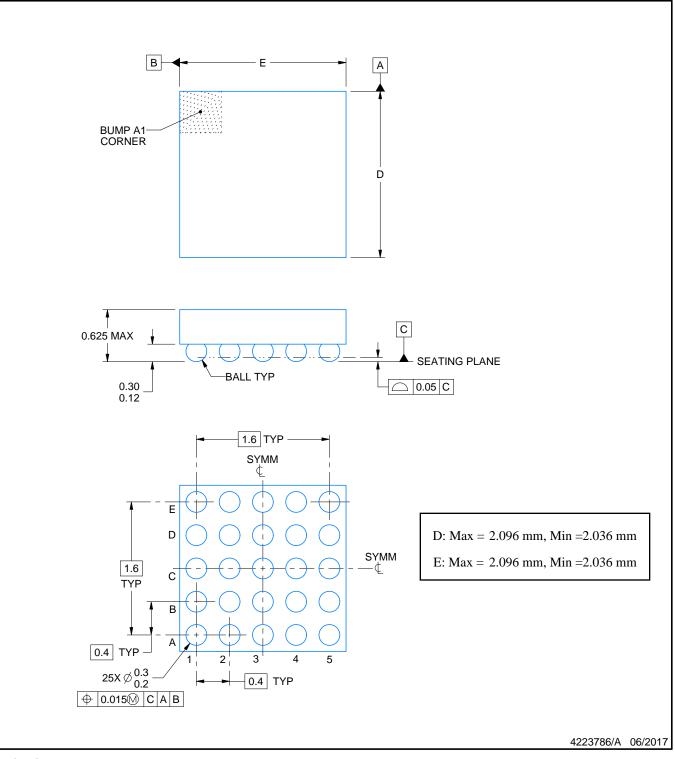

### **PIN OUT**

#### **PIN FUNCTIONS**

| BALL NO.   | PIN NAME | TYPE | DESCRIPTION                                                             |  |

|------------|----------|------|-------------------------------------------------------------------------|--|

| D1         | VBAT     | -    | 3.0 – 4.4V Battery supply voltage                                       |  |

| A2         | VDDIO    | -    | 1.8 ~ 3.3V Logic Supply                                                 |  |

| A5         | VBUS     | I    | USB connector VBUS                                                      |  |

| A4         | OUT      | 0    | one charger output                                                      |  |

| E5, D3, D4 | GND      | -    | Ground                                                                  |  |

| B1         | DP_HT    | I/O  | USB data plus                                                           |  |

| C1         | DM_HT    | I/O  | USB data minus                                                          |  |

| D2         | IDBP     | I/O  | USB ID data                                                             |  |

| E1         | RxD      | I/O  | UART receive data                                                       |  |

| E2         | TxD      | I/O  | UART transmit data                                                      |  |

| C3         | NC       | -    | Not connected internally                                                |  |

| B4         | MIC      | I/O  | Microphone signal                                                       |  |

| C4         | S_R      | I/O  | Stereo headset right sound                                              |  |

| B3         | S_L      | I/O  | Mono or stereo headset left sound                                       |  |

| C2         | SCL      | I    | I2C clock                                                               |  |

| B2         | SDA      | I/O  | I2C data                                                                |  |

| C5         | DP       | I/O  | Common USB connector plus I/O port                                      |  |

| B5         | DM       | I/O  | Common USB connector minus I/O port                                     |  |

| D5         | ID       | I/O  | Common USB connector ID I/O port                                        |  |

| A1         | INTB     | 0    | Interrupt signal when peripheral is plugged/unplugged. Push-pull output |  |

| A3         | ISET     | 0    | High current charger detected. Open-drain output                        |  |

| E4         | JIG      | 0    | GPIO factory output. Open-drain output                                  |  |

| E3         | BOOT     | 0    | GPIO factory output. Push-pull output                                   |  |

#### ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range (unless otherwise noted)

|                                      |                                                |                                                                | MIN  | MAX      | UNIT |

|--------------------------------------|------------------------------------------------|----------------------------------------------------------------|------|----------|------|

| VBUS                                 | Supply voltage from USB                        | connector                                                      | -0.5 | 28       | V    |

| VBAT                                 | Supply voltage from batte                      | ry                                                             | -0.5 | 6        | V    |

| VDDIO                                | Logic supply voltage                           | Logic supply voltage                                           |      | 4.6      | V    |

| VBUS_OUT                             | Phone charger output                           |                                                                | -0.5 | 7        | V    |

| DP                                   | DP Connector voltage                           |                                                                | -0.5 | VBAT+0.5 | V    |

| DM                                   | DM Connector voltage                           |                                                                | -0.5 | VBAT+0.5 | V    |

| ID                                   | ID Connector voltage                           |                                                                | -0.5 | VBAT+0.5 | V    |

| IDBP                                 | ID Host Side voltage                           |                                                                | -0.5 | VBAT+0.5 | V    |

| VAUDIO                               |                                                | Audio Switch (S_L, S_R)                                        | -1.5 | VBAT+0.5 |      |

| VMIC                                 | Switch I/O voltage range                       | Mic Switch (MIC)                                               | -0.5 | VBAT+0.5 | V    |

| VUSB/VUART                           |                                                | USB/UART Switch                                                | -0.5 | VBAT+0.5 |      |

| VJIG & VISET                         | JIG and ISET voltage                           | JIG and ISET voltage                                           |      | VBAT+0.5 | V    |

| VLOGIC_O                             | Voltage applied to logic of                    | utput (SCL, SDA, INTB, BOOT)                                   | -0.5 | VDDIO    | V    |

| IBUS                                 | Peak input current on VB                       | BUS pin (12.5% duty cycle)                                     |      | 2.0      | А    |

| 1603                                 | Peak input current on VB                       | JS pin (3% duty cycle, 4ms on-time)                            |      | 2.5      | A    |

| IBUS_OUT                             | Peak input current on VB                       | Peak input current on VBUS pin (12.5% duty cycle)              |      |          | А    |

| 1603_001                             | Peak input current on VB                       |                                                                | 2.5  | A        |      |

| I <sub>ISET</sub> & I <sub>JIG</sub> | ISET and JIG pins peak of                      | urrent                                                         |      | 50       | mA   |

| IK                                   | Analog port diode current                      |                                                                | -50  | 50       | mA   |

| ISW-DC                               | ON-state continuous swite                      | ch current                                                     | -60  | 60       | mA   |

| ISW PEAK                             | ON-state peak switch cur                       | rent                                                           | -150 | 150      | mA   |

| ІІК                                  | Digital logic input clamp<br>current VDDIO < 0 |                                                                |      | -50      | mA   |

| ILOGIC_O                             | Continuous current throug                      | Continuous current through logic output (SCL, SDA, INTB, BOOT) |      | 50       | mA   |

| IGND                                 | Continuous current throug                      | Continuous current through GND                                 |      |          | mA   |

| Tstg                                 | Storage temperature rang                       | e                                                              | -65  | 150      | °C   |

## THERMAL IMPEDANCE RATINGS

|               |                 |             | VALUE | UNIT | 1 |

|---------------|-----------------|-------------|-------|------|---|

| $\theta_{JA}$ | Package thermal | YFP package | 98.8  | °C/W | 1 |

|               | impedance       |             |       |      | 1 |

#### SUMMARY OF TYPICAL CHARACTERISTICS

| AMBIENT TEMPERATURE = 25°C                                 | USB/UART PATH        | AUDIO PATH    | MIC PATH       |

|------------------------------------------------------------|----------------------|---------------|----------------|

| Number of channels                                         | 2                    | 1             | 1              |

| ON-state resistance (r <sub>on</sub> )                     | 6 Ω / 7 Ω (USB/UART) | 2.5 Ω         | 40 Ω           |

| ON-state resistance match ( $\Delta_{ron}$ )               | 0.2 Ω / 1.5 Ω        | 0.15 Ω        | N/A            |

| ON-state resistance flatness (ron(flat))                   | 1.4 Ω / 1.4 Ω        | 0.15 Ω        | N/A            |

| Turn-on/Turn-off time (t <sub>ON</sub> /t <sub>OFF</sub> ) | 130 µs/ 100 µs       | 200 µs/100 µs | 260 µs /180 µs |

| Bandwidth (BW)                                             | 510 MHz              | 450MHz        | 250 MHz        |

| OFF isolation (O <sub>ISO</sub> )                          | –26 dB at 250 MHz    | –100 dB       | –95 dB         |

| Crosstalk (X <sub>TALK</sub> )                             | –32 dB at 250 MHz    | –85 dB        | –85 dB         |

| Total Harmonic Distortion (THD)                            | N/A                  | 0.05%         | 0.46%          |

| Leakage current (I <sub>IO(ON)</sub> )                     | 50 nA                | 200 nA        | 5 nA           |

SCDS345-JUNE 2013

www.ti.com

STRUMENTS

# **RECOMMENDED OPERATING CONDITIONS**

over operating free-air temperature range (unless otherwise noted)

| PARAMETER         | DESCRIPTION             | MIN  | MAX | UNITS |

|-------------------|-------------------------|------|-----|-------|

| V <sub>BUS</sub>  | VBUS voltage            | 4.0  | 6.5 | V     |

| V <sub>BAT</sub>  | VBAT voltage            | 3.0  | 4.4 | V     |

| V <sub>DDIO</sub> | VDDIO voltage           | 1.65 | 3.6 | V     |

| ID_Cap            | ID capacitance          |      | 3   | nF    |

| USB_I/O           | USB path signal range   | 0    | 3.6 | V     |

| UART_I/O          | UART path signal range  | 0    | 2.7 | V     |

| Audio_I/O         | Audio path signal range | -1.5 | 1.5 | V     |

| MIC_I/O           | MIC path signal range   | 0    | 2.3 | V     |

| Temperature       | Operating Temperature   | -40  | 85  | °C    |

## **ELECTRICAL SPECIFICATIONS**

## DIGITAL SIGNALS – I<sup>2</sup>C INTERFACE (SCL and SDA)

$T_A = -40^{\circ}C$  to 85°C, Typical values are at  $T_A = 25^{\circ}C$  (unless otherwise noted)

|                   | PARAMETER                     | TEST CONDITIONS          | MIN         | МАХ         | UNIT |

|-------------------|-------------------------------|--------------------------|-------------|-------------|------|

| V <sub>DDIO</sub> | Logic and I/O supply voltage  |                          | 1.65        | 3.6         | V    |

| VIH               | High-level input voltage      |                          | VDDIO × 0.7 | VDDIO       | V    |

| V <sub>IL</sub>   | Low-level input voltage       |                          | 0           | VDDIO × 0.3 | V    |

| V <sub>OH</sub>   | SDA High-level output voltage | $I_{OH} = -3 \text{ mA}$ | VDDIO × 0.7 |             | V    |

| V <sub>OL</sub>   | SDA Low-level output voltage  | $I_{OL} = 3 \text{ mA}$  | 0           | 0.4         | V    |

| f <sub>SCL</sub>  | SCL frequency                 |                          |             | 400         | kHz  |

## JIG AND ISET FAST-MODE CHARGER OUTPUT (OPEN-DRAIN OUTPUT)

$T_A = -40^{\circ}C$  to 85°C, Typical values are at  $T_A = 25^{\circ}C$  (unless otherwise noted)

|          | PARAMETER                | TEST CONDITIONS                       | MIN | MAX | UNIT |

|----------|--------------------------|---------------------------------------|-----|-----|------|

| VOL_JIG  | Low-level output voltage | I <sub>OL</sub> = 10 mA, VBAT = 3.0 V | 0   | 0.5 | V    |

| VOL_ISET | Low-level output voltage | I <sub>OL</sub> = 10 mA, VBAT = 3.0 V | 0   | 0.7 | V    |

## INTB AND BOOT (PUSH-PULL OUTPUT)

$T_A = -40^{\circ}$ C to 85°C, Typical values are at  $T_A = 25^{\circ}$ C (unless otherwise noted)

|                 | PARAMETER                 | TEST CONDITIONS                          | MIN  | MAX   | UNIT |

|-----------------|---------------------------|------------------------------------------|------|-------|------|

| V <sub>OH</sub> | High-level output voltage | I <sub>OH</sub> = -4 mA , VDDIO = 1.65 V | 1.16 | VDDIO | V    |

| V <sub>OL</sub> | Low-level output voltage  | $I_{OL} = 4 \text{ mA}$ , VDDIO = 1.65 V | 0    | 0.33  | V    |

## TOTAL SWITCH CURRENT CONSUMPTION

$T_A = -40^{\circ}C$  to 85°C, Typical values are at  $T_A = 25^{\circ}C$  (unless otherwise noted)

|                 | PARAMETER                          | TEST CONDITIONS                | MIN | TYP | MAX | UNIT |

|-----------------|------------------------------------|--------------------------------|-----|-----|-----|------|

| IBAT(Standby)   | VBAT Standby Current Consumption   | VBUS = 0 V, Idle state         |     | 36  | 50  | μA   |

| IBAT(Operating) | VBAT Operating Current Consumption | VBUS = 0 V, USB switches ON    |     | 60  | 80  | μA   |

| IVBUS           | VBUS Operating Current Consumption | No load on OUT pin, VBUS = 5 V |     | 135 | 155 | μA   |

## **VBUS CAP SWITCH CHARACTERISTICS**

$T_A = -40^{\circ}$ C to 85°C, Typical values are at  $T_A = 25^{\circ}$ C (unless otherwise noted)

| PARAMETER                              | TEST CONDITIONS                     | MIN | TYP | MAX | UNIT |

|----------------------------------------|-------------------------------------|-----|-----|-----|------|

| RDS-VBUSCAP VBUS CAP switch resistance | VBUS = 5 V, IOUT = $-20 \text{ mA}$ |     | 90  |     | Ω    |

## **VOLTAGE PROTECTION**

$T_A = -40^{\circ}C$  to 85°C, Typical values are at  $T_A = 25^{\circ}C$  (unless otherwise noted)

|                         | PARAMETER                            | TEST CONDITIONS                    | MIN | TYP  | MAX | UNIT |

|-------------------------|--------------------------------------|------------------------------------|-----|------|-----|------|

| V <sub>VBUS_UVLO</sub>  | V <sub>BUS</sub> under voltage+      | Voltage is Rising, device power-up | 3.0 | 3.25 | 3.6 | V    |

|                         | V <sub>BUS</sub> under voltage-      | Voltage is Falling, device reset   | 2.7 | 3    | 3.3 |      |

| V <sub>VBUS_VALID</sub> | V <sub>BUS</sub> interrupt threshold | Voltage is Rising                  |     | 3.6  |     | V    |

| V <sub>VBAT_UVLO</sub>  | V <sub>BAT</sub> under voltage+      | Voltage is Rising, device power-up | 2.5 | 2.8  | 3.1 | V    |

|                         | V <sub>BAT</sub> under voltage-      | Voltage is Falling, device reset   | 2.3 | 2.6  | 2.9 |      |

## LOAD SWITCH CHARACTERISTICS

$T_A = -40^{\circ}C$  to 85°C, Typical values are at  $T_A = 25^{\circ}C$  (unless otherwise noted)

|                    | PARAMETER                                         |                                               | TEST CONDITIONS                                            | MIN  | TYP | MAX  | UNIT |

|--------------------|---------------------------------------------------|-----------------------------------------------|------------------------------------------------------------|------|-----|------|------|

| RDS-<br>VBUSSWITCH | VBUS switch resistance                            | VBUS = 5 V,                                   | IOUT = 100 mA                                              |      | 90  | 150  | mΩ   |

| t <sub>ONa</sub>   | Turn-ON time automatic mode                       | RL = 36 Ω, C                                  | L = 400 pF, Vbus rising > 3.6V                             |      | 175 |      | ms   |

| t <sub>OFFa</sub>  | Turn-OFF time automatic mode                      | RL = 36 Ω, C                                  | L = 400 pF, Vbus falling < 3.6V                            |      | 2.5 |      | ms   |

| t <sub>ONm</sub>   | Turn-ON time manual mode                          | RL = 36 Ω, C<br>bit                           | L = 400 pF, From receipt of I2C ACK                        |      | 230 |      | μs   |

| t <sub>OFFm</sub>  | Turn-OFF time manual mode                         | RL = 36 Ω, C<br>bit                           | L = 400 pF, From receipt of I2C ACK                        |      | 180 |      | μs   |

|                    |                                                   |                                               | I2C reg0x22h, Bit [2:0] = 000                              | 0.8  | 1.0 | 1.2  |      |

|                    | Programmable overcurrent                          |                                               | I2C reg0x22h, Bit [2:0] = 001 (default)                    | 1.3  | 1.5 | 1.7  | •    |

| I <sub>OCP</sub>   | protection                                        | $V_{BUS} = 5.5V$                              | I2C reg0x22h, Bit [2:0] = 010                              |      | 2.0 |      | A    |

|                    |                                                   |                                               | I2C reg0x22h, Bit [2:0] = 011                              |      | 2.0 |      |      |

|                    | Programmable overcurrent limiter                  |                                               | I2C reg0x21h, Bit [7:5] = 000                              | 1.25 | 1.5 | 1.75 |      |

| 1                  |                                                   |                                               | I2C reg0x21h, Bit [7:5] = 001 (default)                    | 1.67 | 2.0 | 2.33 | •    |

| I <sub>OCL</sub>   |                                                   | $V_{BUS} = 5.5V$                              | I2C reg0x21h, Bit [7:5] = 010                              |      | 2.5 |      | A    |

|                    |                                                   |                                               | I2C reg0x21h, Bit [7:5] = 011                              |      | 2.5 |      |      |

| <b>VBUS OVERVO</b> | LTAGE PROTECTION (OVP)                            |                                               |                                                            |      |     |      |      |

| VBUS<br>VOVP       | Input overvoltage protection threshold            | VBUS increas                                  | sing from 6 V to 8 V                                       | 6.8  | 7   | 7.2  | V    |

| VBUS<br>tOFF(OVP)  | OVP delay                                         | Delay from V                                  | <sub>BUS</sub> > VOVP to Load switch OFF                   |      | 200 |      | μs   |

| VBUS<br>VHYS-OVP   | Hysteresis on OVP                                 | VBUS decrea                                   | asing from 8 V to 6 V                                      |      | 140 |      | mV   |

| VBUS<br>tON(OVP)   | Recovery time from input<br>overvoltage condition | Delay from V                                  | Delay from V <sub>BUS</sub> < VOVP-VHYS, to Load switch ON |      | 9   |      | ms   |

| OTP<br>rOTP        | OTP Rising Turn Off                               | Temperature rising until load switch shut off |                                                            |      | 130 |      | °C   |

| OTP<br>fOTP        | OTP Falling Turn On                               | Temperature<br>turn on                        | falling after OTP shutoff until switch                     |      | 120 |      | °C   |

TSU6721YFF SCDS345 – JUNE 2013

## TSU6721YFF

SCDS345-JUNE 2013

www.ti.com

TRUMENTS

XAS

# AUDIO SWITCH ELECTRICAL CHARACTERISTICS<sup>(1)(2)</sup>

$V_{BAT}$  = 3.0 V to 4.4 V,  $V_{DDIO}$  = 2.8 V,  $T_A$  = -40°C to 85°C, Typical values are at  $T_A$  = 25°C (unless otherwise noted)

|                                         | PARAMETER                                           |                                        | TEST CONDITIONS                                                                                                                   | MIN  | TYP  | MAX | UNIT |

|-----------------------------------------|-----------------------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------|------|-----|------|

| ANALOG SWI                              | тсн                                                 |                                        |                                                                                                                                   |      |      |     |      |

| V <sub>AUDIO</sub>                      | Analog signal range                                 |                                        |                                                                                                                                   | -1.5 |      | 3   | V    |

| r <sub>ON</sub>                         | ON-state resistance                                 | S_L or                                 | $V_{I} = \pm 0.8 \text{ V}, I_{O} = -20 \text{ mA}, V_{BAT} = 3.0 \text{ V}$                                                      |      | 2.5  | 5   | Ω    |

| $\Delta r_{ON}$                         | ON-state resistance match between channels          | S_R , DM or<br>DP                      | $V_{I} = 0.8 V, I_{I} = -20 mA, V_{BAT} = 3.0 V$                                                                                  |      | 0.15 | 0.5 | Ω    |

| r <sub>ON(flat)</sub>                   | ON-state resistance flatness                        |                                        | $V_1 = \pm 0.8 \text{ V}, I_0 = -20 \text{ mA}, V_{BAT} = 3.0 \text{ V}$                                                          |      | 0.15 | 0.5 | Ω    |

| I <sub>IO(OFF)</sub>                    | $V_{I} \text{ or } V_{O} \text{ OFF}$ leakage curre | nt                                     | $      (V_{I} = -0.8 \ V, \ V_{O} = 0.8 \ V) \ or \ (V_{I} = 0.8 \ V, \\ V_{O} = -0.8 \ V), \ V_{BAT} = 4.4 \ V, \ Switch \ OFF $ |      | 200  | 500 | nA   |

| I <sub>IO(ON)</sub>                     | VO ON leakage current                               |                                        | $V_{\rm I}$ = OPEN, $V_{\rm O}$ = –0.8 V or 0.8 V, $V_{\rm BAT}$ = 4.4 V, Switch ON                                               |      | 10   | 300 | nA   |

| DYNAMIC                                 |                                                     |                                        |                                                                                                                                   |      |      |     |      |

| t <sub>ON</sub>                         | Turn-ON time                                        | From                                   |                                                                                                                                   |      | 200  |     | μs   |

| t <sub>OFF</sub>                        | Turn-OFF time                                       | receipt of<br>I <sup>2</sup> C ACK bit | $V_{I}$ or $V_{O} = V_{BAT}$ , $R_{L} = 100 \ \Omega$ , $C_{L} = 35 \ pF$                                                         |      | 100  |     |      |

| C <sub>I(OFF)</sub>                     | VI OFF capacitance                                  |                                        |                                                                                                                                   |      | 5.5  |     | pF   |

| C <sub>O(OFF)</sub>                     | VO OFF capacitance                                  |                                        | DC bias = 0 V or 1.6 V f = 10 MHz, Switch OFF                                                                                     |      | 10   |     | pF   |

| C <sub>I(ON)</sub> , C <sub>O(ON)</sub> | VI, VO ON capacitance                               |                                        | DC bias = 0 V or 1.6 V f = 10 MHz, Switch ON                                                                                      |      | 13   |     | pF   |

| BW                                      | Bandwidth                                           |                                        | $R_L = 50 \Omega$ , Switch ON                                                                                                     |      | 450  |     | MHz  |

| O <sub>ISO</sub>                        | OFF Isolation                                       |                                        | f = 20 kHz, $R_L$ = 50 $\Omega$ , Switch OFF                                                                                      |      | -100 |     | dB   |

| X <sub>TALK</sub>                       | Crosstalk                                           |                                        | $f = 20 \text{ kHz}, R_L = 50 \Omega$                                                                                             |      | -85  |     | dB   |

| THD Total harmonic distortion           |                                                     |                                        | $R_L$ = 16 $\Omega,C_L$ = 20 pF, f = 20 Hz–20 kHz , 1.6 Vpp output                                                                |      | 0.05 |     | %    |

|                                         |                                                     |                                        | $R_L$ = 16 $\Omega,C_L$ = 20 pF, f = 20 Hz–20 kHz , 3 Vpp output                                                                  |      | 0.1  |     | %    |

(1)  $V_I$  is equal to the asserted voltage on S\_R and S\_L pins.  $V_O$  is equal to the asserted voltage on DP and DM pins.  $I_I$  is equal to the current on the S\_R and S\_L pins.  $I_O$  is equal to the current on the DP and DMpins

(2) Audio Switch is intended for signals to be asserted on S\_R/S\_L pins and pass to DM/DP

# MIC SWITCH ELECTRICAL CHARACTERISTICS<sup>(1)</sup>

$V_{BAT}$  = 3.0 V to 4.4 V,  $V_{DDIO}$  = 2.8 V,  $T_A$  = -40°C to 85°C, Typical values are at  $T_A$  = 25°C (unless otherwise noted)

|                                         | PARAMETER                                            |                          | TEST CONDITIONS                                                                                                                                                                   | MIN | TYP  | MAX       | UNIT |

|-----------------------------------------|------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----------|------|

| ANALOG SW                               | ІТСН                                                 |                          |                                                                                                                                                                                   |     |      |           |      |

| V <sub>MICIO</sub>                      | Analog signal range                                  |                          |                                                                                                                                                                                   | 0   |      | $V_{BAT}$ | V    |

| r <sub>ON</sub>                         | ON-state resistance                                  | MIC, VBUS                | $V_{I} = 2.3 \text{ V}, I_{O} = -20 \text{ mA}, V_{BAT} = 3.0 \text{ V}$                                                                                                          |     | 40   | 52        | Ω    |

|                                         |                                                      | MIC, DP                  | $V_{I} = 2.3 \text{ V}, I_{I} = -5 \text{ mA}, V_{BAT} = 3.0 \text{ V}$                                                                                                           |     | 15   | 25        | Ω    |

| I <sub>IO(OFF)</sub>                    | V <sub>I</sub> or V <sub>O</sub> OFF leakage current |                          |                                                                                                                                                                                   |     | 5    | 500       | nA   |

| DYNAMIC                                 |                                                      |                          |                                                                                                                                                                                   |     |      |           |      |

| t <sub>ON</sub>                         | Turn-ON time                                         | From receipt of          | $V_{I}$ or $V_{O} = V_{BAT}$ , $R_{L} = 100 \Omega$ , $C_{L} = 35 \text{ pF}$                                                                                                     |     | 260  |           | μs   |

| t <sub>OFF</sub>                        | Turn-OFF time                                        | I <sup>2</sup> C ACK bit |                                                                                                                                                                                   |     | 180  |           |      |

| C <sub>I(OFF)</sub>                     | VI OFF capacitance                                   |                          | DC bias = 0 V or 3.6 V, f = 10 MHz, Switch OFF                                                                                                                                    |     | 130  |           | pF   |

| C <sub>O(OFF)</sub>                     | VO OFF capacitance                                   |                          |                                                                                                                                                                                   |     | 10.5 |           | pF   |

| C <sub>I(ON)</sub> , C <sub>O(ON)</sub> | VI, VO ON capacitance                                | Э                        | DC bias = 0 V or 3.6 V f = 10 MHz, Switch ON                                                                                                                                      |     | 140  |           | pF   |

| BW                                      | Bandwidth, MIC to VB                                 | US                       | $R_L = 50 \Omega$ , Switch ON                                                                                                                                                     |     | 40   |           | MHz  |

|                                         | Bandwidth, MIC to DP                                 |                          | $R_L = 50 \Omega$ , Switch ON                                                                                                                                                     |     | 250  |           |      |

| O <sub>ISO</sub>                        | OFF Isolation                                        |                          | f = 20 kHz, $R_L$ = 50 $\Omega$ , Switch OFF                                                                                                                                      |     | -95  |           | dB   |

| X <sub>TALK</sub>                       | Crosstalk                                            |                          | f = 20 kHz, $R_L = 50 \Omega$ , to audio output                                                                                                                                   |     | -85  |           | dB   |

| THD                                     | Total harmonic distortion                            | on                       | $\label{eq:RL} \begin{array}{l} {\sf R}_L = 600 \ \Omega, \ C_L = 20 \ p{\sf F}, \ f = 20 \ Hz{-}20 \ Hz \ , \\ {\sf V}_{in} = 0.1 \ Vpp \ centered \ at \ V_{BAT}/2 \end{array}$ |     | 0.05 | 0.65      | %    |

(1)  $V_I$  is equal to the asserted voltage on VBUS/DP pin.  $V_O$  is equal to the asserted voltage on MIC pin.  $I_I$  is equal to the current on the VBUS/DP pin.  $I_O$  is equal to the current on the MIC pin.

TSU6721YFF

SCDS345-JUNE 2013

www.ti.com

STRUMENTS

EXAS

# **USB & UART SWITCH ELECTRICAL CHARACTERISTICS**

$V_{BAT}$  = 3 V to 4.4 V,  $V_{DDIO}$  = 2.8 V,  $T_A$  = -40°C to 85°C, Typical values are at  $T_A$  = 25°C (unless otherwise noted)

|                                         | PARAMETER                                  |                                   | TEST CONDITIONS                                                                                      | MIN | TYP | MAX  | UNIT |

|-----------------------------------------|--------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| ANALOG SW                               | ІТСН                                       |                                   |                                                                                                      |     |     |      |      |

| V <sub>USBIO</sub>                      | Analog signal range                        |                                   |                                                                                                      | 0   |     | 3.6  | V    |

| VUARTIO                                 | Analog signal range                        |                                   |                                                                                                      | 0   |     | 2.7  |      |

| r <sub>ON</sub>                         | ON-state resistance                        | DM_HT,DM<br>DP_HT,DP              | $V_{I} = 0$ V to 3.6 V, $I_{O} = -20$ mA, $V_{BAT} = 3.0$ V                                          |     | 6   | 11   | Ω    |

|                                         |                                            | TxD, DM<br>RxD, DP                | $V_{\rm I}$ = 0 V to 3.6 V, $I_{\rm O}$ = –20 mA, $V_{\rm BAT}$ = 3.0 V                              |     | 7   | 14.3 |      |

| r <sub>ON</sub>                         | ON-state resistance                        | ID, IDBP                          | $V_{\rm I}$ = 0 V to 3.6 V, $I_{\rm O}$ = –20 mA, $V_{\rm BAT}$ = 3.0 V                              |     | 30  |      | Ω    |

| Δr <sub>ON</sub>                        | ON-state resistance match between channels | DM_HT,DM<br>DP_HT,DP              | $V_{I} = 0.4 \text{ V}, I_{O} = -20 \text{ mA}, V_{BAT} = 3.0 \text{ V}$                             |     | 0.2 | 1    | Ω    |

|                                         |                                            | TxD, DM<br>RxD, DP                | $V_{I} = 0.4 \text{ V}, I_{O} = -20 \text{ mA}, V_{BAT} = 3.0 \text{ V}$                             |     | 1.5 | 3    |      |

| r <sub>ON(flat)</sub>                   | ON-state resistance flatness               | DM_HT, DP_HT,<br>TxD, RxD, DM, DP | $V_I = 0 V$ to 3.6 V, $I_O = -20 mA$ ,<br>$V_{BAT} = 3.0 V$                                          |     | 1.4 | 3.2  | Ω    |

| I <sub>IO(OFF)</sub>                    | VI or VO OFF leakage<br>current            | DM_HT, DP_HT,<br>TxD, RxD, DM, DP | $V_{I} = 0.3 V, V_{O} = 2.7 V \text{ or } V_{I} = 2.7 V, V_{O} = 0.3 V, V_{BAT} = 4.4 V, Switch OFF$ |     | 45  | 200  | nA   |

| I <sub>IO(ON)</sub>                     | VO ON leakage current                      | DM_HT, DP_HT,<br>TxD, RxD, DM, DP | $V_I = OPEN, V_O = 0.3 V \text{ or } 2.7 V,$<br>$V_{BAT} = 4.4 V, Switch ON$                         |     | 50  | 200  | nA   |

| DYNAMIC                                 |                                            |                                   |                                                                                                      | 1   |     |      |      |

| t <sub>ON</sub>                         | Turn-ON time                               | From receipt of I <sup>2</sup> C  | $V_{I}$ or $V_{O} = V_{BAT}$ , $R_{L} = 100 \Omega$ , $C_{L} = 35 pF$                                |     | 130 |      | μs   |

| t <sub>OFF</sub>                        | Turn-OFF time                              | ACK bit                           |                                                                                                      |     | 100 |      |      |

| C <sub>I(OFF)</sub>                     | VI OFF capacitance                         |                                   | DC bias = 0 V or 1.6 V, f = 10 MHz,                                                                  |     | 4   |      | pF   |

| C <sub>O(OFF)</sub>                     | VO OFF capacitance                         |                                   | Switch OFF                                                                                           |     | 7   |      | pF   |

| C <sub>I(ON)</sub> , C <sub>O(ON)</sub> | VI, VO ON capacitance                      |                                   | DC bias = 0 V or 3.6 V f = 10 MHz,<br>Switch ON                                                      |     | 9   |      | pF   |

| BW                                      | Bandwidth                                  |                                   | $R_L = 50 \Omega$ , Switch ON                                                                        |     | 510 |      | MHz  |

| O <sub>ISO</sub>                        | OFF Isolation                              |                                   | f = 240 kHz, $R_L$ = 50 $\Omega$ , Switch OFF                                                        |     | -26 |      | dB   |

| X <sub>TALK</sub>                       | Crosstalk                                  |                                   | f = 240 kHz, $R_{L}$ = 50 Ω                                                                          |     | -32 |      | dB   |

#### **GENERAL OPERATION**

The TSU6721 is a multimedia switch that connects a common USB connector to USB, UART or audio signals. The device also has a MIC switch that connects to either VBUS or DP. It has an integrated load switch to support charging. The load switch has OverVoltage Protection as well as OverCurrent Limiting Protection. In addition, the TSU6721 also has an ID bypass switch to transmit ID signal from the connector to the host. It has an internal FET switch that disconnects the coupling capacitor connected to the VBUS line.

#### Standby Mode

Standby mode is the default mode upon power up and occurs when no accessory has been detected. During this mode, the VBUS and ID lines are continually monitored through comparators to determine when an accessory is inserted. Power consumption is minimal during standby mode.

#### Load Switch

The integrated load switch provides both overvoltage/undervoltage and overcurrent limiting protection:

#### **Overvoltage Protection**

When the input voltage rises above VOVP, the internal load switch is turned off. The response is very rapid, with the FET turning off in less than 1µs tOFF(OVP). The OVP\_EN interrupt bit is set high when an overvoltage condition is detected. When the input voltage returns below VOVP-VHYS\_OVP and remains above VUVLO, the VBUS switch is turned on again after a deglitch time of tON(OVP). This deglitch time ensures that the input supply has stabilized before turning the switch on. When the OVP condition is cleared, the OVP\_OCP\_DIS interrupt bit is set high.

#### Undervoltage Protection

When VBUS is not present and VBAT is less than 2.5V, VBAT and VBUS voltages are below the undervoltage threshold and TSU6721 is powered off.

#### **Overcurrent Limiting Protection**

The TSU6721 also provides overcurrent limiting protection. When current increases beyond the  $I_{OCP}$  threshold, a time-out delay is initiated. After the delay has expired, and the current is still greater than  $I_{OCP}$ , then load switch is disabled. The maximum current that flows through the load switch is controlled by the  $I_{OCL}$  limit. This feature provides control on the VBUS charging current and minimizes the chance of internal circuitry damage caused by overcurrent event. The overcurrent level can be programmed through I2C.

#### **Power Supervisor**

TSU6721 uses VBAT as the primary supply voltage. VBUS is the secondary supply. VDDIO is used for I2C communication.

|      |      |       |           |                  | •           |                                                   |  |  |  |  |  |

|------|------|-------|-----------|------------------|-------------|---------------------------------------------------|--|--|--|--|--|

| VBAT | VBUS | VDDIO | DETECTION | LOAD SWITCH      | I2C         | COMMENTS                                          |  |  |  |  |  |

| Yes  | No   | No    | Enabled   | Not Enabled      | Not Enabled | VBAT is supply                                    |  |  |  |  |  |

| Yes  | Yes  | No    | Enabled   | Enabled          | Not enabled | VBAT is supply. LOAD SWITCH controlled by<br>VBUS |  |  |  |  |  |

| Yes  | No   | Yes   | Enabled   | Not Enabled      | Enabled     | VBAT is supply                                    |  |  |  |  |  |

| Yes  | Yes  | Yes   | Enabled   | Enabled          | Enabled     | VBAT is supply. LOAD SWITCH controlled by<br>VBUS |  |  |  |  |  |

| No   | Yes  | No    | Enabled   | Enabled          | Not Enabled | VBUS is supply. LOAD SWITCH controlled by<br>VBUS |  |  |  |  |  |

| No   | Yes  | Yes   |           |                  | Not vali    | d                                                 |  |  |  |  |  |

| No   | No   | Yes   |           | Not valid        |             |                                                   |  |  |  |  |  |

| No   | No   | No    |           | Power Down Reset |             |                                                   |  |  |  |  |  |

#### Table 1. Supply Voltage States

#### ACCESSORY ID DETECTION

If VBUS is high and the attachment is a non-compliant charger (see Table 5), the impedance on the ID pin is then determined. If VBUS is low and an accessory is attached, then an ADC for impedance sensing is used on the ID pin to identify which accessory is attached and/or what kind of remote control key button is pushed.

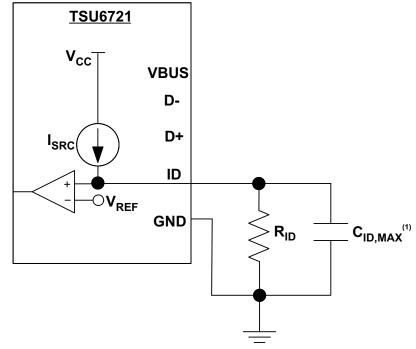

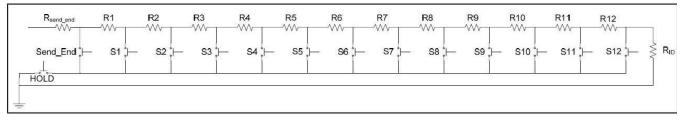

The TSU6721 features impedance detection for identification of various accessories that might be attached to the micro-USB port. Each accessory is identified by a unique resistor value connected between the ID pin and Ground. During impedance detection a current source is applied to the ID pin. The current source is then applied to the ID pin while an internal voltage reference is incremented till it matches the ID pin voltage. This produces a 5-bit ADC value that corresponds to the ID resistance found. Once an ID resistance is identified, a current source is continuously applied to determine when the resistance is detached.

(1) Maximum ID\_Cap capacitance as noted in RECOMMENDED OPERATING CONDITIONS

Figure 1. Impedance Detection Circuitry

#### Impedance Buckets for Each Accessory and Remote Control Key Button

In order to implement ID detection, each accessory and remote control key button of audio accessory should contain below ID impedance resistor value which is 1% tolerance accuracy.

#### Switch Matrix

MCPC accessory table is selected only when MCPC mode is enabled in Control Reg02h. VBUS to OUT Load Switch is enabled anytime VBUS is applied to the USB connector.

# TSU6721YFF

SCDS345-JUNE 2013

|                                 |          | _          |              |     | SI    | NITCH STA | TE   |       | ST   | ATUS OUT | PUT  |

|---------------------------------|----------|------------|--------------|-----|-------|-----------|------|-------|------|----------|------|

| ACCESSORY                       | ID       | Res<br>(%) | ADC<br>Value |     | DP/DM |           | VBUS | ID    |      |          | DOOT |

|                                 |          | (70)       | value        | USB | UART  | Audio     | MIC  | ID_HT | ISET | JIG      | BOOT |

| OTG                             | 0        | -          | 00000        | ON  | OFF   | OFF       | OFF  | ON    | OFF  | OFF      | OFF  |

| Video                           | 75       | 5%         | 00000        | OFF | OFF   | ON        | OFF  | OFF   | OFF  | OFF      | OFF  |

| MHL                             | 1K       | 5%         | 00000        | OFF | OFF   | OFF       | OFF  | OFF   | OFF  | OFF      | OFF  |

| Send End Button                 | 2K       | 10%        | 00001        | OFF | OFF   | ON        | ON   | OFF   | OFF  | OFF      | OFF  |

| Stereo Headset RC S1<br>Button  | 2.604K   | 5%         | 00010        | OFF | OFF   | ON        | ON   | OFF   | OFF  | OFF      | OFF  |

| Stereo Headset RC S2<br>Button  | 3.208K   | 5%         | 00011        | OFF | OFF   | ON        | ON   | OFF   | OFF  | OFF      | OFF  |

| Stereo Headset RC S3<br>Button  | 4.014K   | 5%         | 00100        | OFF | OFF   | ON        | ON   | OFF   | OFF  | OFF      | OFF  |

| Stereo Headset RC S4<br>Button  | 4.82K    | 5%         | 00101        | OFF | OFF   | ON        | ON   | OFF   | OFF  | OFF      | OFF  |

| Stereo Headset RC S5<br>Button  | 6.03K    | 5%         | 00110        | OFF | OFF   | ON        | ON   | OFF   | OFF  | OFF      | OFF  |

| Stereo Headset RC S6<br>Button  | 8.03K    | 5%         | 00111        | OFF | OFF   | ON        | ON   | OFF   | OFF  | OFF      | OFF  |

| Stereo Headset RC S7<br>Button  | 10.03K   | 5%         | 01000        | OFF | OFF   | ON        | ON   | OFF   | OFF  | OFF      | OFF  |

| Stereo Headset RC S8<br>Button  | 12.03K   | 5%         | 01001        | OFF | OFF   | ON        | ON   | OFF   | OFF  | OFF      | OFF  |

| Stereo Headset RC S9<br>Button  | 14.46K   | 5%         | 01010        | OFF | OFF   | ON        | ON   | OFF   | OFF  | OFF      | OFF  |

| Stereo Headset RC S10<br>Button | 17.26K   | 5%         | 01011        | OFF | OFF   | ON        | ON   | OFF   | OFF  | OFF      | OFF  |

| Stereo Headset RC S11<br>Button | 20.5K    | 5%         | 01100        | OFF | OFF   | ON        | ON   | OFF   | OFF  | OFF      | OFF  |

| Stereo Headset RC S12<br>Button | 24.07K   | 5%         | 01101        | OFF | OFF   | ON        | ON   | OFF   | OFF  | OFF      | OFF  |

| Audio Device Type 3             | 28.7K    | 5%         | 01110        | OFF | OFF   | ON        | OFF  | OFF   | OFF  | OFF      | OFF  |

| Reserved Accessory #1           | 34K      | 5%         | 01111        | OFF | OFF   | ON        | ON   | OFF   | OFF  | OFF      | OFF  |

| Reserved Accessory #2           | 40.2K    | 5%         | 10000        | OFF | OFF   | ON        | ON   | OFF   | OFF  | OFF      | OFF  |

| Reserved Accessory #3           | 49.9K    | 5%         | 10001        | OFF | OFF   | ON        | ON   | OFF   | OFF  | OFF      | OFF  |

| Reserved Accessory #4           | 64.9K    | 5%         | 10010        | OFF | OFF   | ON        | ON   | OFF   | OFF  | OFF      | OFF  |

| Audio Device Type 2             | 80.27K   | 5%         | 10011        | OFF | OFF   | ON        | OFF  | OFF   | OFF  | OFF      | OFF  |

| Phone Powered Device            | 102K     | 5%         | 10100        | OFF | ON    | OFF       | OFF  | OFF   | OFF  | OFF      | OFF  |

| TTY Converter                   | 121K     | 5%         | 10101        | OFF | OFF   | ON        | ON   | OFF   | OFF  | OFF      | OFF  |

| UART Cable                      | 150K     | 5%         | 10110        | OFF | ON    | OFF       | OFF  | OFF   | OFF  | OFF      | OFF  |

| Type 1 Charger                  | 200K     | 5%         | 10111        | ON  | OFF   | OFF       | OFF  | OFF   | ON   | OFF      | OFF  |

| Factory Mode - Boot Off USB     | 255K     | 5%         | 11000        | ON  | OFF   | OFF       | OFF  | OFF   | OFF  | ON       | OFF  |

| Factory Mode - Boot On USB      | 301K     | 5%         | 11001        | ON  | OFF   | OFF       | OFF  | OFF   | OFF  | ON       | ON   |

| Audio/Video Cable               | 365K     | 5%         | 11010        | OFF | OFF   | ON        | OFF  | OFF   | OFF  | OFF      | OFF  |

| A/V + VBUS                      | 365K     | 5%         | 11010        | OFF | OFF   | ON        | OFF  | OFF   | OFF  | OFF      | OFF  |

| Type 2 Charger                  | 442K     | 5%         | 11011        | ON  | OFF   | OFF       | OFF  | OFF   | ON   | OFF      | OFF  |

| Factory Mode - Boot Off<br>UART | 523K     | 5%         | 11100        | OFF | ON    | OFF       | OFF  | OFF   | OFF  | ON       | OFF  |

| Factory Mode - Boot On<br>UART  | 619K     | 5%         | 11101        | OFF | ON    | OFF       | OFF  | OFF   | OFF  | ON       | ON   |

| Sterero Audio Device Type 1     | 1000.07K | 10%        | 11110        | OFF | OFF   | ON        | ON   | OFF   | OFF  | OFF      | OFF  |

| Mono Audio Device Type 1        | 1002K    | 10%        | 11110        | OFF | OFF   | ON        | ON   | OFF   | OFF  | OFF      | OFF  |

|                           |            |         |       |                      | SWITCH                | STATE     |      |       | STA  | TUS OUT | IPUT |

|---------------------------|------------|---------|-------|----------------------|-----------------------|-----------|------|-------|------|---------|------|

| ACCESSORY                 | ID         | RES (%) | ADC   | DP                   | /DM                   |           | VBUS | ID    |      |         |      |

|                           | 10         |         | VALUE | USB                  | UART                  | AUDI<br>O | МІС  | ID_HT | ISET | JIG     | воот |

| Sand End SW               | 47K        | 5%      | 10000 | OFF                  | OFF                   | ON        | ON   | OFF   | OFF  | OFF     | OFF  |

| Send_End_SW               | 4/1        | 5%      | 10001 | OFF                  | OFF                   | UN        | UN   | OFF   | OFF  | UFF     | UFF  |

| Send End SW with VBUS     | 47K        | 5%      | 10000 | OFF                  | OFF                   | ON        | OFF  | OFF   | OFF  | OFF     | OFF  |

| Send_End_Svv with VBUS    | 4/1        | 5%      | 10001 | OFF                  | OFF                   | UN        | UFF  | OFF   | OFF  | UFF     | UFF  |

| Maintanence               | 180K       | 5%      | 10110 |                      |                       | OFF       | OFF  | OFF   | OFF  | OFF     | OFF  |

| Maintanence               | TOUR       | 5%      | 10111 | OFF                  | OFF OFF               |           | OFF  | OFF   | OFF  | OFF     | UFF  |

| Mode 1 Stereo             | 47K + 240K | 5%      | 11000 | OFF                  | OFF                   | ON        | ON   | OFF   | OFF  | OFF     | OFF  |

| Mode I Stereo             | 47K + 240K | 5%      | 11001 | OFF                  | OFF                   |           |      |       |      |         |      |

| Mode 1 Stereo with VBUS   | 47K + 240K | 5%      | 11000 | OFF                  | OFF                   | ON        | OFF  | OFF   | OFF  | OFF     | OFF  |

| Mode I Stereo with VBUS   | 47K + 240K | 5%      | 11001 | OFF                  | OFF                   |           |      |       |      |         |      |

| Reserved                  | 390K       | 5%      | 11010 | OFF                  | OFF                   | OFF       | OFF  | OFF   | OFF  | OFF     | OFF  |

| Reserved                  | 390K       | 5%      | 11011 | OFF                  | OFF                   |           |      |       |      |         |      |

| Mode 3 Monaural           | 47K + 510K | 5%      | 11100 | DM to S I            |                       | c         | OFF  | OFF   | OFF  | OFF     | OFF  |

|                           | 47K + 510K | 5%      | 11101 | DIVI IO 3_L          | DM to S_L; DP to MIC  |           |      |       |      |         |      |

| Mode 3 Monaural with VBUS | 47K + 510K | 5%      | 11100 | DM to S I            | DM to S. L. DR to MIC |           | OFF  | OFF   | OFF  | OFF     | OFF  |

|                           | 4/K + 310K | 5%      | 11101 | DM to S_L; DP to MIC |                       |           |      |       |      |         |      |

| Mode 2 Monaural           | 47K + 750K | 5%      | 11110 | DM to S_L            | DM to S_L; DP OPEN    |           |      | OFF   | OFF  | OFF     | OFF  |

| Mode 2 Monaural with VBUS | 47K + 750K | 5%      | 11110 | DM to S_L            | DM to S_L; DP OPEN    |           |      | OFF   | OFF  | OFF     | OFF  |

# Table 3. Accessory ID and Switch States MCPC Mode

www.ti.com

Copyright © 2013, Texas Instruments Incorporated

#### **CHARGER DETECTION**

|                                 |    |         |              |     | SI    | NITCH STA | ST   | ATUS OUTF | PUT  |     |      |

|---------------------------------|----|---------|--------------|-----|-------|-----------|------|-----------|------|-----|------|

| ACCESSORY                       | ID | RES (%) | ADC<br>VALUE |     | DP/DM |           | VBUS | ID        | IOFT | "0  | DOOT |

|                                 |    |         | TALUL        | USB | UART  | AUDIO     | MIC  | ID_HT     | ISET | JIG | BOOT |

| No ID                           | -  | -       | 11111        | OFF | OFF   | OFF       | OFF  | OFF       | OFF  | OFF | OFF  |

| Apple Charger                   | _  | -       | 11111        | OFF | OFF   | OFF       | OFF  | OFF       | OFF  | OFF | OFF  |

| Non-standard Charger            | -  | -       | 11111        | OFF | OFF   | OFF       | OFF  | OFF       | OFF  | OFF | OFF  |

| USB Standard Downstream<br>Port | -  | -       | 11111        | ON  | OFF   | OFF       | OFF  | ON        | OFF  | OFF | OFF  |

| USB Charging Downstream<br>Port | -  | -       | 11111        | ON  | OFF   | OFF       | OFF  | ON        | ON   | OFF | OFF  |

| Dedicated Charging Port         | -  | -       | 11111        | ON  | OFF   | OFF       | OFF  | ON        | ON   | OFF | OFF  |

#### Table 4. Chargers Detected and Switch States

Table 5 lists the configurations of the DP\_CON (D+) and DM\_CON (D-) that are internal to the various device types.

| DEVICE TYPE                             | VBUS | DP_CON (D+)            | DM_CON (D–)            |

|-----------------------------------------|------|------------------------|------------------------|

| Standard Downstream Port                | >4 V | Pull-down R 15k to GND | Pull-down R 15k        |

| Charging Downstream Port                | >4 V | Pull-down R 15k to GND | $V_{DM\_SRC}$ =0.6V    |

| Dedicated Charging Port                 | >4 V | Short to D-            | Short to D+            |

| Apple Charger                           | >4 V | $2.0 < V_{DP} < 2.8$   | $2.0 < V_{DM} < 2.8$   |

| U200                                    | >4 V | V <sub>DP</sub> = 1.34 | V <sub>DM</sub> = 1.34 |

| Non-compliant USB Charger Any<br>Device | >4 V | Open                   | Open                   |

#### Table 5. Charger Detection Table

#### Power-On Reset

When power (from 0 V) is applied to  $V_{BAT}$ , an internal power-on reset holds the TSU6721 in a reset condition until  $V_{BAT}$  has reached  $V_{POR}$ . At that point, the reset condition is released, and the TSU6721 registers and I<sup>2</sup>C state machine initialize to their default states.

After the initial power-up phase,  $V_{BAT}$  must be lowered to below 0.2 V and then back up to the operating voltage ( $V_{DDIO}$ ) for a power-reset cycle.

#### Software Reset

The TSU6721 has software a reset feature. Set the reset bit in the I2C register high to reset TSU6721. After resetting, INTB will keep low until INT\_Mask bit of Control register (0x02) is cleared.

TSU6721YFF

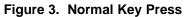

SCDS345-JUNE 2013 www.ti.com **Key Press Identification** Key Key Press Timing Long Key Press Timing INTB **Key Press** Interrupt Long Key Press Interrupt Long Key Release Interrupt (Ċ) (A) (B) A. Key press Released key press  $\rightarrow$  Set KP Interrupt  $\rightarrow$  Set error bit in Button register  $\rightarrow$  INTB pulled low Β. C. I<sup>2</sup>C read of INT register  $\rightarrow$  Clear KP interrupt  $\rightarrow$  INTB goes back high Figure 2. Short Key Press Key Key Press Timing Long Key Press Timing INTB

A. Key press

**Release Interrupt**

Key Press Interrupt

Long Key Press Interrupt

Long Key

B. Released key press  $\rightarrow$  Set KP Interrupt  $\rightarrow$  Set Key (S/E, 1–12) bit in Button register  $\rightarrow$  INTB pulled low .

C. I<sup>2</sup>C read of INT register  $\rightarrow$  Clear KP interrupt  $\rightarrow$  INTB goes back high.

(A)

(B)

(C)

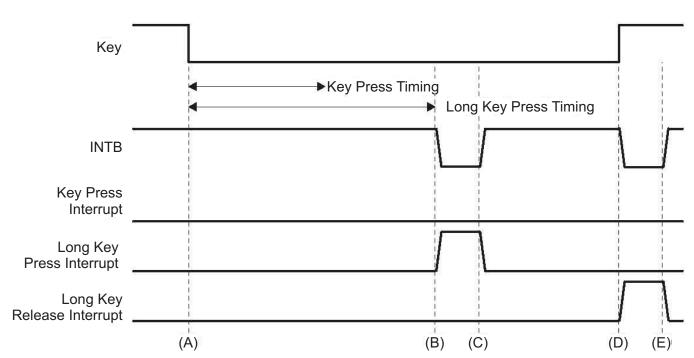

A. Key press

B. Long key press timing reached  $\rightarrow$  Set LKP interrupt bit  $\rightarrow$  Set Key (S/E, 1–12) bit in Button register  $\rightarrow$  INTB pulled low

C. I2C read of INT register  $\rightarrow$  Clear LKP interrupt bit  $\rightarrow$  INTB goes back high

D. Released key press  $\rightarrow$  Set LKR Interrupt bit  $\rightarrow$  INTB pulled low

E. I<sup>2</sup>C read of INT register  $\rightarrow$  Clear LKR interrupt bit  $\rightarrow$  INTB goes back high

#### Figure 4. Long Key Press

A. Key press detected when accessory attached

B. Long key press timing reached  $\rightarrow$  Set SK interrupt bit  $\rightarrow$  Set Key (S/E, 1–12) bit in Button register  $\rightarrow$  INTB pulled low

C. I<sup>2</sup>C read of INT register  $\rightarrow$  Clear SK interrupt bit  $\rightarrow$  INTB goes back high

D. Released key press detected when accessory ID resistor is 1  $M\Omega \rightarrow$  Set SKR Interrupt bit  $\rightarrow$  INTB pulled low

E. I<sup>2</sup>C read of INT register  $\rightarrow$  Clear SKR interrupt bit  $\rightarrow$  INTB goes back high

Figure 5. Stuck Key Press

Figure 6. Audio/Remote Controller Accessory

#### STANDARD I2C INTERFACE DETAILS

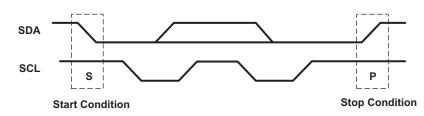

The bidirectional  $I^2C$  bus consists of the serial clock (SCL) and serial data (SDA) lines. Both lines must be connected to a positive supply via a pull-up resistor when connected to the output stages of a device. Data transfer may be initiated only when the bus is not busy.

I<sup>2</sup>C communication with this device is initiated by the master sending a START condition, a high-to-low transition on the SDA input/output while the SCL input is high (see Figure 7). After the start condition, the device address byte is sent, MSB first, including the data direction bit (R/W). This device does not respond to the general call address. After receiving the valid address byte, this device responds with an ACK, a low on the SDA input/output during the high of the ACK-related clock pulse.

Figure 7. Definition of Start and Stop Conditions

The data byte follows the address ACK. The R/W bit is kept low for transfer from the master to the slave. The data byte is followed by an ACK sent from this device. Data are output only if complete bytes are received and acknowledged. The output data is valid at time (tpv) after the low-to-high transition of SCL, during the clock cycle for the ACK.

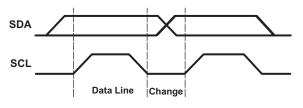

On the I<sup>2</sup>C bus, only one data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the high pulse of the clock period, as changes in the data line at this time are interpreted as control commands (START or STOP) (see Figure 8).

Figure 8. Bit Transfer

A Stop condition, a low-to-high transition on the SDA input/output while the SCL input is high, is sent by the master (see Figure 7).

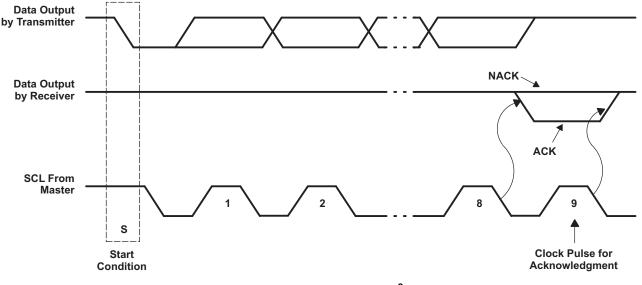

The number of data bytes transferred between the start and the stop conditions from transmitter to receiver is not limited. Each byte of eight bits is followed by one ACK bit. The transmitter must release the SDA line before the receiver can send an ACK bit.

A slave receiver that is addressed must generate an ACK after the reception of each byte. The device that acknowledges has to pull down the SDA line during the ACK clock pulse so that the SDA line is stable low during the high pulse of the ACK-related clock period (see Figure 9). Setup and hold times must be taken into account.

# TSU6721YFF

SCDS345-JUNE 2013

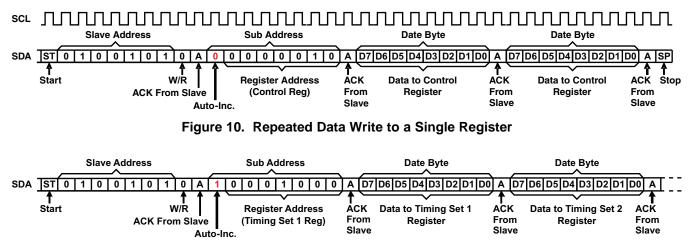

#### Writes

Data is transmitted to the TSU6721 by sending the device slave address and setting the LSB to a logic 0 (see Figure 10 for device address). The command byte is sent after the address and determines which register receives the data that follows the command byte. The next byte is written to the specified register on the rising edge of the ACK clock pulse.

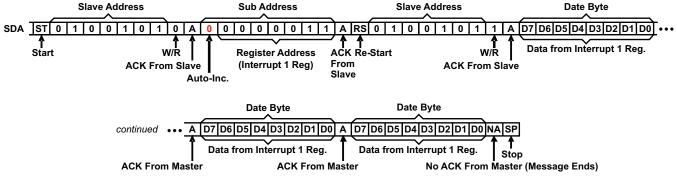

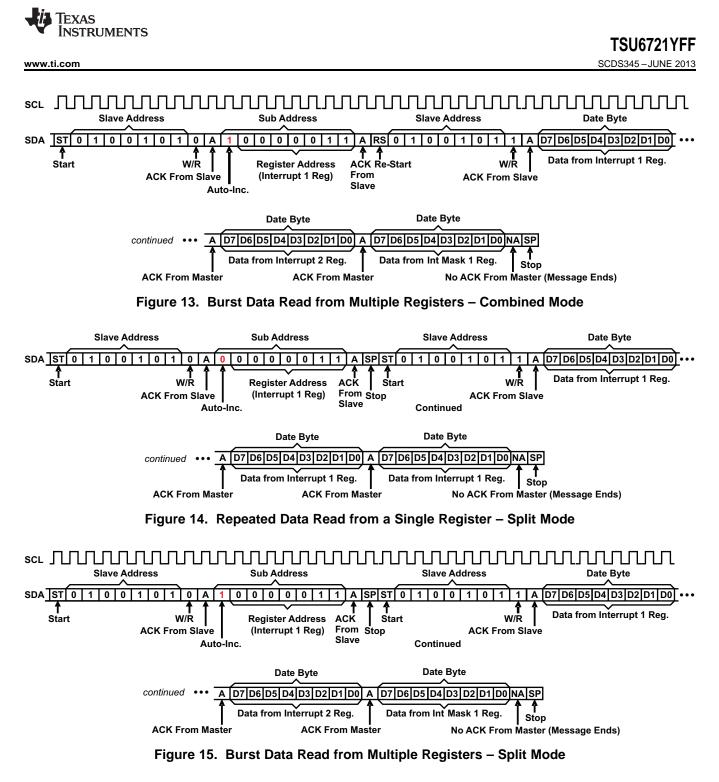

#### Reads

The bus master first must send the TSU6721 slave address with the LSB set to logic 0. The command byte is sent after the address and determines which register is accessed. After a restart, the device slave address is sent again but, this time, the LSB is set to logic 1. Data from the register defined by the command byte then is sent by the TSU6721. Data is clocked into the SDA output shift register on the rising edge of the ACK clock pulse. See Figure 12.

Figure 12. Repeated Data Read from a Single Register – Combined Mode

#### Notes (Applicable to Figure 10 – Figure 15):

- SDA is pulled low on Ack. from slave or Ack. from master.

- Register writes always require sub-address write before first data byte.

- Repeated data writes to a single register continue indefinitely until Stop or Re-Start.

- Repeated data reads from a single register continue indefinitely until No Ack. from master.

- Burst data writes start at the specified register address, then advance to the next register address, even to the read-only registers. For these registers, data write appears to occur, though no data are changed by the writes. After register 14h is written, writing resumes to register 01h and continues until Stop or Re-Start.

- Burst data reads start at the specified register address, then advance to the next register address. Once register 14h is read, reading resumes from register 01h and continues until No Ack. from master.

# I<sup>2</sup>C REGISTER MAP

| ADDRESS | REGISTER             | TYPE | RESET<br>VALUE | BIT 7               | BIT 6                                                  | BIT 5      | BIT4                    | BIT 3                  | BIT 2                 | BIT1                         | BITO        |  |

|---------|----------------------|------|----------------|---------------------|--------------------------------------------------------|------------|-------------------------|------------------------|-----------------------|------------------------------|-------------|--|

| 01h     | Device ID            | R    | 00010010       |                     |                                                        | Version ID |                         |                        |                       | Vendor ID                    |             |  |

| 02h     | Control              | R/W  | xx011111       |                     |                                                        | MCPC Mode  | Switch Open             | Raw Data               | Manual S/W            | Wait                         | INT Mask    |  |

| 03h     | Interrupt 1          | R    | 00000000       | OVP_OCP_OTP<br>_DIS | OCP_EN                                                 | OVP_EN     | LKR                     | LKP                    | KP                    | Detach                       | Attach      |  |

| 04h     | Interrupt 2          | R    | 00000000       | VBUS                | OTP_EN                                                 | CONNECT    | Stuck_Key_<br>RCV       | Stuck_Key              | ADC_<br>Change        | Reserved_<br>Attach          | A/V_Change  |  |

| 05h     | Interrupt Mask 1     | R/W  | 00000000       | OVP_OCP_OTP<br>_DIS | OCP_EN                                                 | OVP_EN     | LKR                     | LKP                    | KP                    | Detach                       | Attach      |  |

| 06h     | Interrupt Mask 2     | R/W  | 00000000       | VBUS                | OTP_EN                                                 | CONNECT    | Stuck_Key_<br>RCV       | Stuck_Key              | ADC_<br>Change        | Reserved_<br>Attach          | A/V_Change  |  |

| 07h     | ADC                  | R    | xxx11111       |                     |                                                        |            |                         |                        | ADC Value             |                              |             |  |

| 08h     | Timing Set 1         | R/W  | 00000000       |                     | Key Pre                                                | ess        |                         |                        | Device                | e Sleep                      |             |  |

| 09h     | Timing Set 2         | R/W  | 00000000       |                     | Switching Wait                                         |            |                         |                        | Long Key Press        |                              |             |  |

| 0Ah     | Device Type 1        | R    | 00000000       | USB OTG             | DCP                                                    | CDP        | Type1/Type<br>2 Charger | UART                   | USB                   | Audio Type2                  | Audio Type1 |  |

| 0Bh     | Device Type 2        | R    | 00000000       | Audio Type3         | A/V                                                    | TTY        | PPD                     | JIG_UART<br>_OFF       | JIG_UART<br>_ON       | JIG_USB<br>_OFF              | JIG_USB_ON  |  |

| 0Ch     | Button 1             | R    | 00000000       | 7                   | 6                                                      | 5          | 4                       | 3                      | 2                     | 1                            | Send_End    |  |

| 0Dh     | Button 2             | R    | x0000000       |                     | Unknown                                                | Error      | 12                      | 11                     | 10                    | 9                            | 8           |  |

| 13h     | Manual S/W 1         | R/W  | 00000000       |                     | DM Switching                                           |            |                         | DP Switching           |                       | VBUS                         | Switching   |  |

| 14h     | Manual S/W 2         | R/W  | xxx00000       |                     |                                                        |            | ISET                    | BOOT                   | JIG                   | ID Sv                        | vitching    |  |

| 15h     | Device Type 3        | R    | 0000x000       | Video               | U200 Chg                                               | Apple Chg  | A/V VBUS                |                        | VBUS non-<br>standard | VBUS<br>Debounce             | MHL         |  |

| 1Bh     | Reset                | W    | xxxxxx0        |                     |                                                        |            |                         |                        |                       |                              | Reset       |  |

| 20h     | Timer Setting        | R/W  | 00010101       | ISET Enable<br>Time | Load Switch<br>Enable Time                             |            | BCDv1.2 Time            | 2 Timer ADC Start Time |                       |                              | ie          |  |

| 21h     | OCL/OCP<br>Setting 1 | R/W  | 001010x1       | OCL Pr              | OCL Protection Level Setting OCP Timeout Delay Setting |            |                         | BCDv1.2<br>Enable      |                       |                              |             |  |

| 22h     | OCL/OCP<br>Setting 2 | R/W  | xxx11001       |                     |                                                        |            | OC Enable               |                        | OCP                   | OCP Protection Level Setting |             |  |

| 23h     | Device Type 4        | R/W  | xxxxx111       |                     |                                                        |            |                         |                        | MC                    | PC ID Resistor               | Value       |  |

#### Notes:

- 1. Do not use blank register bits.

- 2. Write "0" to the blank register bits.

- 3. Values read from the blank register bits are not defined and invalid.

- 4. When reading I2C table after an interrupt first read register Interrupt 1 (03h) followed by Interrupt 2 (04h).

- 5. Interrupt 1 (03h) and Interrupt 2 (04h) should not be read when INT Mask = 0.

- 6. I2C should not be accessed within 5 ms of device power-up.

#### Slave Address

|               | SIZE   |                                           |   | DESCRIPTION |   |   |   |   |     |  |  |  |  |

|---------------|--------|-------------------------------------------|---|-------------|---|---|---|---|-----|--|--|--|--|

| NAME          | (BITS) | BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 |   |             |   |   |   |   |     |  |  |  |  |

| Slave address | 8      | 0                                         | 1 | 0           | 0 | 1 | 0 | 1 | R/W |  |  |  |  |

#### **Device ID**

Address: 01h Reset Value: 00010010 Type: Read

| BIT NO. | NAME       | SIZE<br>(BITS) | DESCRIPTION                                              |

|---------|------------|----------------|----------------------------------------------------------|

| 2-0     | Vendor ID  | 3              | A unique number for vendor<br>010b for Texas Instruments |

| 7-3     | Version ID | 5              | A unique number for chip version<br>00010b for TSU6721   |

## Control

Address: 02h Reset Value: xx011111 Type: Read/Write

| BIT NO. | NAME        | SIZE<br>(BITS) | DESCRIPTION                                                                                                            |

|---------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------|

| 0       | INT Mask    | 1              | 0: Unmask interrupt<br>1: Mask interrupt                                                                               |

| 1       | Wait        | 1              | 0: Wait until host re-sets this bit(WAIT bit) high<br>1: Wait until Switching timer is expired defined in Timing Set 2 |

| 2       | Manual S/W  | 1              | 0: Manual Switching<br>1: Automatic Switching                                                                          |

| 3       | RAW Data    | 1              | 0: Report the status changes on ID to Host<br>1: Don't report the status changes on ID                                 |

| 4       | Switch Open | 1              | 0: Open all Switches (Including load switch)<br>1: Automatic Switching by accessory status                             |

| 5       | MCPC Mode   | 1              | 0: Non-MCPC Mode<br>1: MCPC Mode                                                                                       |

| 7-6     | Unused      | 2              |                                                                                                                        |

# TSU6721YFF

SCDS345-JUNE 2013

## Interrupt 1

Address: 03h Reset Value: 0000000 Type: Read and Clear

| BIT NO. | NAME                | SIZE<br>(BITS) | DESCRIPTION                                                |

|---------|---------------------|----------------|------------------------------------------------------------|

| 0       | Attach              | 1              | 1: Accessory is attached                                   |

| 1       | Detach              | 1              | 1: Accessory is detached                                   |

| 2       | KP                  | 1              | 1: Key press                                               |

| 3       | LKP                 | 1              | 1: Long key press                                          |

| 4       | LKR                 | 1              | 1: Long key release                                        |

| 5       | OVP_EN              | 1              | 1: OVP enabled                                             |

| 6       | OCP_EN              | 1              | 1: OCP enabled                                             |

| 7       | OVP_OCP_OTP_DI<br>S | 1              | 1: OVP_OCP_OTP disabled (device is out of OVP, OCP or OTP) |

### Interrupt 2

Address: 04h Reset Value: 0000000 Type: Read and Clear

| BIT<br>NO. | NAME            | SIZE<br>(BITS) | DESCRIPTION                                                |

|------------|-----------------|----------------|------------------------------------------------------------|

| 0          | A/V_Change      | 1              | 1: Accessory Change is detected when A/V cable is attached |

| 1          | Reserved_Attach | 1              | 1: Reserved Device is attached                             |