# TSD5402-Q1 8W 高効率車載センサドライバアンプ、保護機能と I2C 診断機能 内蔵

## 1 特長

- 車載アプリケーション向けに AEC-Q100 認定済み 温度グレード 1:-40℃~125℃、T<sub>Δ</sub>

- モノラル BTL デジタル パワー アンプ

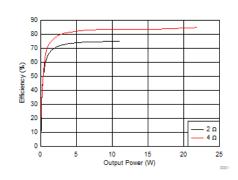

- 出力電力:8W (THD+N = 10%、4Ω 負荷時)

- 4.5V~18Vの動作範囲

- 効率:83% (4Ω 負荷時)

- 差動アナログ入力

- 電源ガード保護 (可変電圧リミッタ)

- 75dB 電源除去率 (PSRR)

- 負荷診断機能:

- 出力負荷の開放と短絡

- 出力と電源、出力とグランドの間の短絡

- 保護および監視機能

- 短絡保護

- ISO-7637-2 準拠の 40V 負荷ダンプ保護

- 出力 DC レベル検出

- 過熱保護

- 過電圧および低電圧保護

- PowerPAD™ (裏面露出パッド) で熱特性を強化した 16 ピン HTSSOP (PWP) パッケージ

- 車載用 EMC 要件に合わせて設計

- ISO9000:2002 TS16949 認定済み」

- スタンバイ時の負荷ダンプ保護:40V

- スタンバイ時も遮断されない I<sup>2</sup>C

## 2 アプリケーション

- リゾルバを使用した車載用および産業用アプリケーショ

- HEV/EV のインバータおよびモーター制御

- 電動パワー ステアリング (EPS)

- リアビュー ミラー モジュール

- 車載用電子ミラー

- サーボドライブの電力段モジュール

- 飛行制御システム

## 3 概要

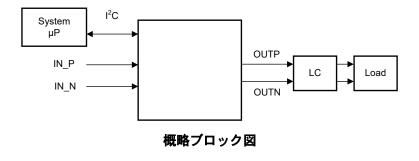

TSD5402-Q1 は Class-D センサ駆動アンプで、車載用 および産業用アプリケーションに理想的です。これらのア プリケーションは、リゾルバを使用したモーター制御、ブレ ーキ システム、電動パワー ステアリング、サーボ、フライト コントロール表面を含みますが、これらに限定されません。 広い動作電圧範囲と優れた効率を備えているため、この デバイスは設計において柔軟性が必要なアプリケーション に理想的です。負荷ダンプ保護が搭載されているため、 外付け電圧クランプのコストとサイズを減らすことができ、 オンボードの負荷診断機能により I<sup>2</sup>C 経由で負荷の状態 が報告されます。内蔵の短絡負荷と開放負荷診断機能に より、システムは外部実装を回避できます。

#### 製品情報

| 部品番号       | パッケージ (1)   | パッケージ サイズ <sup>(2)</sup> |

|------------|-------------|--------------------------|

| TSD5402-Q1 | HTSSOP (16) | 5.0mm × 6.4mm            |

- 利用可能なすべてのパッケージについては、データシートの末尾 にある注文情報を参照してください。

- (2) パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピ ンも含まれます。

出力電力効率

## **Table of Contents**

| 1 特長1                                               | 7.1 I <sup>2</sup> C Address Register Definitions | 18 |

|-----------------------------------------------------|---------------------------------------------------|----|

| 2 アプリケーション1                                         | 8 Application and Implementation                  | 20 |

| 3 概要1                                               | 8.1 Application Information                       | 20 |

| 4 Pin Configuration and Functions3                  | 8.2 Typical Application                           | 20 |

| 5 Specifications4                                   | 8.3 Power Supply Recommendations                  | 23 |

| 5.1 Absolute Maximum Ratings4                       | 8.4 Layout                                        |    |

| 5.2 ESD Ratings4                                    | 9 Device and Documentation Support                |    |

| 5.3 Recommended Operating Conditions4               | 9.1 Device Support                                |    |

| 5.4 Thermal Information5                            | 9.2 Documentation Support                         |    |

| 5.5 Electrical Characteristics5                     | 9.3ドキュメントの更新通知を受け取る方法                             | 28 |

| 5.6 Timing Requirements for I2C Interface Signals 7 | 9.4 サポート・リソース                                     | 28 |

| 5.7 Typical Characteristics8                        | 9.5 Trademarks                                    | 28 |

| 6 Detailed Description10                            | 9.6 静電気放電に関する注意事項                                 | 28 |

| 6.1 Overview10                                      | 9.7 用語集                                           | 28 |

| 6.2 Functional Block Diagram10                      | 10 Revision History                               | 28 |

| 6.3 Feature Description11                           | 11 Mechanical, Packaging, and Orderable           |    |

| 6.4 Device Functional Modes17                       | Information                                       | 29 |

| 7 Register Maps                                     | 11.1 Package Option Addendum                      | 30 |

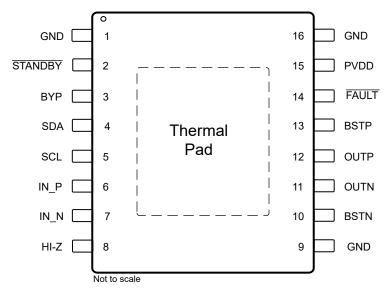

# **4 Pin Configuration and Functions**

図 4-1. PWP Package, 16-Pin, TSSOP With Exposed Thermal Pad (Top View)

表 4-1. Pin Functions

|             | NINI     |                     | 2x 4-1.1 iii i unctions                                                            |

|-------------|----------|---------------------|------------------------------------------------------------------------------------|

| Р           | IN       | TYPE <sup>(1)</sup> | DESCRIPTION                                                                        |

| NAME        | NO.      |                     |                                                                                    |

| BSTN        | 10       | Al                  | Bootstrap for negative-output high-side FET                                        |

| BSTP        | 13       | Al                  | Bootstrap for positive-output high-side FET                                        |

| BYP         | 3        | PBY                 | Voltage-regulator bypass-capacitor pin                                             |

| FAULT       | 14       | DO                  | Active-low open-drain output used to report faults                                 |

| GND         | 1, 9, 16 | GND                 | Ground                                                                             |

| IN_N        | 7        | Al                  | Inverting analog input                                                             |

| IN_P        | 6        | Al                  | Non-inverting analog input                                                         |

| HI-Z        | 8        | DI                  | Stops output switching in DRIVE mode, active-high (no internal pullup or pulldown) |

| OUTN        | 11       | PO                  | Output (–)                                                                         |

| OUTP        | 12       | PO                  | Output (+)                                                                         |

| PVDD        | 15       | PWR                 | Power supply                                                                       |

| SCL         | 5        | DI                  | I <sup>2</sup> C clock                                                             |

| SDA         | 4        | DI/DO               | I <sup>2</sup> C data                                                              |

| STANDBY     | 2        | DI                  | Active-low STANDBY pin (no internal pullup or pulldown)                            |

| Thermal pad | _        | _                   | Must be soldered to ground                                                         |

<sup>(1)</sup> DI = digital input, DO = digital output, AI = analog input, PWR = power supply, PBY = power bypass, PO = power output, GND = ground

## **5 Specifications**

## 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                 |                                                                  |                     | MIN  | MAX  | UNIT |

|-----------------|------------------------------------------------------------------|---------------------|------|------|------|

|                 | DC supply voltage range, V <sub>(PVDD)</sub>                     | Relative to GND     | -0.3 | 30   | V    |

|                 | Pulsed supply voltage range, V <sub>(PVDD_MAX)</sub>             | t ≤ 400 ms exposure | -1   | 40   | V    |

|                 | Supply voltage ramp rate, ΔV <sub>(PVDD_RAMP)</sub>              | <u> </u>            |      | 15   | V/ms |

|                 | For SCL, SDA, and STANDBY, FAULT pins                            | Relative to GND     | -0.3 | 5    |      |

| Input voltage   | For IN_N, IN_P, and HI-Z pins                                    | Relative to GND     | -0.3 | 6.5  |      |

|                 | BYP                                                              | Relative to GND     | -0.3 | 7    | V    |

|                 | BSTN, BSTP                                                       | Relative to BYP     | -0.3 | 30   | V    |

|                 | BSTN, BSTP                                                       | Relative to GND     | -0.3 | 36.3 |      |

|                 | OUTN, OUTP                                                       | Relative to GND     | -0.3 | 30   |      |

|                 | DC current on PVDD, GND and OUTx pins, I <sub>(PVD)</sub>        | o), lo              |      | ±4   | Α    |

| Current         | Maximum current, on all input pins, I <sub>(IN_MAX)</sub> (2)    |                     |      | ±1   | Л    |

|                 | Maximum sink current for open-drain pin, I <sub>(IN_ODMAX)</sub> |                     |      | 7    | mA   |

| Storage tempera | ture, T <sub>stg</sub>                                           |                     | -55  | 150  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 5.2 ESD Ratings

|        |                                            |                                                                                            | VALUE | UNIT |

|--------|--------------------------------------------|--------------------------------------------------------------------------------------------|-------|------|

| V      | V <sub>(ESD)</sub> Electrostatic discharge | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup><br>HBM ESD Classification Level H2 | ±3500 | V    |

| V(ESD) |                                            | Charged-device model (CDM), per AEC Q100-011<br>CDM ESD Classification Level C5            | ±1000 | V    |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## **5.3 Recommended Operating Conditions**

|                            |                                                          |                                                                | MIN  | NOM  | MAX                   | UNIT     |

|----------------------------|----------------------------------------------------------|----------------------------------------------------------------|------|------|-----------------------|----------|

| .,                         | Supply voltage range relative to GND.                    | 4-Ω ±20% load (or higher)                                      | 4.5  | 14.4 | 18                    | .,       |

| V <sub>(PVDD_OP)</sub>     | Includes ac transients, requires proper decoupling. (3)  | 2-Ω ±20% load                                                  | 5    | 14.4 | 18                    | V        |

| V <sub>(PVDD_RIPPLE)</sub> | Maximum ripple on PVDD                                   | V <sub>(PVDD)</sub> < 8 V                                      |      |      | 1                     | $V_{pp}$ |

| V <sub>(HI-Z)</sub>        | HI-Z pin voltage range relative to GND                   |                                                                | -0.3 | 3.3  | 5.5                   | V        |

| V <sub>(AIN)</sub> (1)     | Analog input-signal level                                | AC-coupled input voltage                                       | 0    |      | 0.25-1 <sup>(2)</sup> | Vrms     |

| V <sub>(IH_STANDBY)</sub>  | HI-Z and STANDBY pins input voltage for logic-level high |                                                                | 2    |      |                       | V        |

| V <sub>(IL_STANDBY)</sub>  | HI-Z and STANDBY pins input voltage for logic-level low  |                                                                |      |      | 0.7                   | V        |

| V <sub>(IH_SCL)</sub>      | SCL pin input voltage for logic-level high               | $R_{(PU\_12C)}$ = 4.7-kΩ pullup, supply voltage = 3.3 V or 5 V | 2.1  |      |                       | V        |

| V <sub>(IH_SDA)</sub>      | SDA pin input voltage for logic-level high               | $R_{(PU\_12C)}$ = 4.7-kΩ pullup, supply voltage = 3.3 V or 5 V | 2.1  |      |                       | V        |

| V <sub>(IL_SCL)</sub>      | SCL pin input voltage for logic-level low                | $R_{(PU\_12C)}$ = 4.7-kΩ pullup, supply voltage = 3.3 V or 5 V |      |      | 1.1                   | V        |

| V <sub>(IL_SDA)</sub>      | SDA pin input voltage for logic-level low                | $R_{(PU\_12C)}$ = 4.7-kΩ pullup, supply voltage = 3.3 V or 5 V |      |      | 1.1                   | V        |

| T <sub>A</sub>             | Ambient temperature                                      |                                                                | -40  |      | 125                   | °C       |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2024 Texas Instruments Incorporated

4

Product Folder Links: TSD5402-Q1

<sup>(2)</sup> See the section for information on analog input voltage and ac coupling.

|                                              |                                                                        |                                                                                         | MIN | NOM | MAX | UNIT |

|----------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----|-----|-----|------|

| R <sub>(L)</sub>                             | Nominal load impedance                                                 | When using low-impedance loads, do not exceed overcurrent limit.                        | 2   | 4   | 60  | Ω    |

| V <sub>(PU)</sub>                            | Pullup voltage supply (for open-drain logic outputs)                   | V <sub>(PU)</sub> must be less than (V <sub>(PVDD)</sub> - 1V) during normal operation. | 3   | 3.3 | 5.5 | V    |

| R <sub>(PU_EXT)</sub>                        | External pullup resistor on open-drain logic outputs                   | Resistor connected between open-drain logic output and $V_{(PU)}$ supply.               | 10  |     | 50  | kΩ   |

| R <sub>(PU_I2C)</sub>                        | I <sup>2</sup> C pullup resistance on SDA and SCL pins                 |                                                                                         | 1   | 4.7 | 10  | kΩ   |

| C <sub>(PVDD)</sub>                          | External capacitor on the PVDD pin, typical value ± 20% <sup>(3)</sup> |                                                                                         |     | 10  |     | μF   |

| C <sub>(BYP)</sub>                           | External capacitor on the BYP pin, typical value ± 10%                 |                                                                                         |     | 1   |     | μF   |

| C <sub>(OUT)</sub>                           | External capacitance to GND on OUT_X pins                              |                                                                                         |     |     | 4   | μF   |

| C <sub>(IN)</sub>                            | External capacitance to analog input pin in series with input signal   |                                                                                         |     | 1   |     | μF   |

| C <sub>(BSTN)</sub> ,<br>C <sub>(BSTP)</sub> | External boostrap capacitor, typical value ± 20%                       |                                                                                         |     | 220 |     | nF   |

- Signal input for full unclipped output with gains of 36dB, 32dB, 26dB, and 20dB Maximum recommended input voltage is determined by the gain setting.

- (3) See the section.

#### **5.4 Thermal Information**

|                       |                                              | TSD5402      |      |

|-----------------------|----------------------------------------------|--------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PWP (HTSSOP) | UNIT |

|                       |                                              | 16 PINS      |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 39.4         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 24.9         | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 20           | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.6          | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 19.8         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2            | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the application report.

## 5.5 Electrical Characteristics

$T_C$  = 25°C, PVDD = 14.4 V,  $R_L$  = 4  $\Omega$ ,  $P_{(O)}$  = 1 W/ch, AES17 filter, default I<sup>2</sup>C settings (unless otherwise noted)

| PARAMETER                         | TEST CONDITIONS                                   | MIN | TYP   | MAX | UNIT |

|-----------------------------------|---------------------------------------------------|-----|-------|-----|------|

| OPERATING CURRENT                 |                                                   |     |       |     |      |

| PVDD idle current                 | In DRIVE mode, no signal present                  |     | 16    |     | mA   |

| PVDD standby current              | STANDBY mode, HI-Z= 0 V                           |     | 5     | 20  | μA   |

| OUTPUT POWER                      |                                                   |     |       | '   |      |

| Output newer per channel          | 4 Ω, THD+N ≤ 1%, 1 kHz, T <sub>C</sub> = 75°C     | 6   |       |     | W    |

| Output power per channel          | 4 Ω, THD+N = 10%, 1 kHz, T <sub>C</sub> = 75°C    |     | 8     |     | VV   |

| Power efficiency                  | 4 Ω, P <sub>(O)</sub> = 8 W (10% THD)             |     | 83%   |     |      |

| OUTPUT PERFORMANCE                |                                                   | ,   |       |     |      |

| Noise voltage at output           | G = 20 dB, zero input, and A-weighting            |     | 65    |     | μV   |

| Common-mode rejection ratio       | f = 1 kHz, 100 mVrms referenced to GND, G = 20 dB |     | 63    |     | dB   |

| Power-supply rejection ratio      | PVDD = 14.4 Vdc + 1 Vrms, f = 1 kHz               |     | 75    |     |      |

| Total harmonic distortion + noise | P <sub>(O)</sub> = 1 W, f = 1 kHz                 |     | 0.05% |     |      |

Product Folder Links: TSD5402-Q1

Copyright © 2024 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

5

$T_C$  = 25°C, PVDD = 14.4 V,  $R_L$  = 4  $\Omega$ ,  $P_{(O)}$  = 1 W/ch, AES17 filter, default I<sup>2</sup>C settings (unless otherwise noted)

| PARAMETER                                                               | W/ch, AES17 filter, default I <sup>2</sup> C settings (unless | MIN  | TYP  | MAX  | UNIT |

|-------------------------------------------------------------------------|---------------------------------------------------------------|------|------|------|------|

| Switching fraguency                                                     | Switching frequency selectable for AM                         |      | 400  |      | kHz  |

| Switching frequency                                                     | interference avoidance                                        |      | 500  |      | KΠZ  |

| Internal common-mode input bias voltage                                 | Internal bias applied to IN_N, IN_P pins                      |      | 3    |      | V    |

|                                                                         | Source impedance = $0 \Omega$ , register 0x03 bits 7–6 = 00   | 19   | 20   | 21   |      |

| Voltage gain (V / V )                                                   | Source impedance = 0 $\Omega$ , register 0x03 bits 7–6 = 01   | 25   | 26   | 27   | dB   |

| Voltage gain (V <sub>O</sub> / V <sub>IN</sub> )                        | Source impedance = $0 \Omega$ , register 0x03 bits 7–6 = 10   | 31   | 32   | 33   | αБ   |

|                                                                         | Source impedance = 0 $\Omega$ , register 0x03 bits 7–6 = 11   | 35   | 36   | 37   |      |

| PWM OUTPUT STAGE                                                        |                                                               |      |      | '    |      |

| FET drain-to-source resistance                                          | T <sub>J</sub> = 25°C                                         |      | 180  |      | mΩ   |

| Output offset voltage                                                   | Zero input signal, G = 20 dB                                  |      |      | ±25  | mV   |

| PVDD OVERVOLTAGE (OV) PROTECTION                                        |                                                               |      |      |      |      |

| PVDD overvoltage-shutdown set                                           |                                                               | 19.5 | 21   | 22.5 | V    |

| PVDD overvoltage-shutdown hysteresis                                    |                                                               |      | 0.6  |      | V    |

| PVDD UNDERVOLTAGE (UV) PROTECTION                                       |                                                               |      |      | ,    |      |

| PVDD undervoltage-shutdown set                                          |                                                               | 3.6  | 4    | 4.4  | V    |

| PVDD undervoltage-shutdown hysteresis                                   |                                                               |      | 0.25 |      | V    |

| ВҮР                                                                     |                                                               |      |      |      |      |

| BYP pin voltage                                                         |                                                               | 6.4  | 6.9  | 7.4  | V    |

| POWER-ON RESET (POR)                                                    |                                                               |      |      |      |      |

| PVDD voltage for POR                                                    |                                                               |      |      | 4.1  | V    |

| PVDD recovery hysteresis voltage for POR                                |                                                               |      | 0.3  |      | V    |

| OVERTEMPERATURE (OT) PROTECTION                                         |                                                               |      |      |      |      |

| Junction temperature for overtemperature shutdown                       |                                                               | 155  | 170  |      | °C   |

| Junction temperature overtemperature shutdown hystersis                 |                                                               |      | 15   |      | °C   |

| OVERCURRENT (OC) SHUTDOWN PROTECTION                                    | N                                                             |      |      | '    |      |

| Maximum current (peak output current)                                   |                                                               |      | 2.4  |      | Α    |

| STANDBY PIN                                                             |                                                               |      |      |      |      |

| STANDBY pin current                                                     |                                                               |      | 0.1  | 0.2  | μA   |

| DC DETECT                                                               |                                                               |      |      | ,    |      |

| DC detect threshold                                                     |                                                               |      | 2.9  |      | V    |

| DC detect step response time                                            |                                                               |      | -    | 700  | ms   |

| FAULT REPORT                                                            |                                                               |      |      |      |      |

| FAULT pin output voltage for logic-level high (open-drain logic output) | External 47-kΩ pullup resistor to 3.3 V                       | 2.4  |      |      | V    |

| FAULT pin output voltage for logic-level low (opendrain logic output)   | External 47-kΩ pullup resistor to 3.3 V                       |      |      | 0.5  | V    |

| LOAD DIAGNOSTICS                                                        |                                                               |      |      |      |      |

| Resistance to detect a short from OUT pin(s) to PVDD or ground          |                                                               |      |      | 200  | Ω    |

| Open-circuit detection threshold                                        | Including load wires                                          | 70   | 95   | 120  | Ω    |

| Chart aircuit detection threehold                                       | Including load wires                                          | 0.9  | 1.2  | 1.5  | Ω    |

| Short-circuit detection threshold                                       | Inoldania loda wiles                                          | 0.0  | 1.2  | 1.5  | 32   |

Product Folder Links: TSD5402-Q1

Copyright © 2024 Texas Instruments Incorporated

6

$T_C = 25^{\circ}C$ , PVDD = 14.4 V,  $R_L = 4 \Omega$ ,  $P_{(O)} = 1 \text{ W/ch}$ , AES17 filter, default  $I^2C$  settings (unless otherwise noted)

| PARAMETER                                   | TEST CONDITIONS                                                | MIN | TYP | MAX | UNIT |

|---------------------------------------------|----------------------------------------------------------------|-----|-----|-----|------|

| SDA pin output voltage for logic-level high | $R_{(PU\_12C)}$ = 4.7-kΩ pullup, supply voltage = 3.3 V or 5 V | 2.4 |     |     | V    |

| SDA pin output voltage for logic-level low  | 3-mA sink current                                              |     |     | 0.4 | V    |

| Capacitance for SCL and SDA pins            |                                                                |     |     | 10  | pF   |

| Capacitance for SDA pin                     | STANDBY mode                                                   |     | 30  |     | pF   |

## 5.6 Timing Requirements for I2C Interface Signals

over recommended operating conditions (unless otherwise noted)

|                    |                                                                  | MIN  | NOM MAX | UNIT |

|--------------------|------------------------------------------------------------------|------|---------|------|

| f <sub>(SCL)</sub> | SCL clock frequency                                              |      | 400     | kHz  |

| t <sub>r</sub>     | Rise time for both SDA and SCL signals                           |      | 300     | ns   |

| t <sub>f</sub>     | Fall time for both SDA and SCL signals                           |      | 300     | ns   |

| t <sub>w(H)</sub>  | SCL pulse duration, high                                         | 0.6  |         | μs   |

| t <sub>w(L)</sub>  | SCL pulse duration, low                                          | 1.3  |         | μs   |

| t <sub>su(2)</sub> | Setup time for START condition                                   | 0.6  |         | μs   |

| t <sub>h(2)</sub>  | START condition hold time before generation of first clock pulse | 0.6  |         | μs   |

| t <sub>su(1)</sub> | Data setup time                                                  | 100  |         | ns   |

| t <sub>h(1)</sub>  | Data hold time                                                   | 0(1) |         | ns   |

| t <sub>su(3)</sub> | Setup time for STOP condition                                    | 0.6  |         | μs   |

| C <sub>(B)</sub>   | Load capacitance for each bus line                               |      | 400     | pF   |

<sup>(1)</sup> A device must internally provide a hold time of at least 300ns for the SDA signal to bridge the undefined region of the falling edge of SCL.

1

Product Folder Links: TSD5402-Q1

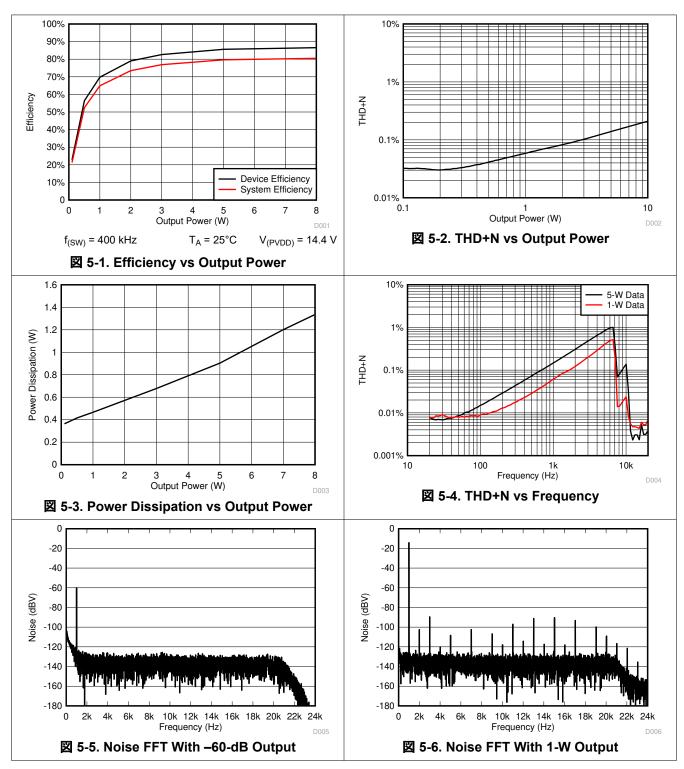

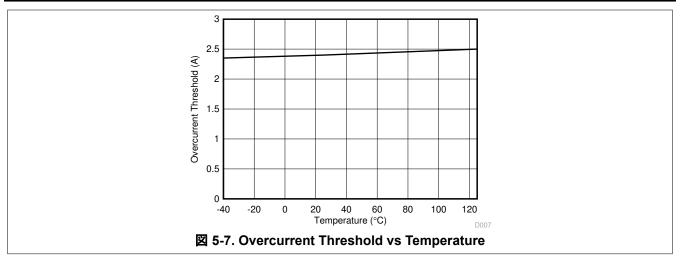

## 5.7 Typical Characteristics

$T_C$  = 25°C, PVDD = 14.4 V,  $R_L$  = 4  $\Omega$ ,  $P_{(O)}$  = 1 W per channel, AES17 filter, 1-kHz input, default I<sup>2</sup>C settings (unless otherwise noted)

9

Product Folder Links: TSD5402-Q1

## 6 Detailed Description

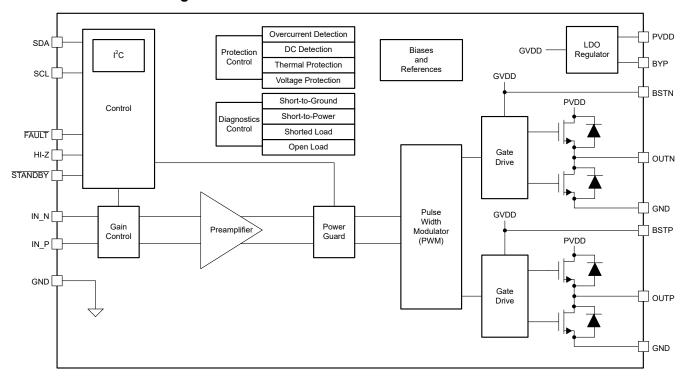

#### 6.1 Overview

The TSD5402-Q1 is an analog-input class-D sensor driving amplifier for use in an automotive/industrial environment. The design uses an ultra-efficient class-D technology developed by Texas Instruments with additional features specific to the automotive industry. The class-D technology allows for reduced power consumption, reduced heat, and reduced peak currents in the electrical system. The device functions as a highly-integrated sensor-driver with smaller size and higher efficiency than traditional class-AB solutions.

The TSD5402-Q1 device has seven core design blocks:

- PWM

- · Gate drive

- Power FETs

- Diagnostics

- Protection

- · Power supply

- I<sup>2</sup>C serial communication bus

## 6.2 Functional Block Diagram

www.ti.com/ja-jp

## **6.3 Feature Description**

#### 6.3.1 Analog Input and Preamplifier

The differential input stage of the amplifier cancels common-mode noise that appears on the inputs. For a differential source, connect the positive lead to IN\_P and the negative lead to IN\_N. The inputs must be accoupled to minimize the output dc-offset and ensure correct ramping of the output voltages. For good transient performance, the impedance seen at each of the two differential inputs should be the same.

The gain setting impacts the analog input impedance of the amplifier. See Input Impedance and Gain for typical values.

| 20-1. Input impedance and Cam |                 |  |  |  |  |  |  |

|-------------------------------|-----------------|--|--|--|--|--|--|

| Gain                          | Input Impedance |  |  |  |  |  |  |

| 20dB                          | 60kΩ ± 20%      |  |  |  |  |  |  |

| 26dB                          | 30kΩ ± 20%      |  |  |  |  |  |  |

| 32dB                          | 15kΩ ± 20%      |  |  |  |  |  |  |

| 36dB                          | 9kΩ ± 20%       |  |  |  |  |  |  |

表 6-1. Input Impedance and Gain

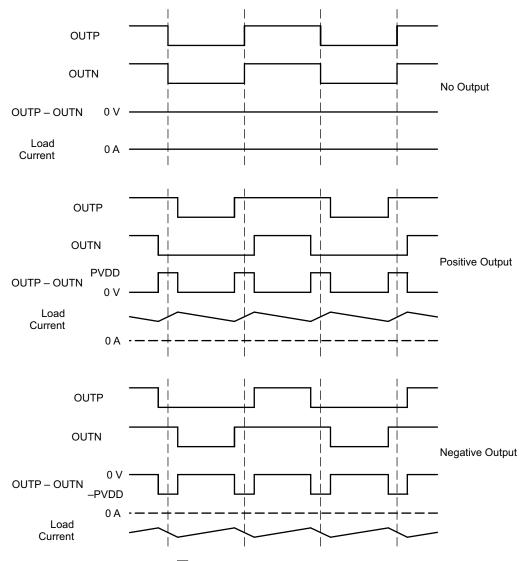

## 6.3.2 Pulse-Width Modulator (PWM)

The PWM converts the analog signal from the preamplifier into a switched signal of varying duty cycle. This is the critical stage that defines the class-D architecture. In the TSD5402-Q1, the modulator is an advanced design with high bandwidth, low noise, low distortion, and excellent stability.

The pulse-width modulation scheme allows increased efficiency at low power. Each output is switching from 0 V to PVDD. The OUTP and OUTN pins are in phase with each other with no input so that there is little or no current in the load. The duty cycle of OUTP is greater than 50% and the duty cycle OUTN is less than 50% for positive output voltages. The duty cycle of OUTN is greater than 50% and the duty cycle of OUTP is less than 50% for negative output voltages. The voltage across the load is at 0 V through most of the switching period, reducing power loss.

Product Folder Links: TSD5402-Q1

資料に関するフィードバック(ご意見やお問い合わせ)を送信

11

図 6-1. BD Mode Modulation

#### 6.3.3 Gate Drive

The gate driver accepts the low-voltage PWM signal and level-shifts the signal to drive a high-current, full-bridge, power FET stage. The device uses proprietary techniques to optimize EMI performance.

#### 6.3.4 Power FETs

The BTL output comprises four matched N-channel FETs for high efficiency and maximum power transfer to the load. By design, the FETs withstand large voltage transients during a load-dump event.

#### 6.3.5 Load Diagnostics

The device incorporates load diagnostic circuitry designed for detecting and determining the status of output connections. The device supports the following diagnostics:

- Short to GND

- · Short to PVDD

- · Short across load

- Open load

The device reports the presence of any of the short or open conditions to the system via I<sup>2</sup>C register read.

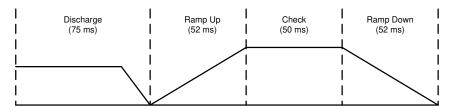

#### 6.3.5.1 Load Diagnostics Sequence

The load diagnostic function runs on de-assertion of STANDBY or when the device is in a fault state (dc detect, overcurrent, overvoltage, undervoltage, and overtemperature). During this test, the outputs are in a Hi-Z state. The device determines whether the output is a short to GND, short to PVDD, open load, or shorted load. The load diagnostic biases the output, which therefore requires limiting the capacitance value for proper functioning; see the *Recommended Operating Conditions*. The load diagnostic test takes approximately 229 ms to run. Note that the *check* phase repeats up to five times if a fault is present or a large capacitor to GND is present on the output. On detection of an open load, the output still operates. On detection of any other fault condition, the output goes into a Hi-Z state, and the device checks the load continuously until removal of the fault condition. After detection of a normal output condition, the signal output starts. The load diagnostics run after every other overvoltage (OV) event. The load diagnostic for open load only has I<sup>2</sup>C reporting. All other faults have I<sup>2</sup>C and FAULT pin assertion.

The device performs load diagnostic tests as shown in  $\boxtimes$  6-2.

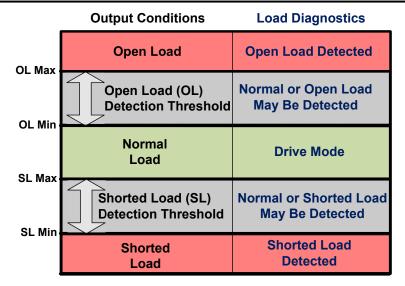

☑ 6-3 illustrates how the diagnostics determine the load based on output conditions.

**図 6-2. Load Diagnostics Sequence of Events**

Product Folder Links: TSD5402-Q1

資料に関するフィードバック(ご意見やお問い合わせ) を送信

13

図 6-3. Load Diagnostic Reporting Thresholds

## 6.3.5.2 Faults During Load Diagnostics

If the device detects a fault (such as overtemperature, overvoltage, or undervoltage) during the load diagnostics test, the device exits the load diagnostics, which can result in a pop or click on the output.

#### 6.3.6 Protection and Monitoring

- Overcurrent Shutdown (OCSD)—The overcurrent shutdown forces the output into Hi-Z. The device asserts the FAULT pin and updates the I<sup>2</sup>C register.

- **DC Detect**—This circuit checks for a dc offset continuously during normal operation at the output of the amplifier. If a dc offset occurs, the device asserts the FAULT pin and updates the I<sup>2</sup>C register. Note that the dc detection threshold follows PVDD changes.

- Overtemperature Shutdown (OTSD)—The device shuts down when the die junction temperature reaches the overtemperature threshold. The device asserts the FAULT pin asserts and updates I<sup>2</sup>C register. Recovery is automatic when the temperature returns to a safe level.

- **Undervoltage (UV)**—The undervoltage (UV) protection detects low voltages on PVDD. In the event of an undervoltage condition, the device asserts the FAULT pin and resets the I<sup>2</sup>C register.

- Power-On Reset (POR)—Power-on reset (POR) occurs when PVDD drops below the POR threshold. A

POR event causes the I<sup>2</sup>C bus to go into a high-impedance state. After recovery from the POR event, the

device restarts automatically with default I<sup>2</sup>C register settings.

- Overvoltage (OV) and Load Dump—OV protection detects high voltages on PVDD. If PVDD reaches the overvoltage threshold, the device asserts the FAULT pin and updates the I<sup>2</sup>C register. The device can withstand 40-V load-dump voltage spikes. The device supports load-dump in both standby and active modes.

- **Power Guard**—This protection circuitry limits the output voltage to the value selected in I<sup>2</sup>C register 0x03. This value determines both the positive and negative limits. The user can use the Power Guard feature to improve battery life or protect the load from exceeding its excursion limits.

- Adjacent-Pin Shorts—The device design is such that shorts between adjacent pins do not cause damage.

#### 6.3.7 I<sup>2</sup>C Serial Communication Bus

The device communicates with the system processor via the I<sup>2</sup>C serial communication bus as an I<sup>2</sup>C target-only device. The processor can poll the device via I<sup>2</sup>C to determine the operating status. All reports of fault conditions and detections are via I<sup>2</sup>C. The system can also set numerous features and operating conditions via I<sup>2</sup>C. The I<sup>2</sup>C interface is active approximately 1 ms after the STANDBY pin is high.

Product Folder Links: TSD5402-Q1

The I<sup>2</sup>C interface controls the following device features:

- Changing gain setting to 20dB, 26dB, 32dB, or 36dB.

- · Controlling peak voltage value of Power Guard protection circuitry

Copyright © 2024 Texas Instruments Incorporated

www.ti.com/ja-jp JAJSVF9 - SEPTEMBER 2024

- Reporting load diagnostic results

- Changing of switching frequency for AM radio avoidance

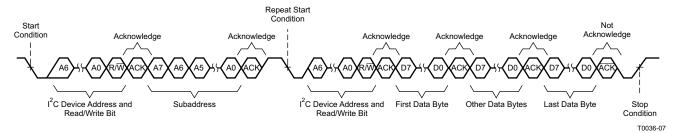

#### 6.3.7.1 I<sup>2</sup>C Bus Protocol

The device has a bidirectional serial control interface that is compatible with the Inter IC (I<sup>2</sup>C) bus protocol and supports 400kbps data transfer rates for random and sequential write and read operations. This is a target-only device that does not support a multicontroller bus environment or wait-state insertion. The controller device uses the I<sup>2</sup>C control interface to program the registers of the device and to read device status.

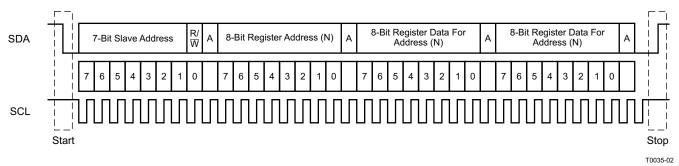

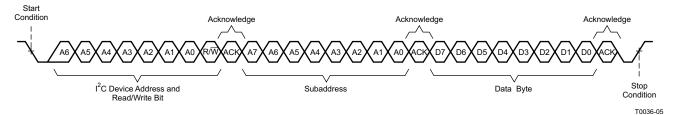

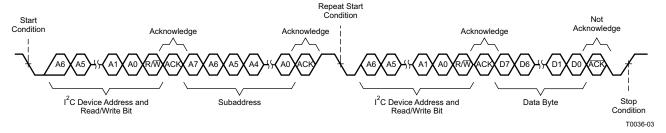

The I<sup>2</sup>C bus employs two signals, SDA (data) and SCL (clock), to communicate between integrated circuits in a system. Data transfer on the bus is serial, one bit at a time. The transfer of address and data is in byte (8-bit) format with the most-significant bit (MSB) transferred first. In addition, the receiving device acknowledges each byte transferred on the bus with an acknowledge bit. Each transfer operation begins with the controller device driving a start condition on the bus and ends with the controller device driving a stop condition on the bus. The bus uses transitions on the data pin (SDA) while the clock is HIGH to indicate start and stop conditions. A HIGHto-LOW transition on SDA indicates a start, and a LOW-to-HIGH transition indicates a stop. Normal data bit transitions must occur within the low time of the clock period. Z 6-4 shows these conditions. The controller generates the 7-bit target address and the read/write  $(R/\overline{W})$  bit to open communication with another device and then waits for an acknowledge condition. The device holds SDA LOW during the acknowledge clock period to indicate an acknowledgment. When this occurs, the controller transmits the next byte of the sequence. The address for each device is a unique 7-bit target address plus a R/ W bit (1 byte). All compatible devices share the same signals via a bidirectional bus using a wired-AND connection. The SDA and SCL signals require the use of an external pullup resistor to set the HIGH level for the bus. There is no limit on the number of bytes that the communicating devices can transmit between start and stop conditions. After transfer of the last word, the controller generates a stop condition to release the bus.

図 6-4. Typical I<sup>2</sup>C Sequence

To communicate with the device, the I<sup>2</sup>C controller uses addresses shown in 🗵 6-4. Transmission of read and write data can be by single-byte or multiple-byte data transfers.

#### 6.3.7.2 Random Write

As shown in 🗵 6-5, a single-byte data-write transfer begins with the controller device transmitting a start condition followed by the I<sup>2</sup>C device address and the read/write bit. The read/write bit determines the direction of the data transfer. For a write data transfer, the read/write bit is a 0. After receiving the correct I<sup>2</sup>C device address and the read/write bit, the device responds with an acknowledge bit. Next, the controller transmits the address byte corresponding to the internal memory address being accessed. After receiving the address byte, the device again responds with an acknowledge bit. Next, the controller device transmits the data byte for writing to the memory address being accessed. After receiving the data byte, the device again responds with an acknowledge bit. Finally, the controller device transmits a stop condition to complete the single-byte data-write transfer.

Product Folder Links: TSD5402-Q1

図 6-5. Random Write Transfer

#### 6.3.7.3 Random Read

As shown in 🗵 6-6, a single-byte data-read transfer begins with the controller device transmitting a start condition followed by the I<sup>2</sup>C device address and the read/write bit. For the data-read transfer, the controller device performs both a write and a following read. Initially, the controller device performs a write to transfer the address byte of the internal memory address to be read. As a result, the read/write bit is a 0. After receiving the address and the read/write bit, the device responds with an acknowledge bit. In addition, after sending the internal memory address byte, the controller device transmits another start condition followed by the device address and the read/write bit again. This time, the read/write bit is a 1, indicating a read transfer. After receiving the address and the read/write bit, the device again responds with an acknowledge bit. Next, the device transmits the data byte from the memory address being read. After receiving the data byte, the controller device transmits a not-acknowledge followed by a stop condition to complete the single-byte data-read transfer.

図 6-6. Random Read Transfer

## 6.3.7.4 Sequential Read

A sequential data-read transfer is identical to a single-byte data-read transfer except that the TSD5402-Q1 transmits multiple data bytes to the controller device as shown in  $\boxtimes$  6-7. Except for the last data byte, the controller device responds with an acknowledge bit after receiving each data byte and automatically increments the I<sup>2</sup>C subaddress by one. After receiving the last data byte, the controller device transmits a not-acknowledge followed by a stop condition to complete the transfer.

図 6-7. Sequential Read Transfer

つせ) を送信 Copyright © 2024 Texas Instruments Incorporated Product Folder Links: *TSD5402-Q1*

#### 6.4 Device Functional Modes

#### 6.4.1 Hardware Control Pins

Three discrete hardware pins are available for real-time control and indication of device status.

- 1. FAULT pin: This active-low open-drain output pin indicates the presence of a fault condition which requires the device to go into the Hi-Z mode. On assertion of this pin, the device has protected itself and the system from potential damage. The system can read the exact nature of the fault via I<sup>2</sup>C with the exception of PVDD undervoltage faults below POR, in which case the I<sup>2</sup>C bus is no longer operational.

- 2. STANDBY pin: Assertion of this active-low pin sends the device into a complete shutdown, limiting the current draw. Load-dump protection is supported. I<sup>2</sup>C is inactive and non-blocking (does not pull I<sup>2</sup>C bus low) and the device registers are reset.

- 3. **HI-Z** pin: On assertion of this active-high pin, the device is in Hi-Z mode. The output pins stop switching and no signal passes from the input to the output. To place the device back into drive mode, deassert this pin. The HI-Z pin should be asserted low when the device is in STANDBY.

#### 6.4.2 EMI Considerations

Automotive-level EMI performance depends on both careful integrated-circuit design and good system-level design. Controlling sources of electromagnetic interference (EMI) was a major consideration in all aspects of the design.

The design has minimal parasitic inductances due to the short leads on the package, which dramatically reduces the EMI that results from current passing from the die to the system PCB. The design incorporates circuitry that optimizes output transitions that cause EMI.

#### 6.4.3 Operating Modes and Faults

The following tables list operating modes and faults.

表 6-2. Operating Modes

| STATE NAME          | OUTPUT                       | OSCILLATOR | I <sup>2</sup> C (1)                       |

|---------------------|------------------------------|------------|--------------------------------------------|

| STANDBY             | HI-Z, floating               | Stopped    | Inactive, Registers<br>Reset, Non-blocking |

| Load diagnostic     | DC biased                    | Active     | Active                                     |

| HI-Z (Hi-Z) / Fault | Hi-Z, floating               | Active     | Active                                     |

| DRIVE               | Switching with output signal | Active     | Active                                     |

(1) See SLOA264 for I2C applications.

表 6-3. Faults and Actions

| FAULT<br>EVENT                     | FAULT EVENT<br>CATEGORY | MONITORING<br>MODES | REPORTING<br>METHOD          | ACTION<br>TYPE      | ACTION<br>RESULT            | CLEARING                        | STANDBY                    |

|------------------------------------|-------------------------|---------------------|------------------------------|---------------------|-----------------------------|---------------------------------|----------------------------|

| POR                                |                         |                     | Not applicable               |                     | Standby                     |                                 | Disabled                   |

| UV                                 | Voltage fault           | HI-Z (Hi-Z), Drive  |                              |                     |                             |                                 | Disabled                   |

| OV and Load<br>dump <sup>(1)</sup> | Tonago nam              | = ( =), 5           | I <sup>2</sup> C + FAULT pin | Hard stop (no ramp) |                             |                                 | Protected, No<br>Reporting |

| OTSD                               | Thermal fault           | HI-Z (Hi-Z), Drive  | _                            |                     | Hi-Z                        | Self-clearing                   |                            |

| OC fault                           | Output channel          | Drive               |                              |                     |                             |                                 |                            |

| DC detect                          | fault                   | Dilve               | I <sup>2</sup> C + FAULT pin |                     |                             |                                 | Disabled                   |

| Load diagnostic -<br>short         | Diagnostic              | Hi-Z                |                              | None                | Hi-Z, re-run<br>diagnostics |                                 | Disabled                   |

| Load diagnostic - open             | Diagilostic             | 111-2               | I <sup>2</sup> C             | NOTIC               | None                        | Clears on next diagnostic cycle |                            |

(1) Tested in accordance with ISO7637-1

Copyright © 2024 Texas Instruments Incorporated

Product Folder Links: TSD5402-Q1

# 7 Register Maps

## 表 7-1. I<sup>2</sup>C Address

| DESCRIPTION            |     |   | FIXI | ED ADDR | READ/WRITE BIT | I <sup>2</sup> C ADDRESS |   |     |             |

|------------------------|-----|---|------|---------|----------------|--------------------------|---|-----|-------------|

| DESCRIPTION            | MSB | 6 | 5    | 4       | 3              | 2                        | 1 | LSB | I C ADDRESS |

| I <sup>2</sup> C write | 1   | 1 | 0    | 1       | 1              | 0                        | 0 | 0   | 0xD8        |

| I <sup>2</sup> C read  | 1   | 1 | 0    | 1       | 1              | 0                        | 0 | 1   | 0xD9        |

# 7.1 I<sup>2</sup>C Address Register Definitions

## 表 7-2. I<sup>2</sup>C Address Register Definitions

| ADDRESS | R/ W | REGISTER DESCRIPTION                 |

|---------|------|--------------------------------------|

| 0x01    | R    | Latched fault register               |

| 0x02    | R    | Status and load diagnostics register |

| 0x03    | R/ W | Control register                     |

## 表 7-3. Fault Register (0x01)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | FUNCTION                                    |

|----|----|----|----|----|----|----|----|---------------------------------------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | No protection-created faults, default value |

| _  | _  | _  | _  | _  | _  | _  | 1  | Reserved                                    |

| -  | -  | -  | _  | _  | -  | 1  | _  | Reserved                                    |

| _  | _  | _  | _  | _  | 1  | _  | _  | A load-diagnostics fault has occurred.      |

| _  | _  | _  | _  | 1  | -  | _  | _  | Overcurrent shutdown has occurred.          |

| _  | _  | _  | 1  | _  | -  | _  | _  | PVDD undervoltage has occurred.             |

| _  | _  | 1  | _  | _  | _  | _  | _  | PVDD overvoltage has occurred.              |

| _  | 1  | _  | -  | _  | _  | _  | _  | DC offset protection has occurred.          |

| 1  | _  | _  | -  | _  | _  | _  | _  | Overtemperature shutdown has occurred.      |

## 表 7-4. Status and Load Diagnostic Register (0x02)

|    | st i ii ctatac ana zoaa zoagneene regieter (exez) |    |    |    |    |    |    |                                                  |

|----|---------------------------------------------------|----|----|----|----|----|----|--------------------------------------------------|

| D7 | D6                                                | D5 | D4 | D3 | D2 | D1 | D0 | FUNCTION                                         |

| 0  | 0                                                 | 0  | 0  | 0  | 0  | 0  | 0  | No load-diagnostic-created faults, default value |

| _  | _                                                 | _  | _  | _  | -  | _  | 1  | Output short to PVDD is present.                 |

| -  | _                                                 | _  | _  | _  | _  | 1  | _  | Output short to ground is present.               |

| -  | _                                                 | _  | _  | _  | 1  | _  | _  | Open load is present.                            |

| _  | _                                                 | _  | _  | 1  | -  | _  | _  | Shorted load is present.                         |

| _  | _                                                 | _  | 1  | _  | -  | _  | _  | In a fault condition                             |

| _  | _                                                 | 1  | _  | _  | -  | _  | _  | Performing load diagnostics                      |

| _  | 1                                                 | _  | _  | _  | _  | _  | _  | In Hi-Z mode                                     |

| 1  | _                                                 | _  | _  | _  | -  | _  | _  | In drive mode                                    |

Product Folder Links: TSD5402-Q1

資料に関するフィードバック(ご意見やお問い合わせ) を送信

Copyright © 2024 Texas Instruments Incorporated

# 表 7-5. Control Register (0x03)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | FUNCTION                                                                                 |

|----|----|----|----|----|----|----|----|------------------------------------------------------------------------------------------|

| 0  | 1  | 1  | 1  | 1  | 0  | 0  | 0  | 26dB gain, switching frequency set to 400kHz , Power Guard protection circuitry disabled |

| _  | _  | _  | _  | _  | _  | _  | 1  | Switching frequency set to 500khz                                                        |

| _  | _  | _  | _  | _  | 1  | 1  | -  | Reserved                                                                                 |

| _  | _  | 1  | 1  | 0  | _  | _  | _  | Power Guard protection circuitry set to 14V peak output                                  |

| _  | _  | 1  | 0  | 1  | _  | _  | _  | Power Guard protection circuitry set to 11.8V peak output                                |

| _  | _  | 1  | 0  | 0  | _  | _  | _  | Power Guard protection circuitry set to 9.8V peak output                                 |

| _  | _  | 0  | 1  | 1  | _  | _  | _  | Power Guard protection circuitry set to 8.4V peak output                                 |

| _  | _  | 0  | 1  | 0  | _  | _  | _  | Power Guard protection circuitry set to 7V peak output                                   |

| _  | _  | 0  | 0  | 1  | _  | _  | _  | Power Guard protection circuitry set to 5.9V peak output                                 |

| _  | _  | 0  | 0  | 0  | _  | _  | _  | Power Guard protection circuitry set to 5V peak output                                   |

| 0  | 0  | -  | -  | -  | -  | -  | _  | Gain set to 20dB                                                                         |

| 1  | 0  | -  | -  | -  | -  | -  | _  | Gain set to 32dB                                                                         |

| 1  | 1  | _  | _  | _  | _  | _  | _  | Gain set to 36dB                                                                         |

19

## 8 Application and Implementation

注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

## 8.1 Application Information

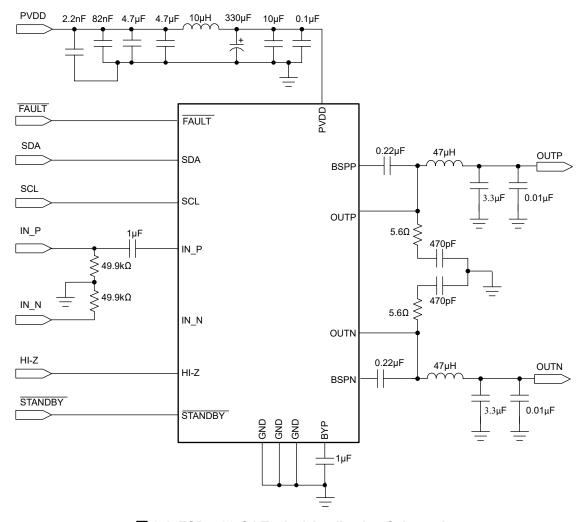

The device is a high-efficiency sensor driving class-D amplifier. Typical use of the device is to amplify a signal input to drive a sensor. The intent of its use is for a bridge-tied load (BTL) application, not for support of single-ended configuration. This section presents how to use the device in the application, including what external components are necessary and how to connect unused pins.

## 8.2 Typical Application

図 8-1. TSD5402-Q1 Typical Application Schematic

Product Folder Links: TSD5402-Q1

合わせ) を送信 Copyright © 2024 Texas Instruments Incorporated

#### 8.2.1 Design Requirements

Use the following for the design requirements:

## **Power supplies**

The device requires only a single power supply compliant with the recommended operation range. The device is designed to work with either a vehicle battery or regulated power supply such as from a backup battery.

#### Communication

The device communicates with the system controller with both discrete hardware control pins and with I<sup>2</sup>C. The device is an I<sup>2</sup>C target and thus requires a controller. If a controller I<sup>2</sup>C-compliant device is not present in the system, the device can still be used, but only with the default settings. Diagnostic information is limited to the discrete reporting FAULT pin.

#### **External components**

• 表 8-1 lists the components required for the device.

| 表 8-1. Supporting Component |

|-----------------------------|

|-----------------------------|

| EVM DESIGNATOR | QUANITY | VALUE          | SIZE                | DESCRIPTION                      | USE IN APPLICATION                 |

|----------------|---------|----------------|---------------------|----------------------------------|------------------------------------|

| C7             | 1       | 10 μF ± 10%    | 1206                | X7R ceramic capacitor, 25-V      | Power supply                       |

| C8             | 1       | 330 µF ± 20%   | 10 mm               | Low-ESR aluminum capacitor, 25-V | Power supply                       |

| C9, C16, C20   | 3       | 1 µF ± 10%     | 0805                | X7R ceramic capacitor, 25-V      | Analog signal input filter, bypass |

| C10, C14       | 2       | 0.22 μF ± 10%  | 0603                | X7R ceramic capacitor, 25-V      | Bootstrap capacitors               |

| C11, C17       | 2       | 3.3 µF ± 10%   | 0805                | X7R ceramic capacitor, 25-V      | Amplifier output filtering         |

| C13, C15       | 2       | 470 pF ± 10%   | 0603                | X7R ceramic capacitor, 250-V     | Amplifier output snubbers          |

| C6             | 1       | 0.1 µF ± 10%   | 0603                | X7R ceramic capacitor, 25-V      | Power supply                       |

| C2             | 1       | 2200 pF ± 10%  | 0603                | X7R ceramic capacitor, 50-V      | Power supply                       |

| C3             | 1       | 0.082 μF ± 10% | 0603                | X7R ceramic capacitor, 25-V      | Power supply                       |

| C4, C5         | 2       | 4.7 µF ± 10%   | 1206                | X7R ceramic capacitor, 25-V      | Power supply                       |

| C12, C18       | 2       | 0.01 µF ± 10%  | 0603                | X7R ceramic capacitor, 25-V      | Output EMI filtering               |

| L1             | 1       | 10 μH ± 20%    | 13.5 mm ×13.5<br>mm | Shielded ferrite inductor        | Power supply                       |

| L2             | 1       | 47<br>μH ± 20% | 8 mm × 8 mm         | Coupled inductor                 | Amplifier output filtering         |

| R5, R6         | 2       | 49.9 kΩ ± 1%   | 0805                | Resistors, 0.125-W               | Analog signal input filter         |

| R4, R7         | 2       | 5.6 Ω ± 5%     | 0805                | Resistors, 0.125-W               | Output snubbers                    |

## 8.2.1.1 Amplifier Output Filtering

Copyright © 2024 Texas Instruments Incorporated

Output FETs drive the amplifier outputs in an H-bridge configuration. These transistors are either fully off or on. The result is a square-wave output signal with a duty cycle that is proportional to the amplitude of the input signal. The amplifier outputs require a low-pass filter to filter out the PWM modulation carrier frequency. People frequently call this filter the L-C filter, due to the presence of an inductive element L and a capacitive element C to make up the 2-pole low-pass filter. The L-C filter attenuates the carrier frequency, reducing electromagnetic emissions and smoothing the current waveform which the load draws from the power supply. See Class-D LC Filter Design for a detailed description on proper component selection and design of an L-C filter based upon the desired load and response.

#### 8.2.1.2 Amplifier Output Snubbers

A snubber is an RC network placed at the output of the amplifier to dampen ringing or overshoot on the PWM output waveform. Overshoot and ringing can have negative impacts including: potential EMI sources and overvoltage stress of the output FETs or board components. For more information on the use and design of output snubbers, see *Class-D Output Snubber Design Guide*.

#### 8.2.1.3 Bootstrap Capacitors

The output stage uses dual NMOS transistors; therefore, the circuit requires bootstrap capacitors for the high side of each output to turn on correctly. The required capacitor connection is from BSTN to OUTN and from BSTP to OUTP as shown in  $\boxtimes$  8-1.

## 8.2.1.4 Analog Signal Input Filter

The circuit requires an input capacitor to allow biasing of the amplifier put to the proper dc level. The input capacitor and the input impedance of the amplifier form a high-pass filter with a -3-dB corner frequency determined by the equation:  $f = 1 / (2\pi R_{(i)}C_{(i)})$ , where  $R_{(i)}$  is the input impedance of the device based on the gain setting and  $C_{(i)}$  is the input capacitor value.  $\gtrsim 8$ -2 lists largest recommended input capacitor values. Use a capacitor which matches the application requirement for the lowest frequency but does not exceed the values listed

TYPICAL INPUT IMPEDANCE INPUT CAPACITANCE (µF) GAIN (dB) **HIGH-PASS FILTER (Hz)**  $(k\Omega)$ 1 27 20 60 1.5 1.8 1 5.3 26 30 3.3 1.6 32 15 5.6 2.3 9 10 36 1.8

表 8-2. Recommended Input AC-Coupling Capacitors

#### 8.2.2 Detailed Design Procedure

Use the following steps for the design procedure:

- Step 1: Hardware Schematic Design: Using the ⊠ 8-1 as a guide, integrate the hardware into the system schematic.

- Step 2: Following the layout guidelines recommended in the セクション 8.4.1 section, integrate the device and its supporting components into the system PCB file.

- Step 3: Thermal Design: The device has an exposed thermal pad which requires proper soldering. For more information, see *Semiconductor and IC Package Thermal Metrics* and *PowerPAD Thermally Enhanced Package*.

- Step 4: Develop software: The EVM User's Guide has detailed instructions for how to set up the device, interpret diagnostic information, and so forth. For information about control registers, see the セクション 7 section.

For questions and support, go to the E2E forums.

#### 8.2.2.1 Unused Pin Connections

Even if unused, always connect pins to a fixed rail; do not leave them floating. Floating input pins represent an ESD risk, therefore the user must adhere to the following guidance for each pin.

#### 8.2.2.1.1 HI-Z Pin

If the HI-Z pin is unused in the application, connect it to GND through a high-impedance resistor.

S問い合わせ) を送信 Copyright © 2024 Texas Instruments Incorporated Product Folder Links: *TSD5402-Q1*

#### 8.2.2.1.2 **STANDBY** Pin

If the STANDBY pin is unused in the application, connect it to a low-voltage rail such as 3.3V or 5V through a high-impedance resistor.

#### 8.2.2.1.3 I<sup>2</sup>C Pins (SDA and SCL)

If there is no microcontroller in the system, use of the device without  $I^2C$  communication is possible. In this situation, connect the SDA and SCL pins to 3.3V.

#### 8.2.2.1.4 Terminating Unused Outputs

If the FAULT pin does not report to a system microcontroller in the application, connect it to GND.

## 8.2.2.1.5 Using a Single-Ended Signal Input

When using a single-ended signal source, ac-ground the negative input through a capacitor equal in value to the input capacitor on the positive input, and apply the signal source to the positive input. For best performance, the ac ground should be at the signal source instead of at the device input if possible.

## 8.2.3 Application Curves

See the *Typical Characteristcs* section for application performance plots.

表 8-3. Table of Graphs

|                                      | <b>-</b> - |

|--------------------------------------|------------|

| GRAPH                                | FIGURE NO. |

| Efficiency vs Output Power           | ⊠ 5-1      |

| THD+N vs Output Power                | ⊠ 5-2      |

| Power Dissipation vs Output Power    | ⊠ 5-3      |

| THD+N vs Frequency                   | ⊠ 5-4      |

| Noise FFT With -60dB Output          | ⊠ 5-5      |

| Noise FFT With 1-W Output            | ⊠ 5-6      |

| Overcurrent Threshold vs Temperature | ⊠ 5-7      |

#### 8.3 Power Supply Recommendations

A car battery that can have a large voltage range most commonly provides power for the device. PVDD, a filtered battery voltage, is the supply for the output FETs and the low-side FET gate driver. Good power-supply decoupling is necessary, especially at low voltage and temperature levels. To meet the PVDD specifications in the *Electrical Characteristics* section, TI uses 10µF and 0.1µF ceramic capacitors near the PVDD pin along with a larger bulk 330µF electrolytic decoupling capacitor.

An internal linear regulator, which powers the analog circuitry, provides the voltage on the BYP pin. This supply requires an external bypass ceramic capacitor at the BYP pin.

23

English Data Sheet: SLOSEC9

Product Folder Links: TSD5402-Q1

#### 8.4 Layout

#### 8.4.1 Layout Guidelines

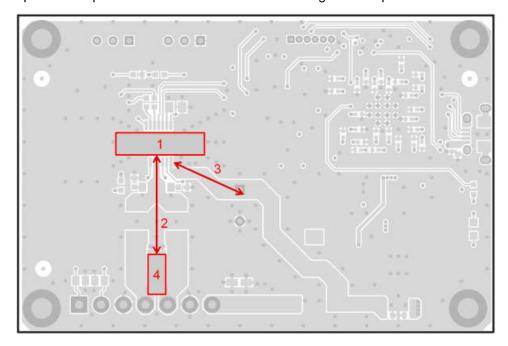

The EVM layout optimizes for thermal dissipation and EMC performance. The TSD5402-Q1 device has a thermal pad down, and good thermal conduction and dissipation require adequate copper area. Layout also affects EMC performance. TSD5402Q1EVM illustrations form the basis for the layout discussions.

## 8.4.2 Layout Examples

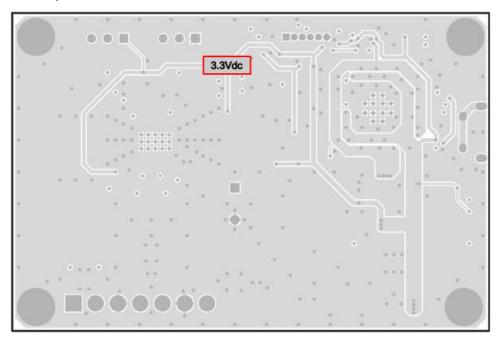

### 8.4.2.1 Top Layer

The red boxes around number 1 are the copper ground on the top layer. Soldered directly to the thermal pad, the ground is the first significant thermal dissipation required. There are vias that go to the other layers for further thermal relief, but vias have high thermal resistance. TI recommends that use of the top layer be mostly for thermal dissipation. A further recommendation is short routes from output pins to the second-order LC filter for EMC suppression. The number 2 arrow indicates these short routes for better ECM results. A short route from the PVDD pin to the LC filter from the battery or power source, as indicated by the number 3 arrow, also improves EMC suppression. Route on an outside layer for added current capability. The red box around number 4 indicates the ground plane that is common to both OUTP and OUTN. Place the capacitors of the LC filter in the common ground plane to help with common-mode noise and short ground loops

図 8-2. Top layer

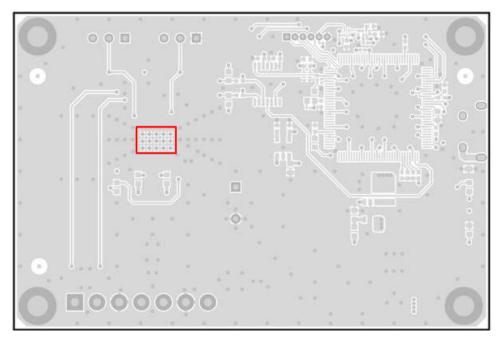

## 8.4.2.2 Second Layer - Signal Layer

Pour a full ground plane on an inner layer to keep current loops small to reduce EMI.

図 8-3. Signal Layer

25

English Data Sheet: SLOSEC9

Product Folder Links: TSD5402-Q1

#### 8.4.2.3 Third Layer - Power Layer

There is no requirement for a power plane, but TI recommends a wide single wide trace to keep the switching noise to a minimum and provide enough current to the device. The wide trace provides a low-impedance path from the power source. Suppression of switching noise (ripple voltage) on both the positive and return (ground) paths requires a low impedance.

図 8-4. Power Layer

#### 8.4.2.4 Bottom Layer - Ground Layer

The device has an exposed thermal pad on the bottom side for improved thermal performance. Conducting heat from the thermal pad to other layers requires thermal vias. Because the bottom layer is the secondary heat exchange surface to ambient, the thermal vias area must have low thermal resistance.

図 8-5. Bottom Layer

27

Product Folder Links: TSD5402-Q1

## 9 Device and Documentation Support

## 9.1 Device Support

## 9.1.1 サード・パーティ製品に関する免責事項

サード・パーティ製品またはサービスに関するテキサス・インスツルメンツの出版物は、単独またはテキサス・インスツルメンツの製品、サービスと一緒に提供される場合に関係なく、サード・パーティ製品またはサービスの適合性に関する是認、サード・パーティ製品またはサービスの是認の表明を意味するものではありません。

## 9.2 Documentation Support

#### 9.2.1 Related Documentation

For related documentation see the following:

- Class-D LC Filter Design (SLOA119)

- Class-D Output Snubber Design Guide (SLOA201)

- PowerPAD Thermally Enhanced Package (SLMA002)

## 9.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、www.tij.co.jp のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。 変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

#### 9.4 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

## 9.5 Trademarks

PowerPAD™ and テキサス・インスツルメンツ E2E™ are trademarks of Texas Instruments. すべての商標は、それぞれの所有者に帰属します。

## 9.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

#### 9.7 用語集

テキサス・インスツルメンツ用語集 この用語集には、用語や略語の一覧および定義が記載されています。

#### 10 Revision History

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| DATE           | REVISION | NOTES           |

|----------------|----------|-----------------|

| September 2024 | *        | Initial Release |

Product Folder Links: TSD5402-Q1

Copyright © 2024 Texas Instruments Incorporated

# 11 Mechanical, Packaging, and Orderable Information

The following pages include mechanical packaging and orderable information. This information is the most-current data available for the designated devices. This data is subject to change without notice and without revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Product Folder Links: TSD5402-Q1

Copyright © 2024 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

29

# 11.1 Package Option Addendum

## 11.1.1 Packaging Information

| Orderable Device | Status (1)  | Packag<br>e Type | Packag<br>e<br>Drawing | Pins | Packag<br>e Qty | Eco Plan | Lead/Ball<br>Finish <sup>(4)</sup> | MSL Peak<br>Temp <sup>(3)</sup> | Op Temp<br>(°C) | Device Marking <sup>(5) (6)</sup> |

|------------------|-------------|------------------|------------------------|------|-----------------|----------|------------------------------------|---------------------------------|-----------------|-----------------------------------|

| TSD5402QPWPRQ1   | PREVI<br>EW | HTSSO<br>P       | PWP                    | 16   | 2000            | TBD      | NIPDAU                             | Level-3-260C-1<br>68 HR         | -40 to 125      | TSD5402                           |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PRE PROD Unannounced device, not in production, not available for mass market, nor on the web, samples not available.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

**Green (RoHS & no Sb/Br)**: TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

- (3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

- (5) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device

- (6) Multiple Device markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

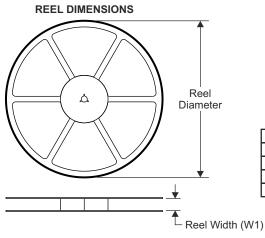

## 11.1.2 Tape and Reel Information

# TAPE DIMENSIONS KO P1 BO W Cavity AO

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

|    | Their between successive eavity conters                   |

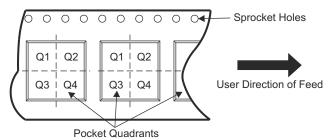

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| Device         | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TSD5402QPWPRQ1 | HTSSOP          | PWP                | 16   | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TSD54021QPWPRQ1 | HTSSOP       | PWP             | 16   | 2000 | 350.0       | 350.0      | 43.0        |

33

English Data Sheet: SLOSEC9

Product Folder Links: TSD5402-Q1

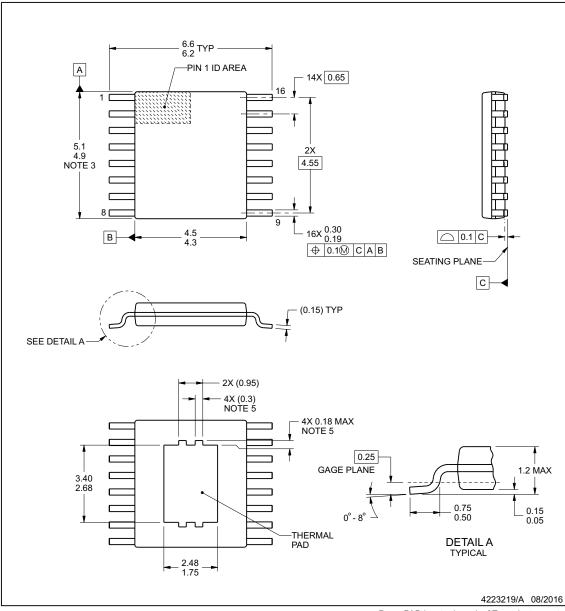

**PWP0016D**

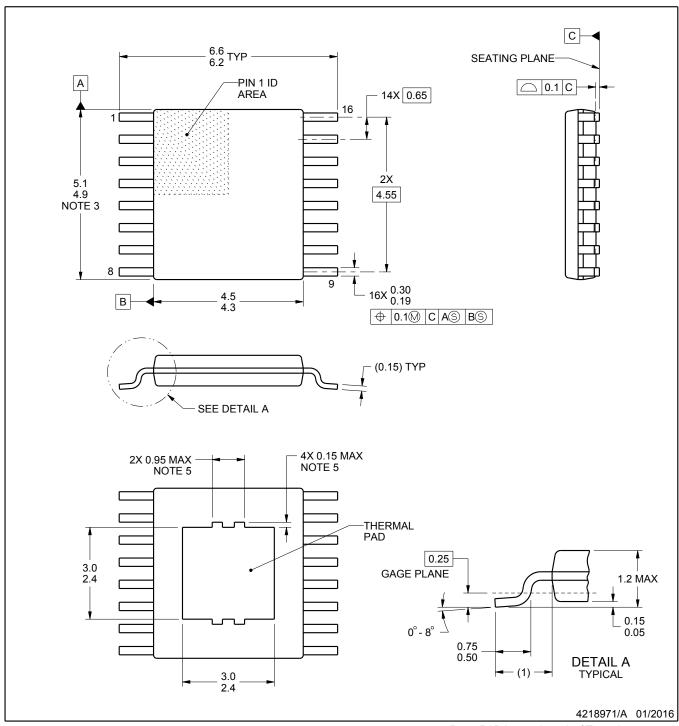

## **PACKAGE OUTLINE**

## PowerPAD™ TSSOP - 1.2 mm max height

PLASTIC SMALL OUTLINE

#### NOTES:

PowerPAD is a trademark of Texas Instruments.

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

This drawing is subject to change without notice.

This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

4. Reference JEDEC registration MO-153.

- 5. Features may differ and may not be present.

www.ti.com

Product Folder Links: TSD5402-Q1

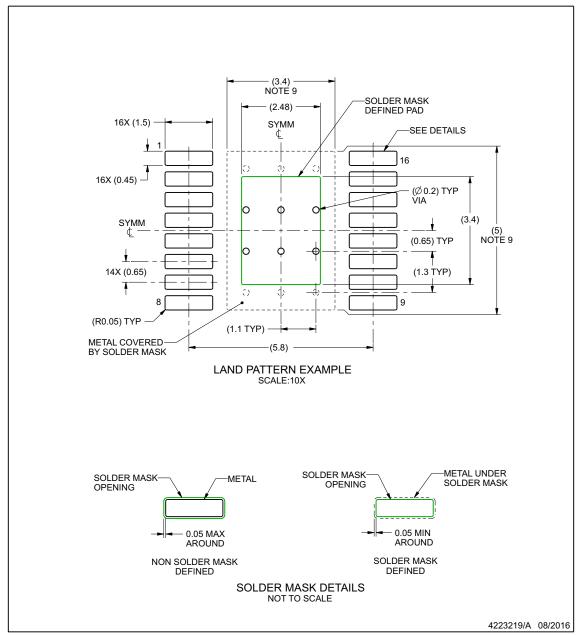

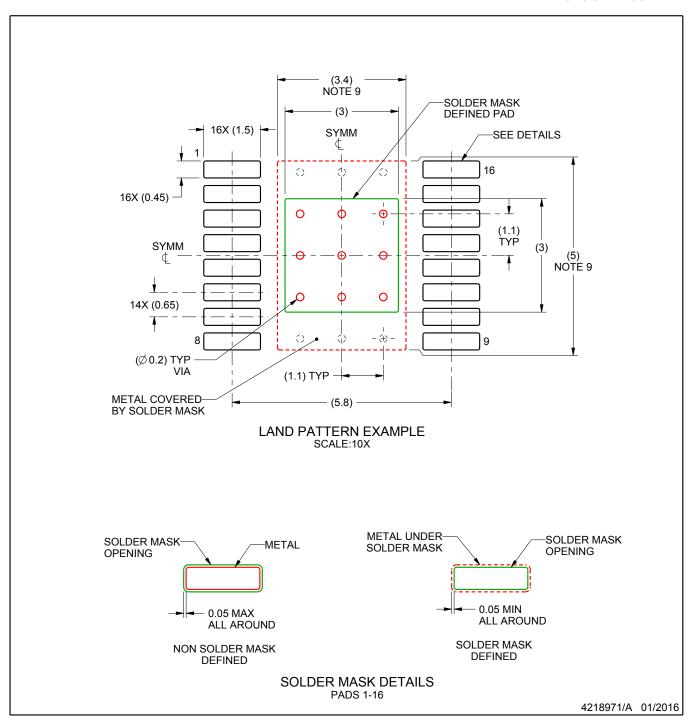

## **EXAMPLE BOARD LAYOUT**

## **PWP0016D**

## PowerPAD™ TSSOP - 1.2 mm max height

PLASTIC SMALL OUTLINE

#### NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

8. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 (www.ti.com/lit/slma002) and SLMA004 (www.ti.com/lit/slma004).

- 9. Size of metal pad may vary due to creepage requirement.

www.ti.com

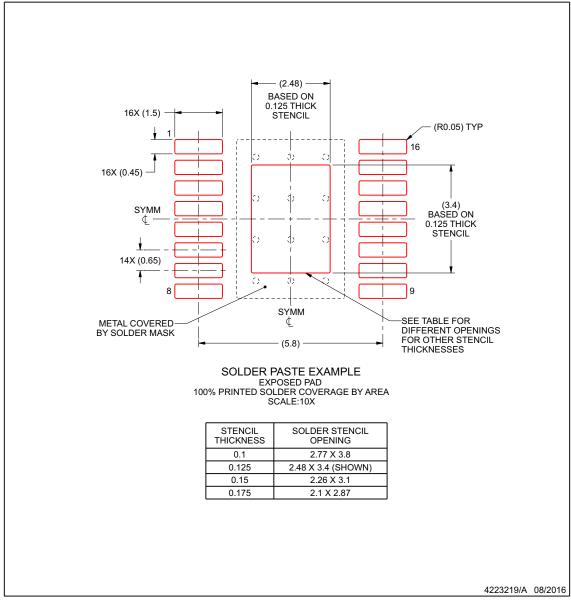

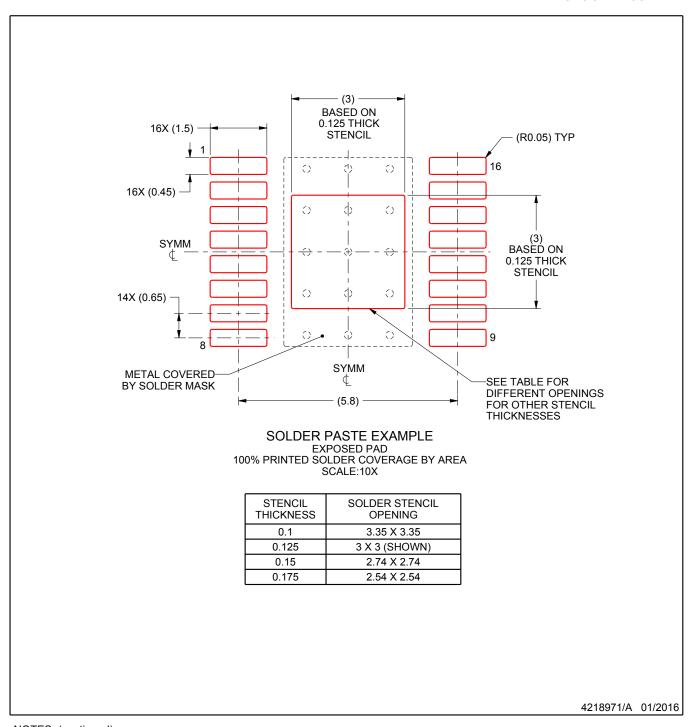

## **EXAMPLE STENCIL DESIGN**

## **PWP0016D**

## PowerPAD™ TSSOP - 1.2 mm max height

PLASTIC SMALL OUTLINE

NOTES: (continued)

www.ti.com

<sup>10.</sup> Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

11. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。