TPS2HCS10-Q1 JAJSOU6 - OCTOBER 2023

# TPS2HCS10-Q1 11mQ、車載用デュアル・チャネルの SPI 制御ハイサイド・ス イッチ、低静止電流オン・モード、I<sup>2</sup>t ワイヤ保護内蔵

### 1 特長

**TEXAS**

INSTRUMENTS

- 車載アプリケーション向けに AEC-Q100 認定済み

- 温度グレード 1:-40℃~125℃

- デバイス HBM ESD 分類レベル 2

- デバイス CDM ESD 分類レベル C5

- 35V の負荷ダンプへの耐性

- 機能安全準拠開発

- ASIL-B までの ISO 26262 システム設計を支援す る安全メカニズムに関するドキュメントを製品リリース 時に提供予定

- 25℃の FET で 11mΩの Rdson を標準値とするデュ アル・チャネルの SPI 制御スマート・ハイサイド・スイッ チ

- MCU を介さないワイヤ・ハーネス保護機能と SPI でプ ログラム可能なヒューズ曲線を内蔵 - 持続的な過負荷状態からの保護

- SPI でプログラム可能な可変過電流保護によりシステ

- ム・レベルの信頼性を向上

- 過電流保護スレッショルド:10~70 A

- 幅広い容量性入力 ECU の負荷電流ニーズに対応す る SPI で構成可能な容量性充電モード

- 低静止電流 / 低消費電力オン状態で常時オンの負荷 に電力を供給、MCU に対するウェーク信号によりウェ イクオン時の負荷電流を自動的に供給

- 堅牢な出力保護機能を内蔵:

- 熱保護機能を内蔵

- グランド短絡からの保護

- 逆電源電圧による FET の自動スイッチ・オンを含 むバッテリ逆接続からの保護

- バッテリおよびグランドの喪失時に自動シャットオフ

- 誘導性負荷の逆起電圧の発生を防止する出力クラ ンプを内蔵

- SPI によるデジタル・センス出力で以下を測定するよう に構成可能:

- 負荷電流 (内蔵 ADC による高精度の測定) – 出力または電源電圧、FET 温度

- SPI インターフェイスによる完全なフォルト診断と FLT ピンによるフォルト表示

- 開放負荷とバッテリ短絡の検出

## 2 アプリケーション

- 車載ゾーン ECU

- パワー・ディストリビューション・モジュール

- 車体制御モジュール

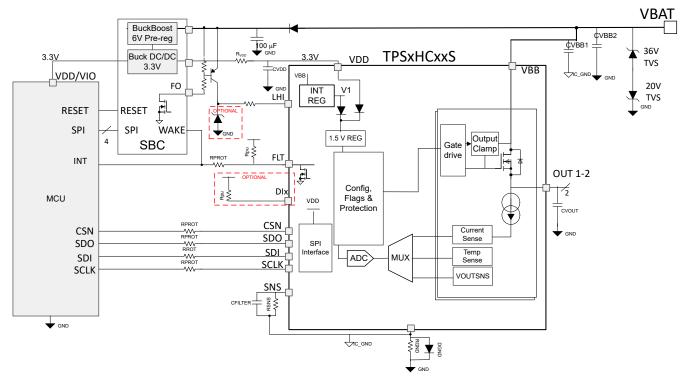

### 3 概要

TPS2HCS10-Q1 デバイスは、シリアル・ペリフェラル・イン ターフェイス (SPI) で制御されるデュアル・チャネルのスマ ート・ハイサイド・スイッチです。このデバイスには堅牢な保 護機能が内蔵されており、短絡や過負荷の状態から出力 ワイヤと負荷を確実に保護できます。このデバイスには、2 つの範囲のスレッショルドを SPI で構成可能な過電流保 護機能が搭載されています。これにより、大きな突入電流 を必要とする負荷をサポートする十分な柔軟性が得られる と同時に、保護機能も強化されます。さらに、このデバイス には持続的な過負荷状態下でスイッチをオフにするプロ グラム可能なヒューズ・プロファイル (電流と時間) が内蔵さ れており、MCU のオーバーヘッドが軽減されます。これら の2つの機能を組み合わせた完全な保護機能により、あ らゆる負荷プロファイルに対してワイヤ・ハーネスを最適化 できます。

このデバイスは、パワー・ディストリビューション・スイッチ・ アプリケーションの ECU 負荷用に、SPI で構成可能な容 量性充電モードをサポートしています。また、このデバイス には低静止電流オン状態もあり、この状態でのピーク電流 は最大 800mA、消費電流は約 10µA です。

TPS2HCS10-Q1 デバイスは SPI による高精度のデジタ ル電流センスも備えているため、負荷の診断も強化されま す。負荷電流、チャネル出力電圧、出力 FET 温度をシス テムの MCU に報告することで、スイッチや負荷の障害を 診断することができます。

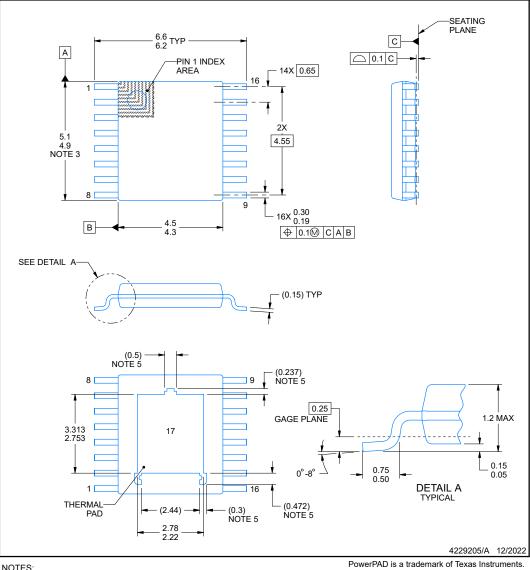

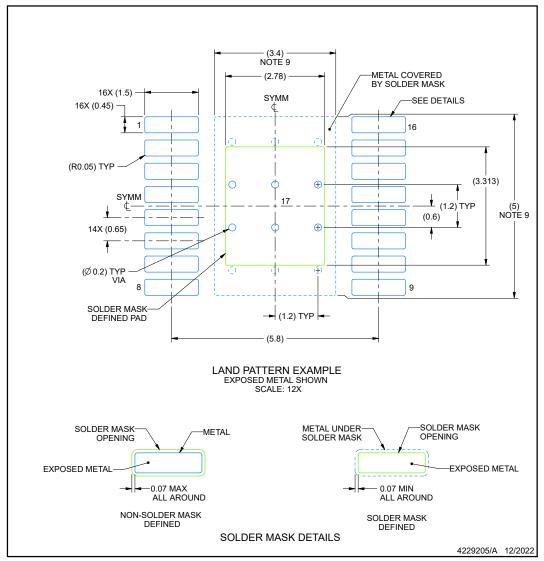

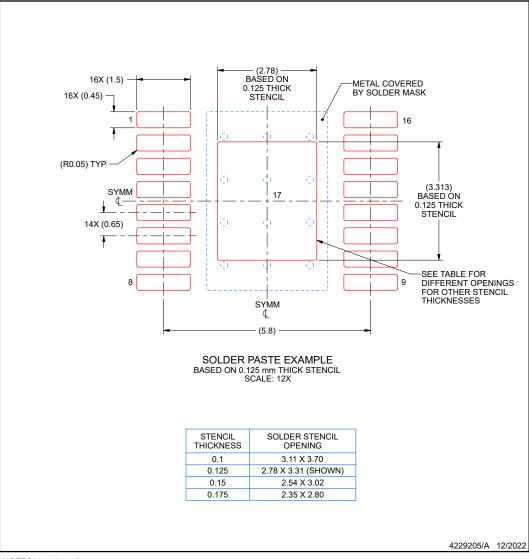

TPS2HCS10-Q1 は、PCB の占有面積を減らすことがで きる HTSSOP パッケージで供給されます。

パッケージ情報

|              | · · / / / / INTA     |                          |

|--------------|----------------------|--------------------------|

| 部品番号         | パッケージ <sup>(1)</sup> | パッケージ・サイズ <sup>(2)</sup> |

| TPS2HCS10-Q1 | PWP (HTSSOP、16)      | 5.0mm × 6.40mm           |

(1) 利用可能なすべてのパッケージについては、データシートの末尾 にある注文情報を参照してください。

(2) パッケージ・サイズ (長さ×幅) は公称値であり、該当する場合はピ ンも含まれます。

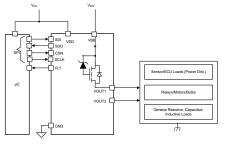

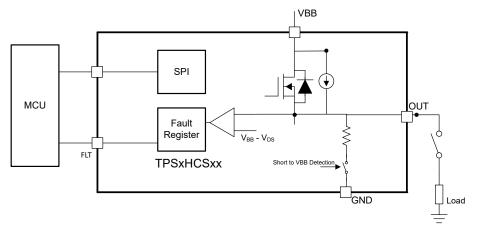

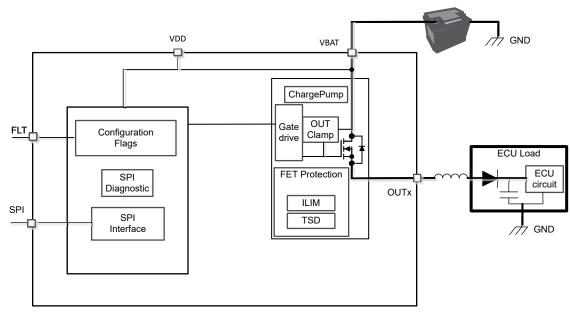

概略回路図

## **Table of Contents**

| 1 | 特長                                          | 1              |

|---|---------------------------------------------|----------------|

|   | アプリケーション                                    |                |

| 3 | 概要                                          | 1              |

|   | Revision History                            |                |

| 5 | Pin Configuration and Functions             | 3              |

|   | 5.1 Recommended Connections for Unused Pins |                |

| 6 | Specifications                              | <mark>5</mark> |

|   | 6.1 Absolute Maximum Ratings                | <mark>5</mark> |

|   | 6.2 ESD Ratings                             |                |

|   | 6.3 Recommended Operating Conditions        | 5              |

|   | 6.4 Thermal Information                     | <mark>6</mark> |

|   | 6.5 Electrical Characteristics              |                |

|   | 6.6 SPI Timing Requirements                 |                |

|   | 6.7 Switching Characteristics               |                |

| 7 | Parameter Measurement Information           | 11             |

| 8 | Detailed Description                        |                |

|   | 8.1 Overview                                |                |

|   | 8.2 Functional Block Diagram                | 13             |

|   |                                             |                |

| 8.3 Feature Description                 | 13 |

|-----------------------------------------|----|

| 8.4 Device Functional Modes             |    |

| 8.5 TPS2HC10S Registers                 |    |

| 9 Application and Implementation        |    |

| 9.1 Application Information             |    |

| 9.2 Typical Application                 |    |

| 9.3 Power Supply Recommendations        |    |

| 9.4 Layout                              | 69 |

| 10 Device and Documentation Support     |    |

| 10.1 Documentation Support              | 71 |

| 10.2ドキュメントの更新通知を受け取る方法                  | 71 |

| 10.3 サポート・リソース                          | 71 |

| 10.4 Trademarks                         | 71 |

| 10.5 静電気放電に関する注意事項                      | 71 |

| 10.6 用語集                                | 71 |

| 11 Mechanical, Packaging, and Orderable |    |

| Information                             | 71 |

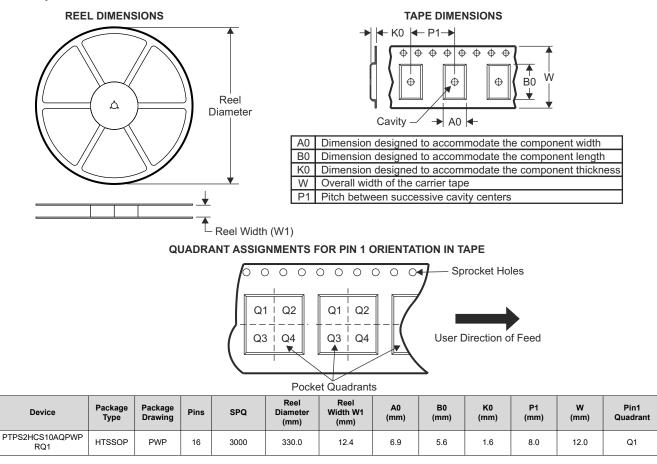

| 11.1 Tape and Reel Information          | 72 |

## 4 Revision History

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| DATE         | REVISION | NOTES           |

|--------------|----------|-----------------|

| October 2023 | *        | Initial Release |

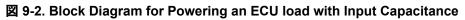

### **5** Pin Configuration and Functions

### 図 5-1. PWP Package, 16-Pin HTSSOP (Top View)

### 表 5-1. Pin Functions

| P           | IN                | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                    |  |  |

|-------------|-------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO.         | NAME              |                    | DESCRIPTION                                                                                                                                                                                                                                                    |  |  |

| 1           | GND               | —                  | Device ground.                                                                                                                                                                                                                                                 |  |  |

| 2           | SNS               | 0                  | Sense current output. Use a parallel RC network to the GND pin of the IC.                                                                                                                                                                                      |  |  |

| 3           | VDD               | Р                  | Logic supply input. Closely decouple to the GND pin of the IC with a ceramic 1-µF capacitor.                                                                                                                                                                   |  |  |

| 4           | DI                | I                  | Sets the output behavior in the LIMP HOME mode, if configured as such. The pin needs to be connected to MCU or other HI/LO source through a 10-k $\Omega$ resistor for protection and enabling the reverse polarity FET turn-on function.                      |  |  |

| 5           | LHI               | I                  | Externally enables the LIMP HOME mode.                                                                                                                                                                                                                         |  |  |

| 6, 7, 8     | VOUT1             | 0                  | Output of channel 1.                                                                                                                                                                                                                                           |  |  |

| 9,10, 11    | VOUT2             | 0                  | Output of channel 2.                                                                                                                                                                                                                                           |  |  |

| 12          | FLT ,WAKE_SI<br>G | 0                  | Fault output (active low), indicating faulton any (one or more) channel. Open drain, pull up with a 4.7-k $\Omega$ resistor to the VDD pin. Also functions as a wake signal to the MCU upon load current demand in Low Power Mode or the vehicle key-off mode. |  |  |

| 13          | SDI               | I                  | SPI device (secondary) data input.                                                                                                                                                                                                                             |  |  |

| 14          | 14 SDO O          |                    | SPI data output from the device. Internally pulled up to VDD.                                                                                                                                                                                                  |  |  |

| 15          | CS                | I                  | SPI interface chip select (active low). Internally pulled up to VDD.                                                                                                                                                                                           |  |  |

| 16          | SCLK              | I                  | SPI interface clock input to the device.                                                                                                                                                                                                                       |  |  |

| Exposed pad | VBB               | Р                  | Power supply input.                                                                                                                                                                                                                                            |  |  |

(1) I = input, O = output, P = power

TPS2HCS10-Q1 JAJSOU6 – OCTOBER 2023

### 5.1 Recommended Connections for Unused Pins

4 資料に関するフィードバック (ご意見やお問い合わせ) を送信 Product Folder Links: TPS2HCS10-Q1

### **6** Specifications

#### 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                       |                                               | MIN  | MAX                  | UNIT |

|-------------------------------------------------------|-----------------------------------------------|------|----------------------|------|

| Maximum continuous supply voltage, V <sub>VBB</sub>   |                                               |      | 28                   | V    |

| Load dump voltage                                     | ISO16750-2:2010(E)                            |      | 36                   | V    |

| Maximum transient voltage on VBB pin, (example during | ISO 7637 pulse 2a transient) V <sub>BBt</sub> |      | 54                   | V    |

| VOUT voltage                                          |                                               | -30  | V <sub>VS</sub> +0.3 | V    |

| Reverse polarity voltage, continuous on VBB pin       |                                               | -18  |                      | V    |

| Low voltage supply pin voltage, V <sub>DD</sub>       |                                               | -0.3 | 5.5                  | V    |

| Digital input pin voltages, V <sub>DIG</sub>          | SDI, SDO, SCLK, CS                            | -0.3 | 5.5                  | V    |

| nse pin voltage, V <sub>SNS</sub>                     |                                               | -0.3 | 5.5                  | V    |

| FLT pin voltage, V <sub>FLT</sub>                     |                                               | -0.3 | 5.5                  | V    |

| Limp home activation pin voltage, V <sub>LHI</sub>    |                                               |      | V <sub>BB</sub>      | V    |

| Limp home direct input pin voltages, V <sub>DI</sub>  |                                               | -0.3 | 5.5                  | V    |

| Reverse ground current, I <sub>GND</sub>              | V <sub>BB</sub> < 0 V                         |      | -50                  | mA   |

| Maximum junction temperature, T <sub>J</sub>          |                                               |      | 150                  | °C   |

| Storage temperature, T <sub>stg</sub>                 |                                               | -65  | 150                  | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

### 6.2 ESD Ratings

|                    |                                           |                                                                                     |                                  | VALUE | UNIT |

|--------------------|-------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------|-------|------|

|                    |                                           | Human-body model (HBM), per AEC<br>Q100-002 Classification Level H2                 | All pins including VBB and VOUTx | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic<br>discharge <sup>(1)</sup> | Human-body model (HBM), per AEC<br>Q100-002 Classification Level H3A <sup>(2)</sup> | VBB and VOUTx                    | ±4000 | V    |

|                    |                                           | Charged-device model (CDM), per AEC Q100-011<br>Classification Level C5             | All pins                         | ±750  |      |

(1) AEC-Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specifications.

(2) ESD strikes are with reference from the pin mentioned to GND

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                     |                                       |                                                                                                | MIN  | MAX             | UNIT |

|---------------------|---------------------------------------|------------------------------------------------------------------------------------------------|------|-----------------|------|

| V <sub>BB_NOM</sub> | Nominal supply voltage                |                                                                                                | 6    | 18              | V    |

| V <sub>BB_EXT</sub> | Extended supply voltage               | See the conditions in section 9.2, power<br>supply recommendations, operating<br>voltage range | 3    | 28              | V    |

| V <sub>DD</sub>     | Low voltage supply voltage            | Low voltage supply voltage                                                                     |      | 5.5             | V    |

| V <sub>DIG</sub>    | All digital input pin voltage         |                                                                                                | -0.3 | 5.5             | V    |

| V <sub>FLT</sub>    | FLT pin voltage                       | FLT pin voltage                                                                                |      | 5.5             | V    |

| V <sub>LHI</sub>    | Limp home activation pin voltage, LHI |                                                                                                |      | V <sub>BB</sub> | V    |

| V <sub>DI</sub>     | Limp home direct pin input voltag     | je, DI                                                                                         | -0.3 | 5.5             | V    |

### 6.3 Recommended Operating Conditions (続き)

over operating free-air temperature range (unless otherwise noted)

|                |                                | MIN | MAX | UNIT |

|----------------|--------------------------------|-----|-----|------|

| T <sub>A</sub> | Operating free-air temperature | -40 | 125 | °C   |

### 6.4 Thermal Information

|                       |                                              | TPS2HCS10-Q1 |      |

|-----------------------|----------------------------------------------|--------------|------|

|                       | THERMAL METRIC <sup>(1)</sup> <sup>(2)</sup> | PWP          | UNIT |

|                       |                                              | 16 PINS      | _    |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 33.0         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 26.2         | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 9.4          | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 3.0          | °C/W |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 9.3          | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.1          | °C/W |

(1) For more information about traditional and new thermal metrics, see the https://www.ti.com/lit/an/spra953c/spra953c.pdf application report.

(2) The thermal parameters are based on a 4-layer PCB according to the JESD51-5 and JESD51-7 standards.

### 6.5 Electrical Characteristics

$V_{BB}$  = 6 V to 18 V,  $V_{DD}$  = 3.0 V to 5.5 V,  $T_{J}$  = -40°C to 150°C (unless otherwise noted)

|                              | PARAMETER                                                       | TEST CO                                                                                                                                                                                  | NDITIONS                                                                                                                                                                                 | MIN  | TYP  | MAX  | UNIT |

|------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| INPUT VOL                    | TAGE AND CURRENT                                                | 1                                                                                                                                                                                        |                                                                                                                                                                                          |      |      |      |      |

| V <sub>Clamp</sub>           | VDS clamp voltage                                               | FET current = 10 mA VBB > 28 V                                                                                                                                                           | T <sub>J</sub> = 25°C to 150°C                                                                                                                                                           | 35   | 40   | 45   | V    |

| V <sub>Clamp</sub>           | VDS clamp voltage                                               | FET current = 10 mA 12 V <<br>VBB < 28 V                                                                                                                                                 | $T_J = -40^{\circ}C$ to $150^{\circ}C$                                                                                                                                                   | 30   | 34   | 38   | V    |

| V <sub>Clamp</sub>           | VDS clamp voltage                                               | FET current = 10 mA VBB = 3 V                                                                                                                                                            | $T_J = -40^{\circ}C$ to $150^{\circ}C$                                                                                                                                                   | 27.5 |      | 36.5 | V    |

| V <sub>VBB_UVLOR</sub>       | V <sub>BB</sub> undervoltage lockout<br>rising                  | Measured with respect to<br>the GND pin of the device,<br>FETs can turn-on above this<br>level, full switch functionality<br>and OCP and TSD<br>protection. Diagnostics only<br>at > 6 V | Measured with respect to<br>the GND pin of the device,<br>FETs can turn-on above this<br>level, full switch functionality<br>and OCP and TSD<br>protection. Diagnostics only<br>at > 6 V | 3.0  | 3.5  | 4.0  | V    |

| V <sub>VBB_UVLOF</sub>       | V <sub>BB</sub> undervoltage lockout<br>falling                 | Measured with respect to<br>the GND pin of the device,<br>FETs turn-off below this<br>level.                                                                                             | Measured with respect to<br>the GND pin of the device,<br>FETs turn-off below this<br>level.                                                                                             | 2.6  | 2.8  | 3.0  | V    |

| V <sub>BB_UV_WR</sub><br>n_r | VBB voltage UV_WRN bit is set (rising threshold)                | Measured with respect to the undervoltage at which diagno                                                                                                                                |                                                                                                                                                                                          |      | 4.9  |      | V    |

| V <sub>bb_uv_wr</sub><br>n_f | V <sub>BB</sub> undervoltage at which diagnostics is turned OFF | Measured with respect to the<br>undervoltage at which diagno<br>(turned OFF). Overcurrent an<br>available till VBB_UVLO                                                                  | ostics are no longer available                                                                                                                                                           |      | 4.5  |      | V    |

| V <sub>VDD_UVLOF</sub>       | V <sub>VDD</sub> undervoltage lockout falling                   | SPI communication is lost                                                                                                                                                                |                                                                                                                                                                                          | 1.95 |      | 2.07 | V    |

| V <sub>VDD_UVLOR</sub>       | V <sub>VDD</sub> undervoltage lockout rising                    | Measured with respect to the                                                                                                                                                             | GND pin of the device                                                                                                                                                                    | 2.02 |      | 2.2  | V    |

| V <sub>VDD_UVLOH</sub>       | V <sub>VDD</sub> undervoltage lockout<br>hysteresis             | V <sub>UVLOR</sub> – V <sub>UVLOF</sub>                                                                                                                                                  |                                                                                                                                                                                          |      | 0.09 |      | V    |

Copyright © 2023 Texas Instruments Incorporated

### 6.5 Electrical Characteristics (続き)

$V_{BB}$  = 6 V to 18 V,  $V_{DD}$  = 3.0 V to 5.5 V,  $T_J$  = -40°C to 150°C (unless otherwise noted)

|                                | PARAMETER                                                                                                           | TEST CO                                                                                             | NDITIONS                                      | MIN   | TYP  | MAX   | UNIT |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------|-------|------|-------|------|

|                                | Continuous load current, per                                                                                        | All channels enabled, T <sub>AMB</sub> =                                                            | 85°C                                          |       | 7    |       | А    |

| IL <sub>NOM</sub>              | channel                                                                                                             | One channel enabled, T <sub>AMB</sub> =                                                             | = 85°C                                        |       | 12   |       | Α    |

| I <sub>SLEEP,VBB</sub>         | Sleep current (total device<br>leakage including all<br>MOSFET channels)                                            | $V_{BB} \le 18 \text{ V}$ , device in SLEEP<br>mode, $V_{OUT} = 0 \text{ V}$                        | T <sub>J</sub> = 25°C                         |       |      | 0.3   | μA   |

| I <sub>SLEEP,VBB</sub>         | Sleep current (total device<br>leakage including all<br>MOSFET channels)                                            | $V_{BB} \le 18 \text{ V}$ , device in SLEEP mode, $V_{OUT} = 0 \text{ V}$                           | T <sub>J</sub> = 85°C                         |       |      | 1.8   | μA   |

| OUT(OFF)                       | Output leakage current (per<br>channel) from the FET,<br>ACTIVE mode                                                | V <sub>BB</sub> ≤ 18 V, V <sub>OUT</sub> = 0<br>FET off, ACTIVE mode                                | T <sub>J</sub> = -40 to 125°C                 |       |      | 12    | μA   |

| I <sub>DD</sub>                | Active State VDD quiescent<br>current, SCLK off, ACTIVE<br>state,                                                   | $V < V_{BB} \le 18 \text{ V}, \text{ V}_{DD} = 5.5 \text{ V}$                                       |                                               |       |      | 1.5   | mA   |

| I <sub>DD</sub>                | Active State VDD quiescent current, SCLK off, ACTIVE state                                                          | 6 V < V <sub>BB</sub> ≤ 18 V, V <sub>DD</sub> = 3.0 V                                               | I                                             |       |      | 60    | μA   |

| IDDQ                           | Active State VDD quiescent<br>current, SCLK ON, 10 MHz,<br>ACTIVE state                                             | 6 V < V <sub>BB</sub> ≤ 18 V, V <sub>DD</sub> = 5.5 \                                               | I                                             |       |      | 2     | mA   |

| V <sub>BB</sub> I <sub>Q</sub> | V <sub>BB</sub> quiescent current,<br>SCLK off, all diagnostics<br>disabled,(OL_OFF, OL_ON,<br>SHRT_VS, ISNS, ADC)  | V <sub>BB</sub> ≤ 18 V, V <sub>DD</sub> = 5.5 V<br>All channels enabled, I <sub>OUTx</sub> = 0 A    |                                               |       | 2.35 | 2.75  | mA   |

| V <sub>BB</sub> I <sub>Q</sub> | V <sub>BB</sub> quiescent current,<br>SCLK off, all diagnostics<br>disabled, (OL_OFF, OL_ON,<br>SHRT_VS, ISNS, ADC) | V <sub>BB</sub> ≤ 18 V, V <sub>DD</sub> = 3.0 V<br>All channels enabled, I <sub>OUTx</sub> = 0 A    |                                               |       | 3.6  | 4.5   | mA   |

| V <sub>BB</sub> I <sub>Q</sub> | V <sub>BB</sub> quiescent current,<br>SCLK off, all diagnostics<br>(ISNS, ADC) enabled                              | $V_{BB} \le 18 \text{ V}, V_{DD} = 3.0 \text{ V}$<br>All channels enabled, $I_{OUTx} = 0 \text{ A}$ |                                               |       | 4.9  | 6     | mA   |

| RON CHAP                       | RACTERISTICS                                                                                                        | I                                                                                                   |                                               |       |      |       |      |

| R <sub>ON</sub>                | On-resistance<br>(Includes MOSFET and<br>package)                                                                   | $6 V \le V_{BB} \le 28 V$ , $I_{OUTx} = 1$<br>A                                                     | T <sub>J</sub> = 25°C                         |       | 11.3 |       | mΩ   |

| R <sub>ON</sub>                | On-resistance<br>(Includes MOSFET and<br>package)                                                                   | 6 V ≤ V <sub>BB</sub> ≤ 28 V, I <sub>OUTx</sub> = 1<br>A                                            | T <sub>J</sub> = 150°C                        |       |      | 22    | mΩ   |

| <b>D</b>                       | On-resistance during                                                                                                |                                                                                                     | T <sub>J</sub> = 25°C                         |       | 10   |       | mΩ   |

| R <sub>ON(REV)</sub>           | reverse polarity                                                                                                    | $-18 \text{ V} \le \text{V}_{\text{BB}} \le -7 \text{ V}$                                           | T <sub>J</sub> = 150°C                        |       |      | 25    | mΩ   |

| CURRENT                        | SENSE CHARACTERISTICS                                                                                               | 1                                                                                                   | 1                                             | I     |      |       |      |

| K <sub>SNS</sub>               | Current sense ratio                                                                                                 | I <sub>OUT</sub> = 1.0 A,<br>OL_ON_EN_CHx = 0                                                       | I <sub>OUT</sub> = 1.0 A,<br>OL_ON_EN_CHx = 0 |       | 5000 |       |      |

| K <sub>SNS</sub>               | Current sense ratio                                                                                                 | I <sub>OUT</sub> = 50 mA,<br>OL_ON_EN_CHx = 1                                                       | I <sub>OUT</sub> = 50 mA,<br>OL_ON_EN_CHx = 1 |       | 1200 |       |      |

| I <sub>SNSI</sub>              | Current sense current                                                                                               | Channel current sense<br>diagnostic ADC enabled,<br>OL_ON_EN_CHx = 0                                | I <sub>OUT</sub> = 10 A (±4% error)           | 1.92  | 2.00 | 2.08  | mA   |

| I <sub>SNSI</sub>              | Current sense current                                                                                               | Channel current sense<br>diagnostic ADC enabled,<br>OL_ON_EN_CHx = 0                                | I <sub>OUT</sub> = 2 A (±4% error)            | 0.385 | 0.40 | 0.41  | mA   |

| I <sub>SNSI</sub>              | Current sense current                                                                                               | Channel current sense<br>diagnostic ADC enabled,<br>OL_ON_EN_CHx = 0                                | I <sub>OUT</sub> = 500 mA (±6% error)         | 0.096 | 0.10 | 0.106 | mA   |

Copyright © 2023 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信 7

Product Folder Links: TPS2HCS10-Q1

### 6.5 Electrical Characteristics (続き)

$V_{BB}$  = 6 V to 18 V,  $V_{DD}$  = 3.0 V to 5.5 V,  $T_J$  = -40°C to 150°C (unless otherwise noted)

|                                                | PARAMETER                                                            | TEST CO                                                              | NDITIONS                                                          | MIN   | TYP   | MAX   | UNIT |

|------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------|-------|-------|-------|------|

| I <sub>SNSI</sub>                              | Current sense current                                                | Channel current sense<br>diagnostic ADC enabled,<br>OL_ON_EN_CHx = 1 | I <sub>OUT</sub> = 25 mA (15 % error)                             | 0.018 | 0.021 | 0.024 | mA   |

| ADC CHAR                                       | ACTERISTICS                                                          |                                                                      |                                                                   |       |       | 1     |      |

| V <sub>ADCEFfHI</sub>                          | ADC reference voltage                                                |                                                                      |                                                                   | 2.76  | 2.8   | 2.84  | V    |

| Isample                                        | Current sense sampling time                                          | Including mux timing and AD                                          | C conversion time                                                 | 50    |       |       | μs   |

| I <sub>ADC</sub>                               | ADC current consumption                                              |                                                                      |                                                                   |       |       | 0.5   | mA   |

| SNS CHAR                                       | ACTERISTICS                                                          | I                                                                    |                                                                   |       |       |       |      |

| ADC<br>VOUT <sub>SNS</sub> _<br><sup>CHx</sup> | ADC VOUT <sub>SNS</sub> output code                                  | VOUT_CHx = 13.5 V                                                    | Includes buffer gain                                              |       | 459   |       |      |

| OVERCURF                                       | RENT PROTECTION CHARC                                                | TERISTICS                                                            |                                                                   |       |       |       |      |

| I <sub>OCth</sub>                              | Overcurrent protection<br>threshold, immediate<br>shutdown mode      | T <sub>J</sub> = –40°C to 125°C                                      | IOC setting = 62.5 A, VBB =<br>18 V dl/dt = 2 A / μs              |       | 65    |       | A    |

| I <sub>CL_ENPS</sub>                           | Peak current enabling into<br>permanent short, immediate<br>shutdown | T <sub>J</sub> = –40°C to 125°C                                      | OCP setting = 62.5 A, Test<br>setup per AEC Q100-12               |       |       | 70    | A    |

| CAP CHRG                                       | CURRENT LIMITATION                                                   |                                                                      | · · · · · · · · · · · · · · · · · · ·                             |       |       |       |      |

| I <sub>CL_Reg</sub>                            | Regulation mode current                                              | T <sub>J</sub> = -40°C to 125°C dl/dt <<br>0.01 A/ms                 | SPI Setting<br>(ILIM_CHx_SET) of 10 A,<br>I <sub>ILIM</sub> = 2 A | 1.70  | 2.15  | 2.5   | A    |

| I <sub>CL_Reg</sub>                            | Regulation mode current                                              | T <sub>J</sub> = -40°C to 125°C dl/dt <<br>0.01 A/ms                 | SPI Setting<br>(ILIM_CHx_SET) of 20 A,<br>I <sub>ILIM</sub> = 4 A | 3.35  | 3.8   | 4.55  | А    |

| CAPACITIV                                      | E CHARGING                                                           |                                                                      | · · · · · · · · · · · · · · · · · · ·                             |       |       |       |      |

| T <sub>DELAY_RAN</sub><br>GE                   | Range of Tdelay settings                                             | SPI settting, Pulsed current n                                       | node                                                              | 1     |       | 100   | ms   |

| dV_dt <sub>RANG</sub><br>E                     | Range of dV/dt during<br>Tdelay                                      | SPI settting, dV/dt mode                                             | VBB = 16V, Capacitance =<br>1 mF                                  | 0.33  |       | 1.6   | V/ms |

| FAULT CHA                                      | RACTERISTICS                                                         |                                                                      |                                                                   |       |       |       |      |

|                                                |                                                                      |                                                                      | OL_PULLUP_STR=00                                                  | 23    | 25    | 28    | μA   |

|                                                | Off state open-load (OL) detection internal pull-up                  | Switch disabled,<br>OL_OFF_EN_CHx =                                  | OL_PULLUP_STR=01                                                  | 52    | 57    | 63    | μA   |

| I <sub>OL_OFF</sub>                            | current                                                              | enabled                                                              | OL_PULLUP_STR=10                                                  | 112   | 121   | 130   | μA   |

|                                                |                                                                      |                                                                      | OL_PULLUP_STR=11                                                  | 235   | 256   | 265   | μA   |

| R <sub>SHRT_VBB</sub>                          | Off state short to VBB<br>detection pulldown<br>resistance           | Channel disabled, off-state sl<br>enabled                            | nort_VBB diagnostics                                              | 6     | 7.5   | 9     | kΩ   |

| V <sub>OL_OFF_TH</sub>                         | Off state Open-load (OL) detection voltage                           | Channel Disabled, off-state o enabled, V <sub>OUTx</sub>             | pen load diagnostics                                              | 1.9   | 2.5   | 2.95  | V    |

| T <sub>ABS</sub>                               | Thermal shutdown                                                     |                                                                      |                                                                   | 155   | 180   | 205   | °C   |

| T <sub>OTW</sub>                               | Thermal shutdown warning                                             |                                                                      |                                                                   | 130   | 150   | 170   | °C   |

| T <sub>REL</sub>                               | Relative thermal shutdown temperature                                |                                                                      |                                                                   |       | 60    |       | °C   |

| T <sub>HYS</sub>                               | Thermal shutdown<br>hysteresis                                       |                                                                      |                                                                   | 20    | 25    | 30    | °C   |

| PWM CHAF                                       | ACTERISTICS                                                          |                                                                      |                                                                   |       |       |       |      |

| PWM <sub>FREQ</sub>                            | PWM Frequency                                                        | PWM_EN = 1                                                           | PWM_FREQ_CHx = 000                                                | 0.80  | 0.86  | 0.93  | Hz   |

| PWM <sub>FREQ</sub>                            | PWM Frequency                                                        | PWM EN = 1                                                           | PWM FREQ CHx = 111                                                | 1637  | 1770  | 1903  | Hz   |

### 6.5 Electrical Characteristics (続き)

$V_{BB}$  = 6 V to 18 V,  $V_{DD}$  = 3.0 V to 5.5 V,  $T_J$  = -40°C to 150°C (unless otherwise noted)

|                       | PARAMETER                                     | TEST C                                 | ONDITIONS                                                       | MIN                       | TYP | MAX                       | UNIT |

|-----------------------|-----------------------------------------------|----------------------------------------|-----------------------------------------------------------------|---------------------------|-----|---------------------------|------|

| LOW POW               | ER MODE CHARACTERISTI                         | cs                                     |                                                                 |                           |     |                           |      |

| R <sub>DSON</sub>     | RDSON Low Power Mode<br>(LPM)                 | $T_J = -40^{\circ}C$ to $125^{\circ}C$ | $T_J = -40^{\circ}C$ to 125°C                                   |                           | 60  |                           | mΩ   |

| ILOAD <sub>EXIT</sub> | Load current when the channel exits LPM       | Exit Threshold Setting = 00            | Exit Threshold Setting = 00 (600 mA) Current ramp at 1<br>nA/μs |                           | 600 | 675                       | mA   |

| IVDDLPM               | IVDD in LPM mode both channels ON lout = 0    | VDD = 5.0 V                            | $T_J = -40^{\circ}C$ to $85^{\circ}C$                           |                           | 14  |                           | μA   |

| IVBBLPM               | IVBB per channel, both channels OFF, lout = 0 | VDD = 5.0 V                            | $T_J = -40^{\circ}C \text{ to } 85^{\circ}C$                    |                           | 2.5 |                           | μA   |

| IVBBLPM               | IVBB per channel, one channel ON, lout = 0    | VDD = 5.0 V                            | $T_J = -40^{\circ}C$ to $85^{\circ}C$                           |                           | 3.6 |                           | μA   |

| IVBBLPM               | IVBB per channel, both channels ON, lout = 0  | VDD = 5.0 V                            | $T_J = -40^{\circ}C$ to $85^{\circ}C$                           |                           | 4.5 |                           | μA   |

| DIGITAL IN            | PUT PIN CHARACTERISTIC                        |                                        |                                                                 |                           |     | 1                         |      |

| V <sub>IH, DIG</sub>  | Digital pin Input voltage<br>high-level       | 3.0 V ≤ VDD ≤ 5.5 V                    |                                                                 | 0.7 ×<br>V <sub>VDD</sub> |     |                           | V    |

| V <sub>IL, DIG</sub>  | Digital pin Input voltage<br>high-level       | 3.0 V ≤ VDD ≤ 5.5 V                    |                                                                 |                           |     | 0.3 ×<br>V <sub>VDD</sub> | V    |

| R <sub>DIGx</sub>     | Internal pulldown resistor                    |                                        |                                                                 | 0.7                       | 1.0 | 1.8                       | MΩ   |

| I <sub>IH, DIG</sub>  | Input current high-level                      | V <sub>DIG</sub> = 5 V                 |                                                                 |                           | 5   |                           | μA   |

| DIGITAL O             | UTPUT PIN CHARACTERIST                        | ICS                                    |                                                                 |                           |     | 1                         |      |

| V <sub>OH_SDO</sub>   | Output logic high voltage drop                | SDO pin current = 2 mA                 |                                                                 |                           |     | 0.2                       | V    |

| V <sub>OL_FLT</sub>   | Output logic high voltage drop                | FLT pin current = 4mA                  |                                                                 |                           |     | 0.5                       | V    |

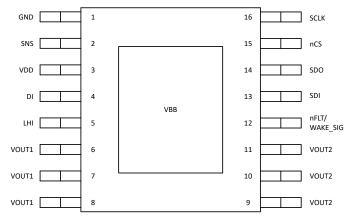

### 6.6 SPI Timing Requirements

Over operating junction temperature  $T_J = -40^{\circ}C$  to  $125^{\circ}C$

|                     | PARAMETER                                                                           | TEST CONDITIONS                                              | MIN | NOM | MAX | UNIT |

|---------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------|-----|-----|-----|------|

| fspi                | SPI clock (SCLK) frequency                                                          | $C_{SDO}$ = 30 pF, IO protection<br>resistor 0.47 k $\Omega$ |     |     | 8   | MHz  |

| t <sub>high</sub>   | High time: SCLK logic high-time duration                                            |                                                              | 45  |     |     | ns   |

| t <sub>low</sub>    | Low time: SCLK logic low-time duration                                              |                                                              | 45  |     |     | ns   |

| t <sub>sucs</sub>   | CS setup time: time delay between falling edge of CS and rising edge of SCLK        |                                                              | 45  |     |     | ns   |

| t <sub>su_SDI</sub> | SDI setup time: setup time of SDI before the falling edge of SCLK                   |                                                              | 15  |     |     | ns   |

| t <sub>h_SDI</sub>  | SDI hold time: hold time of SDI before the falling edge of SCLK                     |                                                              | 30  |     |     | ns   |

| t <sub>d_SDO</sub>  | Delay time: time delay from rising edge of SCLK to data                             | valid at SDO                                                 |     |     | 30  | ns   |

| t <sub>hcs</sub>    | Hold time: time between the falling edge of SCLK and rising edge of $\overline{CS}$ |                                                              | 45  |     |     | ns   |

| t <sub>dis_cs</sub> | cs CS disable time, CS high to SDO high impedance                                   |                                                              |     | 10  |     | ns   |

| t <sub>hics</sub>   | SPI transfer inactive time (time between two transfers) of                          | luring which CS must remain high                             | 500 |     |     | ns   |

### 6.7 Switching Characteristics

Over operating junction temperatures,  $T_J = -40^{\circ}C$  to 150°C (unless otherwise noted)

|                  | PARAMETER | TEST CONDITIONS                                                                                  | MIN | ТҮР | МАХ | UNIT |

|------------------|-----------|--------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>DR1</sub> |           | $V_{S}$ = 13.5 V, $R_{L}$ = 2 $\Omega,$ 50% of $\overline{CS}$ to 10% of VOUT, default slew rate | 8   | 30  | 45  | μs   |

Copyright © 2023 Texas Instruments Incorporated

### 6.7 Switching Characteristics (続き)

Over operating junction temperatures,  $T_J = -40^{\circ}C$  to  $150^{\circ}C$  (unless otherwise noted)

|                       | PARAMETER                      | TEST CONDITIONS                                                                                                                          | MIN | TYP  | MAX | UNIT |

|-----------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| t <sub>DF1</sub>      | Channel turnoff delay time     | $V_S$ = 13.5 V, $R_L$ = 2 $\Omega$ 50% of CS/EN to 90% of VOUT default slew rate                                                         | 10  | 20   | 30  | μs   |

|                       |                                | $      V_{BB} = 13.5 \text{ V}, 20\% \text{ to } 80\% \text{ of } V_{OUT}, \\ R_L = 2 \Omega \text{ Slew Rate Setting (SLRT_CHx)} = 11 $ |     | 0.55 |     | V/µs |

| SR <sub>R</sub>       | VOUT rising slew rate          | $      V_{BB} = 13.5 \text{ V}, 20\% \text{ to } 80\% \text{ of } V_{OUT}, \\ R_L = 2 \Omega \text{ Slew Rate Setting (SLRT_CHx)} = 10 $ |     | 0.45 |     | V/µs |

|                       |                                | $      V_{BB} = 13.5 \text{ V}, 20\% \text{ to } 80\% \text{ of } V_{OUT}, \\ R_L = 2 \Omega \text{ Slew Rate Setting (SLRT_CHx)} = 01 $ |     | 0.34 |     | V/µs |

|                       |                                | $      V_{BB} = 13.5 \text{ V}, 20\% \text{ to } 80\% \text{ of } V_{OUT}, \\ R_L = 2 \Omega \text{ Slew Rate Setting (SLRT_CHx)} = 00 $ |     | 0.25 |     | V/µs |

|                       |                                | $V_{BB}$ = 13.5 V, 80% to 20% of $V_{OUT}$ ,<br>R <sub>L</sub> = 2 $\Omega$ Slew Rate Setting (SLRT_CHx) = 11                            |     | 0.56 |     | V/µs |

| SR <sub>F</sub>       | VOUT falling slew rate         | $      V_{BB} = 13.5 \text{ V}, 80\% \text{ to } 20\% \text{ of } V_{OUT}, \\ R_L = 2 \Omega \text{ Slew Rate Setting (SLRT_CHx)} = 10 $ |     | 0.42 |     | V/µs |

|                       |                                | $      V_{BB} = 13.5 \text{ V}, 80\% \text{ to } 20\% \text{ of } V_{OUT}, \\ R_L = 2 \Omega \text{ Slew Rate Setting (SLRT_CHx)} = 01 $ |     | 0.30 |     | V/µs |

|                       |                                | $      V_{BB} = 13.5 \text{ V}, 80\% \text{ to } 20\% \text{ of } V_{OUT}, \\ R_L = 2 \Omega \text{ Slew Rate Setting (SLRT_CHx)} = 00 $ |     | 0.21 |     | V/µs |

| ON                    | Channel turnon time            | SLRT_CHx=10 (default)                                                                                                                    | 40  | 53   | 70  | μs   |

| OFF                   | Channel turnoff time           | SLRT_CHx=10 (default)                                                                                                                    | 30  | 36   | 50  | μs   |

|                       | Turnon and off matching        | 1 ms ON time switch enable pulse, $V_{BB}$ = 13.5 V, $R_L$ = 2 $\Omega$                                                                  | -10 |      | 30  | μs   |

| ON - t <sub>OFF</sub> |                                | 200-μs OFF time switch enable pulse, $V_{BB}$ = 13.5 V, $R_L$ = 2 Ω, frequency = 1 kHz                                                   | -20 |      | 20  | μs   |

|                       |                                | 200- $\mu$ s ON time switch enable pulse, V <sub>S</sub> = 13.5 V, R <sub>L</sub> = 2 $\Omega$ , frequency = 1 kHz                       | -15 | -4   | 5   | μs   |

|                       |                                | $V_S$ = 13.5 V, $R_L$ = 2 $\Omega$ , 1 ms pulse - VOUT from 0 to VS Slew Rate Setting (SLRT_CHx) = 11                                    |     | 0.4  |     | mJ   |

| _                     | Switching energy losses during | $V_{S}$ = 13.5 V, $R_{L}$ = 2 $\Omega$ , 1 ms pulse - VOUT from<br>0 to VS Slew Rate Setting (SLRT_CHx) = 10                             |     | 0.5  |     | mJ   |

| Eon                   | turnon                         | $V_S$ = 13.5 V, $R_L$ = 2 $\Omega$ , 1 ms pulse - VOUT from<br>0 to VS Slew Rate Setting (SLRT_CHx) = 01                                 |     | 0.65 |     | mJ   |

|                       |                                | $V_{S}$ = 13.5 V, $R_{L}$ = 2 $\Omega$ , 1 ms pulse - VOUT from<br>0 to VS Slew Rate Setting (SLRT_CHx) = 00                             |     | 0.9  |     | mJ   |

|                       |                                | $V_{S}$ = 13.5 V, $R_{L}$ = 2 $\Omega$ , 1 ms pulse - VOUT from VS to 0 Slew Rate Setting (SLRT_CHx) = 11                                |     | 0.37 |     | mJ   |

| =                     | Switching energy losses during | $V_{S}$ = 13.5 V, $R_{L}$ = 2 $\Omega$ , 1 ms pulse - VOUT from VS to 0 Slew Rate Setting (SLRT_CHx) = 10                                |     | 0.48 |     | mJ   |

| OFF                   | turnoff                        | $V_{S}$ = 13.5 V, $R_{L}$ = 2 $\Omega$ , 1 ms pulse - VOUT from VS to 0 Slew Rate Setting (SLRT_CHx) = 01                                |     | 0.68 |     | mJ   |

|                       |                                | $V_{S}$ = 13.5 V, $R_{L}$ = 2 $\Omega$ , 1 ms pulse - VOUT from VS to 0 Slew Rate Setting (SLRT_CHx) = 00                                |     | 0.9  |     | mJ   |

### **7 Parameter Measurement Information**

### 8 Detailed Description

### 8.1 Overview

The TPS2HCS10-Q1 device is a dual-channel smart high-side switch intended for use with 12-V automotive batteries. The TPS2HCS10-Q1 device integrates SPI control and configuration as well digital readout with an ADC of key device and load diagnostics. The device incorporates all of the specific features needed for a power distribution switch as well as the traditional protective and diganostic functions seen in high side switches for actuator drive applications.

Diagnostics features include a digital current, output voltage and FET temperature sense output that can be read over the SPI serial interface. The high-accuracy load current sense allows for diagnostics of complex loads. The output voltage sense and FET temperature sense fearures in the device enables diagnosis of the switch and load failures.

This device includes protection through thermal shutdown, overcurrent protection, transient withstand, and reverse battery operation. In addition, the device also includes an SPI-configurable wire-harness protection function through a defined fuse or tme-current curve. The protection works in conjunction with an immediate switch-off overcurrent protection with an SPI-configurable threshold to fully protect against overload and short circuit faults.

The TPS2HCS10-Q1device also integrates a low quiescent current mode where the device can provide currents in the 100s of mA range while consuming only micro-amps of current. The device automatically switches to the high-current mode on an increase in load current and provide a wake signal to the MCU. Further, the device includes a capacitive charging mode that reduces the peak current load on the supply. Together, the two features support power distribution switch to off-board ECU applications.

For more details on the diagnosis, power distribution and protection features, refer to the *Feature Description* and *Application Information* sections of the document.

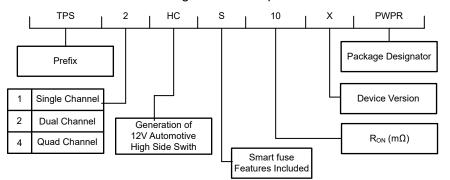

The TPS2HCS10-Q1 is one device in a family of TI high side switches. For each device, the part number indicates elements of the device behavior.  $\boxtimes$  8-1 gives an example of the device nomenclature.

図 8-1. Naming Convention

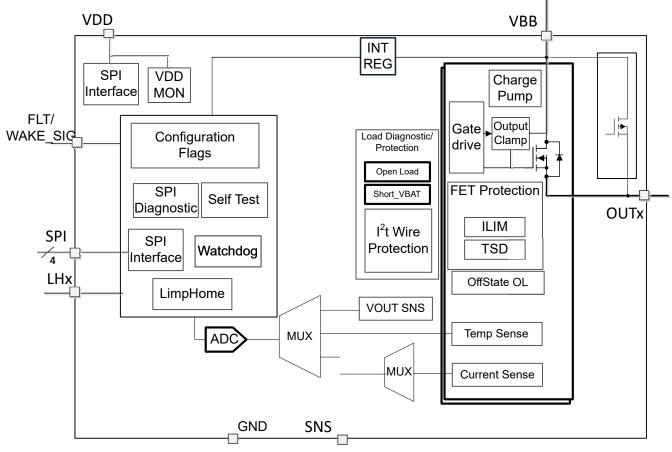

### 8.2 Functional Block Diagram

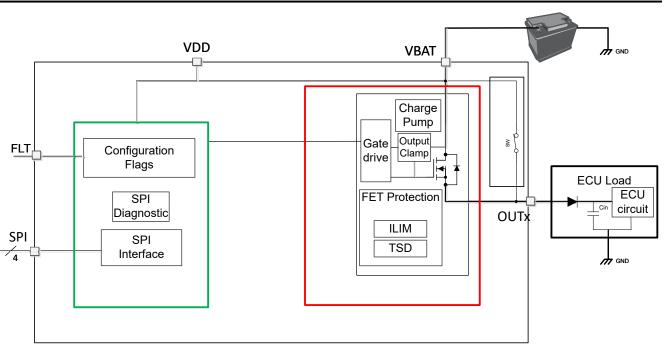

The functional block diagram shown below.

### 8.3 Feature Description

#### 8.3.1 Protection Mechanisms

The TPS2HCS10-Q1device is designed to operate in the automotive environment. The protection mechanisms allow the device to be robust against many system-level events such as load dump, reverse battery, short-to-ground, overload and more.

There are three protection features which, if triggered, will cause the switch to automatically disable:

- Thermal Shutdown

- Overcurrent protection

- Fuse-like protection with a programmable time-current curve

When any of these protections are triggered, the affected channel will be turned off. While one of the switches is in fault turn-off, the fault indication will be available on the  $\overline{FLT}$  pin (see the *Diagnostic Mechanisms* section of the data sheet for more details) and the faulted channel and the type of fault can be read back from the diagnostics registers over the SPI interface.

The ouput is no longer held off (FET and channel can be re-enabled) and the fault indication is reset when all of the below conditions are met:

- Programmed t<sub>RETRY</sub> for the particular protection mode has expired or if set in the latch mode, unlatched through appropriate SPI writes.

- All faults are cleared (thermal shutdown, overcurrent protection, fuse protection).

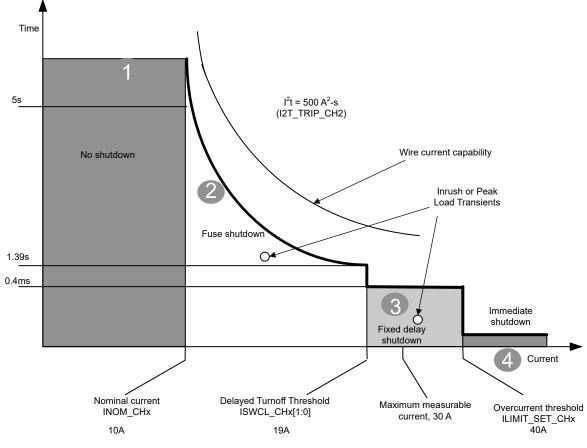

### 8.3.1.1 Programmable Fuse Protection

The device includes a programmable fuse protection, that is based on a defined time-current curve and is commonly referred to as I2t protection in melting fuse data sheets. The intent is to match the switch turnoff behavior of a melting fuse. There are two parameters that can be configured (for each channel) in the I2T\_CONFIG\_CH1 and I2T\_CONFIG\_CH2 registers - that sets the time-current curve. One, the nomimal current (NOM\_CUR\_CHx), is the current below which the device can supply current indefinitely without turn-off. This is roughly equivalent to the fuse current rating of the melting fuses. The second parameter, I2T\_TRIP\_CHx, is the integral energy value above which the switch is turned off. Other parameters that define the region are (1) the maximum current that is measurable (ISWCL\_CHx) that is determined by the current sense ratio (KSNS) of the device and the resistor chosen on the sense pin and (2) the SWCL\_DLY\_TMR\_CHx that sets the time after which the channel shutdown when the current exceeds ISWCL\_CHx. The channel remains off for a period set by TCLDN\_CHx bits before retrying. The device can be configured to latch-off (retry only on MCU re-enable of the channel) by setting the two-bit TCLDN\_CHx to 00.

The operational region for the fuse-based shutdown is shown in the  $\boxtimes$  8-2 below. Exemplary values for the current values that bound the operational region is included.

図 8-2. Current Operational Region of Fuse Based Switchoff

### 8.3.1.2 Thermal Shutdown

The TPS2HCS10-Q1 includes a temperature sensor on the power FET and also within the controller portion of the device. There are two cases that the device will consider to be a thermal shutdown fault:

- $T_{J,FET} > T_{ABS}$

- $(T_{J,FET} T_{J,controller}) > T_{REL}$

After the fault is detected, the switch will turn off. If  $T_{J,FET}$  exceeds  $T_{ABS}$ , the fault is cleared when the switch temperature decreases by the hysteresis value,  $T_{HYS}$ . If instead, the  $T_{REL}$  threshold is exceeded, the fault is cleared after  $T_{RETRY}$  passes.

### 8.3.1.3 Overcurrent Protection And Capacitive Load Charging

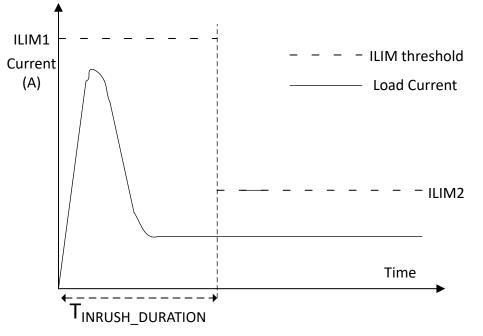

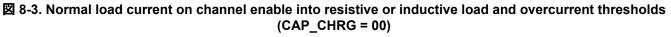

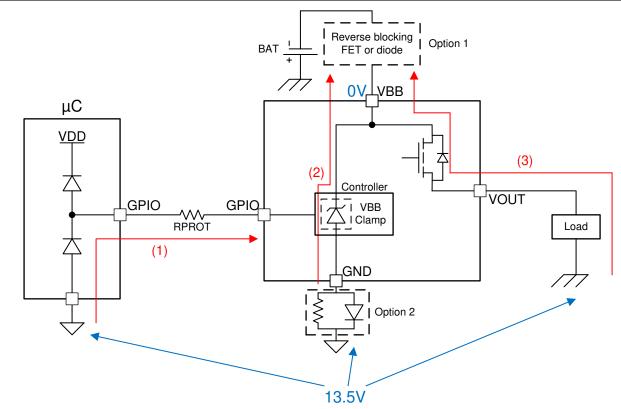

The device features overcurrent protection with an adjustable protection threshold programmed in the ILIM\_CONFIG\_CHx register. Additional programmability is introduced to account for capacitive loads and motor or lamp loads with a high inrush current. The type of load can be specified as capacitive or not using the CAP\_CHRG\_CHx bits in the ILIM\_CONFIG\_CHx register. A value other than 00 indicates capacitive load and the overcurrent protection as well as capacitive load charging behavior is defined for the time defined by the INRUSH\_DURATION\_CHx bits in the ILIM\_CONFIG\_CHx register. In these modes, the current is limited using the cap charging rate that is programmed using the ILIM\_CONFIG\_CHx register CAP\_CHRG\_DVDT [7:4] bits. A CAP\_CHRG\_CHx setting of 00 is used for a non-capacitive loads and here the overcurrent protection threshold is set using INRUSH\_LIMIT\_CHx for the time defined by the INRUSH\_DURATION\_CHx bits. Unlike the capacitive charging modes, the current is not limited but the channel is turned off immediately in case the threshold current is exceeded. In either type of load, the overcurrent protection is immediate turn-off once past the inrush duration phase. The normal load current behavior is shown in the 🛛 8-4 for the capacitive loads and in the 🕅 8-3 for the inductive or resistive loads (like heaters and motors).

図 8-4. Normal load current behavior on channel enable into a capacitive load and overcurrent thresholds

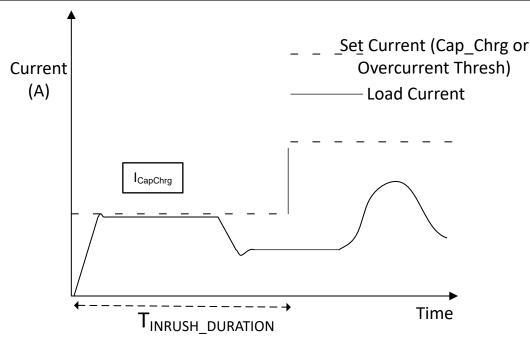

An overcurrent protection event occurs when  $I_{OUTx}$  exceeds the programmed threshold level,  $I_{CL}$ . When  $I_{OUT}$  reaches the current limit threshold, ICL, the channel is immediately turned off. Please note that the current may peak at a higher value ( $I_{CL_pk}$ ) than the programmed overcurrent threshold ( $I_{CL}$ ). This is due to the limitation of the speed of the over-current protection response.

⊠ 8-5 shows the immediate overcurrent protection switch off behavior. The switch will retry after the fault is cleared and t<sub>RETRY</sub> has expired. When the switch retries after a shutdown event, the fault indication will remain until V<sub>OUT</sub> has risen to V<sub>BB</sub> – 1.8 V. Once V<sub>OUT</sub> has risen, the fault indication at the pin is reset and current sensing is available. If there is a short-to-ground and V<sub>OUT</sub> is not able to rise, the fault indication will remain indefinitely.

図 8-5. Overcurrent Protection Response

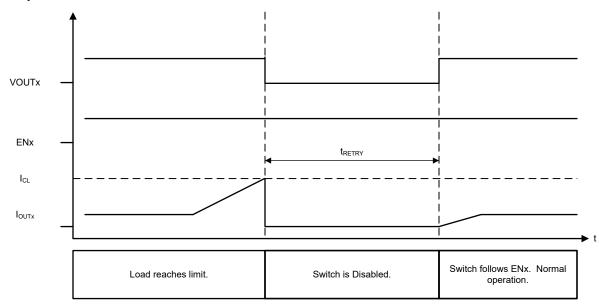

### 8.3.1.4 Reverse Battery

In the reverse battery condition, the switch will automatically be enabled regardless of the state of the output (set by the SW\_STATE register) to prevent excess power dissipation inside the MOSFET body diode. In many applications (for example, resistive loads), the full load current may be present during reverse battery. In order to activate the automatic switch on feature, the DI pin must have a path to ground from either from the MCU or it needs to be tied to ground through  $R_{PROT}$  if unused.

There are two options for blocking reverse current in the system. The first option is to place a blocking device (FET or diode) in series with the battery supply, blocking all current paths. The second option is to place a blocking diode in series with the GND node of the high-side switch. This method will protect the controller portion of the switch (path 2), but it will not prevent current from flowing through the load (path 3). The diode used for the second option may be shared amongst multiple high-side switches.

図 8-6. Current Path During Reverse Battery

For more information on reverse battery protection, refer to TI's *Reverse Battery Protection for High Side Switches* application note.

### 8.3.2 Diagnostic Mechanisms

### 8.3.2.1 VOUT Short-to-Battery and Open-Load

The TPS2HCS10-Q1 is capable of detecting short-to-battery and open-load events regardless of whether the channel output is turned on or off, however the two conditions use different methods.

### 8.3.2.1.1 Detection With Channel Output (FET) Enabled

When the channel output is enabled and the FET is on, the VOUT short-to-battery and open-load conditions can be detected by the current sense feature. In both cases, the load current as measured using the current sense circuit and the ADC (available in the ADC\_RESULT\_CHx\_I register, CH1 shown as example) as below the expected value. The current sense accuracy can be increased at low current levels by changing the current sense ratio from a nominal value of 5000 to a lower value of 1200. This is accomplished by setting the OL\_ON\_EN\_CHx bit to 1 in the DIAG\_CONFIG\_CHx register (CH1 shown for example). However, the load current needs to be confirmed to be below 100 mA for this bit to take effect. In addition, the voltage input to the ADC can be scaled by a factor of 8 by setting the ISNS\_SCALE\_CHx bit in the same DIAG\_CONFIG\_CHx register (CH1 shown for example). This enables the ADC to measure the low load current with better resolution.

### 8.3.2.1.2 Detection With Channel Output Disabled

While the channel output is disabled (FET is off), and if the OL\_OFF\_EN\_CHx bit in the DIAG\_CONFIG\_CHx register (CH1 shown as example) is set high, an internal comparator will detect the condition of  $V_{OUT}$ . The detection circuit is shown in  $\boxtimes$  8-7. If the load is disconnected (open load condition) or there is a short to battery the  $V_{OUT}$  voltage will be higher than the open load threshold ( $V_{OL,off}$ ) and a fault is indicated on the FLT pin unless masked in the FAULT\_MASK register. The faulted channel can be determined by reading the FLT\_STAT\_CHx (CH1 shown as example) register with the OL\_OFF\_CHx bit set if there is a open load on that

channel. An internal pull-up current source of programmable value (through configuration bits OL\_PU\_STR in the DIAG\_CONFIG\_CHx register) is used, so no external component is required if an open load must be detected even with some on-board load and there is significant leakage or other current draw even when the load is disconnected. A pull-up resistor and switch can be added externally to set the V<sub>OUT</sub> voltage above the V<sub>OL,off</sub> during open load conditions, if the internal pull-up is not sufficient.

This figure assumes that the device ground and the load ground are at the same potential. In a real system, there may be a ground shift voltage of the order of 1 V.

### 図 8-7. Short to Battery and Open Load Detection

While the switch is disabled and OL\_OFF\_EN\_CHx bit in the DIAG\_CONFIG\_CHx is set high, the fault indication mechanism will continuously represent the present status. For example, if  $V_{OUT}$  decreases from greater than  $V_{OL}$  to less than  $V_{OL}$ , the fault indication is reset.

Further, to distinguish between an open load and short-to-battery condition, a second diagnostic can be enabled (in the off-state) by setting the SVBB\_EN\_CHx bit in the DIAG\_CONFIG\_CHx register (after the device detect either an open load or short-to-battery). The device then enables a pulldown on the output. If the short-to-battery condition exists,  $V_{OUT}$  voltage will remain higher than the open load threshold ( $V_{OL,off}$ ) the the SHRT\_VBB\_CHx bit will be set high.

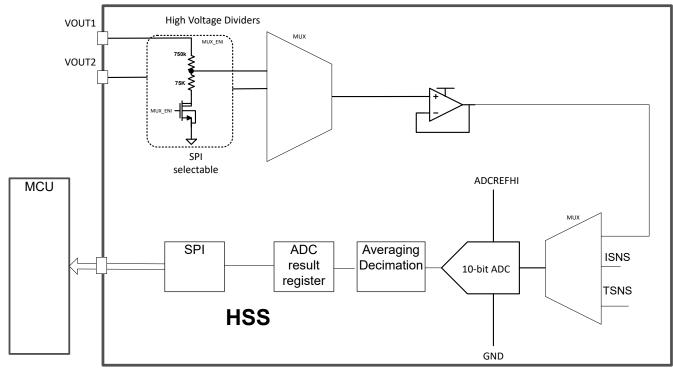

### 8.3.2.2 Digital Current Sense Output

The current sense circuit provide a current output that is proportional to the load current and this current will be sourced into an external resistor to create a voltage that is proportional to the load current. This voltage may be measured by either an external ADC or by the internal ADC. To ensure accurate sensing measurement, the sensing resistor should be connected to the IC GND pin if using the internal ADC. On the other hand, if using the MCU ADC, then the sensing resistor should be connected to the sense ground potential as the microcontroller ADC.

The 10-bit digital current sense output can be read from the ADC\_RESULT\_CHx\_I (H2 shown as example) register. The ISNS\_RDY\_CHx bit is set if the ADC conversion result is updated in the register from the last time the register was read.

#### 8.3.2.2.1 R<sub>SNS</sub> Value and Accuracy / Resolution of Current Measurement

The following factors should be considered when selecting the R<sub>SNS</sub> value:

- Current sense ratio (K<sub>SNS</sub>)

- · Largest and smallest diagnosable load current required for application operation

- Full-scale voltage of the ADC

- Tolerance of the resistor used

At low current levels, the KSNS factor can be scaled up by a factor of around 4.17 using the configuration bit, OL\_ON\_EN\_CHx, in the DIAG\_CONFIG\_CHx register to improve the accuracy of current measurement. In order to further improve the resolution at low current levels, the device offers the configuration bit ISNS\_SCALE\_CHx in the DIAG\_CONFIG\_CHx register that multiplies the input voltage to the ADC by a factor of 8. This enables the ADC to measure currents even of the order of 10 mA with sufficient bit resolution.

#### 8.3.2.2.1.1 High Accuracy Load Current Sense

In many automotive ECUs, the high-side switch is need to provide diagnostic information about the downstream load current. With more complex loads, high accuracy sensing is required. A few examples follow:

- LED lighting: In many architectures, the body control module (BCM) must be compatible with both incandescent bulbs and also LED modules. The inacndescent lamp load may be relatively simple to diagnose. However, the LED module will consume less current and also can include multiple LED strings in parallel. The same BCM is used in both cases, so the high-side switch can accurately diagnose both load types.

- **Solenoid protection**: Often solenoids are precisely controlled by low-side switches. However, in a fault event, the low-side switch cannot disconnect the solenoid from the power supply. A high-side switch can be used to continuously monitor several solenoids. If the system current becomes higher than expected, the high-side switch can disable the module.

#### 8.3.2.2.1.2 SNS Output Filter

To achieve the most accurate current sense value, it is recommended to filter the SNS output. There are two methods of filtering:

- Low-Pass RC filter between the SNS pin and the ADC input. This filter is illustrated in ⊠ 9-1 with typical values for the resistor and capacitor. The designer should select a C<sub>SNS</sub> capacitor value based on system requirements. A larger value will provide improved filtering but a smaller value will allow for faster transient response.

- The ADC and microcontroller can also be used for filtering. It is recommended that the ADC collects several measurements of the current sense output. The median value of this data set should be considered as the most accurate result. By performing this median calculation, the microcontroller can filter out any noise or outlier data.

#### 8.3.2.3 Output Voltage and FET Temperature Sensing

The following voltage and temperature sense output are available as 10-bit digital outputs after ADC conversion.

- Channel output VOUTx voltage sensing available from ADC\_RESULT\_CHx\_V register

- Channel FET temperature sensing available from ADC\_RESULT\_CHx\_T register

- Supply voltage input sense available from ADC\_RESULT\_VBB register

The channel output voltage sensing circuit and the ADC MUX is shown in  $\boxtimes$  8-8. The feature removes the need for external components and reduces the MCU ADC channel use in order to monitor the output voltage for diagnostic purposes.

図 8-8. VOUT Voltage Sensing and ADC MUX

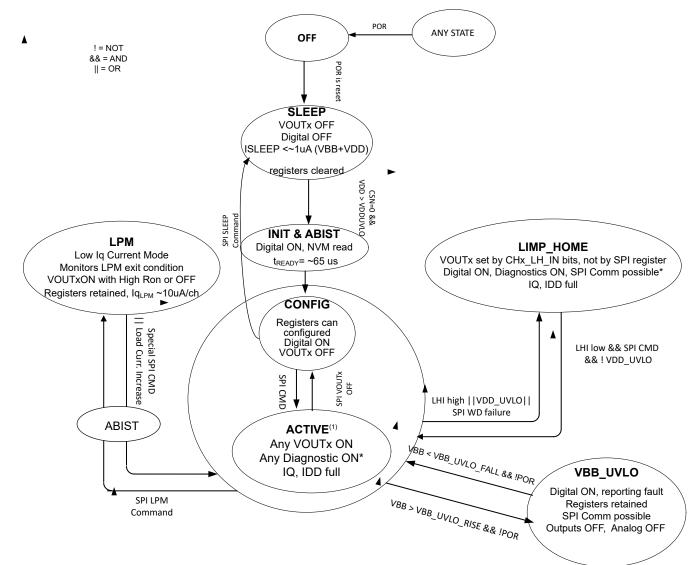

### 8.4 Device Functional Modes

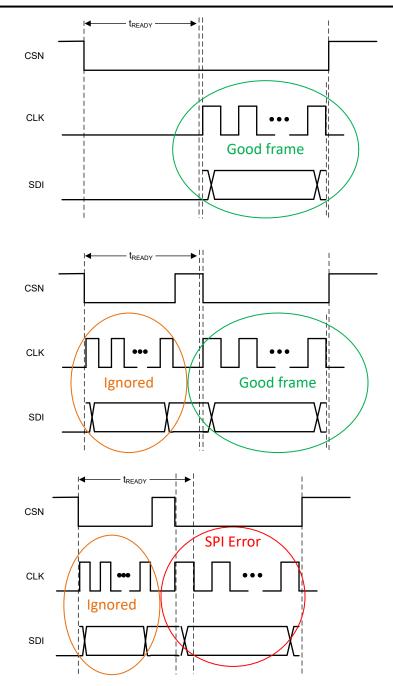

### 8.4.1 State Diagram

The device has three main categories of states it can transition into and out of: low quiescent current, normal operation, and failsafe. Insdie of each of the categories are several states the device can be in. The state diagram for the device is shown in  $\boxed{12}$  8-9

### 🛛 8-9. State Diagram

### 表 8-1. State Transition

| Operating Mode                      | Entering Condition                                           | Leaving Condition                                                                                                                     | Characteristics                                                                                                                                    |

|-------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Off (this is not an operating mode) | ANY STATE <ul> <li>On POR from loss of all supply</li> </ul> | SLEEP POR is RESET when supply input is available                                                                                     | Nothing powered                                                                                                                                    |

| SLEEP                               | OFF<br>• VBB > VBBPOR<br>• ACTIVE<br>– SLEEP SPI<br>Command  | CONFIG /ACTIVE through<br>INIT & ABIST<br>• CS= 0 AND VDD ><br>VDD_UVLOR<br>A Dummy SPI command will<br>wake the device from<br>SLEEP | <ul> <li>VOUTx OFF</li> <li>Digital OFF</li> <li>Registers Lost</li> <li>IVBB = IVBBSLEEP (~1's μA)</li> <li>IVDD = IVDDSLEEP (~sub μA)</li> </ul> |

| 表 8-1. State Transition (続き) |                                                                                                                                                                                                                                |                                                                                                                                                 |                                                                                                                                                                                                                                                         |  |  |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Operating Mode               | Entering Condition                                                                                                                                                                                                             | Leaving Condition                                                                                                                               | Characteristics                                                                                                                                                                                                                                         |  |  |

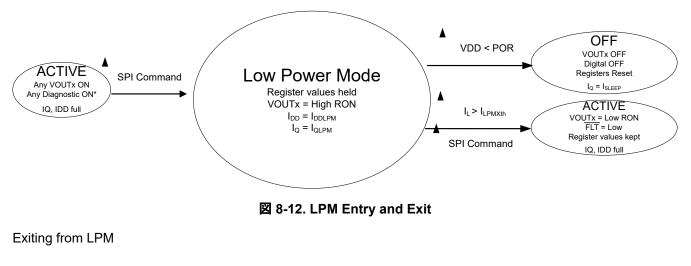

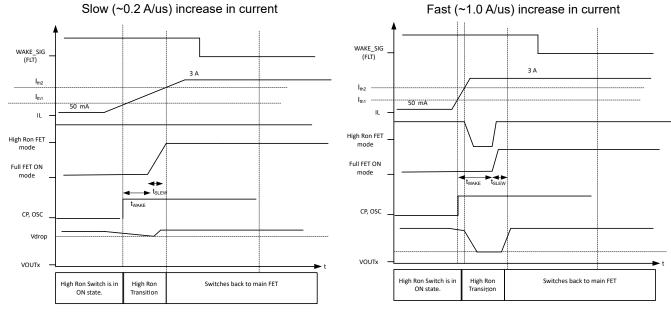

| CONFIG/ACTIVE                | SLEEP through INIT &<br>ABIST<br>• CS = 0 AND<br>• VDD > UVLOR<br>LOW POWER MODE<br>through ABIST<br>• LPM Exit SPI OR<br>• Load current increase<br>LIMP HOME<br>• VDD > UVLOR AND<br>• "LH_STAT" = 1 AND<br>• LHI pin is low | SLEEP<br>SPI SLEEP command<br>LOW POWER MODE<br>LPM SPI Command<br>LIMP HOME<br>VDD < UVLOF OR<br>SPI WD failure if set OR<br>LHI pin pulled HI | <ul> <li>All registers can be configured</li> <li>VOUTx ON/OFF</li> <li>On state diagnostics available <ul> <li>FLT reporting</li> <li>OL on state</li> <li>All ISNS, VSNS, TSNS</li> </ul> </li> <li>IVDD = Full IQ</li> <li>IVBB = Full IQ</li> </ul> |  |  |