PCM6120-Q1 JAJSNF3A - APRIL 2022 - REVISED AUGUST 2022

## PCM6120-Q1 2 チャネル、768kHz、Burr-Brown™ オーディオ ADC

## 1 特長

- マルチチャネルの高性能 ADC:

- 2 チャネルのアナログ・マイクロフォンまたはライン

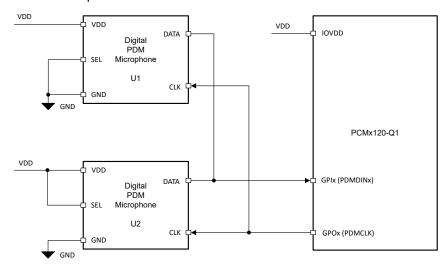

- 4 チャネルのデジタル PDM マイクロフォン

- 最大 2 つのアナログおよび最大 2 つのデジタル・ マイクロフォン・チャネル

- ADC ラインおよびマイクロフォンの差動入力性能:

- ダイナミック・レンジ (DR):

- ダイナミック・レンジ・エンハンサ (DRE) が有効 な状態で 123dB

- DRE が無効な状態で 113dB

- THD+N:-95dB

- ADC チャネル合計モード、DR 性能:

- DRE 無効、2 チャネル合計で 116dB

- ADC 入力電圧:

- 差動、2V<sub>RMS</sub> フルスケール入力

- シングルエンド、1V<sub>RMS</sub>フルスケール入力

- ADC サンプル・レート (f<sub>S</sub>) = 8kHz~768kHz

- プログラム可能なチャネル設定:

- チャネルゲイン:0.5dB 刻みで 0dB~42dB

- デジタル・ボリューム制御:-100dB~27dB

- 0.1dB 分解能のゲイン較正

- 163ns 分解能の位相較正

- マイクロフォンのバイアスまたは電源電圧の生成をプロ グラム可能

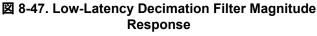

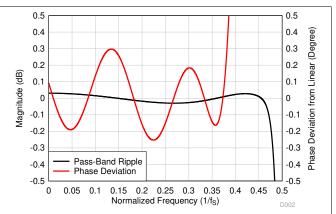

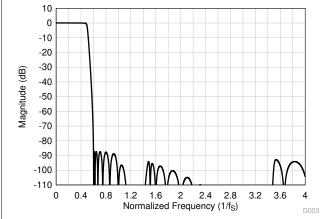

- 低遅延信号処理フィルタの選択

- HPF およびバイカッド・デジタル・フィルタをプログラム

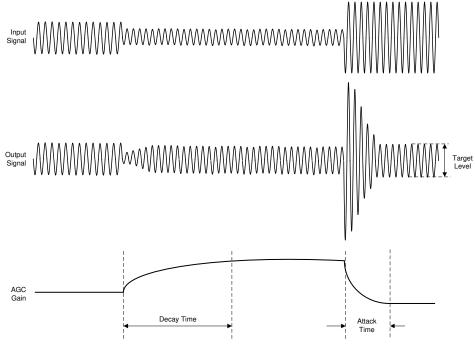

- 自動ゲイン・コントローラ (AGC)

- 音声アクティビティ検出 (VAD)

- I<sup>2</sup>C 制御インターフェイス

- 高性能オーディオ PLL を内蔵

- クロック分周器の設定を自動的に構成

- オーディオ・シリアル・データ・インターフェイス:

- フォーマット: TDM、I<sup>2</sup>S、左揃え (LJ)

- ワード長:16 ビット、20 ビット、24 ビット、32 ビット

- マスタまたはスレーブ・インターフェイス

- 単一電源動作:3.3V または 1.8V

- I/O 電源動作:3.3V または 1.8V

- 1.8V AVDD 電源での消費電力:

- 48kHz サンプル・レートで 9.5mW/ch

## 2 アプリケーション

- 車載アクティブ・ノイズ・キャンセル

- 車載用ヘッド・ユニット

- 後部座席用エンターテインメント

- デジタル・コックピット処理装置

- テレマティクス制御ユニット

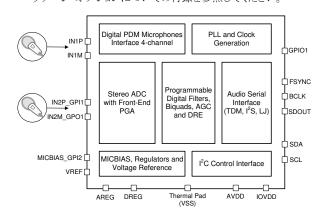

## 3 概要

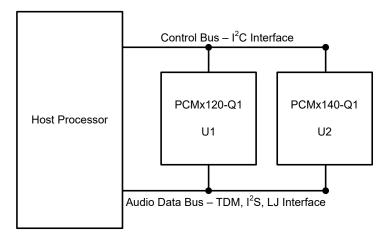

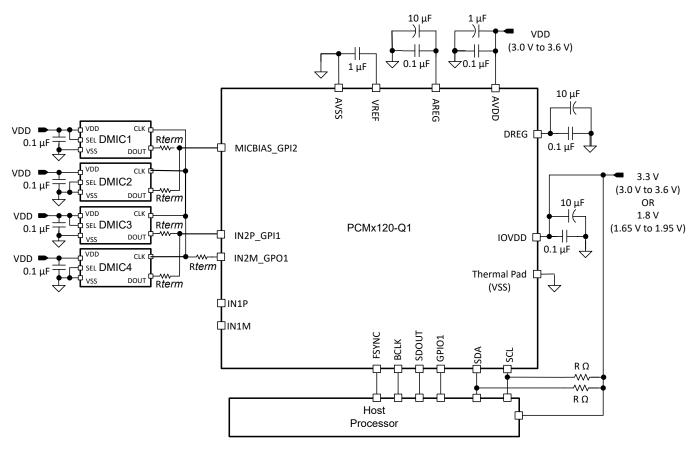

PCM6120-Q1 は、パルス密度変調 (PDM) マイクロフォン 入力のために最大 2 つのアナログ・チャネルまたは 4 つ のデジタル・チャネルを同時にサンプリングできる Burr-Brown<sup>™</sup> 高性能オーディオ A/D コンバータ (ADC) です。 このデバイスは、ラインおよびマイクロフォン入力をサポー トし、シングルエンドと差動の両方の入力構成が可能で す。このデバイスには、プログラム可能なチャネル・ゲイ ン、デジタル・ボリューム制御、プログラム可能なマイクロフ ォン・バイアス電圧、フェーズ・ロック・ループ (PLL)、プロ グラム可能なハイパス・フィルタ (HPF)、バイカッド・フィル タ、低遅延フィルタ・モードが搭載されており、最高 768kHz のサンプル・レートに対応できます。このデバイス は時分割多重化 (TDM)、I<sup>2</sup>S、左揃え (LJ) オーディオ・フ オーマットに対応し、I2C インターフェイスで制御可能で す。これらの高性能な機能を搭載しており、3.3V または 1.8V の単一電源で動作できることから、遠距離マイクロフ オン録音アプリケーションの、スペースの制約が厳しいオ ーディオ・システムに最適です。

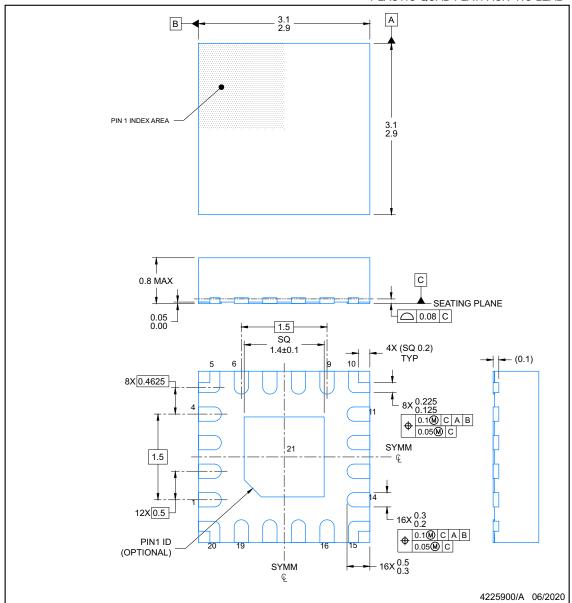

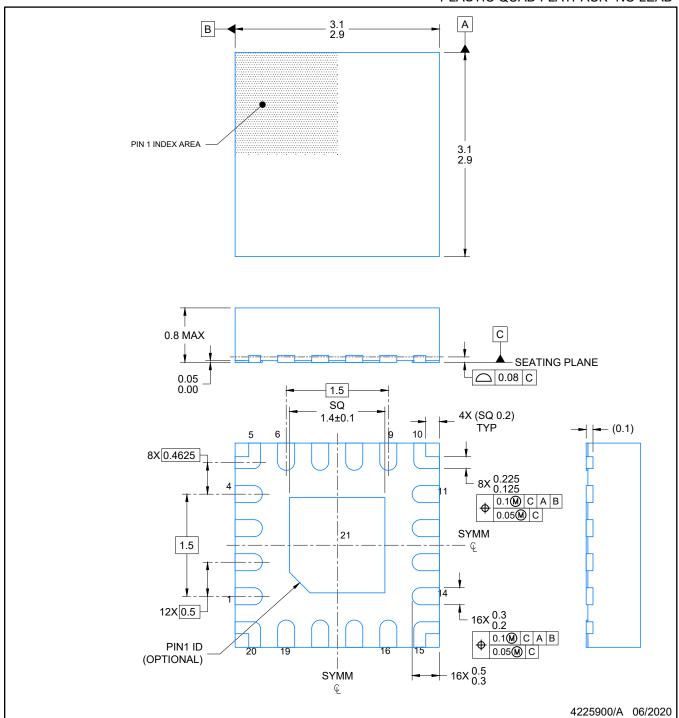

PCM6120-Q1 は -40℃~+125℃で動作が規定されてお り、20 ピンの WQFN パッケージで供給されます。

#### 魁品情報

| _ |                     | A-CHH 113 15 | •                            |  |

|---|---------------------|--------------|------------------------------|--|

|   | 部品番号 <sup>(1)</sup> | パッケージ        | 本体サイズ (公称)                   |  |

|   | PCM6120-Q1          | WQFN (20)    | 3.00mm × 3.00mm、0.5mm<br>ピッチ |  |

利用可能なパッケージについては、データシートの末尾にあるパ ッケージ・オプションについての付録を参照してください。

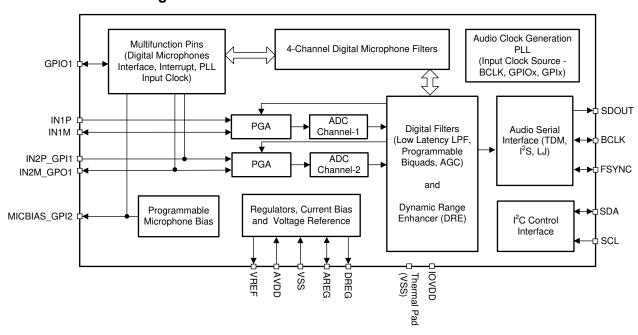

概略ブロック図

## **Table of Contents**

| <b>  特長</b>                                                      | 1 8.1 Overview                            | 19  |

|------------------------------------------------------------------|-------------------------------------------|-----|

| 2 アプリケーション                                                       |                                           | 20  |

| 3 概要                                                             | 0.0 = -4 D +                              | 20  |

| 4 Revision History                                               | 0.45 . 5                                  | 60  |

| 5 Device Comparison Table                                        |                                           | 61  |

| 6 Pin Configuration and Functions                                | 4 8.6 Register Maps                       |     |

| 7 Specifications                                                 |                                           | 102 |

| 7.1 Absolute Maximum Ratings                                     |                                           | 102 |

| 7.2 ESD Ratings                                                  | 5 9.2 Typical Applications                |     |

| 7.3 Recommended Operating Conditions                             | 6 9.3 What to Do and What Not to Do       |     |

| Thermal Information                                              | 6 10 Power Supply Recommendations         |     |

| 7.4 Electrical Characteristics                                   | <sub>7</sub> 11 Layout                    |     |

| 7.5 Timing Requirements: I <sup>2</sup> C Interface              | 1 11.1 Layout Guidelines                  |     |

| 7.6 Switching Characteristics: I <sup>2</sup> C Interface        | 11.2 Layout Example                       |     |

| 7.7 Timing Requirements: TDM, I <sup>2</sup> S or LJ Interface 1 | 12 Device and Documentation Support       | 113 |

| 7.8 Switching Characteristics: TDM, I <sup>2</sup> S or LJ       | 12.1 Documentation Support                |     |

| Interface1                                                       |                                           |     |

| Timing Requirements: PDM Digital Microphone                      | 12.3 サポート・リソース                            | 113 |

| Interface1                                                       |                                           |     |

| 7.9 Switching Characteristics: PDM Digial                        | 12.5 Electrostatic Discharge Caution      |     |

| Microphone Interface1                                            | 2 12.6 Glossary                           | 113 |

| 7.10 Timing Diagrams1                                            | 3 13 Mechanical, Packaging, and Orderable |     |

| 7.11 Typical Characteristics1                                    | 4 Information                             |     |

| B Detailed Description1                                          |                                           | 118 |

|                                                                  |                                           |     |

## **4 Revision History**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

# Changes from Revision \* (April 2022) to Revision A (August 2022)Page・ ドキュメントのステータスを事前情報から量産データに変更1

# **5 Device Comparison Table**

| FEATURE                        | PCM1821-Q1                                              | PCM1820-Q1              | PCM1822-Q1              | PCM3120-Q1           | PCM5120-Q1                                                                                 | PCM6120-Q1 |  |  |

|--------------------------------|---------------------------------------------------------|-------------------------|-------------------------|----------------------|--------------------------------------------------------------------------------------------|------------|--|--|

| Control interface              |                                                         | Pin control             |                         | I <sup>2</sup> C     |                                                                                            |            |  |  |

| Digital audio serial interface |                                                         | TDM or I <sup>2</sup> S |                         |                      | I or I <sup>2</sup> S or left-justifie                                                     | d (LJ)     |  |  |

| Audio analog channel           |                                                         |                         |                         | 2                    |                                                                                            |            |  |  |

| Digital microphone channel     |                                                         | Not available           |                         | 4                    |                                                                                            |            |  |  |

| Programmable MICBIAS voltage   |                                                         | N/A                     |                         |                      | Yes                                                                                        |            |  |  |

| Dynamic range (DRE disabled)   | 106 dB                                                  | 113 dB                  | 111 dB                  | 106 dB               | 108 dB                                                                                     | 113 dB     |  |  |

| Dynamic range (DRE enabled)    | Not available                                           | 123 dB                  | 117 dB                  | Not available        | 120 dB                                                                                     | 123 dB     |  |  |

| ADC SNR with DRE               | N/A                                                     | 123 dB                  | 117 dB                  | N/A                  | 120 dB                                                                                     | 123 dB     |  |  |

| Input Voltage                  | 2 V                                                     | rms                     | 1 V <sub>rms</sub>      |                      | 2 V <sub>rms</sub>                                                                         |            |  |  |

| Input Type                     | Differential/Single-<br>Ended                           | Differential            |                         | Differential/S       | Single-Ended                                                                               |            |  |  |

| Input impedance                | 10 kΩ                                                   | 2.                      | 5 kΩ                    |                      | 2.5 kΩ, 10 kΩ, 20 kΩ                                                                       | Ω          |  |  |

| Compatibility                  | Pin-to-pin, package, drop-in replacements of each other |                         |                         |                      | Pin-to-pin, package, and control registers compatible; drop-<br>replacements of each other |            |  |  |

| Package                        |                                                         | WQF1                    | N (RTE), 20-pin, 3.00 i | mm × 3.00 mm (0.5-mi | m pitch)                                                                                   |            |  |  |

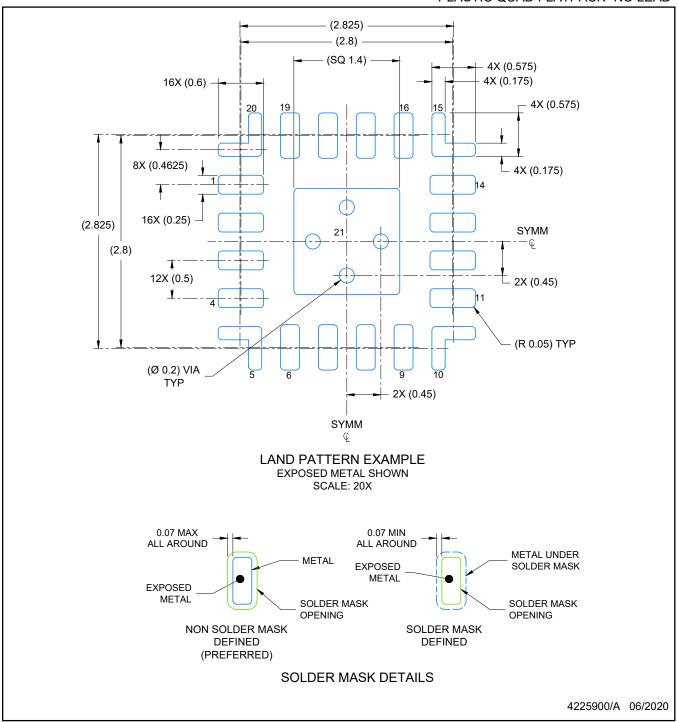

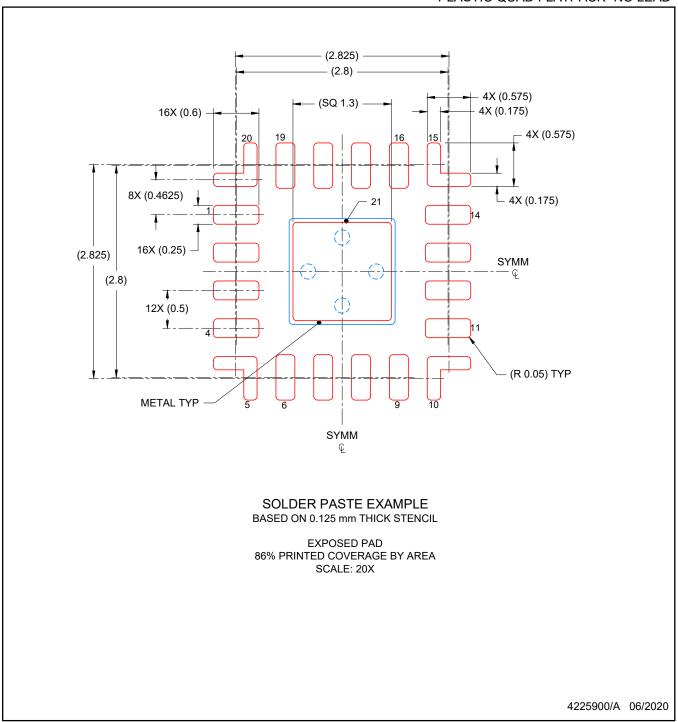

## **6 Pin Configuration and Functions**

図 6-1. RTE Package, 20-Pin WQFN With Exposed Thermal Pad, Top View

表 6-1. Pin Functions

|                                                                          | PIN       | TVDE                                                                                                                                                                                               | DECORIDATION                                                                                                                                                                                       |  |  |

|--------------------------------------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO.                                                                      | NAME      | TYPE                                                                                                                                                                                               | DESCRIPTION                                                                                                                                                                                        |  |  |

| 1                                                                        | IN1P      | Analog input                                                                                                                                                                                       | Analog input 1P pin.                                                                                                                                                                               |  |  |

| 2                                                                        | IN1M      | Analog input                                                                                                                                                                                       | Analog input 1M pin.                                                                                                                                                                               |  |  |

| 3                                                                        | IN2P_GPI1 | Analog input/digital input                                                                                                                                                                         | Analog input 2P pin or general-purpose digital input 1 (multipurpose functions such as digital microphones data, PLL input clock source, and so forth).                                            |  |  |

| 4                                                                        | IN2M_GPO1 | Device ground internally shorted to thermal pad. Short this package corner p                                                                                                                       |                                                                                                                                                                                                    |  |  |

| Device ground internally shorted to thermal pad. Short this package corr |           | Device ground internally shorted to thermal pad. Short this package corner pin directly to the board ground plane. See the package drawings at the end of this document for corner pin dimensions. |                                                                                                                                                                                                    |  |  |

| 6                                                                        | SDOUT     | Digital output                                                                                                                                                                                     | Audio serial data interface bus output.                                                                                                                                                            |  |  |

| 7                                                                        | BCLK      | Digital I/O                                                                                                                                                                                        | Audio serial data interface bus bit clock.                                                                                                                                                         |  |  |

| 8                                                                        | FSYNC     | Digital I/O                                                                                                                                                                                        | Audio serial data interface bus frame synchronization signal.                                                                                                                                      |  |  |

| 9                                                                        | IOVDD     | Digital supply                                                                                                                                                                                     | Digital I/O power supply (1.8 V or 3.3 V, nominal).                                                                                                                                                |  |  |

| 10                                                                       | VSS       | Ground supply                                                                                                                                                                                      | Device ground internally shorted to thermal pad. Short this package corner pin directly to the board ground plane. See the package drawings at the end of this document for corner pin dimensions. |  |  |

| 11                                                                       | GPIO1     | Digital I/O                                                                                                                                                                                        | General-purpose digital input/output 1 (multipurpose functions such as digital microphones clock or data, PLL input clock source, interrupt, and so forth).                                        |  |  |

| 12                                                                       | SDA       | Digital I/O                                                                                                                                                                                        | Data pin for I <sup>2</sup> C control bus.                                                                                                                                                         |  |  |

| 13                                                                       | SCL       | Digital input                                                                                                                                                                                      | Clock pin for I <sup>2</sup> C control bus.                                                                                                                                                        |  |  |

| 14                                                                       | DREG      | Digital supply                                                                                                                                                                                     | Digital regulator output voltage for digital core supply (1.5 V, nominal). Connect a 10-μF and 0.1-μF low ESR capacitor in parallel to device ground (VSS).                                        |  |  |

| 15                                                                       | VSS       | Ground supply                                                                                                                                                                                      | Device ground internally shorted to thermal pad. Short this package corner pin directly to the board ground plane. See the package drawings at the end of this document for corner pin dimensions. |  |  |

| 16                                                                       | AVDD      | Analog supply                                                                                                                                                                                      | Analog power (1.8 V or 3.3 V, nominal).                                                                                                                                                            |  |  |

# 表 6-1. Pin Functions (continued)

|             | PIN                  | TVDE                        | DECODINE                                                                                                                                                                                                                             |  |  |

|-------------|----------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO.         | NAME                 | TYPE                        | DESCRIPTION                                                                                                                                                                                                                          |  |  |

| 17          | AREG                 | Analog supply               | Analog on-chip regulator output voltage for analog supply (1.8 V, nominal) or external analog power (1.8 V, nominal). Connect a 10- $\mu$ F and 0.1- $\mu$ F low ESR capacitor in parallel to analog ground (AVSS).                  |  |  |

| 18 VREF     |                      | Analog                      | Analog reference voltage filter output. Connect a 1-µF capacitor to analog ground (AVSS).                                                                                                                                            |  |  |

| 19          | MICBIAS_GPI2         | Analog output/digital input | MICBIAS output or general-purpose digital input 2 (multipurpose functions such as digital microphones data, PLL input clock source, and so forth). If used as MICBIAS output, then connect a 1-µF capacitor to analog ground (AVSS). |  |  |

| 20          | VSS                  | Ground supply               | Device ground internally shorted to thermal pad. Short this package corner pin directly to the board ground plane. See the package drawings at the end of this document for corner pin dimensions.                                   |  |  |

| Thermal Pad | Thermal Pad<br>(VSS) | Ground supply               | Thermal pad shorted to internal device ground. Short the thermal pad directly to the board ground plane.                                                                                                                             |  |  |

## 7 Specifications

## 7.1 Absolute Maximum Ratings

over the operating ambient temperature range (unless otherwise noted)(1)

|                                             |                                                                                   | MIN                                    | MAX                             | UNIT |

|---------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------|---------------------------------|------|

|                                             | AVDD to AVSS                                                                      | -0.3                                   | 3.9                             |      |

| Analog input voltage  Digital input voltage | AREG to AVSS                                                                      | -0.3                                   | 2.0                             | V    |

|                                             | IOVDD to VSS (thermal pad)                                                        | -0.3                                   | 3.9                             |      |

| Ground voltage differences                  | AVSS to VSS (thermal pad)                                                         | -0.3                                   | 0.3                             | V    |

| Analog input voltage                        | Analog input pins voltage to AVSS                                                 | -0.3                                   | AVDD + 0.3                      | V    |

| Digital input valtage                       | Digital input except IN2P_GPI1 and MICBIAS_GPI2 pins voltage to VSS (thermal pad) | except IN2P_GPI1 and MICBIAS_GPI2 pins | IOVDD + 0.3                     | V    |

| Digital iliput voltage                      | Digital input IN2P_GPI1 and MICBIAS_GPI2 pins voltage to VSS (thermal pad)        | -0.3                                   | 2.0<br>3.9<br>0.3<br>AVDD + 0.3 |      |

|                                             | Operating ambient, T <sub>A</sub>                                                 | -40                                    | 125                             |      |

| Temperature                                 | Junction, T <sub>J</sub>                                                          | -40                                    | 150                             | °C   |

|                                             | Storage, T <sub>stg</sub>                                                         | -65                                    | 150                             |      |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT    |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|---------|

| V                  | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 | V       |

| V <sub>(ESD)</sub> | Liectiostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | \ \ \ \ |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

|                     |                                                                                                         | MIN  | NOM | MAX                                                                           | UNIT |

|---------------------|---------------------------------------------------------------------------------------------------------|------|-----|-------------------------------------------------------------------------------|------|

| POWER               |                                                                                                         |      |     | -                                                                             |      |

| AVDD,               | Analog supply voltage AVDD to AVSS (AREG is generated using onchip regulator): AVDD 3.3-V operation     | 3.0  | 3.3 | 3.6                                                                           | V    |

| AREG <sup>(1)</sup> | Analog supply voltage AVDD and AREG to AVSS (AREG internal regulator is shutdown): AVDD 1.8-V operation | 1.7  | 1.8 | 1.9                                                                           | V    |

| IOVDD               | IO supply voltage to VSS (thermal pad): IOVDD 3.3-V operation                                           | 3.0  | 3.3 | 3.3 3.6<br>1.8 1.9                                                            | V    |

| טטעטו               | IO supply voltage to VSS (thermal pad): IOVDD 1.8-V operation                                           | 1.65 | 1.8 |                                                                               | V    |

| INPUTS              |                                                                                                         |      |     | '                                                                             |      |

|                     | Analog input pins voltage to AVSS                                                                       | 0    |     | AVDD                                                                          | V    |

|                     | Digital input except IN2P_GPI1 and MICBIAS_GPI2 pins voltage to VSS (thermal pad)                       | 0    |     | IOVDD                                                                         | V    |

|                     | Digital input IN2P_GPI1 and MICBIAS_GPI2 pins voltage to VSS (thermal pad)                              | 0    |     | AVDD                                                                          | V    |

| TEMPERA             | TURE                                                                                                    |      |     | '                                                                             |      |

| T <sub>A</sub>      | Operating ambient temperature                                                                           | -40  |     | 125                                                                           | °C   |

| OTHERS              |                                                                                                         |      |     | '                                                                             |      |

|                     | GPIOx or GPIx (used as MCLK input) clock frequency                                                      |      |     | 36.864                                                                        | MHz  |

| C <sub>b</sub>      | SCL and SDA bus capacitance for I <sup>2</sup> C interface supports standard-mode and fast-mode         |      |     | 400                                                                           | pF   |

| -                   | SCL and SDA bus capacitance for I <sup>2</sup> C interface supports fast-mode plus                      |      |     | 3.3 3.6  1.8 1.9  3.3 3.6  1.8 1.95  AVDD  IOVDD  AVDD  125  36.864  400  550 | •    |

| C <sub>L</sub>      | Digital output load capacitance                                                                         |      | 20  | 50                                                                            | pF   |

<sup>(1)</sup> AVSS and VSS (thermal pad): all ground pins must be tied together and must not differ in voltage by more than 0.2 V.

#### **Thermal Information**

|                       |                                              | PCM6120-Q1 |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RTE (WQFN) | UNIT |

|                       |                                              | 20 PINS    |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 55.9       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 33.1       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 23.4       | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.6        | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 23.3       | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 16.7       | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 7.4 Electrical Characteristics

|          | PARAMETER                                            | TEST CONDITIONS                                                                                                                                                           | MIN | TYP         | MAX | UNIT             |

|----------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|-----|------------------|

| ADC CON  | FIGURATION                                           |                                                                                                                                                                           |     |             |     |                  |

|          |                                                      | Input pins INxP or INxM, 2.5-kΩ input impedance selection                                                                                                                 |     | 2.5         |     |                  |

|          | AC input impedance                                   | Input pins INxP or INxM, 10-kΩ input impedance selection                                                                                                                  |     | 10          |     | kΩ               |

|          |                                                      | Input pins INxP or INxM, 20-kΩ input impednace selection                                                                                                                  |     | 20          |     |                  |

|          | Channel gain range                                   | Programmable range with 0.5-dB steps                                                                                                                                      | 0   |             | 42  | dB               |

| ADC PERF | FORMANCE FOR LINE/MICRO                              | PHONE INPUT RECORDING : AVDD 3.3-V OPERATION                                                                                                                              |     |             |     |                  |

|          | Differential input full-scale<br>AC signal voltage   | AC-coupled input                                                                                                                                                          |     | 2           |     | V <sub>RMS</sub> |

|          | Single-ended input full-<br>scale AC signal voltage  | AC-coupled input                                                                                                                                                          |     | 1           |     | $V_{RMS}$        |

|          | Scale AC Signal Voltage                              | IN1 differential input selected and AC signal shorted to ground, DRE enabled (DRE_LVL = –36 dB, DRE_MAXGAIN = 24 dB), 2.5-kΩ input impedance selection                    | 115 | 122         |     |                  |

| SNR      | Signal-to-noise ratio, A-weighted <sup>(1)</sup> (2) | IN1 differential input selected and AC signal shorted to ground, DRE enabled (DRE_LVL = $-36$ dB, DRE_MAXGAIN = 24 dB), $10$ -k $\Omega$ input impedance selection        |     | 117         |     | dB               |

|          |                                                      | IN1 differential input selected and AC signal shorted to ground, DRE disabled, 2.5-k $\Omega$ input impedance selection, 0-dB channel gain                                | 106 | 112         |     |                  |

|          |                                                      | IN1 differential input selected and AC signal shorted to ground, DRE disabled, 2.5-k $\Omega$ input impedance selection, 12-dB channel gain                               |     | 108         |     |                  |

|          | Dynamic range, A-weighted <sup>(2)</sup>             | IN1 differential input selected and –60-dB full-scale AC signal input, DRE enabled (DRE_LVL = –36 dB, DRE_MAXGAIN = 24 dB), 2.5-kΩ input impedance selection              |     | 123         |     |                  |

| DR       |                                                      | IN1 differential input selected and –60-dB full-scale AC signal input, DRE enabled (DRE_LVL = –36 dB, DRE_MAXGAIN = 24 dB), 10-kΩ input impedance selection               |     | 118         |     | dB               |

|          |                                                      | IN1 differential input selected and –60-dB full-scale AC signal input, DRE disabled, 2.5-kΩ input impedance selection, 0-dB channel gain                                  |     | 113         |     |                  |

|          |                                                      | IN1 differential input selected and $-72\text{-dB}$ full-scale AC signal input, DRE disabled, $2.5\text{-k}\Omega$ input impedance selection, 12-dB channel gain          |     | 108         |     |                  |

|          |                                                      | IN1 differential input selected and –1-dB full-scale AC signal input, DRE enabled (DRE_LVL = –36 dB, DRE_MAXGAIN = 24 dB), 2.5-kΩ input impedance selection               |     | <b>-</b> 95 | -80 |                  |

| ΓHD+N    | Total harmonic distortion <sup>(2)</sup>             | IN1 differential input selected and –1-dB full-scale AC signal input, DRE enabled (DRE_LVL = –36 dB, DRE_MAXGAIN = 24 dB), 10-kΩ input impedance selection                |     | <b>-</b> 95 |     | dB               |

|          |                                                      | IN1 differential input selected and –1-dB full-scale AC signal input, DRE disabled, 2.5-kΩ input impedance selection, 0-dB channel gain                                   |     | <b>–</b> 95 |     |                  |

|          |                                                      | IN1 differential input selected and $-13\text{-dB}$ full-scale AC signal input, DRE disabled, $2.5\text{-}k\Omega$ input impedance selection, $12\text{-dB}$ channel gain |     | -93         |     |                  |

| ADC PERF | FORMANCE FOR LINE/MICRO                              | PHONE INPUT RECORDING : AVDD 1.8-V OPERATION                                                                                                                              |     |             |     |                  |

|          | Differential input full-scale<br>AC signal voltage   | AC-coupled Input                                                                                                                                                          |     | 1           |     | $V_{RMS}$        |

|          | Single-ended input full-<br>scale AC signal voltage  | AC-coupled Input                                                                                                                                                          |     | 0.5         |     | $V_{RMS}$        |

|          | PARAMETER                                            | TEST CONDITIONS                                                                                                                                                             | MIN TYP | MAX             | UNIT      |

|----------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------|-----------|

|          |                                                      | IN1 differential input selected and AC signal shorted to ground, DRE enabled (DRE_LVL = -36 dB, DRE_MAXGAIN = 24 dB), 2.5-kΩ input impedance selection                      | 116     |                 |           |

| SNR      | Signal-to-noise ratio, A-weighted <sup>(1)</sup> (2) | IN1 differential input selected and AC signal shorted to ground, DRE enabled (DRE_LVL = -36 dB, DRE_MAXGAIN = 24 dB), 10-kΩ input impedance selection                       | 111     |                 | dB        |

|          |                                                      | IN1 differential input selected and AC signal shorted to ground, DRE disabled, 2.5-k $\Omega$ input impedance selection, 0-dB channel gain                                  | 105     | 27<br>768<br>32 |           |

|          |                                                      | IN1 differential input selected and $-60$ -dB full-scale AC signal input, DRE enabled (DRE_LVL = $-36$ dB, DRE_MAXGAIN = 24 dB), 2.5-k $\Omega$ input impedance selection   | 117     |                 |           |

| DR       | Dynamic range, A-weighted <sup>(2)</sup>             | IN1 differential input selected and $-60$ -dB full-scale AC signal input, DRE enabled (DRE_LVL = $-36$ dB, DRE_MAXGAIN = 24 dB), $10$ -k $\Omega$ input impedance selection | 112     |                 | dB        |

|          |                                                      | IN1 differential input selected and –60-dB full-scale AC signal input, DRE disabled, 2.5-kΩ input impedance selection, 0-dB channel gain                                    | 106     | 27<br>768       |           |

|          |                                                      | IN1 differential input selected and –2-dB full-scale AC signal input, DRE enabled (DRE_LVL = –36 dB, DRE_MAXGAIN = 24 dB), 2.5-kΩ input impedance selection                 | -90     |                 |           |

| THD+N    | Total harmonic distortion <sup>(2)</sup> (3)         | IN1 differential input selected and –2-dB full-scale AC signal input, DRE enabled (DRE_LVL = $-36$ dB, DRE_MAXGAIN = 24 dB), 10-k $\Omega$ input impedance selection        | -90     |                 | dB        |

|          |                                                      | IN1 differential input selected and –2-dB full-scale AC signal Input, DRE disabled, 2.5-kΩ input impedance selection, 0 dB channel gain                                     | -90     |                 |           |

| ADC OTHE | R PARAMETERS                                         |                                                                                                                                                                             |         |                 |           |

|          | Digital volume control range                         | Programmable 0.5-dB steps                                                                                                                                                   | -100    | 27              | dB        |

|          | Output data sample rate                              | Programmable                                                                                                                                                                | 7.35    | 768             | kHz       |

|          | Output data sample word length                       | Programmable                                                                                                                                                                | 16      | 32              | Bits      |

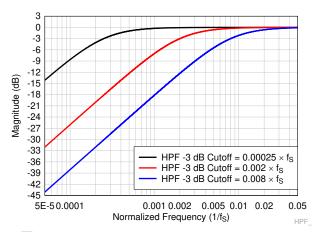

|          | Digital high-pass filter cutoff frequency            | First-order IIR filter with programmable coefficients,  –3-dB point (default setting)                                                                                       | 12      |                 | Hz        |

|          | Interchannel isolation                               | –1-dB full-scale AC-signal input to non measurement channel                                                                                                                 | -124    |                 | dB        |

|          | Interchannel gain mismatch                           | –6-dB full-scale AC-signal input and 0-dB channel gain                                                                                                                      | 0.1     |                 | dB        |

|          | Gain drift <sup>(4)</sup>                            | 0-dB channel gain, across temperature range –40°C to 125°C                                                                                                                  | 36.8    |                 | ppm/°C    |

|          | Interchannel phase mismatch                          | 1-kHz sinusoidal signal                                                                                                                                                     | 0.02    |                 | Degrees   |

|          | Phase drift <sup>(5)</sup>                           | 1-kHz sinusoidal signal, across temperature range – 40°C to 125°C                                                                                                           | 0.0005  |                 | Degrees/° |

| PSRR     | Power-supply rejection ratio                         | 100-mV <sub>PP</sub> , 1-kHz sinusoidal signal on AVDD, differential input selected, 0-dB channel gain                                                                      | 102     |                 | dB        |

| CMRR     | Common-mode rejection ratio                          | Differential microphone input selected, 0-dB channel gain, 100-mV <sub>PP</sub> , 1-kHz signal on both pins and measure level at output in high CMRR Mode                   | 80      |                 | dB        |

| міскорно | ONE BIAS                                             |                                                                                                                                                                             |         |                 |           |

|          |                                                      | BW = 20 Hz to 20 kHz, A-weighted, 1-µF capacitor                                                                                                                            |         |                 |           |

|            | PARAMETER                                                                                                                                | TEST CONDITIONS                                                                                | MIN             | TYP N           | ИΑХ                                              | UNIT |

|------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------|-----------------|--------------------------------------------------|------|

|            |                                                                                                                                          | MICBIAS programmed to VREF and VREF programmed to either 2.75 V, 2.5 V, or 1.375 V             |                 | VREF            |                                                  |      |

|            | MICBIAS voltage                                                                                                                          | MICBIAS programmed to VREF × 1.096 and VREF programmed to either 2.75 V, 2.5 V, or 1.375 V     |                 | VREF ×<br>1.096 |                                                  | V    |

|            |                                                                                                                                          | Bypass to AVDD with 5-mA load                                                                  |                 | AVDD - 0.2      |                                                  |      |

|            | MICBIAS current drive                                                                                                                    |                                                                                                |                 |                 | 5                                                | mA   |

|            | MICBIAS load regulation                                                                                                                  | MICBIAS programmed to either VREF or VREF × 1.096, measured up to max load                     | 0               | 0.6             | 1                                                | %    |

|            | MICBIAS over current protection threshold                                                                                                |                                                                                                | 6.1             |                 |                                                  | mA   |

| IGITAL I/O |                                                                                                                                          |                                                                                                |                 |                 |                                                  |      |

| ,          | Low-level digital input logic                                                                                                            | All digital pins except IN2P_GPI1 and MICBIAS_GPI2, SDA and SCL, IOVDD 1.8-V operation         | -0.3            |                 |                                                  | V    |

| IL         | voltage threshold  High-level digital input logic voltage threshold  Low-level digital output voltage  High-level digital output voltage | All digital pins except IN2P_GPI1 and MICBIAS_GPI2, SDA and SCL, IOVDD 3.3-V operation         | -0.3            |                 | 0.8                                              | V    |

| ,          | High-level digital input logic                                                                                                           | All digital pins except IN2P_GPI1 and MICBIAS_GPI2, SDA and SCL, IOVDD 1.8-V operation         | 0.65 ×<br>IOVDD | IOVDD +         | 0.3                                              | V    |

| /ін        | voltage threshold                                                                                                                        | All digital pins except IN2P_GPI1 and MICBIAS_GPI2, SDA and SCL, IOVDD 3.3-V operation         | 2               | IOVDD +         | PREF  EF × 1.096  - 0.2  5  0.6  1  0.35 × IOVDD | V    |

| ,          | Low-level digital output                                                                                                                 | All digital pins except IN2M_GPO1, SDA and SCL, I <sub>OL</sub> = -2 mA, IOVDD 1.8-V operation |                 | ı               | 0.45                                             |      |

| OL .       | , ·                                                                                                                                      | All digital pins except IN2M_GPO1, SDA and SCL, I <sub>OL</sub> = -2 mA, IOVDD 3.3-V operation |                 |                 | 0.4                                              | V    |

|            | High-level digital output                                                                                                                | All digital pins except IN2M_GPO1, SDA and SCL, I <sub>OH</sub> = 2 mA, IOVDD 1.8-V operation  | IOVDD -<br>0.45 |                 |                                                  | .,   |

| ОН         |                                                                                                                                          | All digital pins except IN2M_GPO1, SDA and SCL, I <sub>OH</sub> = 2 mA, IOVDD 3.3-V operation  | 2.4             |                 |                                                  | V    |

| IL(I2C)    | Low-level digital input logic voltage threshold                                                                                          | SDA and SCL                                                                                    | -0.5            | 0.3 x IO\       | /DD                                              | V    |

| (IH(I2C)   | High-level digital input logic voltage threshold                                                                                         | SDA and SCL                                                                                    | 0.7 x IOVDD     | IOVDD +         | 0.5                                              | V    |

| OL1(I2C)   | Low-level digital output voltage                                                                                                         | SDA, I <sub>OL(I2C)</sub> = -3 mA, IOVDD > 2 V                                                 |                 |                 | 0.4                                              | V    |

| OL2(I2C)   | Low-level digital output voltage                                                                                                         | SDA, $I_{OL(I2C)} = -2 \text{ mA}$ , $IOVDD \le 2 \text{ V}$                                   |                 | 0.2 x IO        | /DD                                              | V    |

|            | Low-level digital output                                                                                                                 | SDA, V <sub>OL(I2C)</sub> = 0.4 V, standard-mode or fast-mode                                  | 3               |                 |                                                  | mA   |

| DL(I2C)    | current                                                                                                                                  | SDA, V <sub>OL(I2C)</sub> = 0.4 V, fast-mode plus                                              | 20              |                 |                                                  | ША   |

| Н          | Input logic-high leakage for digital inputs                                                                                              | All digital pins except IN2P_GPI1 and MICBIAS_GPI2 pins, input = IOVDD                         | -5              | 0.1             | 5                                                | μΑ   |

| L          | Input logic-low leakage for digital inputs                                                                                               | All digital pins except IN2P_GPI1 and MICBIAS_GPI2 pins, input = 0 V                           | -5              | 0.1             | 5                                                | μΑ   |

| ,          | Low-level digital input logic                                                                                                            | IN2P_GPI1 and MICBIAS_GPI2 digital pins, AVDD 1.8-V operation                                  | -0.3            | 0.35 × A        | /DD                                              | V    |

| IL(GPIx)   | voltage threshold                                                                                                                        | IN2P_GPI1 and MICBIAS_GPI2 digital pins, AVDD 3.3-V operation                                  | -0.3            |                 | 0.8                                              | V    |

| ,          | High-level digital input logic                                                                                                           | IN2P_GPI1 and MICBIAS_GPI2 digital pins, AVDD 1.8-V operation                                  | 0.65 × AVDD     | AVDD +          | 0.3                                              |      |

| (IH(GPIx)  | voltage threshold                                                                                                                        | IN2P_GPI1 and MICBIAS_GPI2 digital pins, AVDD 3.3-V operation                                  | 2               | AVDD +          | 0.3                                              | V    |

| ,          | Low-level digital output                                                                                                                 | IN2M_GPO2 digital pin, I <sub>OL</sub> = –2 mA, AVDD 1.8-V operation                           |                 | ı               | 0.45                                             |      |

| OL(GPOx)   | voltage                                                                                                                                  | IN2M_GPO2 digital pin, I <sub>OL</sub> = –2 mA, AVDD 3.3-V operation                           |                 |                 | 0.4                                              | V    |

| ,          | High-level digital output                                                                                                                | IN2M_GPO2 digital pin, I <sub>OH</sub> = 2 mA, AVDD 1.8-V operation                            | AVDD - 0.45     |                 |                                                  |      |

| OH(GPOx)   | voltage                                                                                                                                  | IN2M_GPO2 digital pin, I <sub>OH</sub> = 2 mA, AVDD 3.3-V operation                            | 2.4             |                 |                                                  | V    |

|                       | PARAMETER                                                                                | TEST CONDITIONS                                                                        | MIN | TYP  | MAX | UNIT |  |

|-----------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----|------|-----|------|--|

| I <sub>IH(GPIx)</sub> | Input logic-high leakage for digital inputs                                              | IN2P_GPI1 and MICBIAS_GPI2 digital pins, input = AVDD                                  | -5  | 0.1  | 5   | μА   |  |

| I <sub>IL(GPIx)</sub> | Input logic-high leakage for digital inputs                                              | IN2P_GPI1 and MICBIAS_GPI2 digital pins, input = 0 V                                   | -5  | 0.1  | 5   | μА   |  |

| C <sub>IN</sub>       | Input capacitance for digital inputs                                                     | All digital pins                                                                       |     | 5    |     | pF   |  |

| R <sub>PD</sub>       | Pulldown resistance for digital I/O pins when asserted on                                |                                                                                        |     | 20   |     | kΩ   |  |

| TYPICAL S             | SUPPLY CURRENT CONSUMP                                                                   | TION                                                                                   | •   |      |     |      |  |

| I <sub>AVDD</sub>     |                                                                                          | All external clocks stopped, AVDD = 3.3 V, internal AREG                               |     | 5    |     |      |  |

| I <sub>AVDD</sub>     | Current consumption in sleep mode (software shutdown mode)                               | All external clocks stopped, AVDD = 1.8 V, external AREG supply (AREG shorted to AVDD) |     | 29   |     | μΑ   |  |

| I <sub>IOVDD</sub>    | Shutdown mode)                                                                           | All external clocks stopped, IOVDD = 3.3 V                                             |     | 0.5  |     |      |  |

| I <sub>IOVDD</sub>    |                                                                                          | All external clocks stopped, IOVDD = 1.8 V                                             |     | 0.5  |     |      |  |

| I <sub>AVDD</sub>     |                                                                                          | AVDD = 3.3 V, internal AREG                                                            |     | 11.3 |     |      |  |

| I <sub>AVDD</sub>     | Current consumption with ADC 2-channel operating at f <sub>S</sub> 48-kHz, PLL off, BCLK | AVDD = 1.8 V, external AREG supply (AREG shorted to AVDD)                              |     | 10.6 |     | mA   |  |

| I <sub>IOVDD</sub>    | = 512 × f <sub>S</sub> and DRE disable                                                   | IOVDD = 3.3 V                                                                          |     | 0.1  |     |      |  |

| I <sub>IOVDD</sub>    |                                                                                          | IOVDD = 1.8 V                                                                          |     | 0.05 |     |      |  |

| I <sub>AVDD</sub>     |                                                                                          | AVDD = 3.3 V, internal AREG                                                            |     | 11.5 |     |      |  |

| I <sub>AVDD</sub>     | Current consumption with ADC 2-channel operating                                         | AVDD = 1.8 V, external AREG supply (AREG shorted to AVDD)                              |     | 10.8 |     | mA   |  |

| I <sub>IOVDD</sub>    | at f <sub>S</sub> 16-kHz, PLL on, BCLK<br>= 256 × f <sub>S</sub> and DRE disable         | IOVDD = 3.3 V                                                                          |     | 0.05 |     |      |  |

| I <sub>IOVDD</sub>    |                                                                                          | IOVDD = 1.8 V                                                                          |     | 0.02 |     |      |  |

| I <sub>AVDD</sub>     |                                                                                          | AVDD = 3.3 V, internal AREG                                                            |     | 12.4 |     |      |  |

| I <sub>AVDD</sub>     | Current consumption with ADC 2-channel operating at f <sub>S</sub> 48-kHz, PLL on, BCLK  | AVDD = 1.8 V, external AREG supply (AREG shorted to AVDD)                              |     | 11.7 |     | mA   |  |

| I <sub>IOVDD</sub>    | = $256 \times f_S$ and DRE disable                                                       | IOVDD = 3.3 V                                                                          |     | 0.1  |     |      |  |

| I <sub>IOVDD</sub>    |                                                                                          | IOVDD = 1.8 V                                                                          |     | 0.05 |     |      |  |

| I <sub>AVDD</sub>     | Current consumption with                                                                 | AVDD = 3.3 V, internal AREG                                                            |     | 13.8 |     |      |  |

| I <sub>AVDD</sub>     | ADC 2-channel operating at f <sub>S</sub> 48-kHz, PLL on, BCLK                           | AVDD = 1.8 V, external AREG supply (AREG shorted to AVDD)                              |     | 13.1 |     | mA   |  |

| I <sub>IOVDD</sub>    | = 256 × f <sub>S</sub> and DRE                                                           | IOVDD = 3.3 V                                                                          |     | 0.1  |     |      |  |

| I <sub>IOVDD</sub>    | — enable                                                                                 | IOVDD = 1.8 V                                                                          |     | 0.05 |     |      |  |

- (1) Ratio of output level with 1-kHz full-scale sine-wave input, to the output level with the AC signal input shorted to ground, measured A-weighted over a 20-Hz to 20-kHz bandwidth using an audio analyzer.

- (2) All performance measurements done with 20-kHz low-pass filter and, where noted, A-weighted filter. Failure to use such a filter may result in higher THD and lower SNR and dynamic range readings than shown in the Electrical Characteristics. The low-pass filter removes out-of-band noise, which, although not audible, may affect dynamic specification values.

- (3) For best distortion performance, use input AC-coupling capacitors with low-voltage coefficient.

- (4) Gain drift = gain variation (in temperature range) / typical gain value (gain at room temperature) / temperature range × 10<sup>6</sup> measured with gain in linear scale.

- (5) Phase drift = phase deviation (in temperature range) / (temperature range).

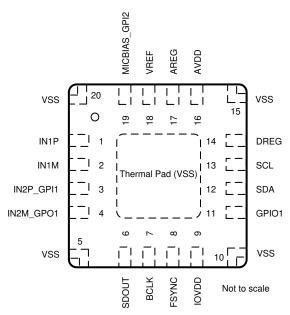

# 7.5 Timing Requirements: I<sup>2</sup>C Interface

at  $T_A = 25^{\circ}$ C, IOVDD = 3.3 V or 1.8 V (unless otherwise noted); see Figure 7-1 for timing diagram

|                     |                                                                                              | MIN                     | NOM MAX | UNIT |

|---------------------|----------------------------------------------------------------------------------------------|-------------------------|---------|------|

| STANDARD-N          | MODE                                                                                         |                         |         |      |

| fscL                | SCL clock frequency                                                                          | 0                       | 100     | kHz  |

| t <sub>HD;STA</sub> | Hold time (repeated) START condition. After this period, the first clock pulse is generated. | 4                       |         | μs   |

| t <sub>LOW</sub>    | Low period of the SCL clock                                                                  | 4.7                     |         | μs   |

| t <sub>HIGH</sub>   | High period of the SCL clock                                                                 | 4                       |         | μs   |

| t <sub>SU;STA</sub> | Setup time for a repeated START condition                                                    | 4.7                     |         | μs   |

| t <sub>HD;DAT</sub> | Data hold time                                                                               | 0                       | 3.45    | μs   |

| t <sub>SU;DAT</sub> | Data setup time                                                                              | 250                     |         | ns   |

| t <sub>r</sub>      | SDA and SCL rise time                                                                        |                         | 1000    | ns   |

| t <sub>f</sub>      | SDA and SCL fall time                                                                        |                         | 300     | ns   |

| t <sub>su;sto</sub> | Setup time for STOP condition                                                                | 4                       |         | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                                             | 4.7                     |         | μs   |

| FAST-MODE           |                                                                                              |                         |         |      |

| f <sub>SCL</sub>    | SCL clock frequency                                                                          | 0                       | 400     | kHz  |

| t <sub>HD;STA</sub> | Hold time (repeated) START condition. After this period, the first clock pulse is generated. | 0.6                     |         | μs   |

| t <sub>LOW</sub>    | Low period of the SCL clock                                                                  | 1.3                     |         | μs   |

| t <sub>HIGH</sub>   | High period of the SCL clock                                                                 | 0.6                     |         | μs   |

| t <sub>SU;STA</sub> | Setup time for a repeated START condition                                                    | 0.6                     |         | μs   |

| t <sub>HD;DAT</sub> | Data hold time                                                                               | 0                       | 0.9     | μs   |

| t <sub>SU;DAT</sub> | Data setup time                                                                              | 100                     |         | ns   |

| t <sub>r</sub>      | SDA and SCL rise time                                                                        | 20                      | 300     | ns   |

| t <sub>f</sub>      | SDA and SCL fall time                                                                        | 20 × (IOVDD / 5.5<br>V) | 300     | ns   |

| t <sub>su;sto</sub> | Setup time for STOP condition                                                                | 0.6                     |         | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                                             | 1.3                     |         | μs   |

| FAST-MODE I         | PLUS                                                                                         |                         |         |      |

| f <sub>SCL</sub>    | SCL clock frequency                                                                          | 0                       | 1000    | kHz  |

| t <sub>HD;STA</sub> | Hold time (repeated) START condition. After this period, the first clock pulse is generated. | 0.26                    |         | μs   |

| t <sub>LOW</sub>    | Low period of the SCL clock                                                                  | 0.5                     |         | μs   |

| t <sub>HIGH</sub>   | High period of the SCL clock                                                                 | 0.26                    |         | μs   |

| t <sub>SU;STA</sub> | Setup time for a repeated START condition                                                    | 0.26                    |         | μs   |

| t <sub>HD;DAT</sub> | Data hold time                                                                               | 0                       |         | μs   |

| t <sub>SU;DAT</sub> | Data setup time                                                                              | 50                      |         | ns   |

| t <sub>r</sub>      | SDA and SCL rise time                                                                        |                         | 120     | ns   |

| t <sub>f</sub>      | SDA and SCL fall time                                                                        | 20 × (IOVDD / 5.5<br>V) | 120     | ns   |

| t <sub>su;sto</sub> | Setup time for STOP condition                                                                | 0.26                    |         | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                                             | 0.5                     |         | μs   |

# 7.6 Switching Characteristics: I<sup>2</sup>C Interface

at T<sub>A</sub> = 25°C, IOVDD = 3.3 V or 1.8 V (unless otherwise noted); see Figure 7-1 for timing diagram

|                                      | PARAMETER | TEST CONDITIONS | MIN | TYP | MAX  | UNIT |

|--------------------------------------|-----------|-----------------|-----|-----|------|------|

| t <sub>d(SDA)</sub> SCL to SDA delay |           | Standard-mode   | 250 |     | 1250 |      |

|                                      | ,         | Fast-mode       | 250 |     | 850  | ns   |

|                                      |           | Fast-mode plus  |     |     | 400  |      |

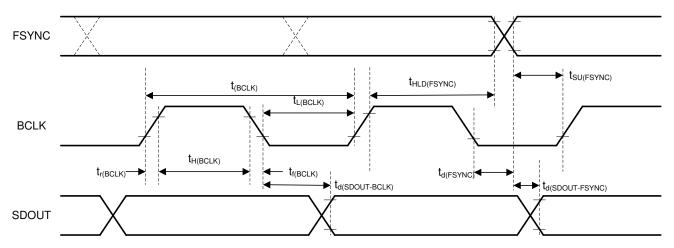

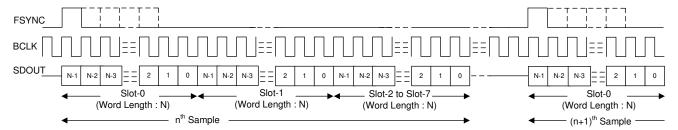

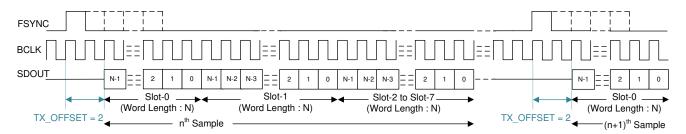

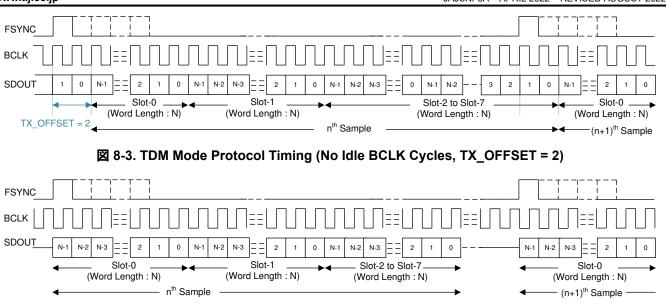

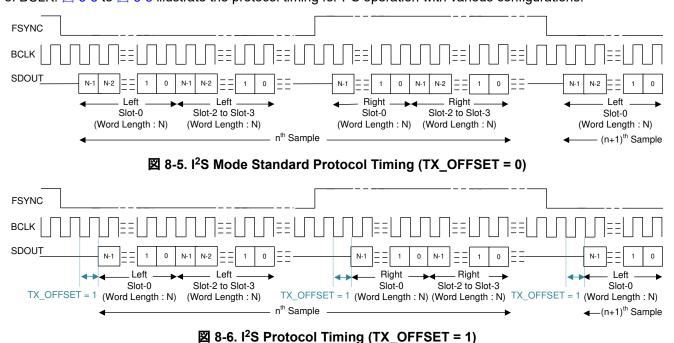

## 7.7 Timing Requirements: TDM, I<sup>2</sup>S or LJ Interface

at T<sub>A</sub> = 25°C, IOVDD = 3.3 V or 1.8 V and 20-pF load on all outputs (unless otherwise noted); see 🗵 7-2 for timing diagram

| Α /                     |                              | ,,                                 |     | , ,     |      |

|-------------------------|------------------------------|------------------------------------|-----|---------|------|

|                         |                              |                                    | MIN | NOM MAX | UNIT |

| t <sub>(BCLK)</sub>     | BCLK period                  |                                    | 40  |         | ns   |

| t <sub>H(BCLK)</sub>    | BCLK high pulse duration (1) |                                    | 25  |         | ns   |

| t <sub>L(BCLK)</sub>    | BCLK low pulse duration (1)  |                                    | 25  |         | ns   |

| t <sub>SU(FSYNC)</sub>  | FSYNC setup time             |                                    | 8   |         | ns   |

| t <sub>HLD(FSYNC)</sub> | FSYNC hold time              |                                    | 8   |         | ns   |

| t <sub>r(BCLK)</sub>    | BCLK rise time               | 10% - 90% rise time <sup>(2)</sup> |     | 10      | ns   |

| t <sub>f(BCLK)</sub>    | BCLK fall time               | 90% - 10% fall time <sup>(2)</sup> |     | 10      | ns   |

|                         |                              |                                    |     |         |      |

<sup>(1)</sup> The BCLK minimum high or low pulse duration can be relaxed to 14 ns (to meet the timing specifications), if the SDOUT data line is latched on the same BCLK edge polarity as the edge used by the device to transmit SDOUT data.

## 7.8 Switching Characteristics: TDM, I<sup>2</sup>S or LJ Interface

at T<sub>A</sub> = 25°C, IOVDD = 3.3 V or 1.8 V and 20-pF load on all outputs (unless otherwise noted); see 🗵 7-2 for timing diagram

|                             | PARAMETER                                                                | TEST CONDITIONS              | MIN | TYP MAX | UNIT |

|-----------------------------|--------------------------------------------------------------------------|------------------------------|-----|---------|------|

| t <sub>d(SDOUT-BCLK)</sub>  | BCLK to SDOUT delay                                                      | 50% of BCLK to 50% of SDOUT  | 3   | 18      | ns   |

| $t_{d(SDOUT\text{-}FSYNC)}$ | FSYNC to SDOUT delay in TDM or LJ mode (for MSB data with TX_OFFSET = 0) | 50% of FSYNC to 50% of SDOUT |     | 18      | ns   |

| f <sub>(BCLK)</sub>         | BCLK output clock frequency: master mode <sup>(1)</sup>                  |                              |     | 24.576  | MHz  |

| t <sub>H(BCLK)</sub>        | BCLK high pulse duration: master mode                                    |                              | 14  |         | ns   |

| t <sub>L(BCLK)</sub>        | BCLK low pulse duration: master mode                                     |                              | 14  |         | ns   |

| t <sub>d(FSYNC)</sub>       | BCLK to FSYNC delay: master mode                                         | 50% of BCLK to 50% of FSYNC  | 3   | 18      | ns   |

| t <sub>r(BCLK)</sub>        | BCLK rise time: master mode                                              | 10% - 90% rise time          |     | 8       | ns   |

| t <sub>f(BCLK)</sub>        | BCLK fall time: master mode                                              | 90% - 10% fall time          |     | 8       | ns   |

<sup>(1)</sup> The BCLK output clock frequency must be lower than 18.5 MHz (to meet the timing specifications), if the SDOUT data line is latched on the opposite BCLK edge polarity than the edge used by the device to transmit SDOUT data.

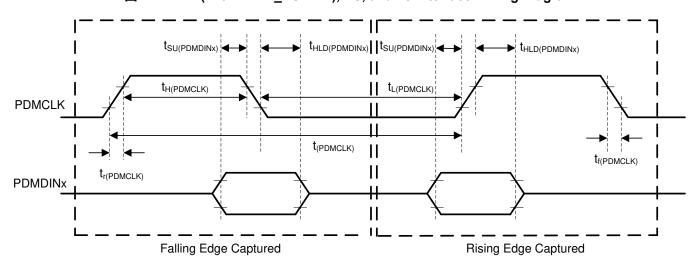

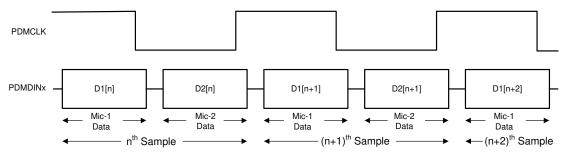

#### **Timing Requirements: PDM Digital Microphone Interface**

at  $T_A$  = 25°C, IOVDD = 3.3 V or 1.8 V and 20-pF load on all outputs (unless otherwise noted); see Figure 7-3 for timing diagram

|                           |                    | MIN | NOM MAX | UNIT |

|---------------------------|--------------------|-----|---------|------|

| t <sub>SU(PDMDINx)</sub>  | PDMDINx setup time | 30  |         | ns   |

| t <sub>HLD(PDMDINx)</sub> | PDMDINx hold time  | 0   |         | ns   |

## 7.9 Switching Characteristics: PDM Digial Microphone Interface

at  $T_A$  = 25°C, IOVDD = 3.3 V or 1.8 V and 20-pF load on all outputs (unless otherwise noted); see Figure 7-3 for timing diagram

|                        | PARAMETER                  | TEST CONDITIONS     | MIN   | TYP | MAX   | UNIT |

|------------------------|----------------------------|---------------------|-------|-----|-------|------|

| f <sub>(PDMCLK)</sub>  | PDMCLK clock frequency     |                     | 0.768 |     | 6.144 | MHz  |

| t <sub>H(PDMCLK)</sub> | PDMCLK high pulse duration |                     | 72    |     |       | ns   |

| t <sub>L(PDMCLK)</sub> | PDMCLK low pulse duration  |                     | 72    |     |       | ns   |

| t <sub>r(PDMCLK)</sub> | PDMCLK rise time           | 10% - 90% rise time |       |     | 18    | ns   |

Submit Document Feedback

<sup>(2)</sup> The BCLK maximum rise and fall time can be relaxed to 13 ns if the BCLK frequency used in the system is below 20 MHz. Relaxing the BCLK rise and fall time can cause noise to increase because of higher clock jitter.

at  $T_A = 25$ °C, IOVDD = 3.3 V or 1.8 V and 20-pF load on all outputs (unless otherwise noted); see Figure 7-3 for timing diagram

|                 | PARAMETER        | TEST CONDITIONS     | MIN | TYP | MAX | UNIT |

|-----------------|------------------|---------------------|-----|-----|-----|------|

| $t_{f(PDMCLK)}$ | PDMCLK fall time | 90% - 10% fall time |     |     | 18  | ns   |

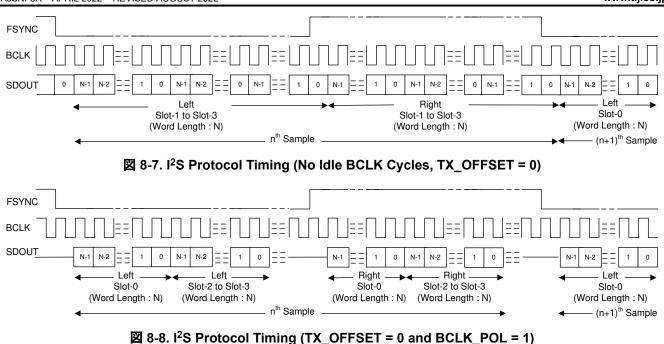

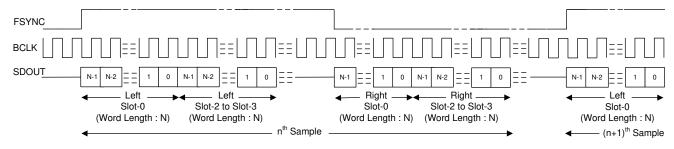

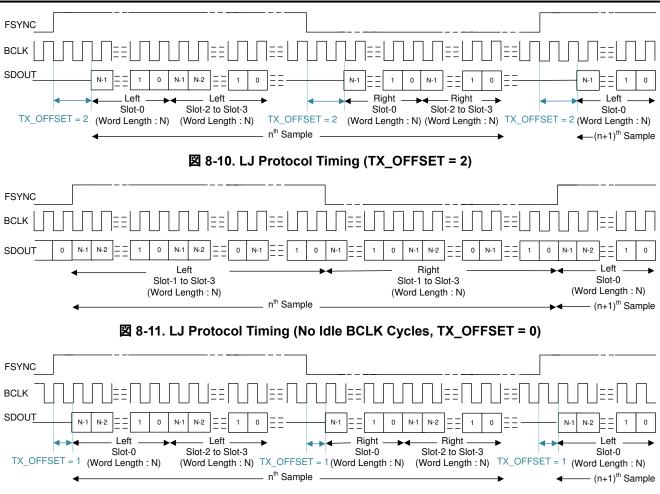

## 7.10 Timing Diagrams

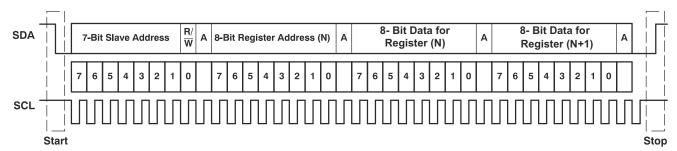

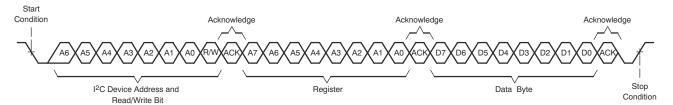

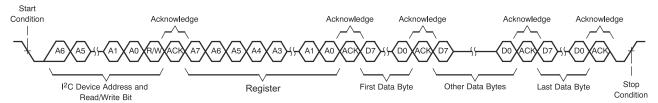

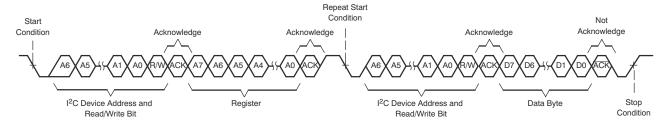

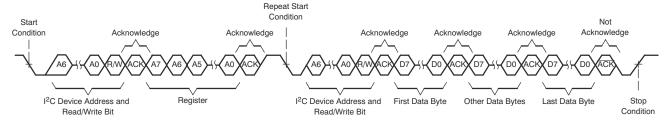

図 7-1. I<sup>2</sup>C Interface Timing Diagram

図 7-2. TDM (With BCLK\_POL = 1), I<sup>2</sup>S, and LJ Interface Timing Diagram

図 7-3. PDM Digital Microphone Interface Timing Diagram

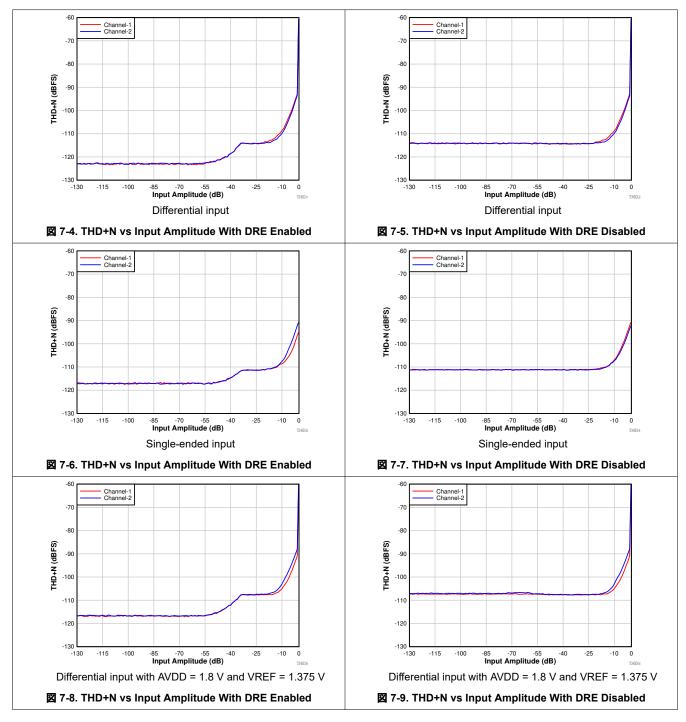

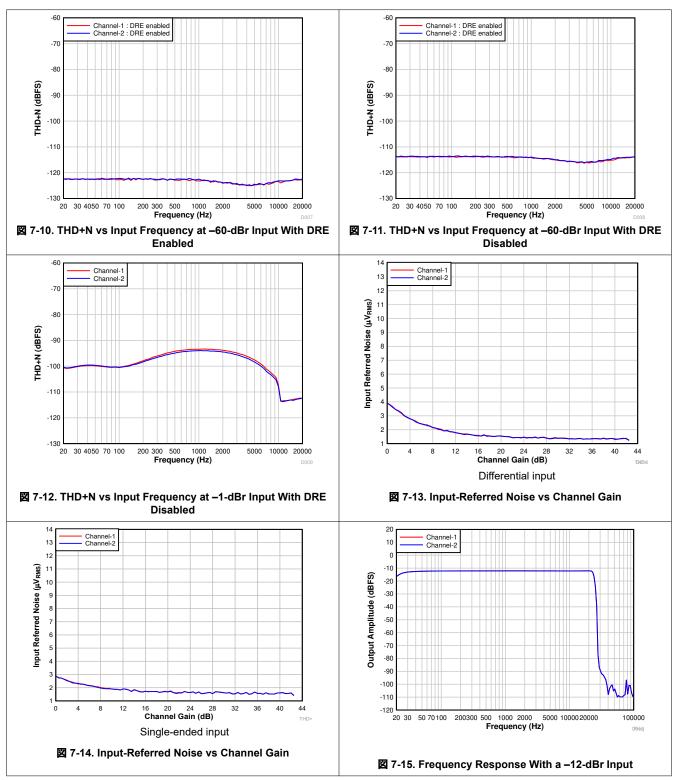

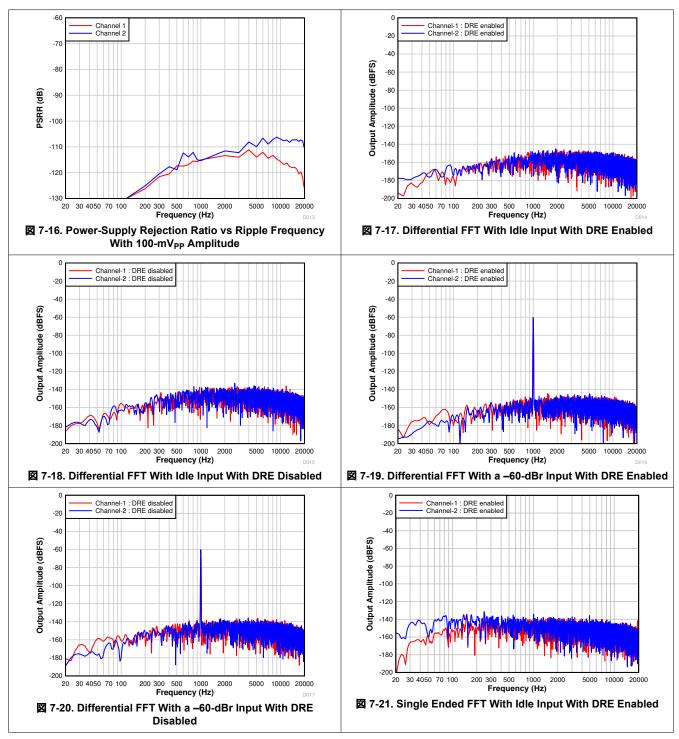

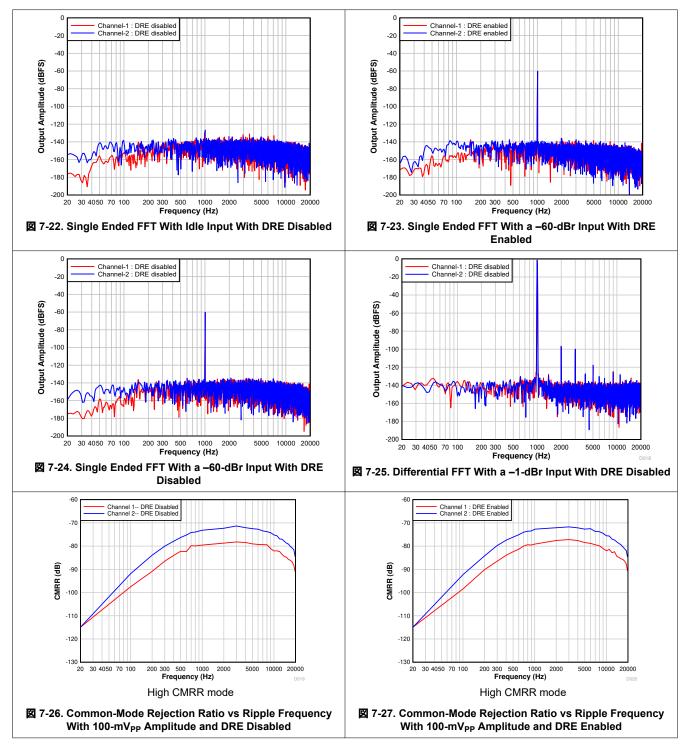

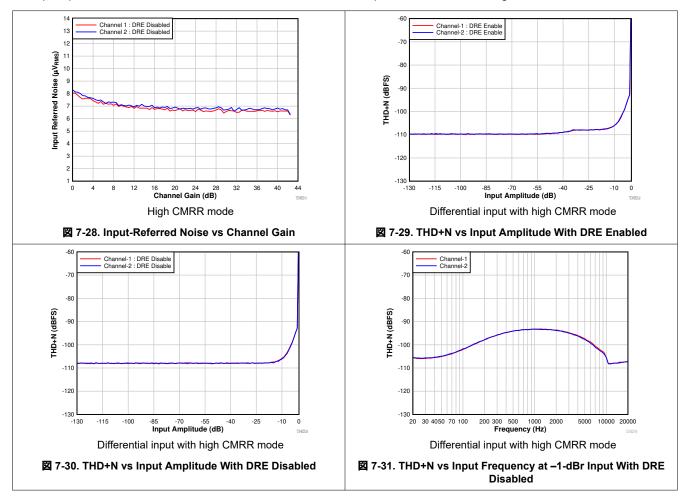

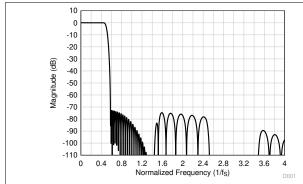

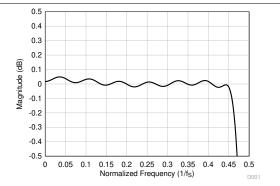

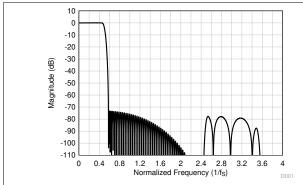

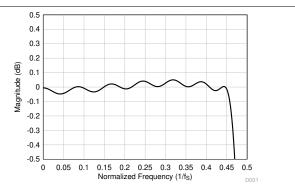

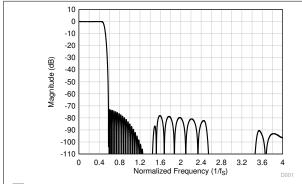

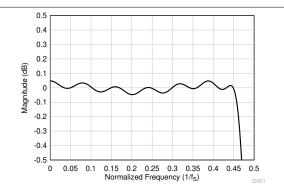

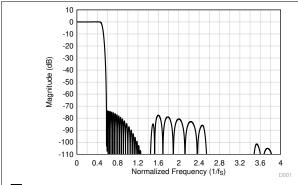

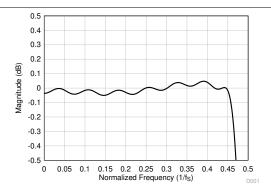

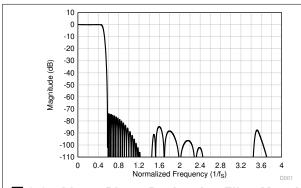

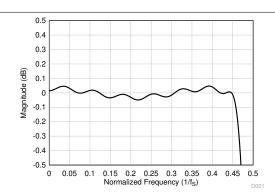

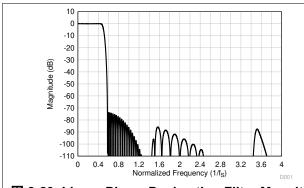

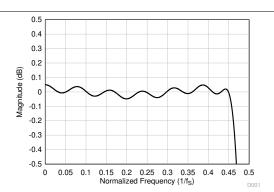

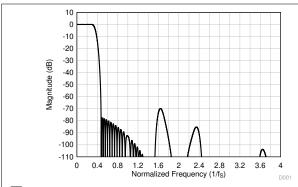

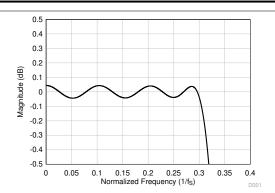

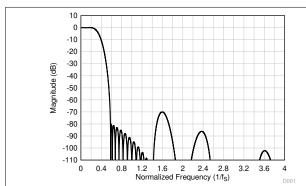

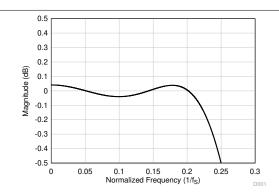

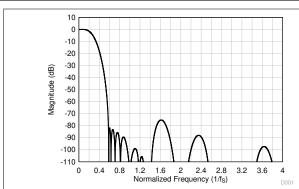

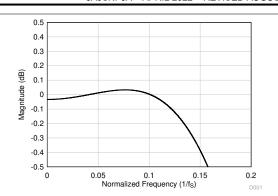

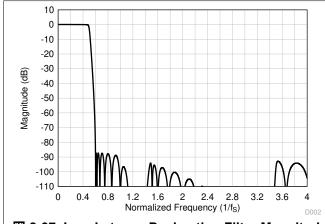

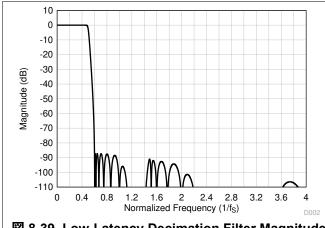

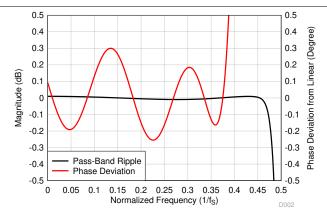

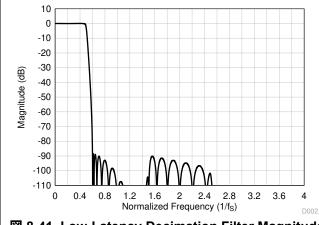

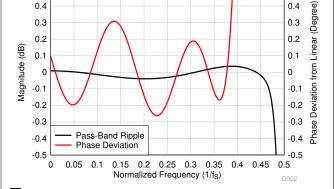

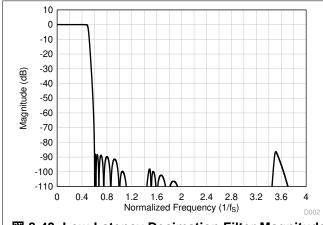

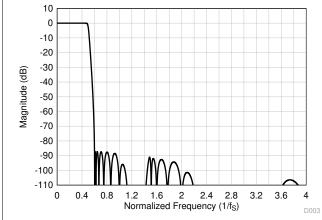

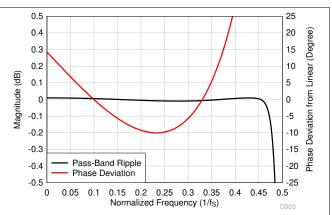

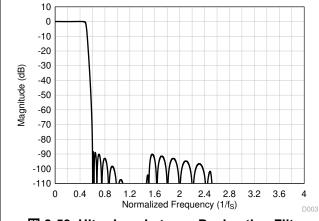

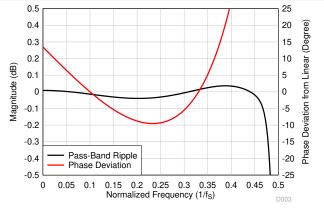

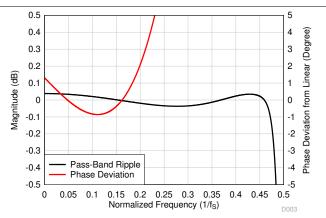

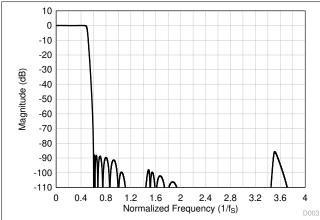

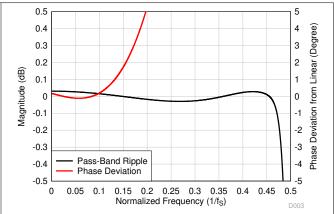

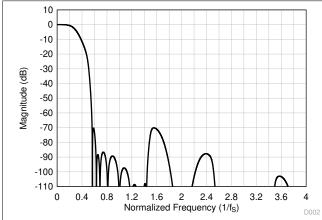

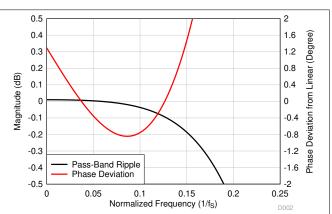

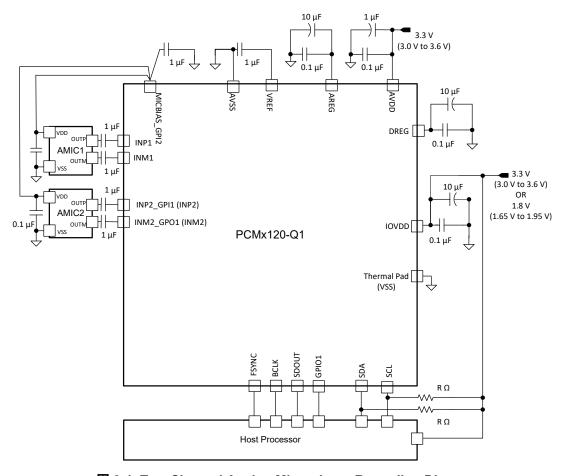

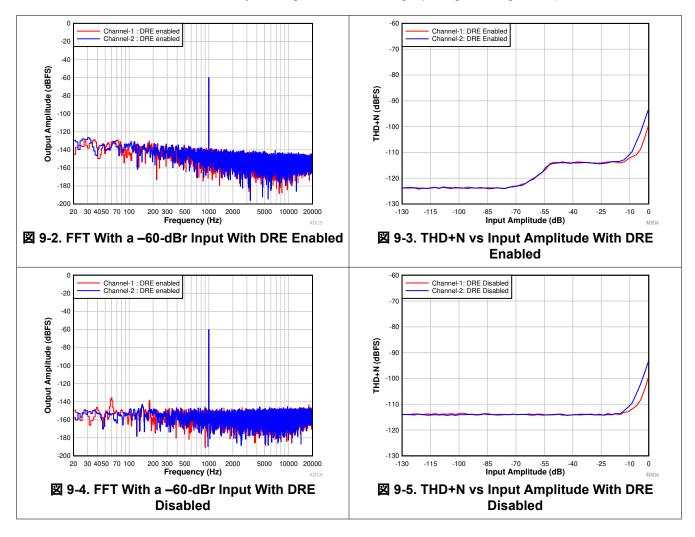

## 7.11 Typical Characteristics

## 8 Detailed Description

#### 8.1 Overview

The PCM6120-Q1 is a high-performance, low-power, flexible, 2-channel, audio analog-to-digital converter (ADC) with extensive feature integration. This device is intended for applications in voice-activated systems, professional microphones, audio conferencing, portable computing, communication, and entertainment applications. The high dynamic range of the device enables far-field audio recording with high fidelity. This device integrates a host of features that reduces cost, board space, and power consumption in space-constrained, battery-powered, consumer, home, and industrial applications.

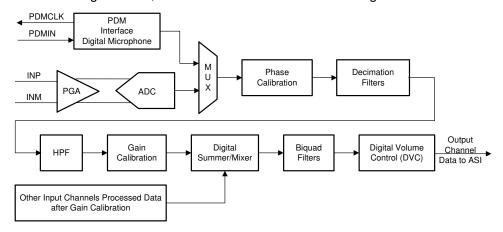

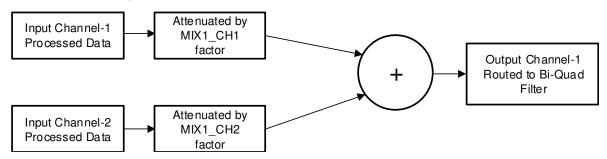

The PCM6120-Q1 consists of the following blocks:

- 2-channel, multibit, high-performance delta-sigma ( $\Delta\Sigma$ ) ADC

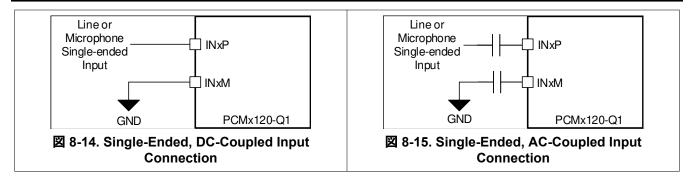

- · Configurable single-ended or differential audio inputs

- Low-noise, programmable microphone bias output