**OPA4830**

# JAJSVY8B - DECEMBER 2006 - REVISED DECEMBER 2024

# OPA4830 クワッド、低消費電力、単一電源、広帯域オペアンプ

#### 1 特長

- 広い帯域幅:

- 230MHz (ゲイン = +1)

- 100MHz (ゲイン = +2)

- 低い消費電流:4.4mA/ch (V<sub>S</sub> = 5V)

- フレキシブルな電源電圧範囲:

- デュアル電源:±1.5V~±5.5V

- シングル電源:3V~11V

- シングル電源の場合、入力範囲はグランドにも対応

- 5V 電源で 4.91V の出力スイング

- 高いスルーレート:560V/µs

- 小さい入力電圧ノイズ:9.2nV/√Hz

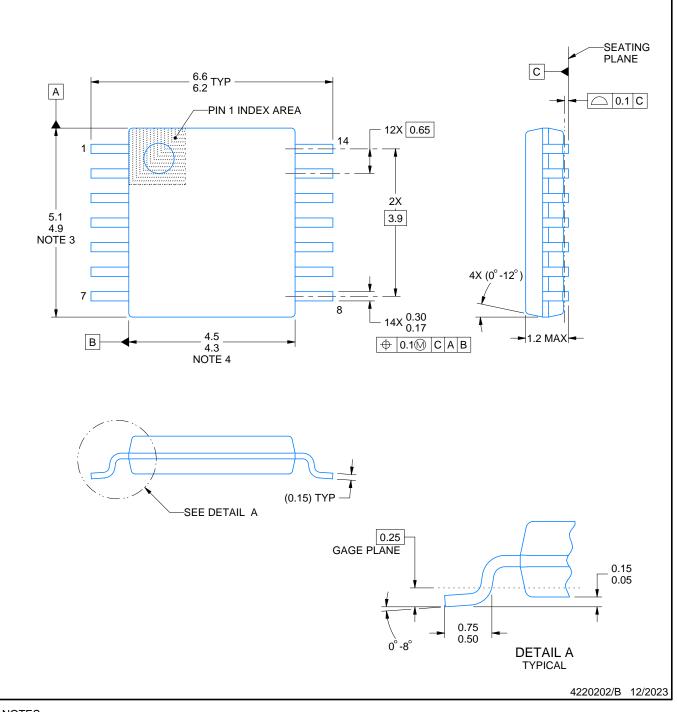

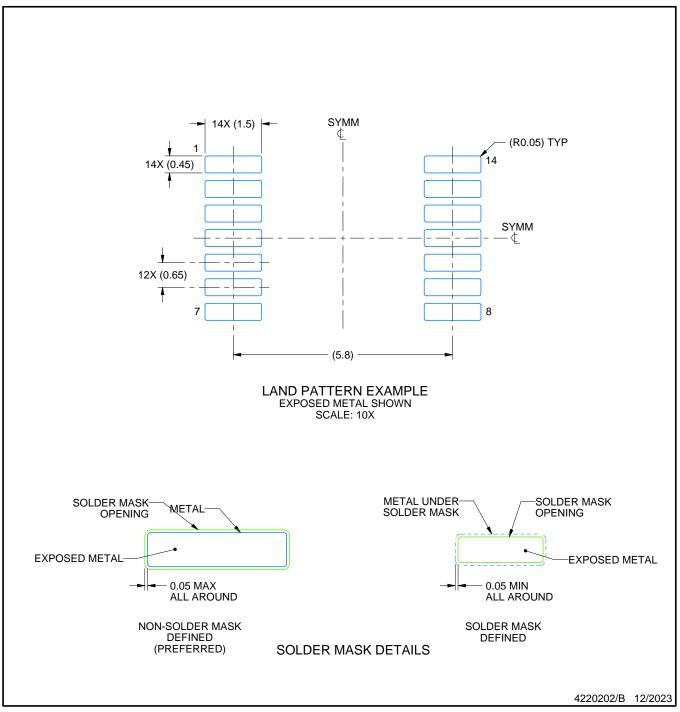

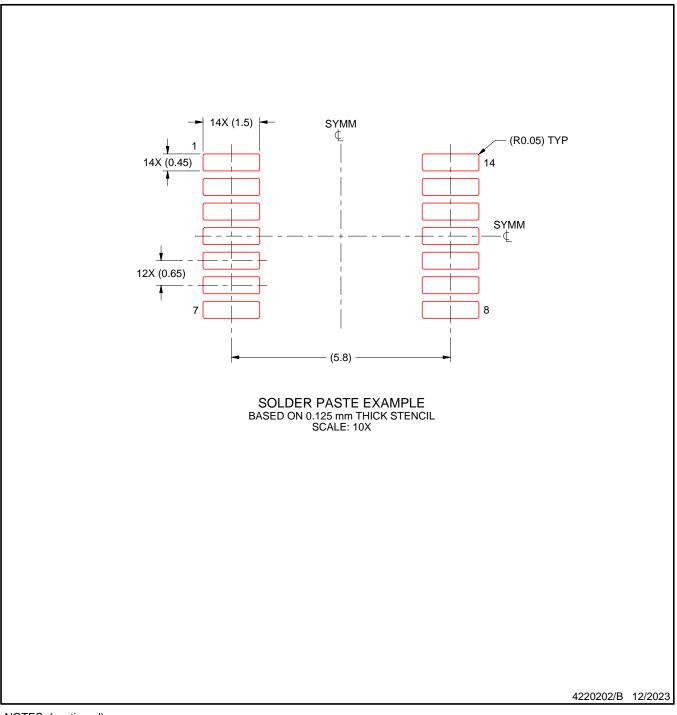

- TSSOP-14 パッケージで供給

# 2 アプリケーション

- ・ 単一電源 A/D コンバータ (ADC) の入力バッファ

- 単一電源ビデオ ラインドライバ

- CCD イメージング チャネル

- アクティブ フィルタ

- **PLL** 積分器

- 携帯型消費者向け電子機器

#### 3 概要

OPA4830 は、クワッド、低消費電力、単一電源、広帯域、 電圧帰還型アンプであり、3V または 5V の単一電源で動 作するよう設計されています。 ±5V または +10V 電源での 動作もサポートしています。入力範囲は、負の電源より低 く、正の電源の 1.8V 以内まで拡張されています。相補的 共通エミッタ出力を使用することにより、150Ωを駆動し て、どちらの電源からも 220mV 以内の出力スイングが得 られます。また、大きい出力駆動電流 (±80mA) と、小さい 差動ゲインおよび位相誤差により、このアンプは単一電源 の消費者向けビデオ製品に最適です。

低歪み動作は、高いゲイン帯域幅積 (110MHz) とスルー レート (560V/µs) により規定されているため、OPA4830 は 3V および 5V の CMOS A/D コンバータ (ADC) への 優れた入力バッファ段となります。他の低消費電力、単電 源のアンプとは異なり、信号振幅が小さくなるにつれて歪 み性能は向上します。入力電圧ノイズが 9.2nV/√Hz と低 いため、広いダイナミック レンジでの動作に対応できま す。

OPA4830 は業界標準のクワッド 14 ピン TSSOP パッケ ージで供給されます。

パッケージ情報

| 部品番号    | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |  |  |  |  |

|---------|----------------------|--------------------------|--|--|--|--|

| OPA4830 | PW (TSSOP、14)        | 5mm × 6.4mm              |  |  |  |  |

- (1) 供給されているすべてのパッケージについては、セクション 11 を 参照してください。

- (2) パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピ ンも含まれます。

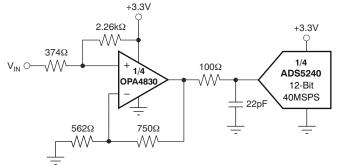

DC 結合、3.3V ADC ドライバ

# **Table of Contents**

| 1 特長                                                                                                                                                                                                                                                                                                                                                                |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 3 概要                                                                                                                                                                                                                                                                                                                                                                |  |

| 4 Related Products.       2         5 Pin Configuration and Functions.       3         6 Specifications.       4         6.1 Absolute Maximum Ratings.       4         6.2 ESD Ratings.       4         6.3 Recommended Operating Conditions.       4         6.4 Thermal Information.       4         6.5 Electrical Characteristics V <sub>S</sub> = ±5V.       5 |  |

| 5 Pin Configuration and Functions.       3         6 Specifications.       4         6.1 Absolute Maximum Ratings.       4         6.2 ESD Ratings.       4         6.3 Recommended Operating Conditions.       4         6.4 Thermal Information.       4         6.5 Electrical Characteristics V <sub>S</sub> = ±5V.       5                                     |  |

| 6 Specifications       4         6.1 Absolute Maximum Ratings       4         6.2 ESD Ratings       4         6.3 Recommended Operating Conditions       4         6.4 Thermal Information       4         6.5 Electrical Characteristics V <sub>S</sub> = ±5V       5                                                                                              |  |

| 6.1 Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                        |  |

| 6.3 Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                |  |

| 6.4 Thermal Information                                                                                                                                                                                                                                                                                                                                             |  |

| 6.5 Electrical Characteristics V <sub>S</sub> = ±5V5                                                                                                                                                                                                                                                                                                                |  |

|                                                                                                                                                                                                                                                                                                                                                                     |  |

|                                                                                                                                                                                                                                                                                                                                                                     |  |

| 6.6 Electrical Characteristics V <sub>S</sub> = 5V7                                                                                                                                                                                                                                                                                                                 |  |

| 6.7 Electrical Characteristics V <sub>S</sub> = 3V9                                                                                                                                                                                                                                                                                                                 |  |

| 6.8 Typical Characteristics: V <sub>S</sub> = ±5V11                                                                                                                                                                                                                                                                                                                 |  |

| 6.9 Typical Characteristics: $V_S = \pm 5V$ , Differential                                                                                                                                                                                                                                                                                                          |  |

| Configuration14                                                                                                                                                                                                                                                                                                                                                     |  |

| 6.10 Typical Characteristics: V <sub>S</sub> = 5V 15                                                                                                                                                                                                                                                                                                                |  |

| 6.11 Typical Characteristics: V <sub>S</sub> = 5V, Differential                                                                                                                                                                                                                                                                                                     |  |

| Configuration19                                                                                                                                                                                                                                                                                                                                                     |  |

| 6.12 Typical Characteristics: V <sub>S</sub> = 3V       | 20 |

|---------------------------------------------------------|----|

| 6.13 Typical Characteristics: $V_s = 3V$ , Differential |    |

| Configuration                                           | 23 |

| 7 Parameter Measurement Information                     | 24 |

| 8 Application and Implementation                        | 25 |

| 8.1 Application Information                             | 25 |

| 8.2 Power Supply Recommendations                        | 39 |

| 8.3 Layout.                                             | 40 |

| 9 Device and Documentation Support                      | 42 |

| 9.1 Device Support                                      | 42 |

| 9.2ドキュメントの更新通知を受け取る方法                                   | 42 |

| 9.3 サポート・リソース                                           | 42 |

| 9.4 Trademarks                                          |    |

| 9.5 静電気放電に関する注意事項                                       | 42 |

| 9.6 用語集                                                 | 43 |

| 10 Revision History                                     | 43 |

| 11 Mechanical, Packaging, and Orderable                 |    |

| Information                                             | 43 |

# **4 Related Products**

| DESCRIPTION                             | SINGLES | DUALS   | TRIPLES | QUADS   |

|-----------------------------------------|---------|---------|---------|---------|

| Rail-to-rail                            | OPA830  | OPA2830 | —       | —       |

| Rail-to-rail fixed-gain                 | OPA832  | OPA2832 | OPA3832 | —       |

| General-purpose<br>(1800V/µs slew rate) | OPA690  | OPA2690 | OPA3690 | _       |

| Low-noise,<br>high dc precision         | OPA820  | OPA2822 | _       | OPA4820 |

OPA4830 JAJSVY8B – DECEMBER 2006 – REVISED DECEMBER 2024

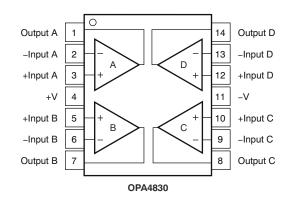

## **5** Pin Configuration and Functions

Top View

## 図 5-1. PW Package, 14-Pin TSSOP (Top View)

| PI       | N   |        |                               |

|----------|-----|--------|-------------------------------|

| NAME     | NO. | TYPE   | DESCRIPTION                   |

| –Input A | 2   | Input  | Inverting input, channel A    |

| –Input B | 6   | Input  | Inverting input, channel B    |

| –Input C | 9   | Input  | Inverting input, channel C    |

| –Input D | 13  | Input  | Inverting input, channel D    |

| +Input A | 3   | Input  | Noninverting input, channel A |

| +Input B | 5   | Input  | Noninverting input, channel B |

| +Input C | 10  | Input  | Noninverting input, channel C |

| +Input D | 12  | Input  | Noninverting input, channel D |

| Output A | 1   | Output | Output, channel A             |

| Output B | 7   | Output | Output, channel B             |

| Output C | 8   | Output | Output, channel C             |

| Output D | 14  | Output | Output, channel D             |

| -V       | 11  | Power  | Negative (lowest) supply      |

| +V       | 4   | Power  | Positive (highest) supply     |

#### 表 5-1. Pin Functions

TSSOP

# 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                      |                            | MIN                       | MAX                       | UNIT            |

|----------------------|----------------------------|---------------------------|---------------------------|-----------------|

| $V_{S-}$ to $V_{S+}$ | Power supply               |                           | ±6.5                      | V <sub>DC</sub> |

|                      | Internal power dissipation | See Thermal Informat      | ion Table                 |                 |

| V <sub>ID</sub>      | Differential input voltage |                           | ±2.5                      | V               |

| VI                   | Input voltage              | (V <sub>S-</sub> ) – 0.5V | (V <sub>S+</sub> ) + 0.3V | V               |

| TJ                   | Junction temperature       |                           | 150                       | °C              |

| T <sub>stg</sub>     | Storage temperature        | -65                       | 125                       | °C              |

(1) Operation outside the Absolute Maximum Ratings causes permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device can not be fully functional, and this can affect device reliability, functionality, performance, and shorten the device lifetime.

#### 6.2 ESD Ratings

|   |       |                          |                                                                                | VALUE | UNIT |

|---|-------|--------------------------|--------------------------------------------------------------------------------|-------|------|

|   | /     | Electrostatic discharge  | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 | V    |

| ľ | (ESD) | Electrostatic discriarge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1000 | v    |

(1) JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

#### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                       | MIN | NOM | MAX | UNIT |

|----------------|-----------------------|-----|-----|-----|------|

| Vs             | Total supply voltage  | 3   | 10  | 11  | V    |

| T <sub>A</sub> | Operating temperature | -40 |     | 85  | °C   |

#### 6.4 Thermal Information

|                       |                                              | OPA4830    |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PW (TSSOP) | UNIT |

|                       |                                              | 14 PINS    |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 109.6      | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 36.6       | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 66.0       | °C/W |

| Ψ <sub>JT</sub>       | Junction-to-top characterization parameter   | 1.6        | °C/W |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 65.2       | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 6.5 Electrical Characteristics $V_S = \pm 5V$

at  $T_A = 25^{\circ}C^{(1)}$ , G = +2,  $R_F = 750\Omega$ ,  $R_L = 150\Omega$  to GND, and  $R_{SRC} = 375\Omega$  (unless otherwise noted)

| PARAMETER                          | TEST CONDITIONS                                                                   | MIN | TYP       | MAX  | UNITS   |  |

|------------------------------------|-----------------------------------------------------------------------------------|-----|-----------|------|---------|--|

| AC PERFORMANCE                     |                                                                                   |     |           |      |         |  |

|                                    | $G = +1, V_O \le 0.2V_{PP}$                                                       |     | 290       |      |         |  |

| Small-signal bandwidth             | $G = +2, V_O \le 0.2V_{PP}$                                                       | 66  | 100       |      | MHz     |  |

|                                    | $G = +5, V_O \le 0.2V_{PP}$                                                       | 16  | 30        |      |         |  |

|                                    | $G = +10, V_O \le 0.2V_{PP}$                                                      | 8   | 13        |      |         |  |

| Gain bandwidth product             | G ≥ +10                                                                           | 80  | 130       |      | MHz     |  |

| Peaking at a gain of +1            | $V_{O} \leq 0.2V_{PP}$                                                            |     | 4         |      | dB      |  |

| Slew rate                          | G = +2, 2V step, 20% to 80%                                                       | 275 | 560       |      | V/µs    |  |

| Rise time                          | 0.5V step, 20% to 80%                                                             |     | 3.4       | 5.9  | ns      |  |

| Fall time                          | 0.5V step, 20% to 80%                                                             |     | 3.6       | 6.0  | ns      |  |

| Settling time to 0.1%              | G = +2, 1V step                                                                   |     | 43        | 64   | ns      |  |

|                                    | 2nd-harmonic, $V_0 = 2V_{PP}$ , f = 5MHz, R <sub>L</sub> = 150 $\Omega$           | -55 | -62       |      |         |  |

|                                    | 2nd-harmonic, $V_O = 2V_{PP}$ , f = 5MHz, $R_L \ge 500\Omega$                     | -58 | -66       |      |         |  |

| Harmonic distortion                | 3rd-harmonic, $V_0 = 2V_{PP}$ , f = 5MHz, R <sub>L</sub> = 150 $\Omega$           | -50 | -59       |      | dBc     |  |

|                                    | 3rd-harmonic, V <sub>O</sub> = 2V <sub>PP</sub> , f = 5MHz, R <sub>L</sub> ≥ 500Ω | -65 | -77       |      |         |  |

|                                    | f > 1MHz                                                                          |     | 5.6       | 10.6 |         |  |

| Input voltage noise                | f > 1MHz, T <sub>A</sub> = -40°C to +85°C                                         |     |           | 11.6 | nV/√ Hz |  |

|                                    | f > 1MHz                                                                          |     | 3.7       | 5.4  | pA/√Hz  |  |

| nput current noise                 | f > 1MHz, T <sub>A</sub> = -40°C to +85°C                                         |     |           | 6.4  |         |  |

| DC PERFORMANCE                     |                                                                                   |     |           |      |         |  |

|                                    | $V_{O} = \pm 1 V$                                                                 | 66  | 74        |      |         |  |

| Open-loop voltage gain             | $V_{O} = \pm 1V$ , $T_{A} = -40^{\circ}C$ to $+85^{\circ}C$                       | 64  |           |      | dB      |  |

|                                    |                                                                                   |     | ±1.5      | ±7.5 |         |  |

| Input offset voltage               | $T_A = -40^{\circ}C$ to $+85^{\circ}C$                                            |     |           | ±9.3 | mV      |  |

| Average offset voltage drift       | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$                                   |     |           | ±27  | µV/°C   |  |

|                                    | V <sub>CM</sub> = 2V                                                              |     | 5         | 18   |         |  |

| Input bias current                 | $V_{CM} = 2V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                        |     |           | 19   | μA      |  |

| Input bias current drift           | $V_{CM} = 0V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                        |     |           | ±46  | nA/°C   |  |

|                                    | V <sub>CM</sub> = 2V                                                              |     | ±0.2      | ±1.1 |         |  |

| Input offset current               | $V_{CM} = 2V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                        |     |           | ±1.5 | μA      |  |

| Input offset current drift         | $V_{CM} = 0V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                        |     |           | ±6   | nA/°C   |  |

| INPUT                              |                                                                                   |     |           |      |         |  |

|                                    | 0.4V step                                                                         |     | -5.5      | -5.4 |         |  |

| Negative input voltage             | 0.4V step, $T_A = -40^{\circ}$ C to +85°C                                         |     |           | -5.2 | V       |  |

|                                    | 0.4V step                                                                         | 3.1 | 3.2       | _    |         |  |

| Positive input voltage             | 0.4V step, $T_A = -40^{\circ}$ C to +85°C                                         | 2.9 |           |      | V       |  |

|                                    | Input-referred                                                                    | 76  | 80        |      |         |  |

| Common-mode rejection ratio (CMRR) | Input-referred, $T_A = -40^{\circ}C$ to +85°C                                     | 71  |           |      | dB      |  |

|                                    | Differential mode                                                                 |     | 10    2.1 |      |         |  |

| Input impedance                    | Common-mode                                                                       |     | 00    1.2 |      | kΩ∥pF   |  |

# 6.5 Electrical Characteristics $V_S = \pm 5V$ (続き)

at  $T_A = 25^{\circ}C^{(1)}$ , G = +2,  $R_F = 750\Omega$ ,  $R_L = 150\Omega$  to GND, and  $R_{SRC} = 375\Omega$  (unless otherwise noted)

| PARAMETER                            | TEST CONDITIONS                                             | MIN   | TYP   | MAX  | UNITS |

|--------------------------------------|-------------------------------------------------------------|-------|-------|------|-------|

| Ουτρυτ                               |                                                             |       |       |      |       |

| Output voltage swing                 | $R_L = 1k\Omega$ to GND                                     | ±4.86 | ±4.88 |      | V     |

|                                      | $R_L$ = 1k $\Omega$ to GND, $T_A$ = -40°C to +85°C          | ±4.84 |       |      |       |

|                                      | $R_L = 150\Omega$ to GND                                    | ±4.60 | ±4.64 |      | v     |

|                                      | $R_L$ = 150 $\Omega$ to GND, $T_A$ = -40°C to +85°C         | ±4.56 |       |      |       |

| Current output, sinking and sourcing | V <sub>O</sub> = ±2.75V, V <sub>OS</sub> = 20mV             | ±63   | ±82   |      | mA    |

|                                      | $V_{O}$ = ±2.75V, $V_{OS}$ = 20mV, $T_{A}$ = -40°C to +85°C | ±53   |       |      |       |

| Short-circuit current                | Output shorted to ground                                    |       | 120   |      | mA    |

| Closed-loop output impedance         | G = +2, f ≤ 100kHz                                          |       | 0.03  | Ω    | Ω     |

| POWER SUPPLY                         |                                                             |       |       |      |       |

| Quiescent current                    |                                                             | 15.2  | 18    | 21.2 | mA    |

| Quiescent current                    | $T_A = -40^{\circ}C$ to $+85^{\circ}C$                      | 12.4  |       | 24.4 | mA    |

| Power supply rejection ratio ( DSPP) | Input-referred, 1V step                                     | 61    | 66    |      | dB    |

| Power-supply rejection ratio (–PSRR) | Input-referred, $T_A = -40^{\circ}C$ to +85°C               | 59    |       |      | uБ    |

(1) Junction temperature = ambient for 25°C specifications.

# 6.6 Electrical Characteristics V<sub>S</sub> = 5V

at  $T_A = 25^{\circ}C^{(1)}$ , G = +2,  $R_F = 750\Omega$ , and  $R_L = 150\Omega$  to GND (unless otherwise noted)

| PARAMETER                               | TEST CONDITIONS                                                         | MIN     | TYP       | MAX  | UNITS              |  |

|-----------------------------------------|-------------------------------------------------------------------------|---------|-----------|------|--------------------|--|

| AC PERFORMANCE                          |                                                                         |         |           |      |                    |  |

|                                         | $G = +1, V_O \le 0.2V_{PP}$                                             |         | 230       |      |                    |  |

| Small-signal bandwidth                  | $G = +2, V_O \le 0.2V_{PP}$                                             | 70      | 100       |      | MHz                |  |

|                                         | $G = +5, V_O \le 0.2 V_{PP}$                                            | 15      | 21        |      | 111112             |  |

|                                         | $G = +10, V_O \le 0.2V_{PP}$                                            | 7       | 10        |      |                    |  |

| Gain bandwidth product                  | G ≥ +10                                                                 | 75      | 100       |      | MHz                |  |

| Peaking at a gain of +1                 | $V_{O} \leq 0.2V_{PP}$                                                  |         | 4         |      | dB                 |  |

| Slew rate                               | G = +2, 2V step, 20% to 80%                                             | 270     | 500       |      | V/µs               |  |

| Rise time                               | 0.5V step, 20% to 80%                                                   |         | 3.4       | 5.8  | ns                 |  |

| Fall time                               | 0.5V step, 20% to 80%                                                   |         | 3.4       | 5.8  | ns                 |  |

| Settling time to 0.1%                   | G = +2, 1V step                                                         |         | 44        | 65   | ns                 |  |

|                                         | 2nd-harmonic, $V_0 = 2V_{PP}$ , f = 5MHz, $R_L = 150\Omega$             | -52     | -58       |      |                    |  |

| Llormonia distortion                    | 2nd-harmonic, $V_0 = 2V_{PP}$ , f = 5MHz, $R_L \ge 500\Omega$           | -56     | -62       |      | dDo                |  |

| Harmonic distortion                     | 3rd-harmonic, $V_O = 2V_{PP}$ , f = 5MHz, R <sub>L</sub> = 150 $\Omega$ | -50     | -58       |      | dBc                |  |

|                                         | 3rd-harmonic, $V_O = 2V_{PP}$ , f = 5MHz, $R_L \ge 500\Omega$           | -65     | -84       |      |                    |  |

| lument and the merice of a second       | f > 1MHz                                                                |         | 5.8       | 10.3 |                    |  |

| Input voltage noise                     | f > 1MHz, T <sub>A</sub> = -40°C to +85°C                               |         |           | 11.3 | nV/√ <del>Hz</del> |  |

| land a sum of the land                  | f > 1MHz                                                                |         | 4         | 5.4  |                    |  |

| Input current noise                     | f > 1MHz, T <sub>A</sub> = -40°C to +85°C                               |         |           | 6.4  | pA/√ <del>Hz</del> |  |

| All Hostile Crosstalk, Input - Referred | 3 Channels Driven at 5MHz, 1VPP, 4th Channel Measured                   |         | -62       |      | dB                 |  |

| DC PERFORMANCE                          |                                                                         |         |           | 1    |                    |  |

|                                         | V <sub>O</sub> = ±1V                                                    | 66      | 72        |      |                    |  |

| Open-loop voltage gain                  | $V_{O} = \pm 1V$ , $T_{A} = -40^{\circ}C$ to $+85^{\circ}C$             | 64      |           |      | dB                 |  |

| land the standard                       |                                                                         |         | ±0.5      | ±5.5 |                    |  |

| Input offset voltage                    | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                           |         |           | ±7.0 | mV                 |  |

| Average offset voltage drift            | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                           |         |           | ±22  | µV/°C              |  |

|                                         | V <sub>CM</sub> = 2.5V                                                  |         | +5        | +18  |                    |  |

| Input bias current                      | $V_{CM}$ = 2.5V, $T_A$ = -40°C to +85°C                                 |         |           | +18  | μA                 |  |

| Input bias current drift                | $V_{CM}$ = 2.5V, $T_{A}$ = -40°C to +85°C                               |         |           | ±46  | nA/°C              |  |

|                                         | V <sub>CM</sub> = 2.5V                                                  |         | ±0.2      | ±0.9 |                    |  |

| Input offset current                    | $V_{CM}$ = 2.5V, $T_A$ = -40°C to +85°C                                 |         |           | ±1.3 | μA                 |  |

| Input offset current drift              | $V_{CM}$ = 2.5V, $T_A$ = -40°C to +85°C                                 |         |           | ±6   | nA/°C              |  |

| INPUT                                   |                                                                         |         |           |      |                    |  |

|                                         | 0.4V step                                                               |         | -0.5      | -0.4 |                    |  |

| Negative input voltage                  | 0.4V step, $T_A = -40^{\circ}C$ to +85°C                                |         |           | -0.2 | V                  |  |

|                                         | 0.4V step                                                               | 3.1 3.2 |           |      |                    |  |

| Positive input voltage                  | 0.4V step, $T_A = -40^{\circ}$ C to +85°C                               | 2.9     |           |      | V                  |  |

|                                         | Input-referred                                                          | 76      | 80        |      |                    |  |

| Common-mode rejection ratio (CMRR)      | Input-referred, $T_A = -40^{\circ}C$ to +85°C                           | 71      |           |      | dB                 |  |

|                                         | Differential mode                                                       |         | 10    2.1 |      |                    |  |

| Input impedance                         |                                                                         |         |           |      | kΩ    pF           |  |

# 6.6 Electrical Characteristics $V_S = 5V$ (続き)

at  $T_A = 25^{\circ}C^{(1)}$ , G = +2,  $R_F = 750\Omega$ , and  $R_L = 150\Omega$  to GND (unless otherwise noted)

| PARAMETER                            | TEST CONDITIONS                                                                  | MIN  | ТҮР  | MAX  | UNITS |

|--------------------------------------|----------------------------------------------------------------------------------|------|------|------|-------|

| OUTPUT                               |                                                                                  |      |      |      |       |

| Output voltage swing low             | G = +5, $R_L$ = 1k $\Omega$ to 2.5V                                              |      |      | 0.09 |       |

|                                      | G = +5, R <sub>L</sub> = 1k $\Omega$ to 2.5V, T <sub>A</sub> = -40°C to +85°C    | ·    |      | 0.13 | V     |

|                                      | G = +5, $R_L$ = 150 $\Omega$ to 2.5V                                             |      |      | 0.21 |       |

|                                      | G = +5, R <sub>L</sub> = 150 $\Omega$ to 2.5V, T <sub>A</sub> = -40°C to +85°C   |      |      | 0.26 |       |

| Output voltage swing high            | G = +5, $R_L$ = 1k $\Omega$ to 2.5V                                              | 4.91 |      |      |       |

|                                      | G = +5, R <sub>L</sub> = 1k $\Omega$ to 2.5V, T <sub>A</sub> = -40°C to +85°C    | 4.87 |      |      | V     |

|                                      | G = +5, $R_L$ = 150 $\Omega$ to 2.5V                                             | 4.78 |      |      |       |

|                                      | G = +5, R <sub>L</sub> = 150 $\Omega$ to 2.5V, T <sub>A</sub> = -40°C to +85°C   | 4.72 |      |      |       |

| Current output, sinking and sourcing | V <sub>O</sub> = ±0.88V, V <sub>OS</sub> = 20mV                                  | ±58  | ±75  |      | mA    |

|                                      | $V_{O} = \pm 0.88V$ , $V_{OS} = 20mV$ , $T_{A} = -40^{\circ}C$ to $+85^{\circ}C$ | ±50  |      |      |       |

| Short-circuit current                | Output shorted to either supply                                                  |      | 125  |      | mA    |

| Closed-loop output impedance         | G = +2, f ≤ 100kHz                                                               |      | 0.06 |      | Ω     |

| POWER SUPPLY                         |                                                                                  |      |      |      |       |

| Quiescent current                    |                                                                                  | 14.8 | 17.6 | 20   | mA    |

|                                      | $T_A = -40^{\circ}C$ to $+85^{\circ}C$                                           | 12.4 |      | 22.8 |       |

| Quiescent Current                    | $T_{A} = -40^{\circ}C \text{ to } +125^{\circ}C$                                 | 12.4 |      | 25.2 | mA    |

| Power-supply rejection ratio (PSRR)  | Input-referred, 0.5V step                                                        | 61   | 66   |      | dB    |

|                                      | Input-referred, $T_A = -40^{\circ}C$ to +85°C                                    | 59   |      |      | uБ    |

(1) Junction temperature = ambient for +25°C specifications.

# 6.7 Electrical Characteristics V<sub>S</sub> = 3V

at  $T_A = 25^{\circ}C^{(1)}$ , G = +2,  $R_F = 750\Omega$ , and  $R_L = 150\Omega$  to  $V_S/3$  (unless otherwise noted)

| PARAMETER                            | TEST CONDITIONS                                                                | MIN | TYP        | MAX   | UNITS    |  |

|--------------------------------------|--------------------------------------------------------------------------------|-----|------------|-------|----------|--|

| AC PERFORMANCE                       |                                                                                |     |            |       |          |  |

| Small-signal bandwidth               | $G = +2, V_O \le 0.2V_{PP}$                                                    | 70  | 90         |       |          |  |

|                                      | $G = +5, V_O \le 0.2V_{PP}$                                                    | 15  | 20         |       | MHz      |  |

|                                      | $G = +10, V_O \le 0.2 V_{PP}$                                                  | 7.5 | 9          |       |          |  |

| Gain bandwidth product               | G ≥ +10                                                                        | 75  | 90         |       | MHz      |  |

| Slew rate                            | G = +2, 1V step, 20% to 80%                                                    | 135 | 220        |       | V/µs     |  |

| Rise time                            | 0.5V step, 20% to 80%                                                          |     | 3.4        | 5.6   | ns       |  |

| Fall time                            | 0.5V step, 20% to 80%                                                          |     | 3.4        | 5.6   | ns       |  |

| Settling time to 0.1%                | G = +2, 1V step                                                                |     | 46         | 73    | ns       |  |

|                                      | 2nd-harmonic, $V_0 = 1V_{PP}$ , f = 5MHz, $R_L = 150\Omega$                    | -56 | -60        |       |          |  |

| Harmonic distortion                  | 2nd-harmonic, $V_0 = 1V_{PP}$ , f = 5MHz, $R_L \ge 500\Omega$                  | -59 | -64        |       | dBc      |  |

|                                      | 3rd-harmonic, $V_0 = 1V_{PP}$ , f = 5MHz, R <sub>L</sub> = 150 $\Omega$        | -59 | -68        |       |          |  |

|                                      | 3rd-harmonic, $V_O = 1V_{PP}$ , f = 5MHz, $R_L \ge 500\Omega$                  | -65 | -72        |       |          |  |

|                                      | f > 1MHz                                                                       |     | 5.8        | 10.3  | ∣ nV/√ H |  |

| Input voltage noise                  | f > 1MHz, T <sub>A</sub> = 0°C to 70°C                                         |     |            | 10.8  |          |  |

|                                      | f > 1MHz                                                                       |     | 4          | 5.4   | • • • •  |  |

| Input current noise                  | f > 1MHz, T <sub>A</sub> = 0°C to 70°C                                         |     |            | 6.2   | pA/√ Ħ   |  |

| DC PERFORMANCE                       |                                                                                |     |            | I     |          |  |

|                                      | $V_{O} = \pm 0.5 V$                                                            | 66  | 72         |       |          |  |

| Open-loop voltage gain               | $V_{O} = \pm 0.5V$ , $T_{A} = 0^{\circ}C$ to $70^{\circ}C$                     | 65  |            |       | dB       |  |

|                                      |                                                                                |     | ±1.5       | ±7.5  | mV       |  |

| nput offset voltage                  | $T_A = 0^{\circ}C \text{ to } 70^{\circ}C$                                     |     |            | ±8.7  |          |  |

| Average offset voltage drift         | $T_A = 0^{\circ}C \text{ to } 70^{\circ}C$                                     |     |            | ±27   | µV/°C    |  |

|                                      | V <sub>CM</sub> = 1.0V                                                         |     | +5         | +18   |          |  |

| nput bias current                    | $V_{CM} = 1.0V, T_A = 0^{\circ}C \text{ to } 70^{\circ}C$                      |     |            | ±18   | - μA     |  |

| nput bias current drift              | $V_{CM} = 1.0V, T_A = 0^{\circ}C$ to 70°C                                      |     |            | ±44   | nA/°C    |  |

| -                                    | V <sub>CM</sub> = 1.0V                                                         |     | ±0.2       | ±1.1  | μΑ       |  |

| Input offset current                 | $V_{CM} = 1.0V, T_A = 0^{\circ}C \text{ to } 70^{\circ}C$                      |     |            | ±1.3  |          |  |

| Input offset current drift           | $V_{CM} = 1.0V, T_A = 0^{\circ}C$ to 70°C                                      |     |            | ±5    | nA/°C    |  |

| INPUT                                |                                                                                |     |            |       | 10.0     |  |

|                                      | 0.4V step                                                                      |     | -0.45      | -0.4  |          |  |

| Negative input voltage               | $T_A = 0^{\circ}C$ to +70°C, 0.4V step                                         |     | -0.40      | -0.27 | V        |  |

|                                      | 0.4V step                                                                      | 1.1 | 1.2        | -0.27 |          |  |

| Positive input voltage               | $T_A = 0^{\circ}C$ to +70°C, 0.4V step                                         | 1.1 | 1.2        |       | V        |  |

| Common-mode rejection ratio (CMRR)   | Input-referred                                                                 | 74  | 90         |       | dB       |  |

|                                      |                                                                                | 74  | 80         |       |          |  |

|                                      | Input-referred, $T_A = 0^{\circ}C$ to $70^{\circ}C$                            | 12  | 40 11 0 4  |       | dB       |  |

| Input impedance                      | Differential mode                                                              |     | 10    2.1  |       | kΩ    p  |  |

|                                      | Common-mode                                                                    | 4   | 400    1.2 |       |          |  |

| OUTPUT                               |                                                                                |     |            |       |          |  |

| Current output, sinking and sourcing | $V_{O} = \pm 0.125 V, V_{OS} = 20 mV$                                          | ±20 | ±30        |       | mA       |  |

| e                                    | $V_{O} = \pm 0.125V$ , $V_{OS} = 20mV$ , $T_{A} = 0^{\circ}C$ to $70^{\circ}C$ | ±18 |            |       |          |  |

| Short-circuit current                | Output shorted to either supply                                                |     | 120        |       | mA       |  |

| Closed-loop output impedance         | G = +2, f ≤ 100kHz                                                             |     | 0.06       |       | Ω        |  |

# 6.7 Electrical Characteristics $V_S = 3V$ (続き)

at  $T_A = 25^{\circ}C^{(1)}$ , G = +2,  $R_F = 750\Omega$ , and  $R_L = 150\Omega$  to  $V_S/3$  (unless otherwise noted)

| PARAMETER                           | TEST CONDITIONS                                     | MIN  | TYP  | MAX  | UNITS |  |  |

|-------------------------------------|-----------------------------------------------------|------|------|------|-------|--|--|

| POWER SUPPLY                        |                                                     |      |      |      |       |  |  |

| Quiescent current                   |                                                     | 14   | 17.2 | 19.6 | mA    |  |  |

|                                     | $T_A = 0^{\circ}C$ to +70°C                         | 12.4 |      | 22   |       |  |  |

| Quiescent current at 2.8V supply    |                                                     | 13.2 | 17.2 | 19.2 | mA    |  |  |

|                                     | $T_A = 0^{\circ}C$ to +70°C                         | 12.4 |      | 22   |       |  |  |

| Power-supply rejection ratio (PSRR) | Input-referred, 0.3V step                           | 60   | 64   |      | dB    |  |  |

|                                     | Input-referred, $T_A = 0^{\circ}C$ to $70^{\circ}C$ | 58   |      |      |       |  |  |

(1) Junction temperature = ambient for +25°C specifications.

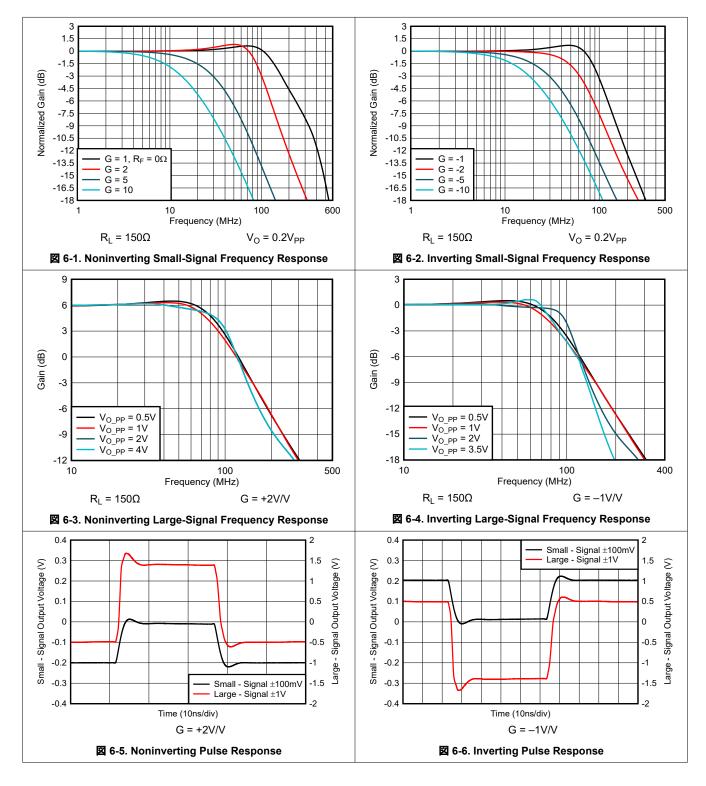

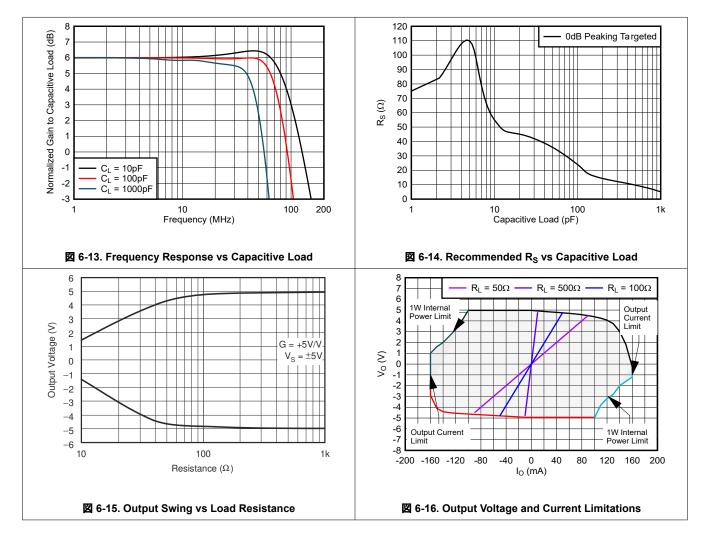

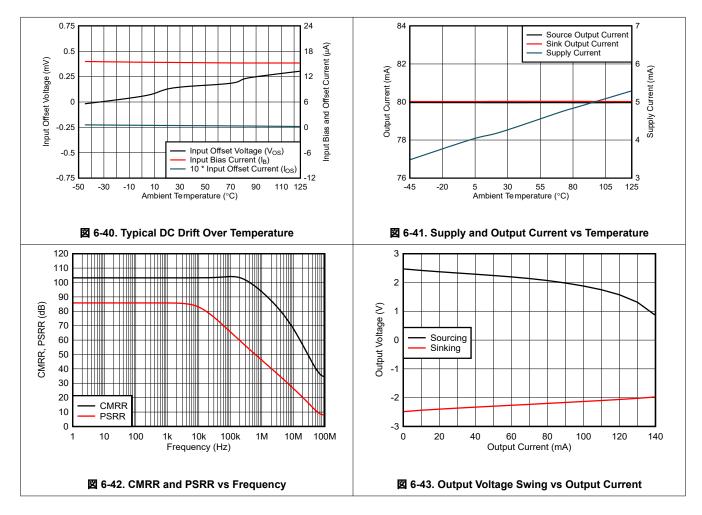

#### 6.8 Typical Characteristics: V<sub>S</sub> = ±5V

at T<sub>A</sub> = 25°C, G = +2V/V, R<sub>F</sub> = 750 $\Omega$ , and R<sub>L</sub> = 150 $\Omega$  to GND (unless otherwise noted); see  $\mathbb{X}$  8-3

# 6.8 Typical Characteristics: V<sub>S</sub> = ±5V (continued)

at  $T_A = 25^{\circ}C$ , G = +2V/V,  $R_F = 750\Omega$ , and  $R_L = 150\Omega$  to GND (unless otherwise noted); see 🗵 8-3

## 6.8 Typical Characteristics: V<sub>S</sub> = ±5V (continued)

at T<sub>A</sub> = 25°C, G = +2V/V, R<sub>F</sub> = 750 $\Omega$ , and R<sub>L</sub> = 150 $\Omega$  to GND (unless otherwise noted); see  $\boxtimes$  8-3

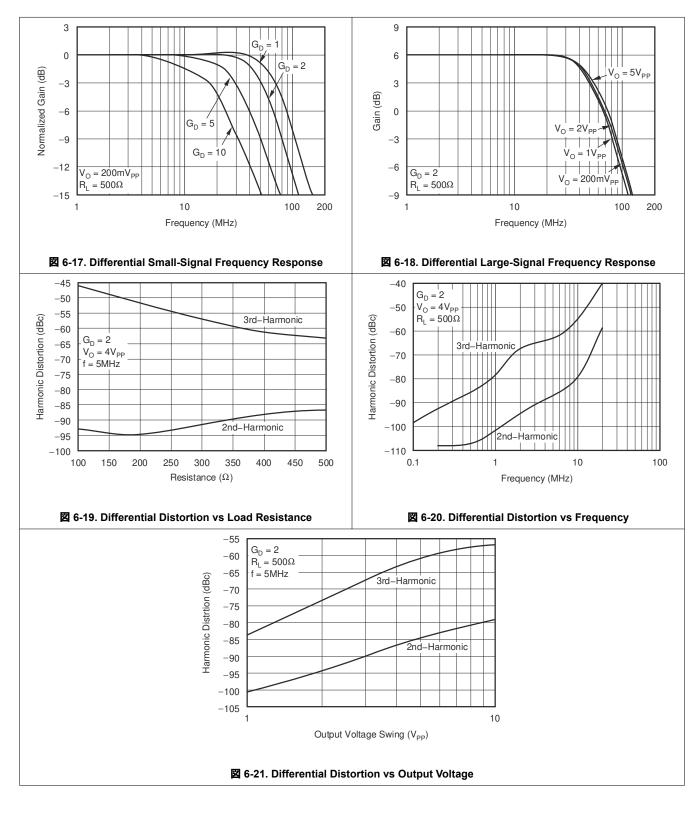

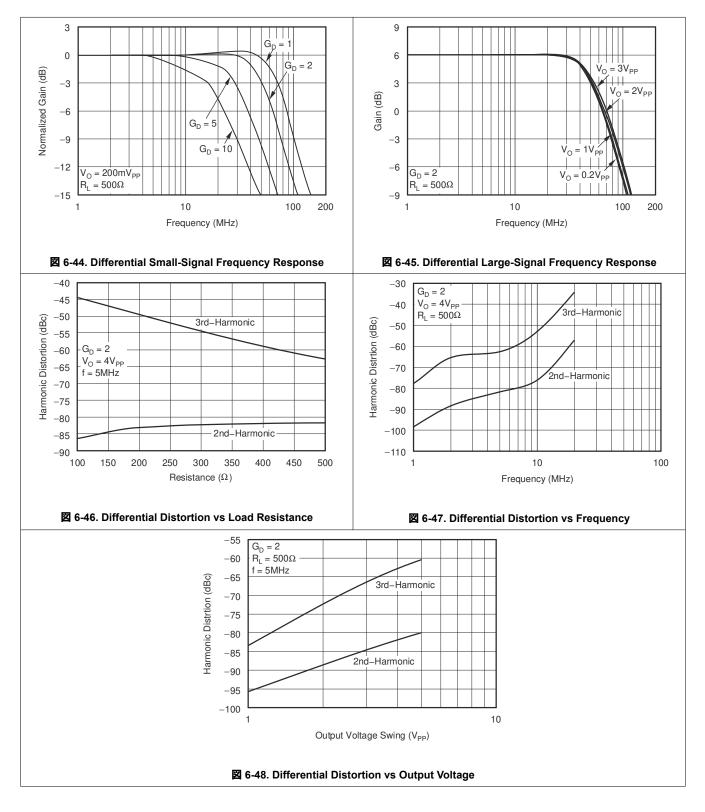

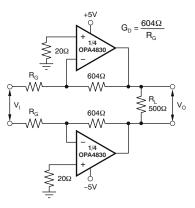

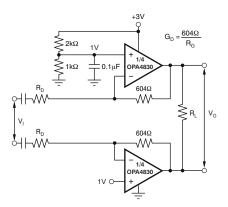

# 6.9 Typical Characteristics: $V_S = \pm 5V$ , Differential Configuration

At  $T_A = 25^{\circ}$ C,  $R_F = 604\Omega$  (see  $\boxtimes$  7-1), and  $R_L = 500\Omega$  (unless otherwise noted)

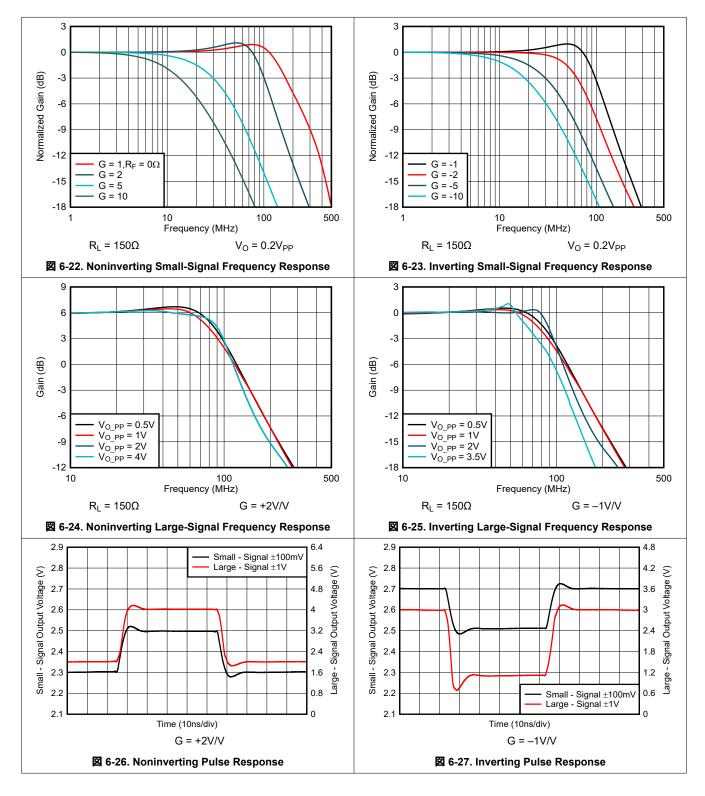

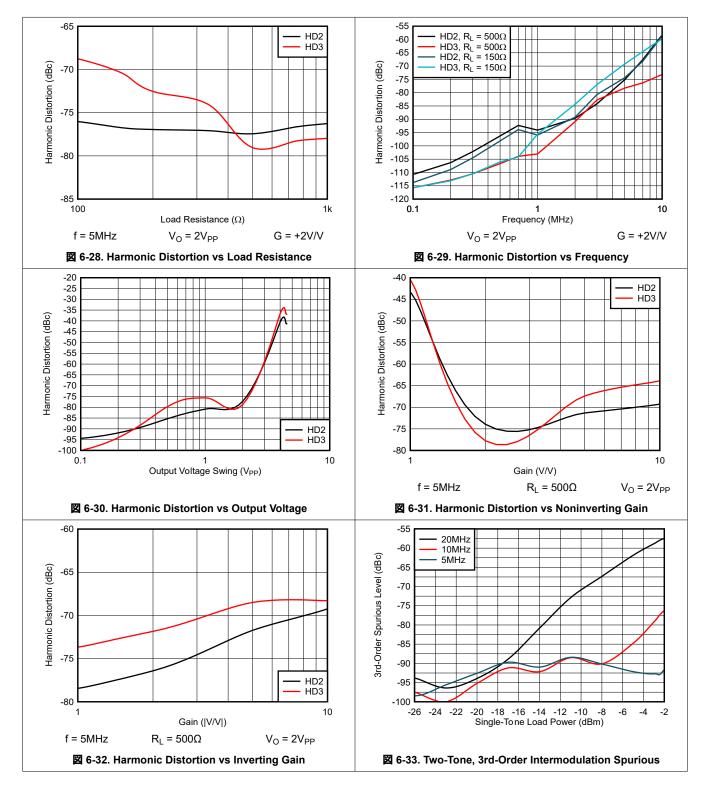

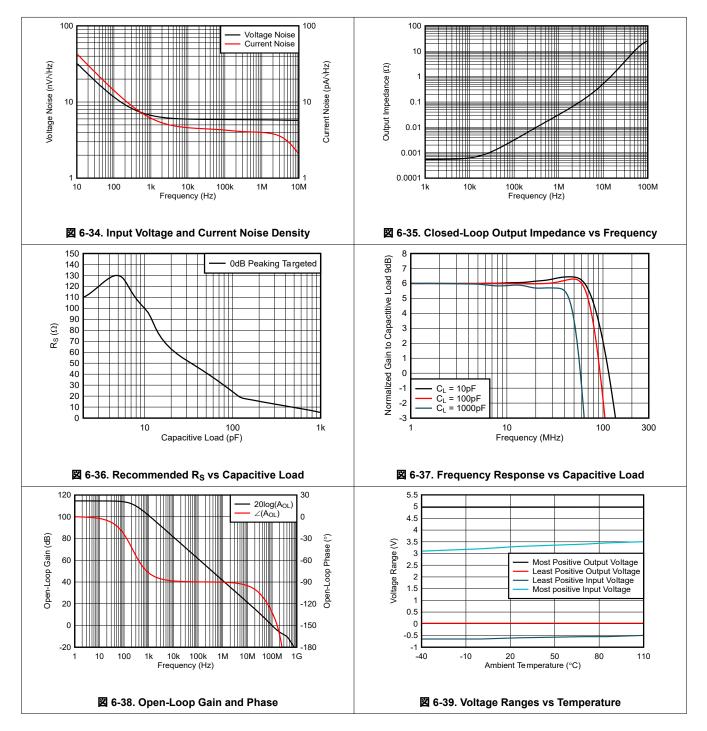

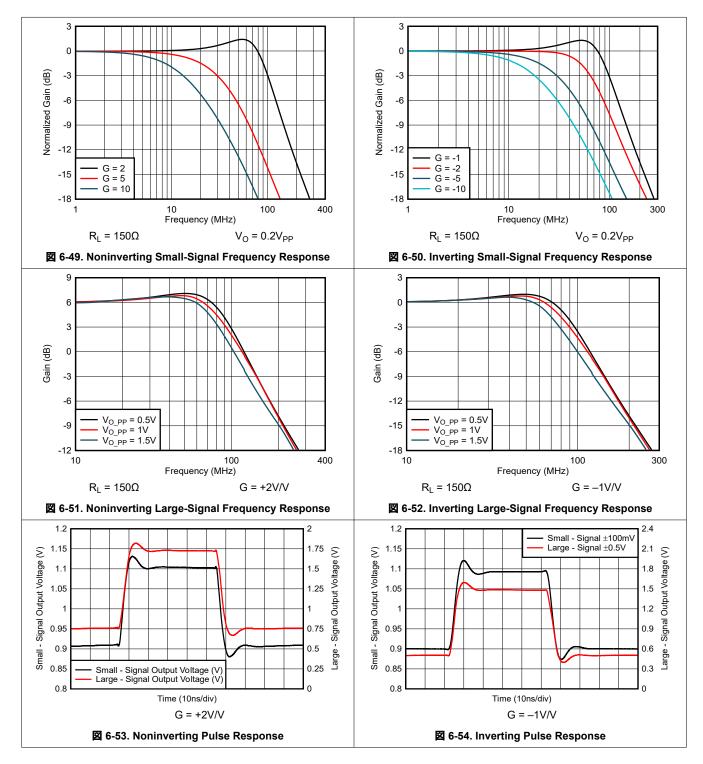

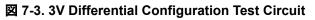

#### 6.10 Typical Characteristics: V<sub>S</sub> = 5V

at T<sub>A</sub> = 25°C, G = +2V/V, R<sub>F</sub> = 750 $\Omega$ , R<sub>L</sub> = 150 $\Omega$  to V<sub>S</sub>/2, and input V<sub>CM</sub> = 2.5V (unless otherwise noted); see  $\mathbb{Z}$  8-1

# 6.10 Typical Characteristics: V<sub>S</sub> = 5V (continued)

at T<sub>A</sub> = 25°C, G = +2V/V, R<sub>F</sub> = 750 $\Omega$ , R<sub>L</sub> = 150 $\Omega$  to V<sub>S</sub>/2, and input V<sub>CM</sub> = 2.5V (unless otherwise noted); see 🗵 8-1

### 6.10 Typical Characteristics: V<sub>S</sub> = 5V (continued)

at T<sub>A</sub> = 25°C, G = +2V/V, R<sub>F</sub> = 750 $\Omega$ , R<sub>L</sub> = 150 $\Omega$  to V<sub>S</sub>/2, and input V<sub>CM</sub> = 2.5V (unless otherwise noted); see  $\boxtimes$  8-1

# 6.10 Typical Characteristics: V<sub>S</sub> = 5V (continued)

at T<sub>A</sub> = 25°C, G = +2V/V, R<sub>F</sub> = 750 $\Omega$ , R<sub>L</sub> = 150 $\Omega$  to V<sub>S</sub>/2, and input V<sub>CM</sub> = 2.5V (unless otherwise noted); see  $\boxtimes$  8-1

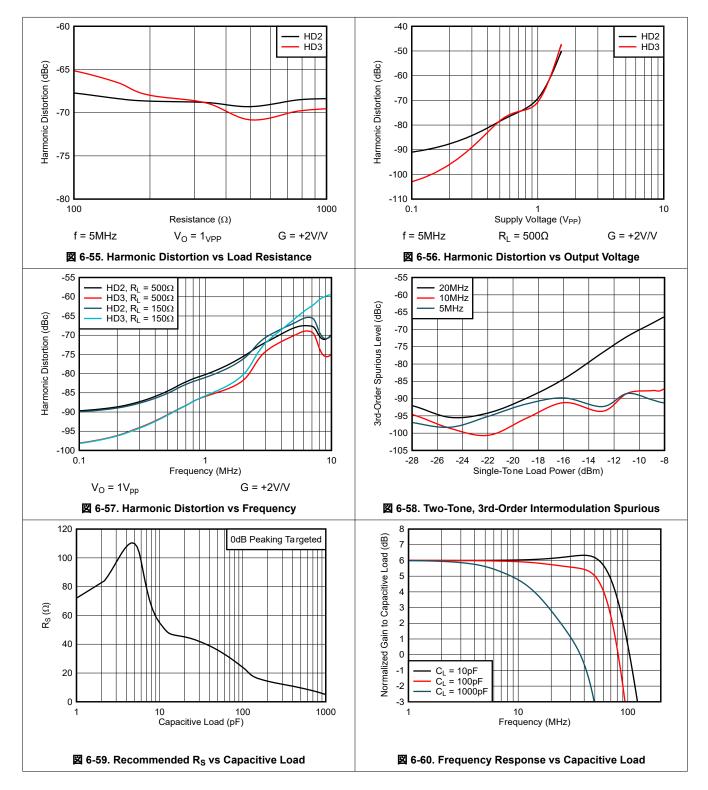

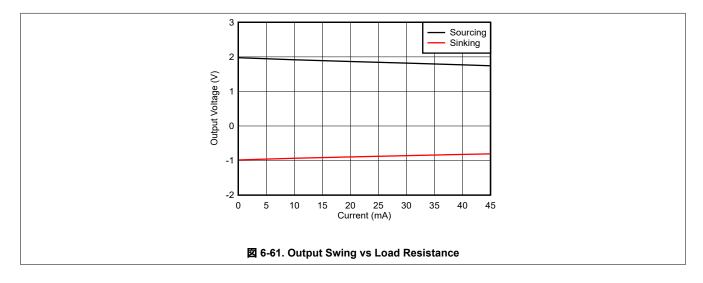

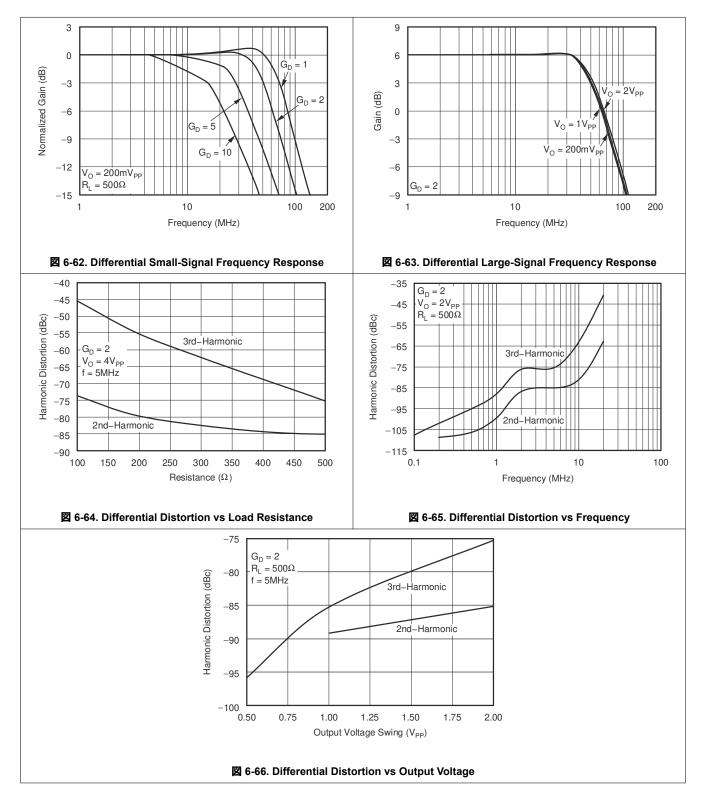

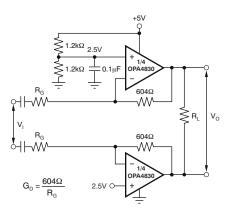

### 6.11 Typical Characteristics: V<sub>S</sub> = 5V, Differential Configuration

at  $T_A = 25^{\circ}$ C,  $R_F = 604\Omega$ , and  $R_L = 500\Omega$  differential; see 🗵 7-2 (unless otherwise noted)

資料に関するフィードバック(ご意見やお問い合わせ)を送信 19

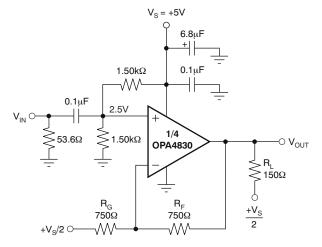

## 6.12 Typical Characteristics: V<sub>S</sub> = 3V

at T<sub>A</sub> = 25°C, G = +2V/V, and R<sub>L</sub> = 150 $\Omega$  to V<sub>S</sub>/3 (unless otherwise noted); see also  $\boxtimes$  8-2

# 6.12 Typical Characteristics: V<sub>S</sub> = 3V (continued)

at T<sub>A</sub> = 25°C, G = +2V/V, and R<sub>L</sub> = 150 $\Omega$  to V<sub>S</sub>/3 (unless otherwise noted); see also 🗵 8-2

# 6.12 Typical Characteristics: V<sub>S</sub> = 3V (continued)

at T<sub>A</sub> = 25°C, G = +2V/V, and R<sub>L</sub> = 150 $\Omega$  to V<sub>S</sub>/3 (unless otherwise noted); see also 🗵 8-2

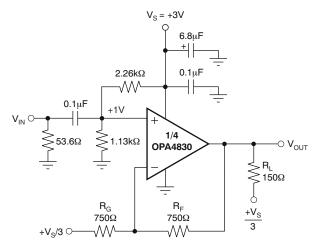

## 6.13 Typical Characteristics: V<sub>S</sub> = 3V, Differential Configuration

at T<sub>A</sub> = 25°C, R<sub>F</sub> = 604 $\Omega$ , and R<sub>L</sub> = 500 $\Omega$  differential; see 🗵 7-3 (unless otherwise noted)

資料に関するフィードバック(ご意見やお問い合わせ)を送信 23

### 7 Parameter Measurement Information

#### 図 7-1. 10V Differential Configuration Test Circuit

#### 図 7-2. 5V Differential Configuration Test Circuit

## 8 Application and Implementation

注

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

#### 8.1 Application Information

#### 8.1.1 Wideband Voltage-Feedback Operation

The OPA4830 is a unity-gain stable, very high-speed voltage-feedback op amp designed for single-supply operation (+3V to +10V). The input stage supports input voltages below ground and to within 1.7V of the positive supply. The complementary common-emitter output stage provides an output swing to within 25mV of ground and the positive supply. The OPA4830 is compensated to provide stable operation with a wide range of resistive loads.

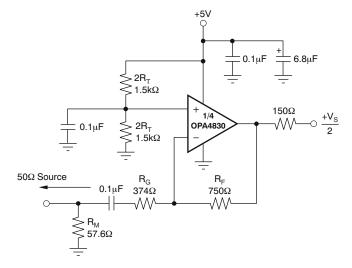

⊠ 8-1 shows the ac-coupled, gain of +2V/V configuration used for the +5V electrical and typical characteristics. For test purposes, the input impedance is set to 50Ω with a resistor to ground. Voltage swings reported in the *Electrical Characteristics*  $V_S$  = 5V are taken directly at the input and output pins. For the circuit of ⊠ 8-1, the total effective load on the output at high frequencies is 150Ω || 1500Ω. The 1.5kΩ resistors at the noninverting input provide the common-mode bias voltage. This parallel combination equals the dc resistance at the inverting input (R<sub>F</sub>), reducing the dc output offset because of input bias current.

図 8-1. AC-Coupled, G = +2V/V, +5V Single-Supply Specification and Test Circuit

$\boxtimes$  8-2 shows the ac-coupled, gain of +2V/V configuration used for the +3V electrical and typical characteristics. For test purposes, the input impedance is set to 50Ω with a resistor to ground. Voltage swings reported in the *Electrical Characteristics*  $V_S$  = 3V are taken directly at the input and output pins. For the circuit of  $\boxtimes$  8-2, the total effective load on the output at high frequencies is 150Ω || 1500Ω. The 1.13kΩ and 2.26kΩ resistors at the noninverting input provide the common-mode bias voltage. The parallel combination equals the dc resistance at the inverting input (R<sub>F</sub>), reducing the dc output offset as a result of input bias current.

☑ 8-2. AC-Coupled, G = +2V/V, +3V Single-Supply Specification and Test Circuit

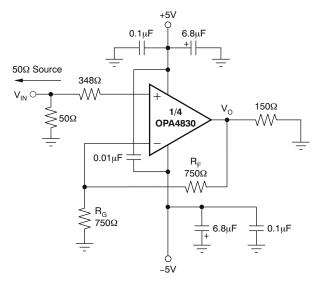

⊠ 8-3 illustrates the dc-coupled, gain of +2V/V, dual power-supply circuit configuration used as the basis of the ±5V electrical and typical characteristics. For test purposes, the input impedance is set to 50Ω with a resistor to ground and the output impedance is set to 150Ω with a series output resistor. Voltage swings reported in the specifications are taken directly at the input and output pins. For the circuit of ⊠ 8-3, the total effective load is 150Ω || 1.5kΩ. Two optional components are included in ⊠ 8-3. An additional resistor (348Ω) is included in series with the noninverting input. Combined with the 25Ω dc source resistance looking back towards the signal generator, this gives an input bias current canceling resistance that matches the 375Ω source resistance seen at the inverting input (see the DC Accuracy and Offset Control section). In addition to the usual power-supply decoupling capacitors to ground, a 0.01µF capacitor is included between the two power-supply pins. In practical printed circuit board layouts, this optional capacitor typically improves the 2nd-harmonic distortion performance by 3dB to 6dB.

図 8-3. DC-Coupled, G = +2V/V, Bipolar Supply Specification and Test Circuit

#### 8.1.2 DC Level-Shifting

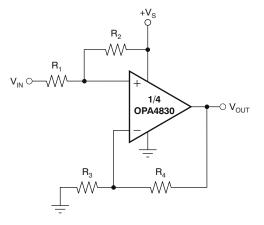

⊠ 8-4 shows a DC-coupled noninverting amplifier that level-shifts the input up to accommodate the desired output voltage range. Given the desired signal gain (G), and the amount V<sub>OUT</sub> needs to be shifted up ( $\Delta V_{OUT}$ ) when V<sub>IN</sub> is at the center of the range,  $\neq$  1 and  $\neq$  2 give the resistor values that produce the desired performance. Assume that R<sub>4</sub> is between 200Ω and 1.5kΩ.

$$NG = G + V_{OUT}/V_{S}$$

$$R_{1} = R_{4}/G$$

$$R_{2} = R_{4}/(NG - G)$$

$$R_{3} = R_{4}/(NG - 1)$$

(1)

where:

$$NG = 1 + R_4/R_3 V_{OUT} = (G)V_{IN} + (NG - G)V_S$$

(2)

Make sure that  $V_{IN}$  and  $V_{OUT}$  stay within the specified input and output voltage ranges.

図 8-4. DC Level-Shifting

The front-page circuit is a good example of this type of application. The device was designed to take V<sub>IN</sub> between 0V and 0.5V and produce V<sub>OUT</sub> between 1V and 2V when using a +3V supply. This output means G = 2.00, and  $\Delta V_{OUT} = 1.50V - G \times 0.25V = 1.00V$ . Plugging these values into  $\pm 1$  and  $\pm 2$  (with R<sub>4</sub> = 750 $\Omega$ ) gives: NG = 2.33, R<sub>1</sub> = 375 $\Omega$ , R<sub>2</sub> = 2.25k $\Omega$ , and R<sub>3</sub> = 563 $\Omega$ . The resistors were changed to the nearest standard values for the front-page circuit.

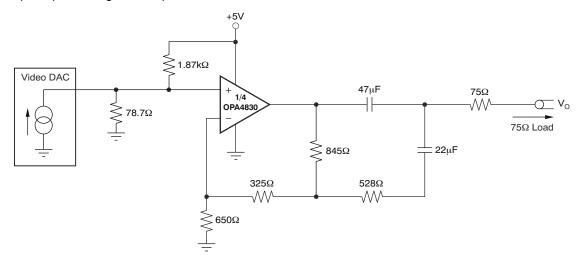

#### 8.1.3 AC-Coupled Output Video Line Driver

Low-power and low-cost video line drivers often buffer digital-to-analog converter (DAC) outputs with a gain of 2V/V into a doubly-terminated line. Those interfaces typically require a dc blocking capacitor. For a simple design, that interface often has used a very large value blocking capacitor ( $220\mu$ F) to limit tilt, or SAG, across the frames. 🛛 8-5 shows one approach to creating a very low high-pass pole location using much lower capacitor values. This circuit gives a voltage gain of 2 at the output pin with a high-pass pole at 8Hz. Given the 150 $\Omega$  load, a simple blocking capacitor approach requires a 133 $\mu$ F value. The two much-lower-valued capacitors give this same low-pass pole using this simple SAG correction circuit of 8-5.

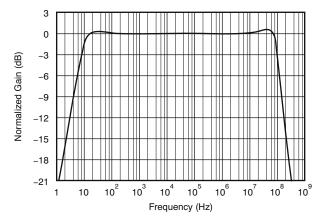

The input is shifted slightly positive in  $\boxtimes$  8-5 using the voltage divider from the positive supply. This configuration gives about a 200mV input dc offset that shows up at the output pin as a 400mV dc offset when the DAC output is at zero current during the sync tip portion of the video signal. This offset acts to hold the output in the linear operating region. This circuit then passes on any power-supply noise to the output with a gain of approximately – 20dB, so good supply decoupling is recommended on the power-supply pin.  $\boxtimes$  8-6 shows the frequency response for the circuit of  $\boxtimes$  8-5. This plot shows the 8Hz low-frequency high-pass pole and a high-end cutoff at approximately 100MHz.

🛛 8-6. Video Line Driver Response to Matched Load

#### 8.1.4 Noninverting Amplifier With Reduced Peaking

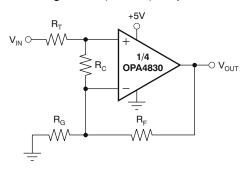

⊠ 8-7 shows a noninverting amplifier that reduces peaking at low gains. The resistor RC compensates the OPA4830 to have higher noise gain (NG), which reduces the ac response peaking (typically 5dB at G = +1V/V without RC) without changing the dc gain.  $V_{IN}$  needs to be a low-impedance source, such as an op amp. The resistor values are low to reduce noise. Using both R<sub>T</sub> and R<sub>F</sub> helps minimize the impact of parasitic impedance.

#### 図 8-7. Compensated Noninverting Amplifier

The noise gain can be calculated as shown in  $\pm 3$ ,  $\pm 4$ , and  $\pm 5$ :

$$G_{1} = 1 + \frac{R_{F}}{R_{G}}$$

$$(3)$$

$$G_2 = 1 + \frac{1 - G_1}{R_C}$$

(4)

$$NG = G_1 \times G_2 \tag{5}$$

A unity-gain buffer can be designed by selecting  $R_T = R_F = 20.0\Omega$  and  $R_C = 40.2\Omega$  (do not use  $R_G$ ). This circuit gives a noise gain of 2V/V, so the response is similar to the characteristics plots with G = +2V/V. Decreasing  $R_C$  to 20.0 $\Omega$  increases the noise gain to 3V/V, which typically gives a flat frequency response, but with less bandwidth.

The circuit in  $\boxtimes$  8-1 can be redesigned to have less peaking by increasing the noise gain to 3. This increase is accomplished by adding R<sub>C</sub> = 2.55k $\Omega$  across the op amp inputs.

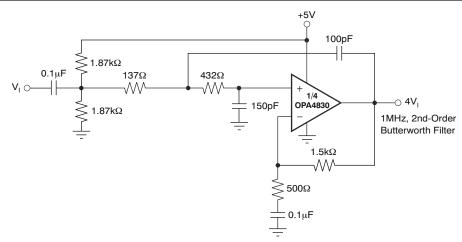

#### 8.1.5 Single-Supply Active Filter

The OPA4830, while operating on a single +3V or +5V supply, lends a well to high-frequency active filter designs. Again, the key additional requirement is to establish the dc operating point of the signal near the supply midpoint for highest dynamic range.  $\boxtimes$  8-8 shows an example design of a 1MHz low-pass Butterworth filter using the Sallen-Key topology.

Both the input signal and the gain setting resistor are ac-coupled using  $0.1\mu$ F blocking capacitors (actually giving bandpass response with the low-frequency pole set to 32kHz for the component values shown). As discussed for 8-1, this configuration allows the midpoint bias formed by the two  $1.87k\Omega$  resistors to appear at both the input and output pins. The midband signal gain is set to +4 (12dB) in this case. The capacitor to ground on the noninverting input is intentionally set larger to dominate input parasitic terms. At a gain of +4, the OPA4830 on a single supply shows 30MHz small- and large-signal bandwidth. The resistor values have been slightly adjusted to account for this limited bandwidth in the amplifier stage. Tests of this circuit show a precise 1MHz, –3dB point with a maximally-flat pass-band (above the 32kHz ac-coupling corner), and a maximum stop band attenuation of 36dB at the amplifier –3dB bandwidth of 30MHz.

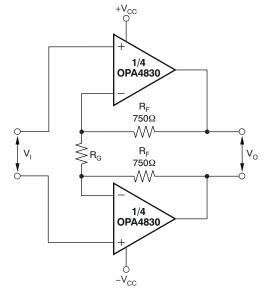

#### 8.1.6 Differential Interface Applications

Dual and quad op amps are particularly designed to differential input to differential output applications. Typically, these op amps fall into either ADC input interface or line driver applications. Two basic approaches to differential I/O are noninverting or inverting configurations. Because the output is differential, the signal polarity is somewhat meaningless—the noninverting and inverting terminology applies here to where the input is brought into the OPA4830. Each has advantages and disadvantages. 🛛 8-9 shows a basic starting point for noninverting differential I/O applications.

This approach provides for a source termination impedance that is independent of the signal gain. For instance, simple differential filters can be included in the signal path right up to the noninverting inputs without interacting with the amplifier gain. The differential signal gain for the circuit of  $\boxtimes$  8-9 is shown in  $\ddagger$  6:

$$\frac{V_{O}}{V_{I}} = A_{D} = 1 + 2 \times \frac{R_{F}}{R_{G}}$$

(6)

$\boxtimes$  8-9 shows the recommended value of 750 $\Omega$ . However, the gain can be adjusted using just the R<sub>G</sub> resistor.

Various combinations of single-supply or ac-coupled gains can also be delivered using the basic circuit of  $\boxtimes$  8-9. Common-mode bias voltages on the two noninverting inputs pass on to the output with a gain of 1V/V because an equal dc voltage at each inverting node creates no current through R<sub>G</sub>, giving that voltage a common-mode gain of 1 to the output.

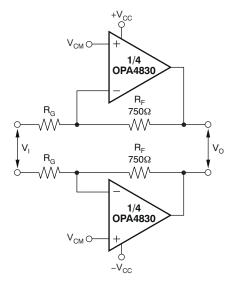

$\boxtimes$  8-10 shows a differential I/O stage configured as an inverting amplifier. In this case, the gain resistors (R<sub>G</sub>) become the input resistance for the source. This configuration provides a better noise performance than the noninverting configuration, but does limit the flexibility in setting the input impedance separately from the gain.

The two noninverting inputs provide an easy common-mode control input. This control is particularly useful if the source is ac-coupled through either blocking caps or a transformer. In either case, the common-mode input voltages on the two noninverting inputs again have a gain of 1 to the output pins, giving an easy common-mode control for single-supply operation. The input resistors can be adjusted to the desired gain but also change the input impedance as well. The differential gain for this circuit is shown in  $\vec{x}$  7:

$$\frac{V_{O}}{V_{I}} = -\frac{R_{F}}{R_{G}}$$

(7)

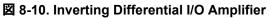

#### 8.1.7 DC-Coupled Single-to-Differential Conversion

The previous differential output circuits were set up to receive a differential input as well as provide a differential output.  $\boxtimes$  8-11 illustrates one way to provide a single-to-differential conversion, with dc coupling, and independent output common-mode control using a quad op amp.

The circuit of  $\boxtimes$  8-11 provides several useful features for isolating the input signal from the final outputs. Using the first amplifier as a simple noninverting stage gives an independent adjustment on R<sub>I</sub> (to set the source loading) while the gain can be easily adjusting in this stage using the R<sub>G</sub> resistor. The next stage allows a separate output common-mode level to be set up. The desired output common-mode voltage, V<sub>CM</sub>, is cut in half and applied to the noninverting input of the second stage. The signal path in this stage sees a gain of -1V/V while this (1/2 × V<sub>CM</sub>) voltage sees a gain of +2V/V. The output of this second stage is then the original common-mode voltage plus the inverted signal from the output of the first stage. The 2nd stage output appears directly at the output of the noninverting final stage. The inverting node of the inverting output stage is also biased to the common-mode voltage, equal to the common-mode voltage appearing at the output of the second stage, creating no current flow and placing the desired V<sub>CM</sub> at the output of this stage as well.

Copyright © 2025 Texas Instruments Incorporated

図 8-11. Wideband, DC-Coupled, Single-to-Differential Conversion

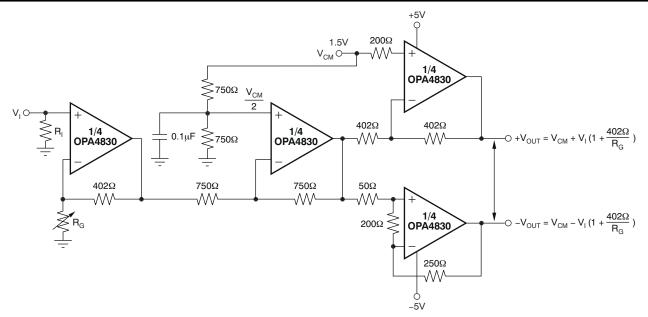

#### 8.1.8 Low-Power, Differential I/O, 4th-Order Active Filter

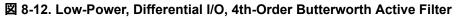

The OPA4830 can give a very capable gain block for active filters. The quad design lends a very well to differential active filters. Where the filter topology is looking for a simple gain function to implement the filter, the noninverting configuration is preferred to isolate the filter elements from the gain elements in the design. See  $\boxtimes$  8-12 for an example of a 10MHz, 4th-order Butterworth, low-pass Sallen-Key filter. The design places the higher Q stage first to allow the lower Q 2nd stage to roll off the peaked noise of the first stage. The resistor values have been adjusted slightly to account for the amplifier group delay.

While this circuit is bipolar, using  $\pm 5V$  supplies, can easily be adapted to single-supply operation. This configuration adds two real zeroes in the response, transforming this circuit into a bandpass. The frequency response for the filter of  $\boxtimes$  8-12 is illustrated in  $\boxtimes$  8-13.

図 8-13. Differential 4th-Order, 10MHz Butterworth Filter

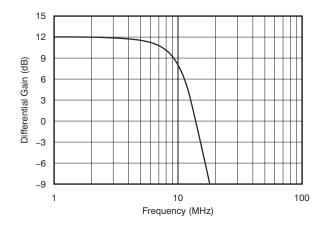

#### 8.1.9 Dual-Channel, Differential ADC Driver

Where a low-noise, single-supply, interface to a differential input +5V ADC is required, the circuit of  $\boxtimes$  8-14 can provide a high dynamic range, medium gain interface for dual high-performance ADCs. The circuit of  $\boxtimes$  8-14 uses two amplifiers in the differential inverting configuration. The common-mode voltage is set on the noninverting inputs to the supply mid-scale. In this example, the input signal is coupled in through a 1:2 transformer. This design provides both signal gain, single to differential conversion, and a reduction in noise figure. To show a 50 $\Omega$  input impedance at the input to the transformer, two 200 $\Omega$  resistors are required on the transformer secondary. These two resistors are also the amplifier gain elements. Because the same dc voltage appears on both inverting nodes in the circuit of  $\boxtimes$  8-14, no dc current flows through the transformer, giving a dc gain of 1 to the output for this common-mode voltage, V<sub>CM</sub>.

The circuit of  $\boxtimes$  8-14 is particularly designed for a moderate resolution dual ADC used as I/Q samplers. The optional 500 $\Omega$  resistors to ground on each amplifier output can be added to improve the 2nd- and 3rd-harmonic distortion by >15dB if higher dynamic range is required.

The 5mA added output stage current significantly improves linearity if that is required. The measured 2ndharmonic distortion is consistently lower than the 3rd-harmonics for this balanced differential design. Particularly helpful for this low-power design if there are no grounds in the signal path after the low-level signal at the transformer input. The two pull-down resistors do show a signal path ground and can be connected at the same physical point to ground, to eliminate imbalanced ground return currents from degrading 2nd-harmonic distortion.

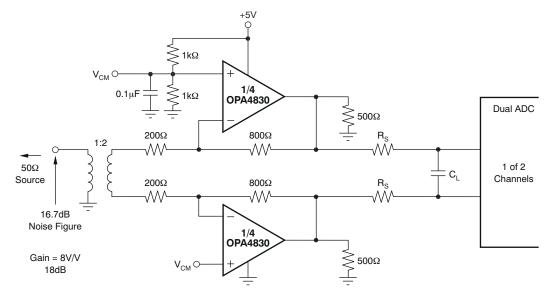

#### 8.1.10 Video Line Driving

Most video distribution systems are designed with 75 $\Omega$  series resistors to drive a matched 75 $\Omega$  cable. To deliver a net gain of 1 to the 75 $\Omega$  matched load, the amplifier is typically set up for a voltage gain of +2V/V, compensating for the 6dB attenuation of the voltage divider formed by the series and shunt 75 $\Omega$  resistors at either end of the cable.

The circuit of  $\boxtimes$  8-1 applies to this requirement if all references to 50 $\Omega$  resistors are replaced by 75 $\Omega$  values. Often, the amplifier gain is further increased to 2.2, which recovers the additional dc loss of a typical long cable run. This change can require the gain resistor (R<sub>G</sub>) in  $\boxtimes$  8-1 to be reduced from 750 $\Omega$  to 625 $\Omega$ . In either case, both the gain flatness and the differential gain/phase performance of the OPA4830 provide exceptional results in video distribution applications. Differential gain and phase measure the change in overall small-signal gain and phase for the color sub-carrier frequency (3.58MHz in NTSC systems) versus changes in the large-signal output level (which represents luminance information in a composite video signal). The OPA4830, with the typical 150 $\Omega$  load of a single matched video cable, shows less than 0.07%/0.17° differential gain/phase errors over the

standard luminance range for a positive video (negative sync) signal. Similar performance is observed for multiple video signals (see ⊠ 8-15).

図 8-14. Single-Supply Differential ADC Driver (1 of 2 channels)

#### 8.1.11 4-Channel DAC Transimpedance Amplifier

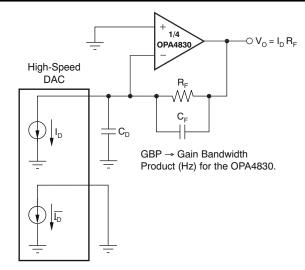

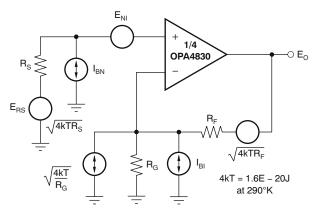

High-frequency Digital-to-Analog Converters (DACs) require a low-distortion output amplifier to retain the SFDR performance into real-world loads. ⊠ 8-16 illustrates a single-ended output drive implementation. In this circuit, only one side of the complementary output drive signal is used. The diagram shows the signal output current connected into the virtual ground-summing junction of the OPA4830, which is set up as a transimpedance stage or I-V converter. The unused current output of the DAC is connected to ground. If the DAC requires the outputs to be terminated to a compliance voltage other than ground for operation, then the appropriate voltage level can be applied to the noninverting input of the OPA4830.

#### 図 8-16. Wideband, Low-Distortion DAC Transimpedance Amplifier

The dc gain for this circuit is equal to  $R_F$ . At high frequencies, the DAC output capacitance ( $C_D$ ) produces a zero in the noise gain for the OPA4830 that can cause peaking in the closed-loop frequency response.  $C_F$  is added across  $R_F$  to compensate for this noise-gain peaking. To achieve a flat transimpedance frequency response, this pole in the feedback network can be set to:

$$\frac{1}{2\pi R_F C_F} = \sqrt{\frac{GBP}{4\pi R_F C_D}}$$

(8)

which gives a corner frequency  $f_{-3dB}$  of approximately:

$$f_{-3dB} = \sqrt{\frac{GBP}{2\pi R_F C_D}}$$

(9)

#### 8.1.12 Operating Suggestions: Optimizing Resistor Values

The OPA4830 is a unity-gain stable, voltage-feedback op amp; therefore, a wide range of resistor values can be used for the feedback and gain setting resistors. The primary limits on these values are set by dynamic range (noise and distortion) and parasitic capacitance considerations. For a noninverting unity-gain follower application, the feedback connection can be made with a direct short.

Less than 200 $\Omega$ , the feedback network presents additional output loading that can degrade the harmonic distortion performance of the OPA4830. Above 1k $\Omega$ , the typical parasitic capacitance (approximately 0.2pF) across the feedback resistor can cause unintentional band limiting in the amplifier response.

Recommended to target the parallel combination of  $R_F$  and  $R_G$  (see  $\boxtimes 8-3$ ) to be less than about 400 $\Omega$ . The combined impedance  $R_F \parallel R_G$  interacts with the inverting input capacitance, placing an additional pole in the feedback network, and thus a zero in the forward response. Assuming a 2pF total parasitic on the inverting node, holding  $R_F \parallel R_G < 400\Omega$  keeps this pole above 200MHz. This constraint implies that the feedback resistor  $R_F$  can increase to several k $\Omega$  at high gains. This increase is acceptable as long as the pole formed by  $R_F$  and any parasitic capacitance appearing in parallel is kept out of the frequency range of interest.

In the inverting configuration, an additional design consideration must be noted.  $R_G$  becomes the input resistor and therefore the load impedance to the driving source. If impedance matching is desired,  $R_G$  can be set equal to the required termination value. However, at low inverting gains, the resulting feedback resistor value can present a significant load to the amplifier output. For example, an inverting gain of 2 with a 50 $\Omega$  input matching resistor (=  $R_G$ ) requires a 100 $\Omega$  feedback resistor, which can contribute to output loading in parallel with the external load. In such a case, preferable technique is to increase both the  $R_F$  and  $R_G$  values, and then achieve

the input matching impedance with a third resistor to ground (see  $\boxtimes$  8-17). The total input impedance becomes the parallel combination of R<sub>G</sub> and the additional shunt resistor.

#### 8.1.13 Bandwidth vs Gain: Noninverting Operation

Voltage-feedback op amps exhibit decreasing closed-loop bandwidth as the signal gain is increased. In theory, this relationship is described by the gain bandwidth product (GBP) shown in the *Electrical Characteristics*. Dividing GBP by the noninverting signal gain (also called the noise gain, or NG) predicts the closed-loop bandwidth. In practice, this calculation only holds true when the phase margin approaches 90°, similar to high-gain configurations. At low gains (increased feedback factors), most amplifiers exhibit a more complex response with lower phase margin. The OPA4830 is compensated to give a slightly peaked response in a noninverting gain of 2V/V (see  $\boxtimes$  8-3). This compensation results in a typical gain of +2V/V bandwidth of 110MHz, far exceeding that predicted by dividing the 110MHz GBP by 2V/V. Increasing the gain causes the phase margin to approach 90° and the bandwidth to more closely approach the predicted value of (GBP/NG). At a gain of +10V/V, the 11MHz bandwidth illustrated in the *Electrical Characteristics* agrees with that predicted using the simple formula and the typical GBP of 110MHz.

Frequency response in a gain of +2V/V can be modified to achieve exceptional flatness simply by increasing the noise gain to 3V/V. One way to do this, without affecting the +2V/V signal gain, is to add a 2.55k $\Omega$  resistor across the two inputs (see  $\boxtimes$  8-7). A similar technique can be used to reduce peaking in unity-gain (voltage follower) applications. For example, by using a 750 $\Omega$  feedback resistor along with a 750 $\Omega$  resistor across the two op amp inputs, the voltage follower response is similar to the gain of +2V/V response of  $\boxtimes$  8-2. Further reducing the value of the resistor across the op amp inputs further dampens the frequency response because of increased noise gain. The OPA4830 exhibits minimal bandwidth reduction going to single-supply (+5V) operation as compared with ±5V. This minimal reduction is because the internal bias control circuitry retains nearly constant quiescent current as the total supply voltage between the supply pins changes.

#### 8.1.14 Inverting Amplifier Operation

All of the familiar op amp application circuits are available with the OPA4830 to the designer. See  $\boxtimes$  8-17 for a typical inverting configuration where the I/O impedance and signal gain from  $\boxtimes$  8-1 are retained in an inverting circuit configuration. Inverting operation is one of the more common requirements and offers several performance benefits. This also allows the input to be biased at V<sub>S</sub>/2 without any headroom issues. The output voltage can be independently moved to be within the output voltage range with coupling capacitors, or bias adjustment resistors.

図 8-17. AC-Coupled, G = -2V/V Example Circuit

In the inverting configuration, three key design considerations must be noted. The first consideration is that the gain resistor ( $R_G$ ) becomes part of the signal channel input impedance. If input impedance matching is desired

(which is beneficial whenever the signal is coupled through a cable, twisted pair, long PCB trace, or other transmission line conductor),  $R_G$ can be set equal to the required termination value and  $R_F$  adjusted to give the desired gain. This approach is the simplest and results in optimum bandwidth and noise performance.

However, at low inverting gains, the resulting feedback resistor value can present a significant load to the amplifier output. For an inverting gain of 2, setting  $R_G$  to  $50\Omega$  for input matching eliminates the need for  $R_M$  but requires a  $100\Omega$  feedback resistor. This configuration has the interesting advantage of the noise gain becoming equal to 2 for a  $50\Omega$  source impedance—the same as the noninverting circuits considered above. The amplifier output now sees the  $100\Omega$  feedback resistor in parallel with the external load. In general, the feedback resistor is limited to the  $200\Omega$  to  $1.5k\Omega$  range. In this case, preferable to increase both the  $R_F$  and  $R_G$  values, as shown in  $\boxtimes$  8-17, and then achieve the input matching impedance with a third resistor ( $R_M$ ) to ground. The total input impedance becomes the parallel combination of  $R_G$  and  $R_M$ .

The second major consideration, touched on in the previous paragraph, is that the signal source impedance becomes part of the noise gain equation and thus influences the bandwidth. For the example in  $\boxtimes$  8-17, the R<sub>M</sub> value combines in parallel with the external 50 $\Omega$  source impedance (at high frequencies), yielding an effective driving impedance of 50 $\Omega$  || 57.6 $\Omega$  = 26.8 $\Omega$ . This impedance is added in series with R<sub>G</sub> for calculating the noise gain. The resulting noise gain is 2.87 for  $\boxtimes$  8-17, as opposed to only 2 if R<sub>M</sub> can be eliminated as discussed above. The bandwidth is therefore lower for the gain of -2 circuit of  $\boxtimes$  8-17 (NG = +2.87) than for the gain of +2 circuit of  $\boxtimes$  8-1.

The third important consideration in inverting amplifier design is setting the bias current cancellation resistors on the noninverting input (a parallel combination of  $R_T = 750\Omega$ ). If this resistor is set equal to the total dc resistance looking out of the inverting node, the output dc error (as a result of the input bias currents) is reduced to (input offset current) times  $R_F$ . With the dc blocking capacitor in series with  $R_G$ , the dc source impedance looking out of the inverting mode is simply  $R_F = 750\Omega$  for  $\boxtimes$  8-17. To reduce the additional high-frequency noise introduced by this resistor and power-supply feed-through,  $R_T$  is bypassed with a capacitor.

### 8.1.15 Output Current and Voltages

The OPA4830 provides outstanding output voltage capability. For the +5V supply, under no-load conditions at +25°C, the output voltage typically swings closer than 90mV to either supply rail.

The minimum specified output voltage and current specifications over temperature are set by worst-case simulations at the cold temperature extreme. Only at cold startup does the output current and voltage decrease to the numbers shown in the specification tables. As the output transistors deliver power, the junction temperatures increase, decreasing the  $V_{BE}$ s (increasing the available output voltage swing), and increasing the current gains (increasing the available output current). In steady-state operation, the available output voltage and current is always greater than that shown in the over-temperature specifications, because the output stage junction temperatures are higher than the minimum specified operating ambient temperature.

To maintain maximum output stage linearity, no output short-circuit protection is provided. This absence of protection is not normally a problem, because most applications include a series matching resistor at the output that limits the internal power dissipation if the output side of this resistor is shorted to ground. However, shorting the output pin directly to the adjacent positive power-supply pin (8-pin packages), in most cases, destroys the amplifier. If additional short-circuit protection is required, consider a small series resistor in the power-supply leads. This resistor reduces the available output voltage swing under heavy output loads.

## 8.1.16 Driving Capacitive Loads