#### LMX2624-SP JAJSVY4 - DECEMBER 2024

## LMX2624-SP5MHz~28GHz 広帯域 シンセサイザ、位相同期および JESD204B/C 対応

## 1 特長

- SMD 5962R2321001PXE

- 総照射線量耐性:100Krad (ELDRS フリー)

- シングル イベント ラッチアップ (SEL) 耐性:最大 75MeV-cm<sup>2</sup>/mg

- シングルイベント機能割り込み (SEFI) 耐性:最大 75MeV-cm<sup>2</sup>/mg

- 広帯域周波数シンセサイザ:出力周波数:5MHz~ 28GHz

- 24GHz 搬送波周波数使用時に、100kHz のオフセッ トで -101dBc/Hz の位相ノイズ

- 24GHz でのジッタ:60fs RMS (1kHz~300MHz)

- 出力電力をプログラム可能

- 主な PLL 仕様

- 性能指数:-236dBc/Hz

- 正規化 1/f ノイズ:-129dBc/Hz

- 最高 200MHz の位相検出周波数

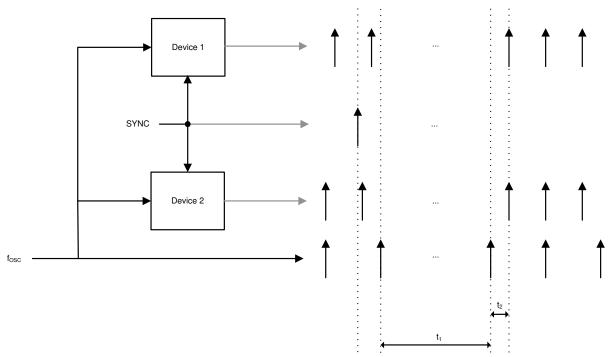

- 複数デバイス間の出力位相の同期

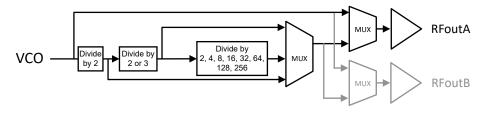

- RFoutA および RFoutB 用の独立した MUTE ピン で、200ns のミュート/ミュート解除時間

- 分解能 9ps のプログラム可能な遅延による SYSREF サポート

- 3.3V 単一電源動作

- ピンモード:整数 PLL モードでピンにより構成可能な N分周器および出力分周器

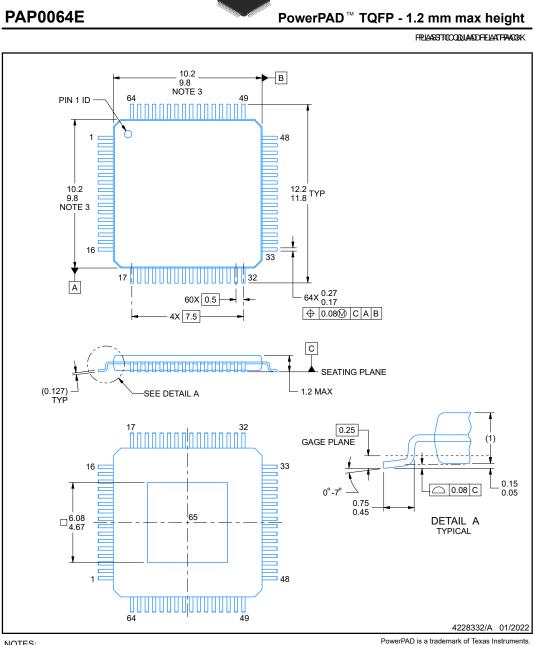

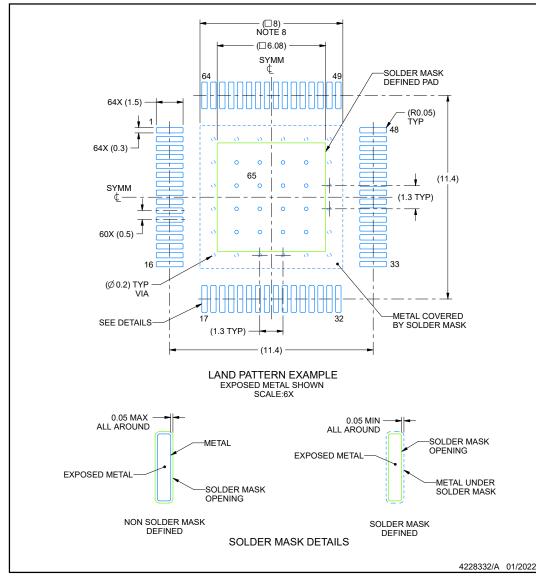

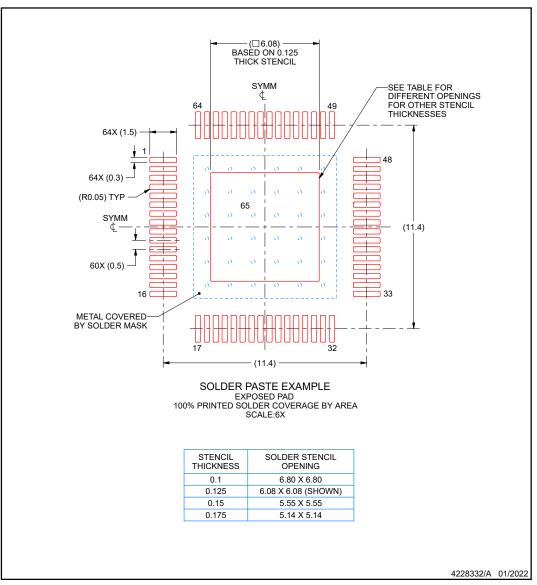

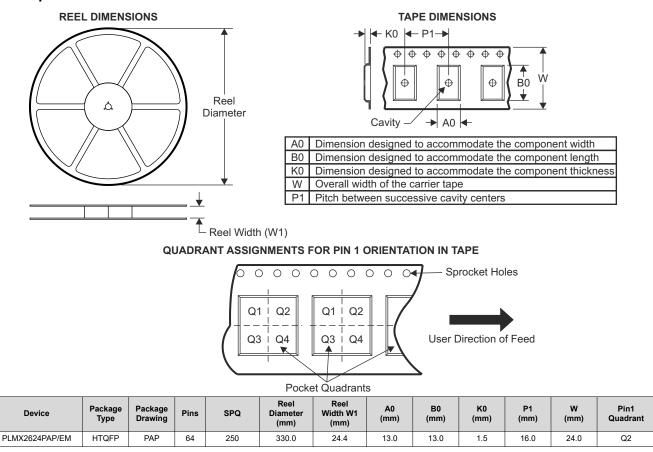

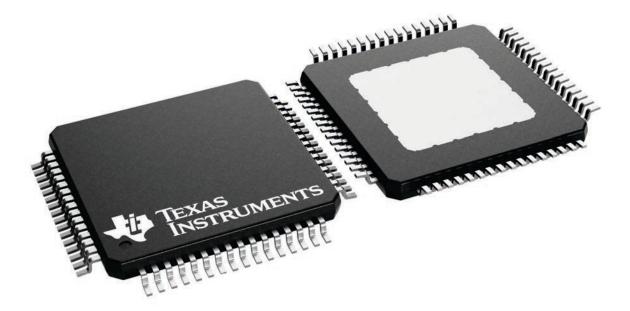

- 10×10mm<sup>2</sup> 64 リード QFP パッケージ

- 動作温度範囲:-55℃~+125℃

- PLLatinum<sup>™</sup> シミュレータ設計ツール対応

## 2 アプリケーション

- Ku/Ka バンドまでの宇宙通信ペイロード

- 宇宙レーダー システム

- コマンドおよびデータの処理系

- 高速データコンバータクロッキング (JESD204B/C 対 応)

- 28GHz までの周波数のミキサ用ローカル発振器

## 3 概要

LMX2624-SP は、周波数 5MHz~28GHz を出力可能な 電圧制御発振器 (VCO) を内蔵した、高性能、広帯域フェ ーズ ロック ループ (PLL) および電圧レギュレータです。こ のデバイスの VCO は、1 オクターブの範囲をカバーして いるため、最低 5MHz までのすべての周波数を出力でき ます。-236dBc/Hz という性能指数を持つ高性能 PLL と 高い位相検出周波数により、帯域内ノイズと積分ジッタを 非常に低く抑えることができます。

LMX2624-SP では、複数のデバイスの出力を同期できま す。このため、フラクショナル エンジンまたは出力分周器 を使用した場合を含めて、あらゆる使用事例でデバイスか ら決定性位相を取得できます。このデバイスは、SYSREF (JESD204B/C 規格に準拠)の生成および中継サポート が追加されており、高速データコンバータ向けの低ノイズ クロックソースとして設計されています。

このデバイスは、テキサス・インスツルメンツの高度な BiCMOS プロセスで製造され、64 リード QFP プラスチッ クパッケージで供給されます。

## パッケージ情報

| 部品番号       | グレード  | パッケージ <sup>(1)</sup> | パッケージ サイズ<br><sup>(2)</sup> |

|------------|-------|----------------------|-----------------------------|

| LMX2624-SP | QML-P | QFP 64 ピン            | 10mm × 10mm                 |

(1) 詳細については、セクション 11 を参照してください。

パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピ (2) ンも含まれます。

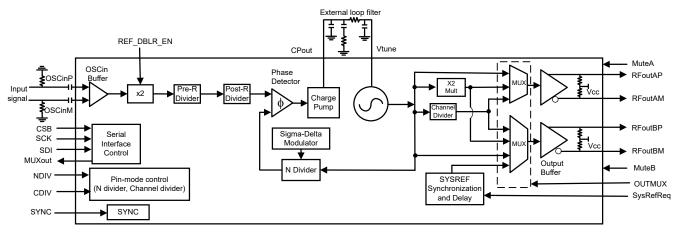

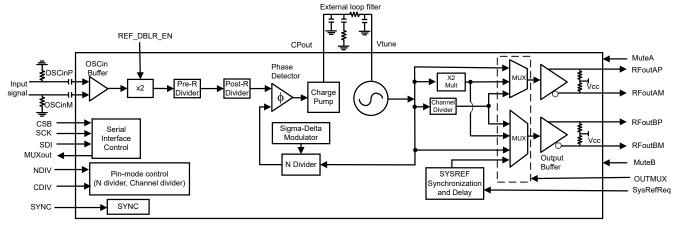

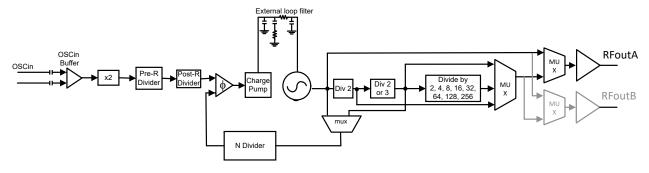

機能ブロック図

## **Table of Contents**

| 1 | 特長                                   | 1              |

|---|--------------------------------------|----------------|

|   | アプリケーション                             |                |

|   | 概要                                   |                |

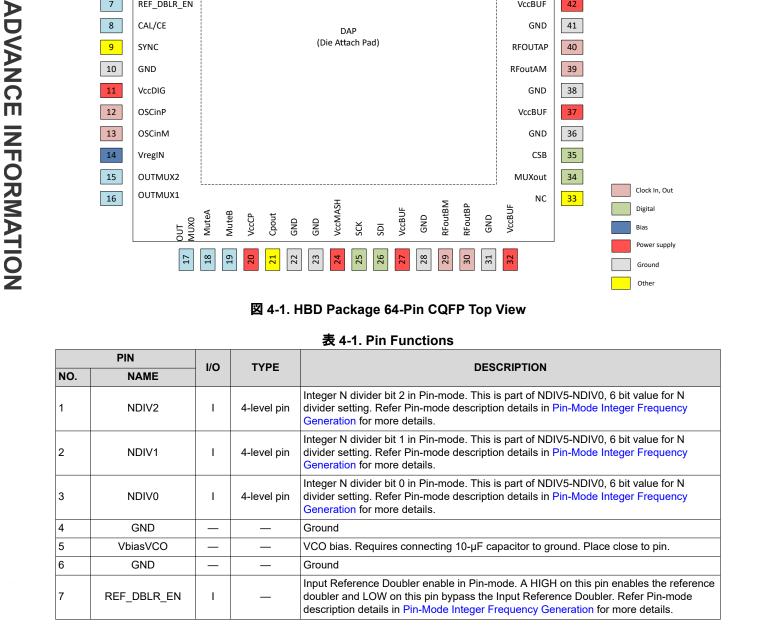

| 4 | Pin Configuration and Functions      | 4              |

| 5 | Specifications                       | 7              |

|   | 5.1 Absolute Maximum Ratings         | 7              |

|   | 5.2 ESD Ratings                      | 7              |

|   | 5.3 Recommended Operating Conditions |                |

|   | 5.4 Thermal Information              | 7              |

|   | 5.5 Electrical Characteristics       | <mark>8</mark> |

|   | 5.6 Timing Requirements              | .14            |

|   | 5.7 Timing Diagrams                  |                |

| 6 | Detailed Description                 | 16             |

|   | 6.1 Overview                         | .16            |

|   | 6.2 Functional Block Diagram         | .17            |

|   | 6.3 Feature Description              | 17             |

|   | 6.4 Device Functional Modes          | 37             |

|   | 6.5 Programming                      | . 38           |

| 7 | Register Maps                        | .39            |

|   | 7.1 Device Registers                 |                |

|   |                                      |                |

| 8 Application and Implementation        | 52 |

|-----------------------------------------|----|

| 8.1 Application Information             |    |

| 8.2 Typical Application                 |    |

| 8.3 Power Supply Recommendations        |    |

| 8.4 Layout                              |    |

| 9 Device and Documentation Support      |    |

| 9.1 Device Support                      |    |

| 9.2 Documentation Support               |    |

| 9.3ドキュメントの更新通知を受け取る方法                   |    |

| 9.4 サポート・リソース                           |    |

| 9.5 Trademarks                          |    |

| 9.6 静電気放電に関する注意事項                       |    |

| 9.7 用語集                                 |    |

| 10 Revision History                     |    |

| 11 Mechanical, Packaging, and Orderable |    |

| Information                             |    |

| 11.1 Engineering Samples                |    |

| 11.2 Package Option Addendum            |    |

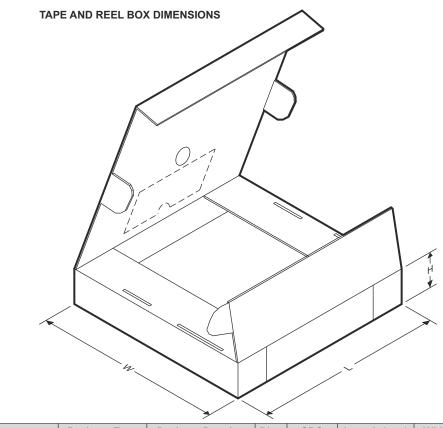

| 11.3 Tape and Reel Information          |    |

|                                         |    |

4

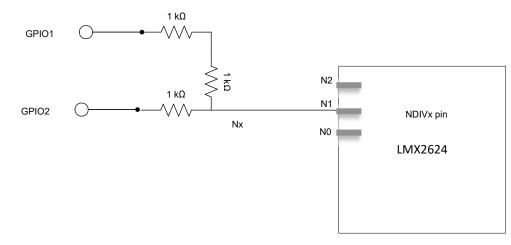

NDIV2

NDIV1

NDIV0

GND

GND

CAL/CE

SYNC

GND

VccDIG

OSCinP

VbiasVCO

REF\_DBLR\_EN

64

NDIV3

63 62

NDIV4 NDIV5 60 59

GND

VregVCO

VccVCO VrefVCO

DAP (Die Attach Pad)

GND

LMX2624-SP

JAJSVY4 – DECEMBER 2024

1

2

3

4

5

6

7

8

9

10

11

12

49

RECAL

VrefVCO2

SyRefReq

VbiasVCO2

VccVCO2

GND

GND

VccBUF

RFOUTAP

RFoutAM

GND

VccBUF

\_EN

48

47

46

45

44 43

42

41

40

39

38

37

50

CDIV1 **CDIVO**

52

GND CDIV2

Vtune

GND

VbiasVAR

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2025 Texas Instruments Incorporated

## 表 4-1. Pin Functions (続き)

| PIN |         | 1/0   | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                                                                           |  |  |  |

|-----|---------|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NO. | NAME    | - I/O | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                                                                           |  |  |  |

| 8   | CAL/CE  | I     | _      | Chip enable. In Pin Mode (not SPI-mode), rising edges presented to this pin activate the VCO calibration. In SPI-mode, this pin acts like CE where a high on CE pin make device to enable and Low disables the device.                                                                                                |  |  |  |

| 9   | SYNC    | I     | —      | Phase synchronization input pin.                                                                                                                                                                                                                                                                                      |  |  |  |

| 10  | GND     | —     | —      | Ground                                                                                                                                                                                                                                                                                                                |  |  |  |

| 11  | VccDIG  | -     | _      | Digital supply. Recommend connecting 0.1-µF capacitor to ground.                                                                                                                                                                                                                                                      |  |  |  |

| 12  | OSCinP  | I     | —      | Complimentary Reference input clock pins. High input impedance. Requires connecting series capacitor (0.1 $\mu F$ recommended).                                                                                                                                                                                       |  |  |  |

| 13  | OSCinM  | I     | _      | Complimentary pin to OSCinP.                                                                                                                                                                                                                                                                                          |  |  |  |

| 14  | VregIN  | _     | _      | Input reference path regulator decoupling. Requires connecting 1-µF capacitor to ground. Place close to pin.                                                                                                                                                                                                          |  |  |  |

| 15  | OUTMUX2 | I     | _      | Controls the Output Mux selection together with OUTMUX1 and OUTMUX0 for RFOUTA and RFOUTB. The eight options include selecting VCO output, Doubler output or Channel Divider output combinations for RFOUTA and RFOUTB. Refer Pin-mode description details in Pin-Mode Integer Frequency Generation for more details. |  |  |  |

| 16  | OUTMUX1 | I     | _      | Controls the Output Mux selection together with OUTMUX2 and OUTMUX0 for RFOUTA and RFOUTB. The eight options include selecting VCO output, Doubler output or Channel Divider output combinations for RFOUTA and RFOUTB. Refer Pin-mode description details in Pin-Mode Integer Frequency Generation for more details. |  |  |  |

| 17  | OUTMUX0 | I     | _      | Controls the Output Mux selection together with OUTMUX2 and OUTMUX1 for RFOUTA and RFOUTB. The eight options include selecting VCO output, Doubler output or Channel Divider output combinations for RFOUTA and RFOUTB. Refer Pin-mode description details in Pin-Mode Integer Frequency Generation for more details. |  |  |  |

| 18  | MuteA   | I     | _      | Output Buffer mute control. High-impedance CMOS input. RFOUTA is muted or unmuted using this MuteA pin                                                                                                                                                                                                                |  |  |  |

| 19  | MuteB   | I     | _      | Output Buffer mute control. High-impedance CMOS input. RFOUTB is muted or unmuted using this MuteB pin                                                                                                                                                                                                                |  |  |  |

| 20  | VccCP   | I     | _      | Charge pump supply. Recommend connecting 0.1-µF capacitor to ground.                                                                                                                                                                                                                                                  |  |  |  |

| 21  | CPout   | 0     | _      | Charge pump output. Recommend connecting C1 of loop filter close to charge pump pin.                                                                                                                                                                                                                                  |  |  |  |

| 22  | GND     | -     | Ground | Ground                                                                                                                                                                                                                                                                                                                |  |  |  |

| 23  | GND     | —     | Ground | Ground                                                                                                                                                                                                                                                                                                                |  |  |  |

| 24  | VccMASH | —     | _      | Digital supply. Recommend connecting 0.1-µF and 10-µF capacitor to ground.                                                                                                                                                                                                                                            |  |  |  |

| 25  | SCK     | I     | _      | SPI input clock. High impedance CMOS input. 1.8 – 3.3V logic.                                                                                                                                                                                                                                                         |  |  |  |

| 26  | SDI     | I     | _      | SPI input data. High impedance CMOS input. 1.8 – 3.3V logic.                                                                                                                                                                                                                                                          |  |  |  |

| 27  | VccBUF  | —     | —      | Output buffer supply. Requires connecting 0.1-µF capacitor to ground.                                                                                                                                                                                                                                                 |  |  |  |

| 28  | GND     | —     | Ground | Ground                                                                                                                                                                                                                                                                                                                |  |  |  |

| 29  | RFoutBM | 0     | _      | Complementary pin for RFoutBP                                                                                                                                                                                                                                                                                         |  |  |  |

| 30  | RFoutBP | 0     | —      | Differential output B Pair. Requires connecting a 50- $\Omega$ resistor pullup to V <sub>CC</sub> as close as possible to pin. Can be used as a synthesizer output or SYSREF output.                                                                                                                                  |  |  |  |

| 31  | GND     | —     | Ground | Ground                                                                                                                                                                                                                                                                                                                |  |  |  |

| 32  | VccBUF  | —     | _      | Output buffer supply. Requires connecting 0.1-µF capacitor to ground.                                                                                                                                                                                                                                                 |  |  |  |

| 33  | NC      | —     | _      | No connection. Leave Unconnected.                                                                                                                                                                                                                                                                                     |  |  |  |

| 34  | MUXout  | -     | _      | Multiplexed output pin. Can output: lock detect, SPI readback and diagnostics.                                                                                                                                                                                                                                        |  |  |  |

| 35  | CSB     | -     |        | SPI chip select bar. High impedance CMOS input. 1.8 – 3.3-V logic.                                                                                                                                                                                                                                                    |  |  |  |

| 36  | GND     | -     | Ground | Ground                                                                                                                                                                                                                                                                                                                |  |  |  |

| 37  | VccBUF  | -     | _      | Output buffer supply. Requires connecting 0.1-µF capacitor to ground.                                                                                                                                                                                                                                                 |  |  |  |

| 38  | GND     | -     | Ground | Ground                                                                                                                                                                                                                                                                                                                |  |  |  |

| 39  | RFoutAM | 0     | _      | Differential output A Pair. 50- $\Omega$ resistor pullup to V <sub>CC</sub> is integrated.                                                                                                                                                                                                                            |  |  |  |

Copyright © 2025 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信 5

Product Folder Links: LMX2624-SP

## 表 4-1. Pin Functions (続き)

| PIN |            | I/O  | TYPE        | DESCRIPTION                                                                                                                                                                                        |  |  |  |  |

|-----|------------|------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NO. | NAME       | _ ″0 | ITPE        | DESCRIPTION                                                                                                                                                                                        |  |  |  |  |

| 40  | RFoutAP    | 0    | _           | Differential output A Pair. 50- $\Omega$ resistor pullup to V <sub>CC</sub> is integrated.                                                                                                         |  |  |  |  |

| 41  | GND        | -    | Ground      | Ground                                                                                                                                                                                             |  |  |  |  |

| 42  | VccBUF     | _    | _           | Output buffer supply. Requires connecting 0.1-µF capacitor to ground.                                                                                                                              |  |  |  |  |

| 43  | GND        | _    | Ground      | Ground                                                                                                                                                                                             |  |  |  |  |

| 44  | VccVCO2    | -    | _           | VCO supply. Recommend connecting 0.1-µF and 10-µF capacitor to ground.                                                                                                                             |  |  |  |  |

| 45  | VbiasVCO2  | -    | _           | VCO bias. Requires connecting 1-µF capacitor to ground.                                                                                                                                            |  |  |  |  |

| 46  | SysRefReq  | 1    | _           | SYSREF request single ended input for JESD204B support.                                                                                                                                            |  |  |  |  |

| 47  | VrefVCO2   | _    | _           | VCO supply reference. Requires connecting 10-µF capacitor to ground.                                                                                                                               |  |  |  |  |

| 48  | RECAL_EN   | I    | _           | Enables the automatic recalibration feature. Low on this pin does not trigger calibration.<br>High on this means the calibration is triggered whenever the device is unlocked after certain delay. |  |  |  |  |

| 49  | CDIV0      | I    | 4-level pin | Controls the Channel Divider along with CDIV2 and CDIV1 in Pin-mode option. Refer<br>Pin-mode description details in Pin-Mode Integer Frequency Generation for more<br>details.                    |  |  |  |  |

| 50  | CDIV1      | I    | 4-level pin | Controls the Channel Divider along with CDIV0 and CDIV2 in Pin-mode option. Refer<br>Pin-mode description details in Pin-Mode Integer Frequency Generation for more<br>details.                    |  |  |  |  |

| 51  | CDIV2      | I    | 4-level pin | Controls the Channel Divider along with CDIV1 and CDIV0 in Pin-mode option. Refer<br>Pin-mode description details in Pin-Mode Integer Frequency Generation for more<br>details.                    |  |  |  |  |

| 52  | GND        | -    | Ground      | Ground                                                                                                                                                                                             |  |  |  |  |

| 53  | VbiasVARAC | _    | _           | VCO Varactor bias. Requires connecting 10-µF capacitor to ground.                                                                                                                                  |  |  |  |  |

| 54  | GND        | -    | Ground      | Ground                                                                                                                                                                                             |  |  |  |  |

| 55  | Vtune      | I    | _           | VCO tuning voltage input.                                                                                                                                                                          |  |  |  |  |

| 56  | VrefVCO    | -    | _           | VCO supply reference. Requires connecting 10-µF capacitor to ground.                                                                                                                               |  |  |  |  |

| 57  | VccVCO     | -    | _           | VCO supply. Recommend connecting 0.1-µF and 10-µF capacitor to ground.                                                                                                                             |  |  |  |  |

| 58  | VregVCO    | -    | _           | VCO regulator node. Requires connecting 1-µF capacitor to ground.                                                                                                                                  |  |  |  |  |

| 59  | GND        | _    | Ground      | Ground                                                                                                                                                                                             |  |  |  |  |

| 60  | GND        | -    | Ground      | Ground                                                                                                                                                                                             |  |  |  |  |

| 61  | NC         | -    | NC          | No Connect                                                                                                                                                                                         |  |  |  |  |

| 62  | NDIV5      | I    | 4-level pin | Integer N divider bit 5 in Pin-mode. This is part of NDIV5-NDIV0, 6 bit value for N divider setting. Refer Pin-mode description details in Pin-Mode Integer Frequency Generation for more details. |  |  |  |  |

| 63  | NDIV4      | I    | 4-level pin | Integer N divider bit 4 in Pin-mode. This is part of NDIV5-NDIV0, 6 bit value for N divider setting. Refer Pin-mode description details in Pin-Mode Integer Frequency Generation for more details. |  |  |  |  |

| 64  | NDIV3      | I    | 4-level pin | Integer N divider bit 3 in Pin-mode. This is part of NDIV5-NDIV0, 6 bit value for N divider setting. Refer Pin-mode description details in Pin-Mode Integer Frequency Generation for more details. |  |  |  |  |

## **5** Specifications

## 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                    |                                                      | MIN  | MAX                  | UNIT            |

|--------------------|------------------------------------------------------|------|----------------------|-----------------|

| V <sub>CC</sub>    | Power supply voltage <sup>(1)</sup>                  | -0.3 | 3.6                  | V               |

| V <sub>DIG</sub>   | Digital pin voltage (SYNC, SysRefReq, RECAL_EN, CAL) | -0.3 | V <sub>CC</sub> +0.3 | V               |

| V <sub>OSCin</sub> | Differential AC voltage between OSCinP and OSCinN    |      | 2.1                  | V <sub>PP</sub> |

| TJ                 | Junction temperature                                 | -55  | 150                  | °C              |

| T <sub>stg</sub>   | Storage temperature                                  | -65  | 150                  | °C              |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 5.2 ESD Ratings

|                                     |                         |                                                                      | VALUE | UNIT |

|-------------------------------------|-------------------------|----------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> Electrostatic di | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>    | ±2500 | V    |

|                                     |                         | Charged device model (CDM), per ANSI/ESDA/ JEDEC JS-002, all pins(2) | ±500  | v    |

(1) JEDEC document JEP155 states that 500 V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500 V HBM is possible with the necessary precautions.

## **5.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                 |                      | MIN | NOM | MAX  | UNIT |

|-----------------|----------------------|-----|-----|------|------|

| V <sub>CC</sub> | Power supply voltage | 3.2 | 3.3 | 3.45 | V    |

| T <sub>C</sub>  | Case temperature     | -55 | 25  | 125  | °C   |

## **5.4 Thermal Information**

|                       | THERMAL METRIC <sup>(1)</sup>                            | CQFP    | UNIT |

|-----------------------|----------------------------------------------------------|---------|------|

|                       |                                                          | 64 PINS |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance                   | 22.7    | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance <sup>(2)</sup> | 7.3     | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance                     | 7.6     | °C/W |

| Ψյτ                   | Junction-to-top characterization parameter               | 2.2     | °C/W |

| Ψјв                   | Junction-to-board characterization parameter             | 7.4     | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance             | 1.0     | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application note.

(2) DAP

#### **5.5 Electrical Characteristics**

$3.2 \text{ V} \le \text{V}_{CC} \le 3.45 \text{ V}, -55^{\circ}\text{C} \le \text{T}_{C} \le +125^{\circ}\text{C}.$ , OSCIN = 100MHz, SM Clock = 12.5MHz, Typical values are at  $\text{V}_{CC} = 3.3 \text{ V}, 25^{\circ}\text{C}$  (unless otherwise noted).

|                 | PARAMETER                                                                 | -                                                                                                                                                                                                                                                                                                                              | TEST CONDITION   | S                             | MIN | TYP MAX  | UNIT       |

|-----------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------|-----|----------|------------|

| POWER           | SUPPLY                                                                    |                                                                                                                                                                                                                                                                                                                                |                  |                               |     |          |            |

| I <sub>CC</sub> | Supply current (VCO output)                                               | $\begin{tabular}{l} \hline $OUTBUFFA_PD$ = 0, \\ $OUTBUFFB_PD$ = 1 \\ $OUTBUFFA_MU$ \\ $XSEL = 1$ \\ $OUTBUFFA_DA$ \\ $CCTRL = 7, CPG$ = 7 \\ $f_{OSC} = f_{PD} = 100$ \\ $MHz, f_{VCO} = f_{OUT}$ = 14.5 \ GHz$ \end{tabular}$                                                                                                |                  |                               |     | 480      | mA         |

| I <sub>cc</sub> | Supply current (channel divider output)                                   | $\begin{array}{c} -14.5  \text{GHz} \\ \hline \text{OUTBUFFA_PD} \\ = 0, \\ \text{OUTBUFFB_PD} \\ = 1 \\ \text{OUTBUFFA_MU} \\ \text{XSEL} = 0 \\ \text{OUTBUFFA_DA} \\ \text{CCTRL} = 7, \text{CPG} \\ = 7 \\ \hline f_{OSC} = f_{PD} = 100 \\ \text{MHz}, f_{VCO} = \\ 15 \text{Ghz}, f_{OUT} = 7 \\ \text{GHz} \end{array}$ |                  |                               |     | 640      | mA         |

| I <sub>CC</sub> | Supply current (Doubler output)                                           | $\begin{array}{c} \text{OUTBUFFA}_{PD} \\ = 0, \\ \text{OUTBUFFB}_{PD} \\ = 1 \\ \text{OUTA}_{MUX} = 2 \\ \text{OUTBUFFA}_{DA} \\ \text{CCTRL} = 7, \\ \text{CPG} \\ = 7 \\ f_{OSC} = f_{PD} = 100 \\ \text{MHz}, \\ f_{VCO} = 12 \\ \text{GHz} \\ f_{OUT} = 24 \\ \text{GHz} \end{array}$                                     |                  |                               |     | 630      | mA         |

| Icc             | Supply current (Doubler output on both RFOUTA and RFOUTB)                 | $\begin{array}{c} OUTBUFFA\_PD \\ = 0, \\ OUTBUFFB\_PD \\ = 0 \\ OUTA\_MUX = 2 \\ OUTBUFFA\_DA \\ CCTRL=7, CPG \\ = 7 \\ f_{OSC} = f_{PD} = 100 \\ MHz, f_{VCO} = \\ 12GHz \\ f_{OUT} = 24 \; GHz \end{array}$                                                                                                                 |                  |                               |     | TBD      | mA         |

| I <sub>CC</sub> | Power on reset current                                                    | RESET = 1<br>(Device wake-up)                                                                                                                                                                                                                                                                                                  |                  | RESET = 1<br>(Device wake-up) |     | 289      | mA         |

| I <sub>CC</sub> | Power down current                                                        | POWERDOWN =<br>1                                                                                                                                                                                                                                                                                                               | POWERDOWN =<br>1 | POWERDOWN =<br>1              |     | 14       | mA         |

|                 |                                                                           | 1                                                                                                                                                                                                                                                                                                                              |                  |                               |     |          |            |

| Fout            | RF output frequency                                                       |                                                                                                                                                                                                                                                                                                                                | -                |                               | 5   | 28000    | MHz        |

| Роит            | Differential output power                                                 | OUTx_PWR = 31                                                                                                                                                                                                                                                                                                                  |                  |                               |     | TBD      | dBm        |

| Роит            | Single-ended output power <sup>(2) (4)</sup>                              | OUTx_PWR = 31                                                                                                                                                                                                                                                                                                                  |                  |                               |     | 3        | dBm        |

| Роит            | Differential output power<br>Single-ended output power <sup>(2) (4)</sup> | OUTx_PWR = 31<br>OUTx_PWR = 31                                                                                                                                                                                                                                                                                                 |                  |                               |     | TBD<br>2 | dBm        |

| Роит            | Differential output power                                                 | OUTX_PWR = 31<br>OUTX_PWR = 31                                                                                                                                                                                                                                                                                                 |                  |                               |     | 2<br>TBD | dBm<br>dBm |

| Роит<br>Роит    | Single-ended output power <sup>(2) (4)</sup>                              | OUTx_PWR = 31                                                                                                                                                                                                                                                                                                                  |                  |                               |     | 2        | dBm        |

| POUT            | Differential output power                                                 | OUTx_PWR = 31                                                                                                                                                                                                                                                                                                                  |                  |                               |     | TBD      | dBm        |

8 資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2025 Texas Instruments Incorporated

| ,                 | less otherwise noted). PARAMETER                       |                                                     | TEST CONDITION                     | 3       | MIN T | YP MAX | UNIT   |

|-------------------|--------------------------------------------------------|-----------------------------------------------------|------------------------------------|---------|-------|--------|--------|

| Роит              | Single-ended output power <sup>(2) (4)</sup>           | OUTx_PWR = 31                                       | f <sub>OUT</sub> = 22 GHz          |         |       | 2      | dBm    |

| Роит              | Differential output power                              | OUTx_PWR = 31                                       | f <sub>OUT</sub> = 18 GHz          |         | Т     | BD     | dBm    |

| Роцт              | Single-ended output power <sup>(2) (4)</sup>           | OUTx_PWR = 31                                       |                                    |         |       | 3      | dBm    |

| Роит              | Differential output power                              | OUTx_PWR =<br>31; VCO output                        | f <sub>OUT</sub> = 15 GHz          |         | Т     | BD     | dBm    |

| Роит              | Single-ended output power <sup>(2) (4)</sup>           | OUTx_PWR =<br>31; VCO output                        | f <sub>OUT</sub> = 15 GHz          |         |       | 3      | dBm    |

| Роит              | Differential output power                              | OUTx_PWR =<br>31; VCO output                        | f <sub>OUT</sub> = 7.5 GHz         |         | Т     | BD     | dBm    |

| Роит              | Single-ended output power <sup>(2) (4)</sup>           | OUTx_PWR =<br>31; VCO output                        | f <sub>OUT</sub> = 7.5GHz          |         |       | 7      | dBm    |

| DOUT              | Differential output power                              | OUTx_PWR =<br>31; VCO output                        | f <sub>OUT</sub> = 4 GHz           |         | т     | BD     | dBm    |

| DOUT              | Single-ended output power <sup>(2) (4)</sup>           | OUTx_PWR =<br>31; VCO output                        | f <sub>OUT</sub> = 4 GHz           |         |       | 6      | dBm    |

| H <sub>3/2</sub>  | 1/2 Harmonic, single ended measurement                 | F <sub>out</sub> = 2 x F <sub>vco</sub> =<br>24 GHz | Measured at<br>12GHz<br>frequency; |         | т     | BD     | dBc    |

| H <sub>3/2</sub>  | 1/2 Harmonic, differential ended                       | F <sub>out</sub> = 2 x F <sub>vco</sub> =<br>24 GHz | Measured at<br>12GHz<br>frequency; |         |       | -55    | dBc    |

| H <sub>3/2</sub>  | 3/2 Harmonic, single ended measurement                 | F <sub>out</sub> = 2 x F <sub>vco</sub> =<br>16 GHz | Measured at<br>24GHz frequency     |         | Т     | BD     | dBc    |

| H <sub>3/2</sub>  | 3/2 Harmonic, differential ended measurement           | $F_{out}$ = 2 x $F_{vco}$ = 16 GHz                  | Measured at<br>24GHz frequency     |         | т     | BD     | dBc    |

| P <sub>mute</sub> | Single-ended output power leakage when output is muted | Fout = 24 GHz                                       |                                    |         |       | -50    | dBm    |

| P <sub>mute</sub> | Single-ended output power leakage when output is muted | Fout = 12 GHz                                       |                                    |         |       | -51    | dBm    |

| P <sub>mute</sub> | Single-ended output power leakage when output is muted | Fout = 6 GHz                                        |                                    |         |       | -91    | dBm    |

| илте              | Mute enable time                                       | Fout = 12 GHz                                       |                                    |         | 2     | 200    | ns     |

| UNMUTE            | Mute disable time                                      | Fout = 12 GHz                                       |                                    |         | 2     | 200    | ns     |

| isoCH             | Channel to channel isolation (Doubler to VCO)          | RFOUTA = 24<br>GHz; RFOUTB =<br>12 GHz              |                                    |         |       | -39    | dBC    |

| isoCH             | Channel to channel isolation (VCO to CH divider)       | RFOUTA = 12<br>GHz; RFOUTB =<br>6 GHz               |                                    |         |       | -53    | dBC    |

| isoCH             | Channel to channel isolation (Doubler to CH divider)   | RFOUTA = 24<br>GHz; RFOUTB =<br>6 GHz               |                                    |         |       | -41    | dBC    |

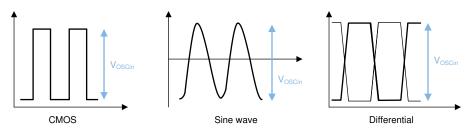

| Phase<br>Noise    | RF Output Frequency Phase Noise                        | Fout = 24 GHz                                       |                                    | 1 KHz   |       | -87    | dBc/Hz |

| Phase<br>Noise    | RF Output Frequency Phase Noise                        | Fout = 24 GHz                                       |                                    | 10 KHz  | <br>  | -99    | dBc/Hz |

| Phase<br>Noise    | RF Output Frequency Phase Noise                        | Fout = 24 GHz                                       |                                    | 100 KHz | -1    | 101    | dBc/Hz |

| Phase<br>Noise    | RF Output Frequency Phase Noise                        | Fout = 24 GHz                                       |                                    | 1 MHz   | -     | 113    | dBc/Hz |

| Phase<br>Noise    | RF Output Frequency Phase Noise                        | Fout = 24 GHz                                       |                                    | 10 MHz  | -1    | 137    | dBc/Hz |

| Phase<br>Noise    | RF Output Frequency Phase Noise                        | Fout = 24 GHz                                       |                                    | 100 MHz | -1    | 151    | dBc/Hz |

| Phase<br>Noise    | RF Output Frequency Phase Noise                        | Fout = 15 GHz                                       |                                    | 1 KHz   |       | -97    | dBc/Hz |

| Phase<br>Noise    | RF Output Frequency Phase Noise                        | Fout = 15 GHz                                       |                                    | 10 KHz  | -1    | 104    | dBc/Hz |

Copyright © 2025 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信 9

| 20 0 (un           | less otherwise noted). PARAMETER                                           |                                                                                                                                  | TEST CONDITION    | S                                       | MIN   | ТҮР  | MAX  | UNIT            |

|--------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------|-------|------|------|-----------------|

| Phase              | RF Output Frequency Phase Noise                                            | Fout = 15 GHz                                                                                                                    |                   | 100 KHz                                 |       | -104 |      | dBc/Hz          |

| Noise              | RF Oulput Frequency Phase Noise                                            |                                                                                                                                  |                   |                                         |       | -104 |      |                 |

| Phase<br>Noise     | RF Output Frequency Phase Noise                                            | Fout = 15 GHz                                                                                                                    |                   | 1 MHz                                   |       | -117 |      | dBc/Hz          |

| Phase<br>Noise     | RF Output Frequency Phase Noise                                            | Fout = 15 GHz                                                                                                                    |                   | 10 MHz                                  |       | -140 |      | dBc/Hz          |

| Phase<br>Noise     | RF Output Frequency Phase Noise                                            | Fout = 15 GHz                                                                                                                    |                   | 100 MHz                                 |       | -156 |      | dBc/Hz          |

| Jitter             | RMS Jitter                                                                 | Fout = 24 GHz,<br>Integration range<br>1 KHz to 100<br>MHz                                                                       |                   |                                         |       | 56   |      | fs              |

| Jitter             | RMS Jitter                                                                 | Fout = 24 GHz,<br>Integration range<br>1 KHz to 12 GHz;<br>No filter in clock<br>output                                          |                   |                                         |       | TBD  |      | fs              |

| Skew               | Skew between RFOUTA and RFOUTB                                             | RFOUTA =<br>RFOUTB = 4GHz                                                                                                        |                   |                                         |       | 7    |      | ps              |

|                    | NAL PATH                                                                   | ·                                                                                                                                | ·                 |                                         |       |      |      |                 |

| f <sub>OSCin</sub> | Reference input frequency                                                  | OSC_2X = 0                                                                                                                       | OSC_2X = 0        | OSC_2X = 0                              | 5     |      | 1200 | MHz             |

| f <sub>OSCin</sub> | Reference input frequency                                                  | OSC_2X = 1                                                                                                                       | OSC_2X = 1        | OSC_2X = 1                              | 5     |      | 200  |                 |

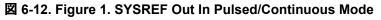

| V <sub>OSCin</sub> | Reference input voltage                                                    | Single-ended AC<br>coupled sine<br>wave input with<br>complementary<br>side AC coupled<br>to ground with 50<br>$\Omega$ resistor |                   | f <sub>OSCin</sub> ≥ 20 MHz             | 0.4   |      | 2    | V <sub>PP</sub> |

| V <sub>OSCin</sub> | Reference input voltage                                                    | Single-ended AC coupled sine wave input with complementary side AC coupled to ground with 50 $\Omega$ resistor                   |                   | 10 MHz ≤ f <sub>OSCin</sub><br>< 20 MHz | 0.8   |      | 2    | V <sub>PP</sub> |

| VOSCin             | Reference input voltage                                                    | Single-ended AC coupled sine wave input with complementary side AC coupled to ground with 50 $\Omega$ resistor                   |                   | 5 MHz ≤ f <sub>OSCin</sub> <<br>10 MHz  | 1.6   |      | 2    | Vpp             |

| PHASE DE           | TECTOR AND CHARGE PUMP                                                     |                                                                                                                                  |                   |                                         |       |      |      |                 |

| f <sub>PD</sub>    | Phase detector frequency <sup>(1)</sup>                                    | MASH_ORDER<br>= 0                                                                                                                | MASH_ORDER<br>= 0 | MASH_ORDER<br>= 0                       | 0.125 |      | 250  | MHz             |

| f <sub>PD</sub>    | Phase detector frequency <sup>(1)</sup>                                    | MASH_ORDER<br>> 0                                                                                                                | MASH_ORDER<br>> 0 | MASH_ORDER<br>> 0                       | 5     |      | 200  | MHz             |

| I <sub>CPout</sub> | Charge-pump leakage current                                                | CPG = 0                                                                                                                          | CPG = 0           | CPG = 0                                 |       | 15   |      | nA              |

| I <sub>CPout</sub> | Effective charge pump current. This is the sum of the up and down currents | CPG = 4                                                                                                                          | CPG = 4           | CPG = 4                                 |       | 3    |      | mA              |

| I <sub>CPout</sub> | Effective charge pump current. This is the sum of the up and down currents | CPG = 1                                                                                                                          | CPG = 1           | CPG = 1                                 |       | 6    |      | mA              |

| I <sub>CPout</sub> | Effective charge pump current. This is the sum of the up and down currents | CPG = 5                                                                                                                          | CPG = 5           | CPG = 5                                 |       | 9    |      | mA              |

| I <sub>CPout</sub> | Effective charge pump current. This is the sum of the up and down currents | CPG = 3                                                                                                                          | CPG = 3           | CPG = 3                                 |       | 12   |      | mA              |

| (                     |                                                                            |                                                                        |                                                                        |                                                          |      |  |        |

|-----------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------|------|--|--------|

|                       | PARAMETER TEST CONDITIONS                                                  |                                                                        | MIN TYP                                                                | MAX                                                      | UNIT |  |        |

| I <sub>CPout</sub>    | Effective charge pump current. This is the sum of the up and down currents | CPG = 7                                                                | CPG = 7                                                                | CPG = 7                                                  | 15   |  | mA     |

| PN <sub>PLL_1/f</sub> | Normalized PLL 1/f noise                                                   | f <sub>PD</sub> = 100 MHz,<br>f <sub>VCO</sub> = 12 GHz <sup>(3)</sup> | f <sub>PD</sub> = 100 MHz,<br>f <sub>VCO</sub> = 12 GHz <sup>(3)</sup> | $f_{PD}$ = 100 MHz,<br>$f_{VCO}$ = 12 GHz <sup>(3)</sup> | -129 |  | dBc/Hz |

| PN <sub>PLL_FOM</sub> | Normalized PLL noise floor                                                 | f <sub>PD</sub> = 100 MHz,<br>f <sub>VCO</sub> = 12 GHz <sup>(3)</sup> | f <sub>PD</sub> = 100 MHz,<br>f <sub>VCO</sub> = 12 GHz <sup>(3)</sup> | $f_{PD}$ = 100 MHz,<br>$f_{VCO}$ = 12 GHz <sup>(3)</sup> | -236 |  | dBc/Hz |

| (ui               | PARAMETER       |                                     | TEST CONDITIONS                     |         | MIN TYP MAX |       |        |  |

|-------------------|-----------------|-------------------------------------|-------------------------------------|---------|-------------|-------|--------|--|

| <b>VCO CHA</b>    | RACTERISTICS    |                                     |                                     |         |             |       |        |  |

| f <sub>VCO</sub>  | VCO frequency   |                                     |                                     |         | 7500        | 15000 | MHz    |  |

| PN <sub>VCO</sub> | VCO phase noise | VCO1<br>f <sub>VCO</sub> = 8.1 GHz  | VCO1<br>f <sub>VCO</sub> = 8.1 GHz  | 100 kHz | -105        |       | dBc/Hz |  |

| PN <sub>VCO</sub> | VCO phase noise | VCO1<br>f <sub>VCO</sub> = 8.1 GHz  | VCO1<br>f <sub>VCO</sub> = 8.1 GHz  | 1 MHz   | -127        |       | dBc/Hz |  |

| PN <sub>VCO</sub> | VCO phase noise | VCO1<br>f <sub>VCO</sub> = 8.1 GHz  | VCO1<br>f <sub>VCO</sub> = 8.1 GHz  | 10 MHz  | -148        |       | dBc/Hz |  |

| PN <sub>VCO</sub> | VCO phase noise | VCO1<br>f <sub>VCO</sub> = 8.1 GHz  | VCO1<br>f <sub>VCO</sub> = 8.1 GHz  | 100 MHz | -155        |       | dBc/Hz |  |

| PN <sub>VCO</sub> | VCO phase noise | VCO2<br>f <sub>VCO</sub> = 9.3 GHz  | VCO2<br>f <sub>VCO</sub> = 9.3 GHz  | 100 kHz | -103        |       | dBc/Hz |  |

| PN <sub>VCO</sub> | VCO phase noise | VCO2<br>f <sub>VCO</sub> = 9.3 GHz  | VCO2<br>f <sub>VCO</sub> = 9.3 GHz  | 1 MHz   | -125        |       | dBc/Hz |  |

| PN <sub>VCO</sub> | VCO phase noise | VCO2<br>f <sub>VCO</sub> = 9.3 GHz  | VCO2<br>f <sub>VCO</sub> = 9.3 GHz  | 10 MHz  | -146        |       | dBc/Hz |  |

| PN <sub>VCO</sub> | VCO phase noise | VCO2<br>f <sub>VCO</sub> = 9.3 GHz  | VCO2<br>f <sub>VCO</sub> = 9.3 GHz  | 100 MHz | -153        |       | dBc/Hz |  |

| PN <sub>VCO</sub> | VCO phase noise | VCO3<br>f <sub>VCO</sub> = 10.4 GHz | VCO3<br>f <sub>VCO</sub> = 10.4 GHz | 100 kHz | -103        |       | dBc/Hz |  |

| PN <sub>VCO</sub> | VCO phase noise | VCO3<br>f <sub>VCO</sub> = 10.4 GHz | VCO3<br>f <sub>VCO</sub> = 10.4 GHz | 1 MHz   | -125        |       | dBc/Hz |  |

| PN <sub>VCO</sub> | VCO phase noise | VCO3<br>f <sub>VCO</sub> = 10.4 GHz | VCO3<br>f <sub>VCO</sub> = 10.4 GHz | 10 MHz  | -147        |       | dBc/Hz |  |

| PN <sub>VCO</sub> | VCO phase noise | VCO3<br>f <sub>VCO</sub> = 10.4 GHz | VCO3<br>f <sub>VCO</sub> = 10.4 GHz | 100 MHz | -158        |       | dBc/Hz |  |

| PN <sub>VCO</sub> | VCO phase noise | VCO4<br>f <sub>VCO</sub> = 11.4 GHz | VCO4<br>f <sub>VCO</sub> = 11.4 GHz | 100 kHz | -101        |       | dBc/Hz |  |

| PN <sub>VCO</sub> | VCO phase noise | VCO4<br>f <sub>VCO</sub> = 11.4 GHz | VCO4<br>f <sub>VCO</sub> = 11.4 GHz | 1 MHz   | -124        |       | dBc/Hz |  |

| PN <sub>VCO</sub> | VCO phase noise | VCO4<br>f <sub>VCO</sub> = 11.4 GHz | VCO4<br>f <sub>VCO</sub> = 11.4 GHz | 10 MHz  | -146        |       | dBc/Hz |  |

| PN <sub>VCO</sub> | VCO phase noise | VCO4<br>f <sub>VCO</sub> = 11.4 GHz | VCO4<br>f <sub>VCO</sub> = 11.4 GHz | 100 MHz | -158        |       | dBc/Hz |  |

| PN <sub>VCO</sub> | VCO phase noise | VCO5<br>f <sub>VCO</sub> = 12.5 GHz | VCO5<br>f <sub>VCO</sub> = 12.5 GHz | 100 kHz | -102        |       | dBc/Hz |  |

| PN <sub>VCO</sub> | VCO phase noise | VCO5<br>f <sub>VCO</sub> = 12.5 GHz | VCO5<br>f <sub>VCO</sub> = 12.5 GHz | 1 MHz   | -126        |       | dBc/Hz |  |

| PN <sub>VCO</sub> | VCO phase noise | VCO5<br>f <sub>VCO</sub> = 12.5 GHz | VCO5<br>f <sub>VCO</sub> = 12.5 GHz | 10 MHz  | -147        |       | dBc/Hz |  |

| PN <sub>VCO</sub> | VCO phase noise | VCO5<br>f <sub>VCO</sub> = 12.5 GHz | VCO5<br>f <sub>VCO</sub> = 12.5 GHz | 100 MHz | -156        |       | dBc/Hz |  |

| PN <sub>VCO</sub> | VCO phase noise | VCO6<br>f <sub>VCO</sub> = 13.6 GHz | VCO6<br>f <sub>VCO</sub> = 13.6 GHz | 100 kHz | -101        |       | dBc/Hz |  |

| PN <sub>VCO</sub> | VCO phase noise | VCO6<br>f <sub>VCO</sub> = 13.6 GHz | VCO6<br>f <sub>VCO</sub> = 13.6 GHz | 1 MHz   | -124        |       | dBc/Hz |  |

| PN <sub>VCO</sub> | VCO phase noise | VCO6<br>f <sub>VCO</sub> = 13.6 GHz | VCO6<br>f <sub>VCO</sub> = 13.6 GHz | 10 MHz  | -146        |       | dBc/Hz |  |

| PN <sub>VCO</sub> | VCO phase noise | VCO6<br>f <sub>VCO</sub> = 13.6 GHz | VCO6<br>f <sub>VCO</sub> = 13.6 GHz | 100 MHz | -160        |       | dBc/Hz |  |

| PN <sub>VCO</sub> | VCO phase noise | VCO7<br>f <sub>VCO</sub> = 14.7 GHz | VCO7<br>f <sub>VCO</sub> = 14.7 GHz | 100 kHz | -101        |       | dBc/Hz |  |

| PN <sub>VCO</sub> | VCO phase noise | VCO7<br>f <sub>VCO</sub> = 14.7 GHz | VCO7<br>f <sub>VCO</sub> = 14.7 GHz | 1 MHz   | -124        |       | dBc/Hz |  |

| PN <sub>VCO</sub> | VCO phase noise | VCO7<br>f <sub>VCO</sub> = 14.7 GHz | VCO7<br>f <sub>VCO</sub> = 14.7 GHz | 10 MHz  | -146        |       | dBc/Hz |  |

| PN <sub>VCO</sub> | VCO phase noise | VCO7<br>f <sub>VCO</sub> = 14.7 GHz | VCO7<br>f <sub>VCO</sub> = 14.7 GHz | 100 MHz | -157        |       | dBc/Hz |  |

12 資料に関するフィードバック (ご意見やお問い合わせ)を送信

Copyright © 2025 Texas Instruments Incorporated

| PARAMETER        |                                                           | TEST CONDITIONS                                                                                                                                         | MIN TYP MAX | UNIT  |

|------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|

|                  | Lock time                                                 | No Assist mode;<br>RFOUTA from<br>9.5GHz to<br>9.52GHz;Loop<br>Bandwidth =<br>300KHz, PFD<br>Frequency =<br>100MHz;                                     | 3000        | μs    |

|                  | Lock time                                                 | Full Assist mode,<br>Loop Bandwidth<br>= 300KHz, PFD<br>Frequency =<br>100MHz;<br>RFOUTA from<br>9.5GHz to<br>9.52GHz, 1PPM<br>settling around<br>RFOUT | 16          | μs    |

| K <sub>VCO</sub> | VCO Gain                                                  | 8.1 GHz                                                                                                                                                 | 94          | MHz/V |

| K <sub>VCO</sub> | VCO Gain                                                  | 9.3 GHz                                                                                                                                                 | 106         | MHz/V |

| K <sub>VCO</sub> | VCO Gain                                                  | 10.4 GHz                                                                                                                                                | 122         | MHz/V |

| K <sub>VCO</sub> | VCO Gain                                                  | 11.4 GHz                                                                                                                                                | 148         | MHz/V |

| K <sub>VCO</sub> | VCO Gain                                                  | 12.5 GHz                                                                                                                                                | 185         | MHz/V |

| K <sub>VCO</sub> | VCO Gain                                                  | 13.6 GHz                                                                                                                                                | 202         | MHz/V |

| K <sub>VCO</sub> | VCO Gain                                                  | 14.7 GHz                                                                                                                                                | 233         | MHz/V |

| ∆T <sub>CL</sub> | Allowable temperature drift when VCO is not re-calibrated | configured in SPI mode                                                                                                                                  | 125         | °C    |

| H2               | VCO second harmonic                                       | f <sub>VCO</sub> = 8 GHz,<br>divider disabled                                                                                                           | -30         | dBc   |

| НЗ               | VCO third harmonic                                        | f <sub>VCO</sub> = 8 GHz,<br>divider disabled                                                                                                           | -25         | dBc   |

|                 | PARAMETER                                                                            | TEST CONDITIONS |  |                          | MIN                   | TYP     | MAX  | UNIT |

|-----------------|--------------------------------------------------------------------------------------|-----------------|--|--------------------------|-----------------------|---------|------|------|

| DIGITAL I       | DIGITAL INTERFACE (Applies to SCK, SDI, CSB, CAL, RECAL_EN, MUXout, SYNC, SysRefReq) |                 |  |                          |                       |         |      |      |

| VIH             | High-level input voltage                                                             |                 |  |                          | 1.6                   |         |      | V    |

| V <sub>IL</sub> | Low-level input voltage                                                              |                 |  |                          |                       |         | 0.4  | V    |

| IIH             | High-level input current                                                             |                 |  |                          | -100                  |         | 100  | μA   |

| IIL             | Low-level input current                                                              |                 |  |                          | -100                  |         | 100  | μA   |

| V <sub>OH</sub> | High-level output voltage                                                            | MUXout pin      |  | Load current = –<br>5 mA | V <sub>CC</sub> - 0.6 |         |      | V    |

| V <sub>OL</sub> | Low-level output voltage                                                             | MUXout pin      |  | Load current = 5<br>mA   |                       |         | 0.6  | V    |

|                 | SYSREF Output Common mode voltage                                                    |                 |  |                          |                       | TBD     |      | V    |

|                 | SYREF Output Swing                                                                   |                 |  |                          |                       | TBD     |      | V    |

|                 | SYSREF Frequency range                                                               |                 |  |                          |                       | TBD     |      | MHz  |

|                 | SYSREF delay step size                                                               |                 |  |                          |                       | TBD     |      | ps   |

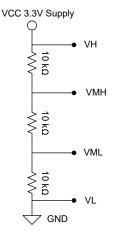

| VL              | CDIV0, CDIV1, CDIV2 Voltage levels                                                   |                 |  |                          | 0                     |         | 0.4  | V    |

| VML             | CDIV0, CDIV1, CDIV2 Voltage levels                                                   |                 |  |                          | 0.8                   | VCC/3   | 1.4  | V    |

| VMH             | CDIV0, CDIV1, CDIV2 Voltage levels                                                   |                 |  |                          | 1.9                   | 2*VCC/3 | 2.5  | V    |

| VH              | CDIV0, CDIV1, CDIV2 Voltage levels                                                   |                 |  |                          | 3                     | VCC     | 3.45 | V    |

| VL              | NDIV0, NDIV1, NDIV2, NDIV3,<br>NDIV4, NDIV5 Voltage levels                           |                 |  |                          | 0                     |         | 0.4  | V    |

| VML             | NDIV0, NDIV1, NDIV2, NDIV3,<br>NDIV4, NDIV5 Voltage levels                           |                 |  |                          | 0.8                   | VCC/3   | 1.4  | V    |

| VMH             | NDIV0, NDIV1, NDIV2, NDIV3,<br>NDIV4, NDIV5 Voltage levels                           |                 |  |                          | 1.9                   | 2*VCC/3 | 2.5  | V    |

| VH              | NDIV0, NDIV1, NDIV2, NDIV3,<br>NDIV4, NDIV5 Voltage levels                           |                 |  |                          | 3                     | VCC     | 3.45 | V    |

(1) For lower VCO frequencies, the N divider minimum value can limit the phase-detector frequency.

(2) Single-ended output power obtained after de-embedding microstrip trace losses and matching with a manual tuner. Unused port terminated to 50-Ω load.

(3) The PLL noise contribution is measured using a clean reference and a wide loop bandwidth and is composed into flicker and flat components. PLL\_flat = PLL\_FOM + 20× log(Fvco/Fpd) + 10 × log(Fpd / 1Hz). PLL\_flicker (offset) = PLL\_1/f + 20 × log(Fvco / 1GHz) – 10× log(offset / 10kHz). After these two components are found, the total PLL noise can be calculated as PLL\_Noise = 10 × log(10 PLL\_Flat / 10 + 10 PLL\_flicker / 10)

(4) Output power, spurs, and harmonics can vary based on board layout and components.

## 5.6 Timing Requirements

$(3.2 \text{ V} \le \text{V}_{CC} \le 3.45 \text{ V}, -55^{\circ}\text{C} \le \text{T}_{A} \le +125^{\circ}\text{C}, \text{ except as specified. Nominal values are at V}_{CC} = 3.3 \text{ V}, \text{T}_{A} = 25^{\circ}\text{C})$

|                           |                                        |                    | MIN | NOM | MAX | UNIT |  |  |

|---------------------------|----------------------------------------|--------------------|-----|-----|-----|------|--|--|

| DIGITAL INTER             | DIGITAL INTERFACE WRITE SPECIFICATIONS |                    |     |     |     |      |  |  |

| f <sub>SPI</sub> Write    | SPI write speed                        |                    |     |     | 40  | MHz  |  |  |

| t <sub>CE</sub>           | Clock to enable low time               |                    | 2.5 |     |     | ns   |  |  |

| t <sub>CS</sub>           | Data to clock setup time               |                    | 8.6 |     |     | ns   |  |  |

| t <sub>CH</sub>           | Data to clock hold time                |                    | 0.6 |     |     | ns   |  |  |

| t <sub>CWH</sub>          | Clock pulse width high                 | See Timing Diagram | 5   |     |     | ns   |  |  |

| t <sub>CWL</sub>          | Clock pulse width low                  |                    | 10  |     |     | ns   |  |  |

| t <sub>CES</sub>          | Enable to clock setup time             |                    | 6.5 |     |     | ns   |  |  |

| t <sub>EWH</sub>          | Enable pulse width high                |                    | 5   |     |     | ns   |  |  |

| DIGITAL INTER             | FACE READBACK SPECIFICATIONS           | ·                  | •   |     |     |      |  |  |

| f <sub>SPI</sub> Readback | SPI readback speed                     |                    |     |     | 40  | MHz  |  |  |

|                  |                                      |                    | MIN | NOM | MAX | UNIT |

|------------------|--------------------------------------|--------------------|-----|-----|-----|------|

| t <sub>CE</sub>  | Clock to enable low time             |                    | 2.5 |     |     | ns   |

| t <sub>CS</sub>  | Clock to data wait time              |                    | 8.6 |     |     | ns   |

| t <sub>CWH</sub> | Clock pulse width high               |                    | 10  |     |     | ns   |

| t <sub>CWL</sub> | Clock pulse width low                | See Timing Diagram | 10  |     |     | ns   |

| t <sub>CES</sub> | Enable to clock setup time           |                    | 6.5 |     |     | ns   |

| t <sub>EWH</sub> | Enable pulse width high              |                    | 5   |     |     | ns   |

| t <sub>CD</sub>  | Falling clock edge to data wait time |                    | TBD |     |     | ns   |

| SYNC and S       | SYSREFREQ                            |                    |     |     |     |      |

$(3.2 \text{ V} \le \text{V}_{\text{CC}} \le 3.45 \text{ V}, -55^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}, \text{ except as specified. Nominal values are at } \text{V}_{\text{CC}} = 3.3 \text{ V}, \text{T}_{\text{A}} = 25^{\circ}\text{C})$

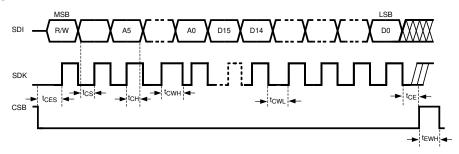

## 5.7 Timing Diagrams

## S-1. Serial Data Input Timing Diagram

There are several other considerations for writing on the SPI:

- The R/W bit must be set to 0.

- The data on SDI pin is clocked into a shift register on each rising edge on the SCK pin.

- The CSB must be held low for data to be clocked. Device is ignore clock pulses if CSB is held high.

- The CSB transition from high to low must occur when SCK is low.

- When SCK and SDI lines are shared between devices, TI recommends hold the CSB line high on the device that is not to be clocked.

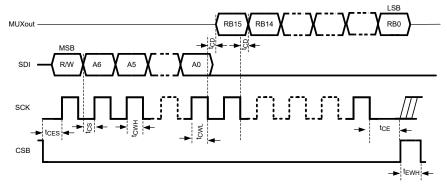

## 5-2. Serial Data Readback Timing Diagram

There are several other considerations for SPI readback:

- The R/W bit must be set to 1.

- The MUXout pin is tristated for the address portion of the transaction, and when there is no transaction

- The data on MUXout becomes available momentarily after the falling edge of SCK and therefore must be read back on the rising edge of SCK.

- The data portion of the transition on the SDI line is always ignored.

## 6 Detailed Description

## 6.1 Overview

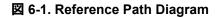

The LMX2624-SP is a high-performance, wideband frequency synthesizer with integrated VCO, output doubler and output divider. The VCO operates from 7500 to 15000 MHz and this can be combined with the output divider and doubler to produce any frequency in the range of 5 MHz to 28 GHz.

The PLL is fractional-N PLL with programmable delta-sigma modulator up to 4<sup>th</sup> order. The fractional denominator is a programmable 32-bit long, which can provide fine frequency steps easily below 1-Hz resolution as well as be used to do exact fractions like 1/3, 7/1000, and many others.

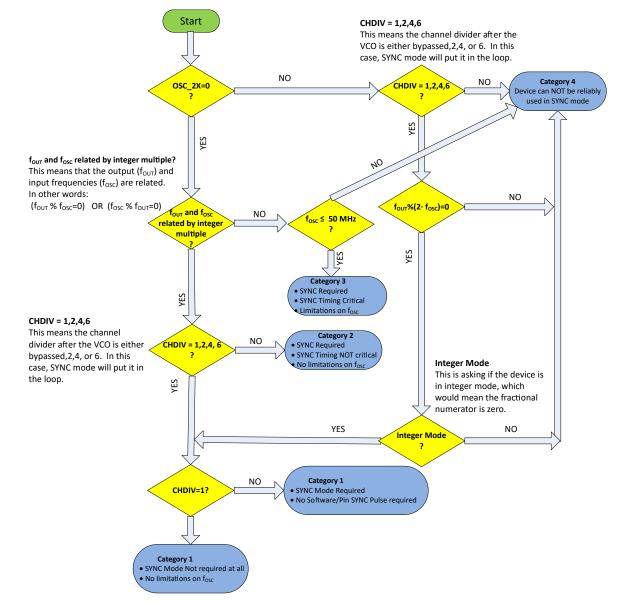

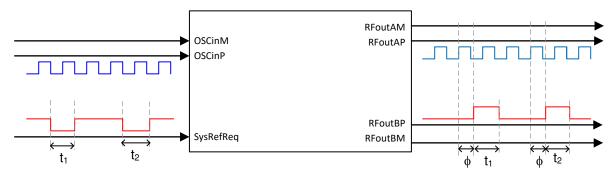

The phase detector frequency goes up to 200MHz in fractional mode and 250MHz in integer mode, although minimum N-divider values must also be taken into account. For applications where deterministic or adjustable phase is desired, the SYNC pin can be used to get the phase relationship between the OSCin and RFout pins deterministic. When this is done, the phase can be adjusted in very fine steps of the VCO period divided by the fractional denominator.

The ultra-fast VCO calibration is designed for applications where the frequency must be swept or abruptly changed. The device has both Pin-mode and SPI-mode options where the frequency can be configured manually using general purpose inputs or programmed using SPI.

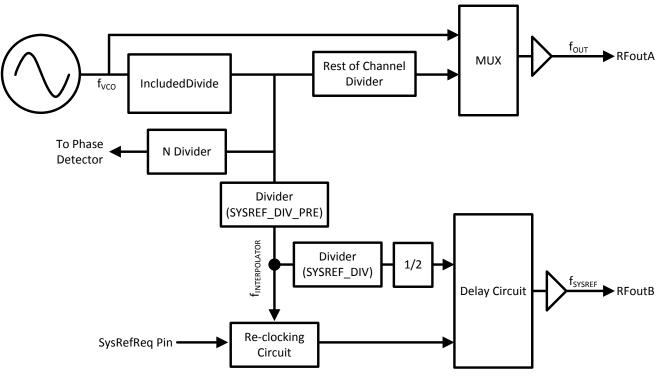

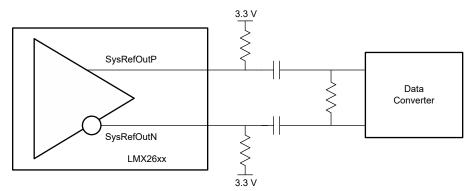

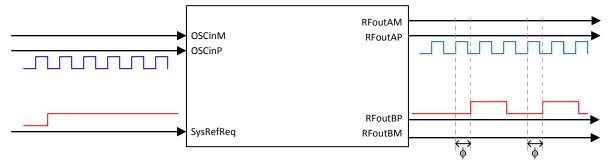

The JESD204B support includes using the RFoutB output to create a differential SYSREF output that can be either a single pulse or a series of pulses that occur at a programmable distance away from the rising edges of the output signal.

The LMX2624-SP device requires only a single 3.3-V power supply. The internal power supplies are provided by integrated LDOs, eliminating the need for high performance external LDOs.

$\pm$  6-1 shows the range of several of the doubler, dividers, and fractional settings.

| 表 6-1. Range of Doubler, Divider, and Fractional Settings |                     |                  |                                  |                                                                                                                                                            |  |  |

|-----------------------------------------------------------|---------------------|------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PARAMETER                                                 | FIELD               | MIN              | MAX                              | COMMENTS                                                                                                                                                   |  |  |

| OSCin doubler                                             | OSC_2X              | 0 (1X)           | 1 (2X)                           | The low noise doubler can be used to increase the phase detector frequency to improve phase noise and avoid spurs. This is in reference to the OSC_2X bit. |  |  |

| Pre-R divider                                             | PLL_R_PRE           | 1 (bypass)       | 128                              | Only use the Pre R divider if the input frequency is too high for the Post R divider.                                                                      |  |  |

| Post-R divider                                            | PLL_R               | 1 (bypass)       | 255                              | The maximum input frequency for the post-R divider is 250 MHz. Use the Pre R divider if necessary.                                                         |  |  |

| N divider                                                 | PLL_N               | ≥ 28             | 524287                           | The minimum divide depends on modulator order and VCO frequency. See $t 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 $                                              |  |  |

| Fractional<br>numerator/<br>denominator                   | PLL_NUM,<br>PLL_DEN | 1 (Integer mode) | 2 <sup>32</sup> – 1 = 4294967295 | The fractional denominator is programmable<br>and can assume any value between 1 and<br>$2^{32} - 1$ ; the denominator is not a fixed value.               |  |  |

| Fractional order                                          | MASH_ORDER          | 0                | 4                                | Order 0 is integer mode and the order can be programmed                                                                                                    |  |  |

| Channel divider                                           | CHDIV               | 1 (bypass)       | 1536                             | This is the series of several dividers. Also, be<br>aware that above 10 GHz, the maximum<br>allowable channel divider value is 6.                          |  |  |

| Output frequency                                          |                     | 5 MHz            | 28 GHz                           | Below 7.6 GHz, Channel Divider is used. 7.6<br>GHz to 15.2 GHz is from VCO. 15.2 GHz to<br>28 GHz is from VCO along with output<br>doubler                 |  |  |

| 表 6-1. | Range of   | Doubler, | Divider,         | and Fr | ractional | Settings |

|--------|------------|----------|------------------|--------|-----------|----------|

| 2011   | i kungo or | Bousier, | <b>D</b> 111001, |        | aotionai  | ooungo   |

## 6.2 Functional Block Diagram

## 6.3 Feature Description

## 6.3.1 Reference Oscillator Input