LMR23630 JAJSEV6E - DECEMBER 2015 - REVISED AUGUST 2020

LMR23630 SIMPLE SWITCHER<sup>®</sup>、36V、3A、同期整流降圧コンバータ

## 1 特長

- 入力電圧範囲:4V~36V

- 3Aの連続出力電流

- 同期整流器内蔵

- 電流モード制御

- 最小スイッチ・オン時間:60ns

- 使いやすい内部補償

- 400kHz のスイッチング周波数と可変周波数を選択可

- PFM および強制 PWM モードのオプション

- 外部クロックへの周波数同期

- PFM オプションのとき、無負荷時の静止電流 75µA

- プリバイアス負荷へのソフト・スタート

- 高いデューティ・サイクルでの動作をサポート

- 高精度イネーブル入力

- ヒカップ・モードによる出力短絡保護

- 過熱保護機能

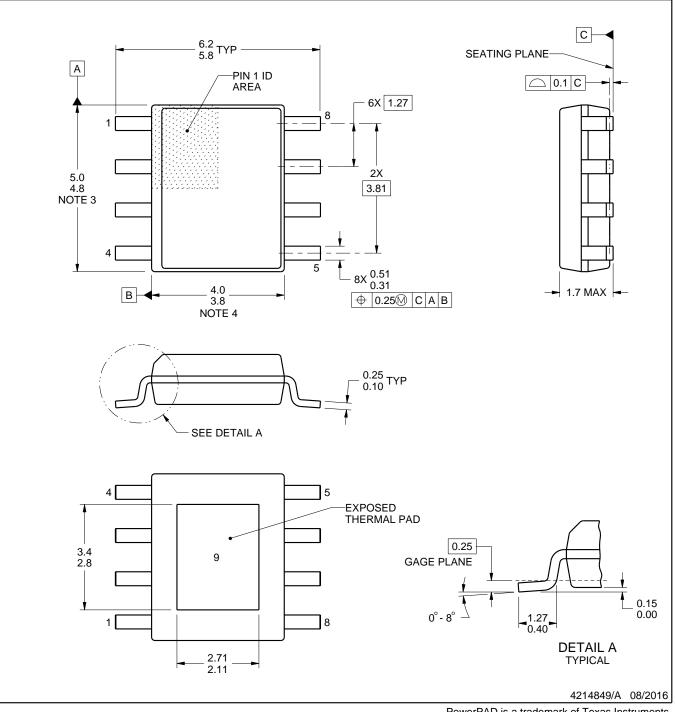

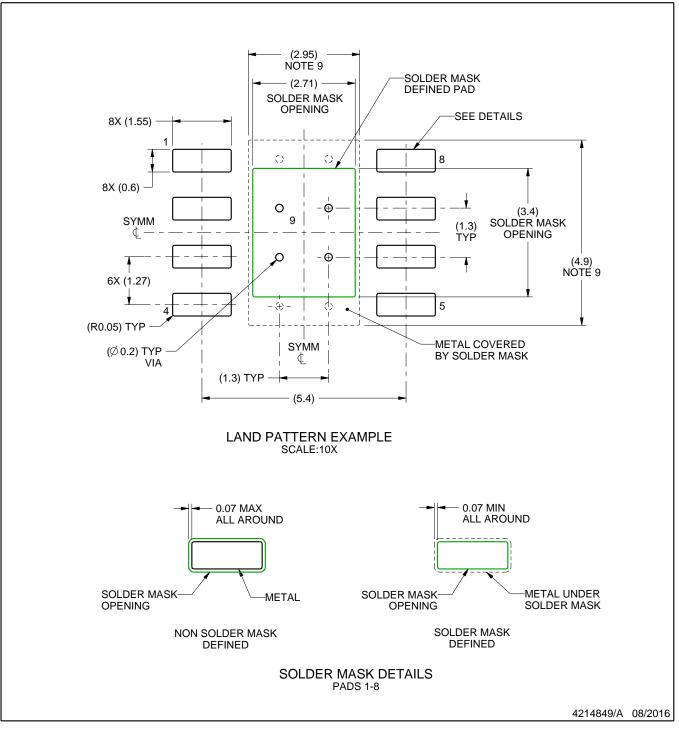

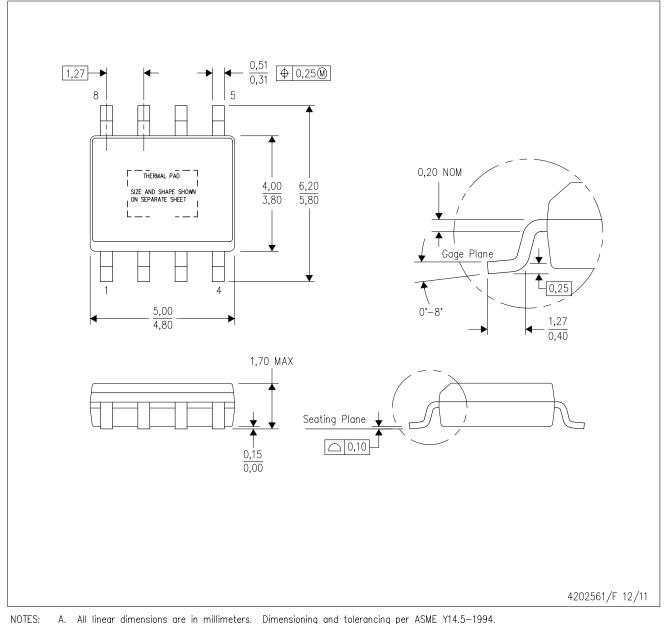

- PowerPAD<sup>™</sup> 付き 8 ピン HSOIC パッケージ

- PowerPAD<sup>™</sup> 付き 12 ピン WSON ウェッタブル・フラ ンク・パッケージ

- LMZM33603 モジュールを使用して、開発期間を短縮

- WEBENCH<sup>®</sup> Power Designer により、LMR23625 を 使用するカスタム設計を作成

# 2 アプリケーション

- ファクトリおよびビルディング・オートメーション・システ ム: PLC CPU、 HVAC 制御、 エレベータ制御

- アセット・トラッキング

- 汎用の広 VIN レギュレーション

## 3 概要

LMR23630 SIMPLE SWITCHER<sup>®</sup> は、使いやすい 36V、3A 同期整流降圧レギュレータです。4V~36V とい う広い入力電圧範囲により、非レギュレーション電源からの 電源調整を行うさまざまな産業用アプリケーションに適して います。ピーク電流モード制御の採用によって、単純な制 御ループ補償とサイクル単位の電流制限を実現していま す。静止電流が 75µA であるため、バッテリ駆動のシステ ムに適しています。シャットダウン電流も 2µA と極めて低 いことから、バッテリ駆動時間のさらなる延長が可能です。 内部ループ補償により、ユーザーはループ補償を設計す る煩雑な作業から解放されます。これによって、外付け部 品の数も最小限に抑えられます。LMR23630 では、軽負 荷時に出力電圧リップルを小さくするための、固定周波数 FPWM モードを選択できます。 拡張ファミリ (HSOIC) とし て、1A (LMR23610) および 2.5A (LMR23625) の負荷 電流オプションを提供しており、いずれもピン互換パッケ ージを採用しているため、PCBレイアウトの簡素化と最適 化が可能になります。高精度のイネーブル入力により、レ ギュレータの制御とシステムの電源シーケンスが単純化さ れます。保護機能として、サイクル単位の電流制限、ヒカッ プ・モードの短絡保護、過剰な消費電力によるサーマル・ シャットダウンが搭載されています。

#### 製品情報

| 部品番号 <sup>(1)</sup> | パッケージ     | 本体サイズ (公称)      |  |

|---------------------|-----------|-----------------|--|

| LMR23630            | HSOIC (8) | 4.89mm × 3.90mm |  |

|                     | WSON (12) | 3.00mm × 3.00mm |  |

利用可能なすべてのオプションに対応する詳細部品番号につい (1)ては、巻末の注文情報を参照してください。

英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、 🐼 www.ti.com で閲覧でき、その内容が常に優先されます。 TI では翻訳の正確性および妥当性につきましては一切保証いたしません。 実際の設計などの前には、必ず 最新版の英語版をご参照くださいますようお願いいたします。

## **Table of Contents**

| 1 | 特長1                                  |

|---|--------------------------------------|

|   | アプリケーション1                            |

|   | 概要1                                  |

|   | Revision History2                    |

| 5 | Device Comparison Table4             |

| 6 | Pin Configuration and Functions4     |

|   | Pin Functions5                       |

| 7 | Specifications6                      |

|   | 7.1 Absolute Maximum Ratings6        |

|   | 7.2 ESD Ratings6                     |

|   | 7.3 Recommended Operating Conditions |

|   | 7.4 Thermal Information7             |

|   | 7.5 Electrical Characteristics7      |

|   | 7.6 Timing Requirements9             |

|   | 7.7 Switching Characteristics9       |

|   | 7.8 Typical Characteristics10        |

| 8 | Detailed Description12               |

|   | 8.1 Overview12                       |

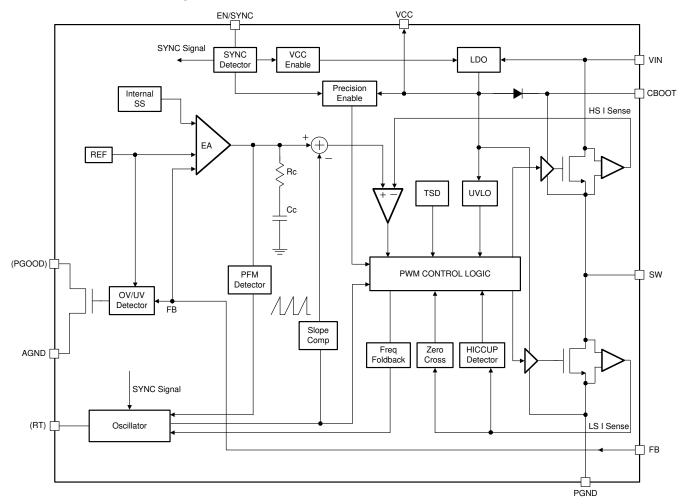

|   | 8.2 Functional Block Diagram12       |

|   | 8.3 Feature Description13            |

| 8.4 Device Functional Modes                           | .20 |

|-------------------------------------------------------|-----|

| 9 Application and Implementation                      | .21 |

| 9.1 Application Information                           |     |

| 9.2 Typical Applications                              |     |

| 10 Power Supply Recommendations                       |     |

| 11 Layout                                             | .28 |

| 11.1 Layout Guidelines                                |     |

| 11.2 Layout Example                                   |     |

| 11.3 Compact Layout for EMI Reduction                 |     |

| 11.4 Ground Plane and Thermal Considerations          |     |

| 11.5 Feedback Resistors                               |     |

| 12 Device and Documentation Support                   | .32 |

| 12.1 Device Support                                   |     |

| 12.2 Receiving Notification of Documentation Updates. |     |

| 12.3 Support Resources                                |     |

| 12.4 Trademarks                                       |     |

| 12.5 静電気放電に関する注意事項                                    |     |

| 12.6 Glossary.                                        |     |

| 13 Mechanical, Packaging, and Orderable               |     |

| Information                                           | 32  |

|                                                       |     |

## **4 Revision History**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Cł | nanges from Revision D (February 2018) to Revision E (July 2020) | Page |

|----|------------------------------------------------------------------|------|

| •  | 文書全体にわたって表、図、相互参照の採番方法を更新                                        | 1    |

| •  | <i>セクション</i> 1 に、LMZM33630 の項目を追加                                | 1    |

|    |                                                                  |      |

## Changes from Revision C (June 2017) to Revision D (February 2018)

| Changes from Revision C (June 2017) to Revision D (Febru                                      | Jary 2018)                        | Page        |

|-----------------------------------------------------------------------------------------------|-----------------------------------|-------------|

| <ul> <li>「アプリケーション」のプログラマブル・ロジック・コントローラの電源</li> </ul>                                         |                                   | ーートメーション・シ  |

| ステムに変更                                                                                        |                                   |             |

| ・「アプリケーション」の多機能プリンタと産業用電源を削除                                                                  |                                   | 1           |

| ・「アプリケーション」の HVAC システムを汎用の広 VIN レギュレー                                                         |                                   |             |

| <ul> <li>Added "2.2-µF, 16-V" for VCC pin bypass capacitor</li> </ul>                         |                                   |             |

| Change the Max Recommend Operating Condition for lout t                                       |                                   |             |

| Consolidating all the common EC table characteristic betwe                                    |                                   |             |

| Input Voltage, VIN_UVLO, I <sub>EN</sub> and Mnimum turn-on time                              |                                   |             |

| Changed Typical Value for VIN_UVLO Rising threshold typic                                     | cal from 3.6-V to 3.7-V and minir | mum Falling |

| threshold from 3-V to 2.9-V                                                                   |                                   | 7           |

| • Changed the operating from "4.5-V" to "4-V" in Device Fu                                    | Inctional Modes                   | 20          |

| • Changed from V <sub>OUT</sub> = 7 V to 36 V to V <sub>IN</sub> = 7 V to 36 V on $\boxtimes$ | ] 9-9                             |             |

| Changes from Revision B (April 2017) to Revision C (June                                      | 2017)                             | Page        |

| <ul> <li>「アプリケーション」の車載用バッテリ・レギュレーションを削除</li> </ul>                                            |                                   | 1           |

| • WSON パッケージおよびオプションを追加                                                                       |                                   | 1           |

| Added Device Comparison Table                                                                 |                                   |             |

| Change EN Abs Max to EN/SYNC Abs Max                                                          |                                   |             |

| Updating ESD Ratings to include HSOIC and WSON                                                |                                   |             |

| Corrected Equation 17 denominator from "(Vour x Voo)" to '                                    | "(Vour + Voo)"                    | 23          |

٠

| С | hanges from Revision A (July 2016) to Revision B (April 2017) | Page |

|---|---------------------------------------------------------------|------|

| • | Changed spec from 6.0 to 6.2 for max under Current Limit      | 7    |

| • | Changed spec from 4.2 to 4.6 for max under Current Limit      | 7    |

| _ |                                                               |      |

| Changes from Revision * (December 2015) to Revision A (July 2016) | Page |

|-------------------------------------------------------------------|------|

|                                                                   |      |

| • | 開発中から量産データに変更、残るすべてのセクションを追加。1 |

|---|--------------------------------|

|   |                                |

3

## **5** Device Comparison Table

| PACKAGE                    | PART NUMBER   | FIXED 400 kHz | ADJUSTABLE<br>FREQUENCY<br>RESISTOR | POWER GOOD | FPWM |

|----------------------------|---------------|---------------|-------------------------------------|------------|------|

| HSOIC (8)                  | LMR23630ADDA  | yes           | no                                  | no         | no   |

|                            | LMR23630AFDDA | yes           | no                                  | no         | yes  |

|                            | LMR23630DRR   | no            | yes                                 | no         | no   |

| WSON (12) (Pin 6 is RT)    | LMR23630FDRR  | no            | yes                                 | no         | yes  |

| WSON (12) (Pin 6 is PGOOD) | LMR23630APDRR | yes           | no                                  | yes        | no   |

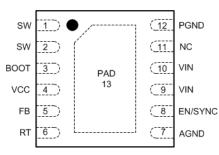

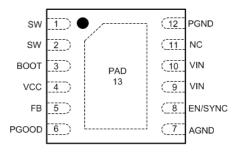

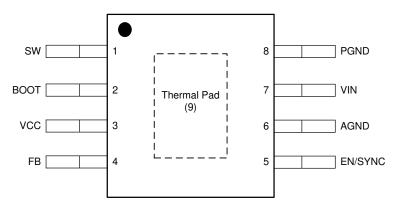

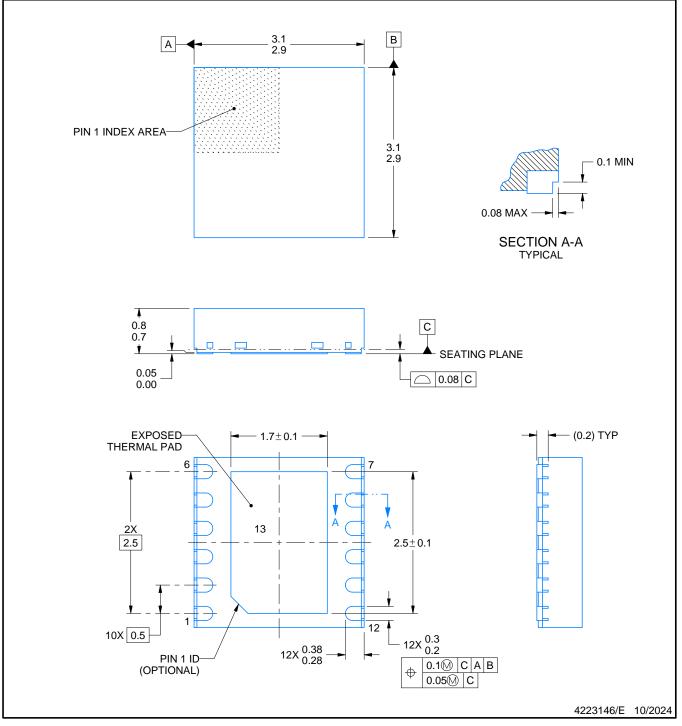

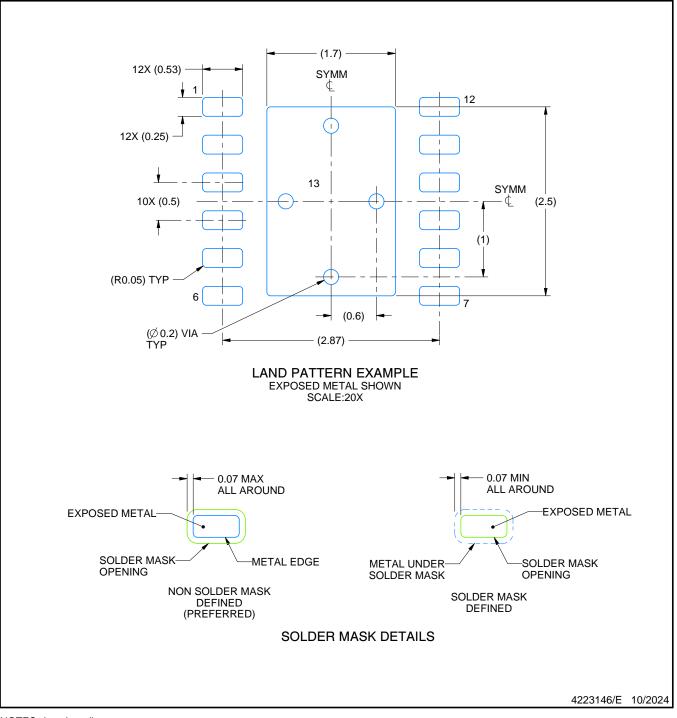

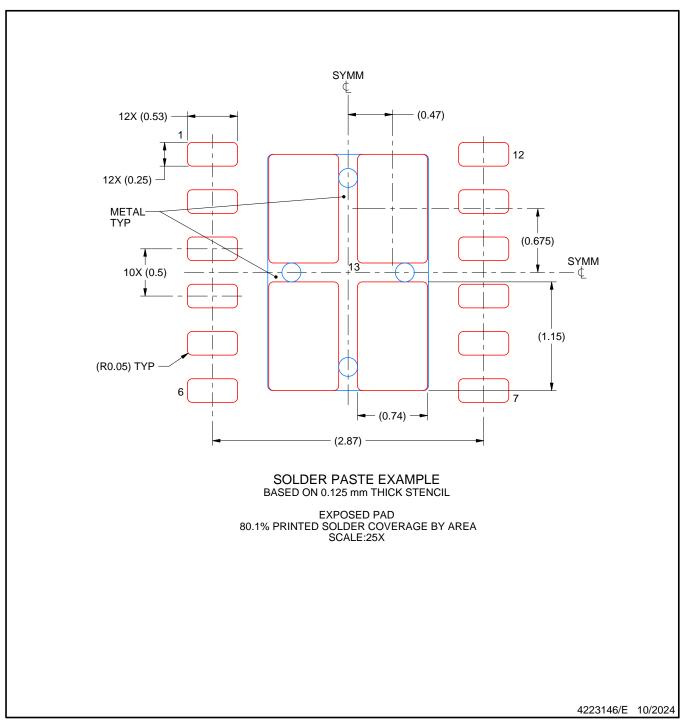

## **6** Pin Configuration and Functions

### 図 6-1. DRR Package 12-Pin WSON With RT and Thermal Pad Top View

## 図 6-2. DRR Package 12-Pin WSON With PGOOD and Thermal Pad Top View

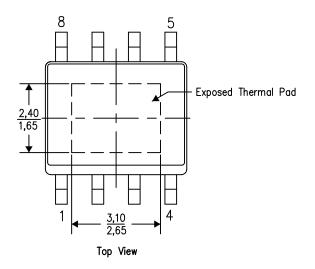

図 6-3. DDA Package 8-Pin HSOIC Top View

## **Pin Functions**

| PIN       |                 |                    |         | I/O (1) | DESCRIPTION                                                                                                                                                                                                                                                                                                                                               |  |

|-----------|-----------------|--------------------|---------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| HSOI<br>C | WSON With<br>RT | WSON With<br>PGOOD | NAME    |         |                                                                                                                                                                                                                                                                                                                                                           |  |

| 1         | 1, 2            | 1, 2               | SW      | Р       | Switching output of the regulator. Internally connected to both power MOSFETs. Connect to power inductor.                                                                                                                                                                                                                                                 |  |

| 2         | 3               | 3                  | BOOT    | Р       | Boot-strap capacitor connection for high-side driver. Connect a high quality 100nF or 470nF capacitor from BOOT to SW.                                                                                                                                                                                                                                    |  |

| 3         | 4               | 4                  | VCC     | Р       | Internal bias supply output for bypassing. Connect 2.2- $\mu$ F, 16-V bypass capacitor from this pin to AGND. Do not connect external loading to this pin. Never short this pin to ground during operation.                                                                                                                                               |  |

| 4         | 5               | 5                  | FB      | A       | Feedback input to regulator, connect the midpoint of feedback resistor divider to this pin.                                                                                                                                                                                                                                                               |  |

| N/A       | 6               | N/A                | RT      | A       | Connect a resistor RT from this pin to AGND to program switching frequency. Leave floating for 400-kHz default switching frequency.                                                                                                                                                                                                                       |  |

| N/A       | N/A             | 6                  | PGOOD   | A       | Open drain output for power-good flag. Use a $10-k\Omega$ to $100-k\Omega$ pullup resistor to logic rail or other DC voltage no higher than 12 V.                                                                                                                                                                                                         |  |

| 5         | 8               | 8                  | EN/SYNC | A       | Enable input to regulator. High = On, Low = Off. Can be connected to VIN. Do not float. Adjust the input undervoltage lockout with two resistors. The internal oscillator can be synchronized to an external clock by coupling a positive pulse into this pin through a small coupling capacitor. See $\frac{1}{2}/\sqrt{2}$ $\frac{3.4}{2}$ for details. |  |

| 6         | 7               | 7                  | AGND    | G       | Analog ground pin. Ground reference for internal references and logic.<br>Connect to system ground.                                                                                                                                                                                                                                                       |  |

| 7         | 9, 10           | 9, 10              | VIN     | Р       | Input supply voltage.                                                                                                                                                                                                                                                                                                                                     |  |

| 8         | 12              | 12                 | PGND    | G       | Power ground pin, connected internally to the low side power FET. Connect to system ground, PAD, AGND, ground pins of $C_{IN}$ and $C_{OUT}$ . Path to $C_{IN}$ must be as short as possible.                                                                                                                                                             |  |

| 9         | 13              | 13                 | PAD     | G       | Low impedance connection to AGND. Connect to PGND on PCB. Major<br>heat dissipation path of the die. Must be used for heat sinking to ground<br>plane on PCB.                                                                                                                                                                                             |  |

| N/A       | 11              | 11                 | NC      | N/A     | Not for use. Leave this pin floating.                                                                                                                                                                                                                                                                                                                     |  |

(1) A = Analog, P = Power, G = Ground.

## 7 Specifications

## 7.1 Absolute Maximum Ratings

Over the recommended operating junction temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C (unless otherwise noted)<sup>(1)</sup>

| PARAMETER                            |                                       | MIN  | MAX                   | UNIT |  |

|--------------------------------------|---------------------------------------|------|-----------------------|------|--|

|                                      | VIN to PGND                           | -0.3 | 42                    |      |  |

|                                      | EN/SYNC to AGND                       | -5.5 | V <sub>IN</sub> + 0.3 |      |  |

| Input voltages                       | FB to AGND                            | -0.3 | 4.5                   | v    |  |

| Input voltages                       | RT to AGND                            | -0.3 | 4.5                   | v    |  |

|                                      | PGOOD to AGND                         | -0.3 | 15                    |      |  |

|                                      | AGND to PGND                          | -0.3 | 0.3                   |      |  |

|                                      | SW to PGND                            | -1   | V <sub>IN</sub> + 0.3 | - V  |  |

| Output valtages                      | SW to PGND less than 10 ns transients | -5   | 42                    |      |  |

| Output voltages                      | BOOT to SW                            | -0.3 | 5.5                   |      |  |

|                                      | VCC to AGND                           | -0.3 | 4.5 <sup>(2)</sup>    |      |  |

| TJ                                   | J Junction temperature                |      | 150                   | °C   |  |

| T <sub>stg</sub> Storage temperature |                                       | -65  | 150                   | °C   |  |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) In shutdown mode, the VCC to AGND maximum value is 5.25 V.

## 7.2 ESD Ratings

|                    |                         |                                                                  | VALUE | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM) for HSOIC <sup>(1)</sup>                  |       |      |

|                    |                         | Human-body model (HBM) for WSON with RT and PGOOD <sup>(1)</sup> | ±2500 | v    |

|                    |                         | Charged-device model (CDM) for HSOIC and WSON RT <sup>(2)</sup>  | ±1000 |      |

|                    |                         | Charged-device model (CDM) for WSON PGOOD <sup>(2)</sup>         | ±750  |      |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

Over the recommended operating junction temperature range of -40°C to +125°C (unless otherwise noted) <sup>(1)</sup>

|                |                                       | MIN  | MAX | UNIT |

|----------------|---------------------------------------|------|-----|------|

|                | VIN                                   | 4    | 36  |      |

| Input voltage  | EN/SYNC                               | -5   | 36  | V    |

|                | FB                                    | -0.3 | 1.2 | v    |

|                | PGOOD                                 | -0.3 | 12  |      |

| Input current  | PGOOD pin current                     | 0    | 1   | mA   |

| Output voltage | V <sub>OUT</sub>                      | 1    | 28  | V    |

| Output current | I <sub>OUT</sub>                      | 0    | 3   | A    |

| Temperature    | Operating junction temperature, $T_J$ | -40  | 125 | °C   |

(1) Operating Ratings indicate conditions for which the device is intended to be functional, but do not ensure specific performance limits. For ensured specifications, see セクション 7.5.

## 7.4 Thermal Information

|                       | THERMAL METRIC <sup>(1)</sup> <sup>(2)</sup> | DDA (8 PINS) | DRR (12 PINS) | UNIT |

|-----------------------|----------------------------------------------|--------------|---------------|------|

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 42.0         | 41.5          | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 5.9          | 0.3           | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 23.4         | 16.5          | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 45.8         | 39.1          | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 3.6          | 3.4           | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 23.4         | 16.3          | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

(2) Determine power rating at a specific ambient temperature  $T_A$  with a maximum junction temperature  $(T_J)$  of 125°C (see t/2s/7.3).

## 7.5 Electrical Characteristics

Limits apply over the recommended operating junction temperature (T<sub>J</sub>) range of  $-40^{\circ}$ C to  $+125^{\circ}$ C, unless otherwise stated. Minimum and maximum limits are specified through test, design or statistical correlation. Typical values represent the most likely parametric norm at T<sub>J</sub> = 25 °C, and are provided for reference purposes only.

|                     | PARAMETER                                       | TEST CONDITIONS                                                                              | MIN   | TYP  | MAX   | UNIT          |

|---------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------|-------|------|-------|---------------|

| POWER SUF           | PPLY (VIN PIN)                                  | · · ·                                                                                        |       |      |       |               |

| V <sub>IN</sub>     | Operation input voltage                         |                                                                                              | 4     |      | 36    | V             |

| VIN_UVLO            | Undervoltage lockout thresholds                 | Rising threshold                                                                             | 3.3   | 3.7  | 3.9   | V             |

|                     |                                                 | Falling threshold                                                                            | 2.9   | 3.3  | 3.5   | v             |

| I <sub>SHDN</sub>   | Shutdown supply current                         | $V_{EN} = 0 V, V_{IN} = 12 V, T_{J} = -40^{\circ}C \text{ to } 125^{\circ}C$                 |       | 2    | 4     | μA            |

| l <sub>Q</sub>      | Operating quiescent current (non-<br>switching) | V <sub>IN</sub> =12 V, V <sub>FB</sub> = 1.1 V, T <sub>J</sub> = -40°C to<br>125°C, PFM mode |       | 75   |       | μA            |

| ENABLE (EN          | I/SYNC PIN)                                     |                                                                                              |       |      |       |               |

| V <sub>EN_H</sub>   | Enable rising threshold voltage                 |                                                                                              | 1.4   | 1.55 | 1.7   | V             |

| V <sub>EN_HYS</sub> | Enable hysteresis voltage                       |                                                                                              |       | 0.4  |       | V             |

| V <sub>WAKE</sub>   | Wake-up threshold                               |                                                                                              | 0.4   |      |       | V             |

| _                   |                                                 | $V_{IN}$ = 4 V to 36 V, $V_{EN}$ = 2 V                                                       |       | 10   | 100   | nA<br>nA      |

| I <sub>EN</sub>     | Input leakage current at EN pin                 | V <sub>IN</sub> = 4 V to 36 V, V <sub>EN</sub> = 36 V                                        |       |      | 1     | μA<br>μA      |

| VOLTAGE RI          | EFERENCE (FB PIN)                               |                                                                                              |       |      |       | <b>h</b> ., , |

| \ <i>\</i>          | Deference velkere                               | $V_{IN}$ = 4.0 V to 36 V, $T_J$ = 25 °C                                                      | 0.985 | 1    | 1.015 | V             |

| V <sub>REF</sub>    | Reference voltage                               | $V_{IN}$ = 4.0 V to 36 V, T <sub>J</sub> = -40°C to 125°C                                    | 0.98  | 1    | 1.02  | V             |

| I <sub>LKG_FB</sub> | Input leakage current at FB pin                 | V <sub>FB</sub> = 1 V                                                                        |       | 10   |       | nA            |

Limits apply over the recommended operating junction temperature (T<sub>J</sub>) range of  $-40^{\circ}$ C to  $+125^{\circ}$ C, unless otherwise stated. Minimum and maximum limits are specified through test, design or statistical correlation. Typical values represent the most likely parametric norm at T<sub>J</sub> = 25 °C, and are provided for reference purposes only.

|                        | PARAMETER                                         | TEST CONDITIONS                                                                | MIN  | TYP   | MAX   | UNIT  |

|------------------------|---------------------------------------------------|--------------------------------------------------------------------------------|------|-------|-------|-------|

| POWER GOO              | DD (PGOOD PIN)                                    |                                                                                | I    |       |       |       |

| V <sub>PG_OV</sub>     | Power-good flag overvoltage tripping threshold    | % of reference voltage                                                         | 104% | 107%  | 110%  |       |

| V <sub>PG_UV</sub>     | Power-good flag undervoltage tripping threshold   | % of reference voltage                                                         | 92%  | 94%   | 96.5% |       |

| V <sub>PG_HY</sub> s   | Power-good flag recovery<br>hysteresis            | % of reference voltage                                                         |      | 1.5%  |       |       |

| V <sub>IN_PG_MIN</sub> | Minimum V <sub>IN</sub> for valid PGOOD<br>output | 50 $\mu$ A pullup to PGOOD pin, V <sub>EN</sub> = 0 V, T <sub>J</sub> = 25°C   |      |       | 1.5   | V     |

|                        |                                                   | 50 $\mu$ A pullup to PGOOD pin, V <sub>IN</sub> = 1.5 V, V <sub>EN</sub> = 0 V |      |       | 0.4   | V     |

| V <sub>PG_LOW</sub>    | PGOOD low level output voltage                    | 0.5 mA pullup to PGOOD pin, V <sub>IN</sub> = 13.5 V, V <sub>EN</sub> = 0 V    |      |       | 0.4   | V     |

| INTERNAL LI            | DO (VCC PIN)                                      | · · ·                                                                          |      |       |       |       |

| V <sub>CC</sub>        | Internal LDO output voltage                       |                                                                                |      | 4.1   |       | V     |

| VCC UVLO               | VCC undervoltage lockout                          | Rising threshold                                                               | 2.8  | 3.2   | 3.6   | V     |

|                        | thresholds                                        | Falling threshold                                                              | 2.4  | 2.8   | 3.2   | v     |

| CURRENT LI             | МІТ                                               | · · ·                                                                          |      |       |       |       |

| l                      | S LIMIT Peak inductor current limit               | HSOIC package                                                                  | 3.8  | 5     | 6.2   | А     |

| I <sub>HS_LIMIT</sub>  |                                                   | WSON package                                                                   | 4    | 5.5   | 6.6   | ~     |

|                        | Valley inductor current limit                     | HSOIC package                                                                  | 2.9  | 3.6   | 4.6   | А     |

| I <sub>LS_LIMIT</sub>  |                                                   | WSON package                                                                   | 2.9  | 3.6   | 4.2   | ~     |

| I <sub>L_ZC</sub>      | Zero cross current limit                          | HSOIC and WSON package                                                         |      | -0.04 |       | А     |

| I <sub>L_NEG</sub>     | Negative current limit (FPWM option)              | SOIC and WSON package                                                          | -2.7 | -2    | -1.3  | A     |

| INTEGRATED             | MOSFETS                                           |                                                                                |      |       |       |       |

| P                      | High-side MOSFET ON-resistance                    | SOIC package, V <sub>IN</sub> = 12 V, I <sub>OUT</sub> = 1 A                   |      | 185   |       | mΩ    |

| R <sub>DS_ON_HS</sub>  |                                                   | WSON package, V <sub>IN</sub> = 12 V, I <sub>OUT</sub> = 1 A                   |      | 160   |       | 11152 |

| R-a au ia              | Low-side MOSFET ON-resistance                     | SOIC package, V <sub>IN</sub> = 12 V, I <sub>OUT</sub> = 1 A                   |      | 105   |       | mΩ    |

| R <sub>DS_ON_LS</sub>  |                                                   | WSON package, V <sub>IN</sub> = 12 V, I <sub>OUT</sub> = 1 A                   |      | 95    |       | 11152 |

| THERMAL SH             | HUTDOWN                                           |                                                                                |      |       |       |       |

| T <sub>SHDN</sub>      | Thermal shutdown threshold                        |                                                                                | 162  | 170   | 178   | °C    |

| T <sub>HYS</sub>       | Hysteresis                                        |                                                                                |      | 15    |       | °C    |

## 7.6 Timing Requirements

Over the recommended operating junction temperature range of -40°C to +125°C (unless otherwise noted)

|                                         |                                                                        |                                                                          | MIN | NOM | MAX | UNIT   |

|-----------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------|-----|-----|-----|--------|

| HICCUP MOI                              | DE                                                                     |                                                                          | ·   |     |     |        |

| N <sub>OC</sub> <sup>(1)</sup>          | Number of cycles that LS current limit is tripped to enter hiccup mode |                                                                          |     | 64  |     | Cycles |

| т                                       | Hissup rathy dolay time                                                | SOIC package                                                             |     | 5   |     | ms     |

| T <sub>OC</sub> Hiccup retry delay time |                                                                        | WSON package                                                             |     | 10  |     | 1115   |

| SOFT START                              | r                                                                      |                                                                          |     |     |     |        |

| <b>T</b>                                | lutere el e eft etert time e                                           | SOIC package, the time of internal reference to increase from 0 V to 1 V |     | 2   |     | ms     |

| T <sub>SS</sub>                         | Internal soft-start time                                               | WSON package, the time of internal reference to increase from 0 V to 1 V |     | 6   |     | ms     |

| POWER GOO                               | סס                                                                     | L                                                                        |     |     |     |        |

| T <sub>PGOOD_RISE</sub>                 | Power-good flag rising transition deglitch delay                       |                                                                          |     | 150 |     | μs     |

| T <sub>PGOOD_FALL</sub>                 | Power-good flag falling transition deglitch delay                      |                                                                          |     | 18  |     | μs     |

(1) Ensured by design.

## 7.7 Switching Characteristics

Over the recommended operating junction temperature range of -40°C to +125°C (unless otherwise noted)

|                                     | PARAMETE                                                 | R                                              | MIN  | TYP  | MAX  | UNIT |

|-------------------------------------|----------------------------------------------------------|------------------------------------------------|------|------|------|------|

| SW (SW PIN)                         |                                                          |                                                |      |      |      |      |

| T <sub>ON_MIN</sub>                 | Minimum turnon time                                      | WSON package                                   |      | 60   | 90   | ns   |

| T <sub>OFF_MIN</sub> <sup>(1)</sup> | Minimum turnoff time                                     |                                                |      | 100  |      | ns   |

| OSCILLATOR                          | (RT and EN/SYNC PIN)                                     |                                                |      |      |      |      |

| fsw_default                         | Oscillator default frequency                             | Fixed frequency version or RT pin open circuit | 340  | 400  | 460  | kHz  |

| £                                   | Minimum adjustable frequency                             | $R_T = 198 k\Omega$ with 1% accuracy           | 150  | 200  | 250  | kHz  |

| f <sub>ADJ</sub>                    | Maximum adjustable frequency                             | $R_T = 17.8 \text{ k}\Omega$ with 1% accuracy  | 1750 | 2150 | 2425 | kHz  |

| f <sub>SYNC</sub>                   | SYNC frequency range                                     |                                                | 200  |      | 2200 | kHz  |

| V <sub>SYNC</sub>                   | Amplitude of SYNC clock AC signal (measured at SYNC pin) |                                                | 2.8  |      | 5.5  | V    |

| T <sub>SYNC_MIN</sub>               | Minimum sync clock ON-time and OFF-time                  |                                                |      | 100  |      | ns   |

(1) Specified by design.

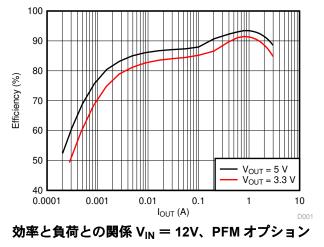

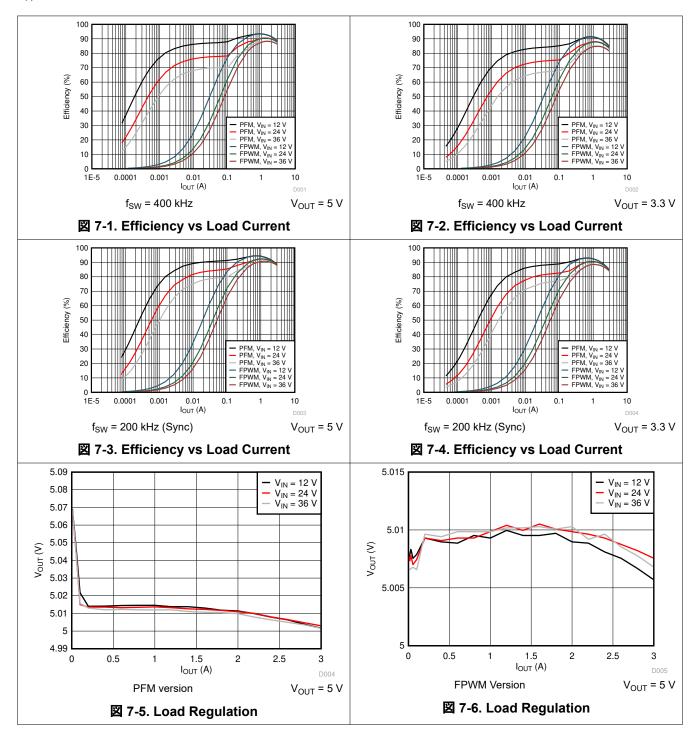

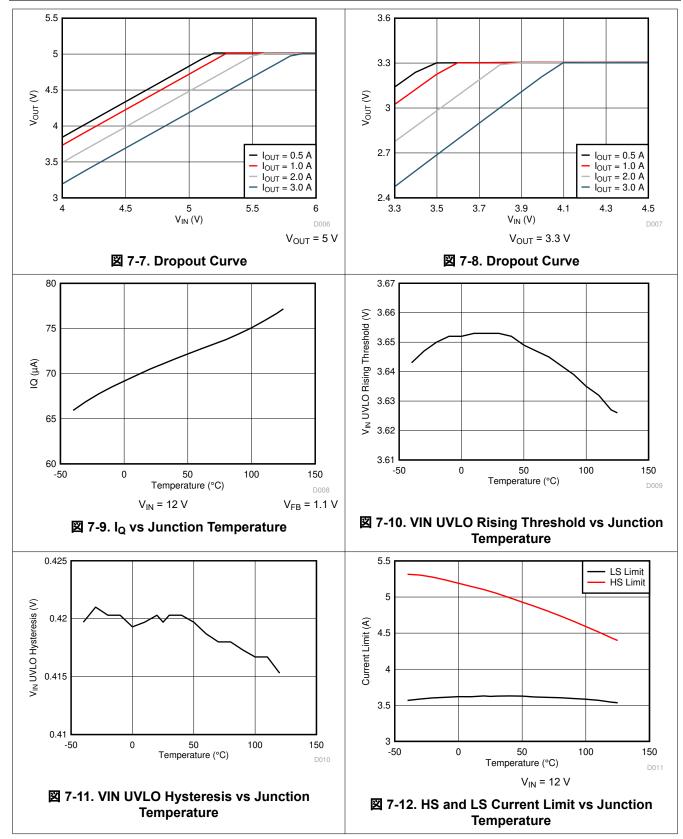

## 7.8 Typical Characteristics

Unless otherwise specified the following conditions apply:  $V_{IN}$  = 12 V,  $f_{SW}$  = 400 kHz, L = 8.2 µH,  $C_{OUT}$  = 150 µF,  $T_A$  = 25°C.

## 8 Detailed Description

### 8.1 Overview

The LMR23630 SIMPLE SWITCHER<sup>®</sup> regulator is an easy-to-use synchronous step-down DC-DC converter operating from 4-V to 36-V supply voltage. The device delivers up to 3-A DC load current with good thermal performance in a small solution size. For both the HSOIC and WSON packages, an extended family is available in multiple current options from 1 A to 3 A in pin-to-pin compatible packages.

The LMR23630 employs constant frequency peak-current-mode control. The device enters PFM mode at light load to achieve high efficiency. A user-selectable FPWM version is provided to achieve low output voltage ripple, tight output voltage regulation, and constant switching frequency. The switching frequency is 400 kHz for the fixed-frequency version. For the version which has RT pin, the switching frequency is adjustable from 200 kHz to 2.2 MHz. The device is internally compensated, which reduces design time and requires few external components. The LMR23630 is capable of synchronization to an external clock within the range of 200 kHz to 2.2 MHz.

Additional features such as precision enable, power-good flag, and internal soft-start provide a flexible and easyto-use solution for a wide range of applications. Protection features include thermal shutdown, VIN and VCC undervoltage lockout, cycle-by-cycle current limit, and hiccup-mode short-circuit protection.

The family requires very few external components and has a pinout designed for simple, optimum PCB layout.

## 8.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

### 8.3 Feature Description

#### 8.3.1 Fixed Frequency Peak Current Mode Control

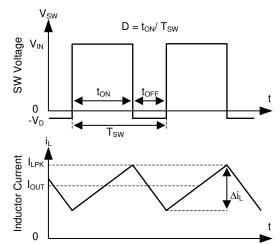

The following operating description of the LMR23630 refers to tripies 8.2 and to the waveforms in 🛛 8-1. The LMR23630 is a step-down synchronous buck regulator with integrated high-side (HS) and low-side (LS) switches (synchronous rectifier). The LMR23630 supplies a regulated output voltage by turning on the HS and LS NMOS switches with controlled duty cycle. During high-side switch ON-time, the SW pin voltage swings up to approximately  $V_{IN}$ , and the inductor current  $i_L$  increase with linear slope ( $V_{IN} - V_{OUT}$ ) / L. When the HS switch is turned off by the control logic, the LS switch is turned on after an anti-shoot-through dead time. Inductor current discharges through the LS switch with a slope of  $-V_{OUT}$  / L. The control parameter of a buck converter is defined as duty cycle D =  $t_{ON}$  /  $T_{SW}$ , where  $t_{ON}$  is the high-side switch ON-time and  $T_{SW}$  is the switching period. The regulator control loop maintains a constant output voltage by adjusting the duty cycle D. In an ideal buck converter, where losses are ignored, D is proportional to the output voltage and inversely proportional to the input voltage: D =  $V_{OUT}$  /  $V_{IN}$ .

**図** 8-1. SW Node and Inductor Current Waveforms in Continuous Conduction Mode (CCM)

The LMR23630 employs fixed-frequency peak-current-mode control. A voltage feedback loop is used to get accurate DC voltage regulation by adjusting the peak current command based on voltage offset. The peak inductor current is sensed from the high-side switch and compared to the peak current threshold to control the ON-time of the high-side switch. The voltage feedback loop is internally compensated, which allows for fewer external components, makes it easy to design, and provides stable operation with almost any combination of output capacitors. The regulator operates with fixed switching frequency at normal load condition. At light load condition, the LMR23630 operates in PFM mode to maintain high efficiency (PFM option) or in FPWM mode for low output-voltage ripple, tight output-voltage regulation, and constant switching frequency (FPWM option).

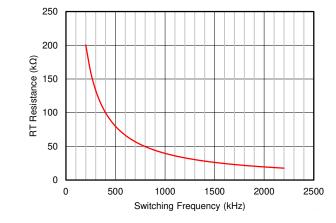

#### 8.3.2 Adjustable Frequency

The switching frequency can be programmed for the adjustable-switching-frequency version of LMR23630 by the impedance R<sub>T</sub> from the RT pin to ground. The frequency is inversely proportional to the R<sub>T</sub> resistance. The RT pin can be left floating and the LMR23630 operates at 400-kHz default switching frequency. The RT pin is not designed to be shorted to ground. For a desired frequency, typical R<sub>T</sub> resistance can be found by  $\vec{x}$  1. 8-1gives typical R<sub>T</sub> values for a given f<sub>SW</sub>.

$$R_{T}(k\Omega) = 40200 / f_{SW}(kHz) - 0.6$$

(1)

**1** 8-2. RT vs Frequency Curve

| f <sub>SW</sub> (kHz) | $R_{\rm T}$ (kΩ) |

|-----------------------|------------------|

| 200                   | 200              |

| 350                   | 115              |

| 500                   | 78.7             |

| 750                   | 53.6             |

| 1000                  | 39.2             |

| 1500                  | 26.1             |

| 2000                  | 19.6             |

| 2200                  | 17.8             |

#### 表 8-1. Typical Frequency Setting RT Resistance

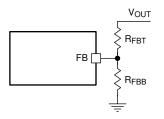

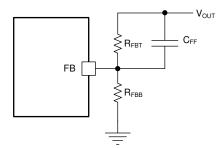

#### 8.3.3 Adjustable Output Voltage

A precision 1-V reference voltage is used to maintain a tightly regulated output voltage over the entire operating temperature range. The output voltage is set by a resistor divider from output voltage to the FB pin. TI recommends using 1% tolerance resistors with a low temperature coefficient for the FB divider. Select the lowside resistor RFBB for the desired divider current and use Equation 2 to calculate high-side R<sub>FBT</sub>. R<sub>FBT</sub> in the range from 10 k $\Omega$  to 100 k $\Omega$  is recommended for most applications. A lower RFBT value can be used if static loading is desired to reduce VOUT offset in PFM operation. Lower RFBT will reduce efficiency at very light load. Less static current goes through a larger RFBT and might be more desirable when light load efficiency is critical. However, RFBT larger than 1 M $\Omega$  is not recommended because it makes the feedback path more susceptible to noise. Larger RFBT value requires more carefully designed feedback path on the PCB. The tolerance and temperature variation of the resistor dividers affect the output voltage regulation.

図 8-3. Output Voltage Setting

$$R_{FBT} = \frac{V_{OUT} - V_{REF}}{V_{REF}} \times R_{FBB}$$

#### 8.3.4 Enable/Sync

The voltage on the EN/SYNC pin controls the ON or OFF operation of LMR23630. A voltage less than 1 V (typical) shuts down the device while a voltage higher than 1.6 V (typical) is required to start the regulator. The EN/SYNC pin is an input and cannot be left open or floating. The simplest way to enable the operation of the LMR23630 is to connect the EN to  $V_{IN}$ . This allows self-start-up of the LMR23630 when  $V_{IN}$  is within the operation range.

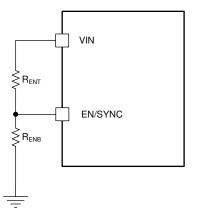

Many applications can benefit from the employment of an enable divider  $R_{ENT}$  and  $R_{ENB}$  ( $\boxtimes$  8-4) to establish a precision system UVLO level for the converter. System UVLO can be used for supplies operating from utility power as well as battery power. It can be used for sequencing, ensuring reliable operation, or supply protection, such as a battery discharge level. An external logic signal can also be used to drive EN input for system sequencing and protection.

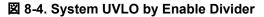

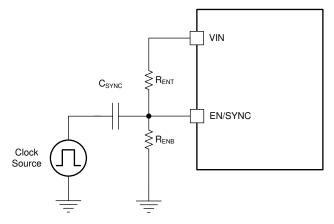

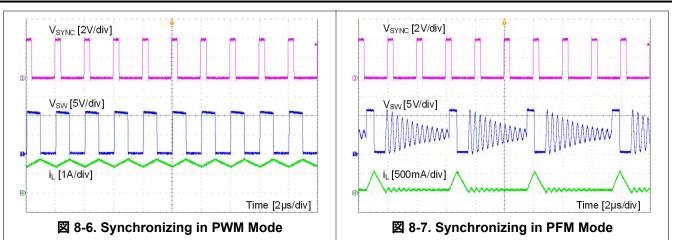

The EN pin also can be used to synchronize the internal oscillator to an external clock. The internal oscillator can be synchronized by AC-coupling a positive edge into the EN pin. The AC-coupled peak-to-peak voltage at the EN pin must exceed the SYNC amplitude threshold of 2.8 V (typical) to trip the internal synchronization pulse detector, and the minimum SYNC clock ON-time and OFF-time must be longer than 100 ns (typical). A 3.3-V or a higher amplitude pulse signal coupled through a 1-nF capacitor  $C_{SYNC}$  is a good starting point. Keeping  $R_{ENT}$  //  $R_{ENB}$  ( $R_{ENT}$  parallel with  $R_{ENB}$ ) in the 100 k $\Omega$  range is a good choice.  $R_{ENT}$  is required for this synchronization circuit, but  $R_{ENB}$  can be left unmounted if system UVLO is not needed. LMR23630 switching action can be synchronized to an external clock from 200 kHz to 2.2 MHz. 🛛 8-6 and  $\bigotimes$  8-7 show the device synchronized to an external system clock.

図 8-5. Synchronize to External Clock

#### 8.3.5 VCC, UVLO

The LMR23630 integrates an internal LDO to generate V<sub>CC</sub> for control circuitry and MOSFET drivers. The nominal voltage for V<sub>CC</sub> is 4.1 V. The VCC pin is the output of an LDO and must be properly bypassed. Place a high-quality ceramic capacitor with a value of 2.2  $\mu$ F to 10  $\mu$ F, 16 V or higher rated voltage as close as possible to VCC and grounded to the exposed PAD and ground pins. The VCC output pin must not be loaded, or shorted to ground during operation. Shorting VCC to ground during operation may cause damage to the LMR23630.

VCC undervoltage lockout (UVLO) prevents the LMR23630 from operating until the V<sub>CC</sub> voltage exceeds 3.3 V (typical). The VCC UVLO threshold has 400 mV (typical) of hysteresis to prevent undesired shutdown due to temporary  $V_{IN}$  drops.

#### 8.3.6 Minimum ON-time, Minimum OFF-time and Frequency Foldback at Dropout Conditions

Minimum ON-time,  $T_{ON\_MIN}$ , is the smallest duration of time that the HS switch can be on.  $T_{ON\_MIN}$  is typically 60 ns in the LMR23630. Minimum OFF-time,  $T_{OFF\_MIN}$ , is the smallest duration that the HS switch can be off.  $T_{OFF\_MIN}$  is typically 100 ns in the LMR23630. In CCM operation,  $T_{ON\_MIN}$  and  $T_{OFF\_MIN}$  limit the voltage conversion range given a selected switching frequency.

The minimum duty cycle allowed is:

$$D_{MIN} = T_{ON MIN} \times f_{SW}$$

(3)

And the maximum duty cycle allowed is:

$$D_{MAX} = 1 - T_{OFF MIN} \times f_{SW}$$

(4)

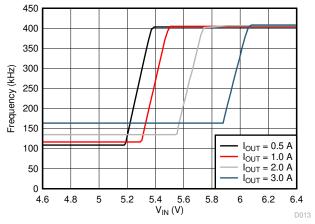

Given fixed  $T_{ON\_MIN}$  and  $T_{OFF\_MIN}$ , the higher the switching frequency the narrower the range of the allowed duty cycle. In the LMR23630, a frequency foldback scheme is employed to extend the maximum duty cycle when  $T_{OFF\_MIN}$  is reached. The switching frequency decreases once longer duty cycle is needed under low  $V_{IN}$  conditions. Wide range of frequency foldback allows the LMR23630 output voltage stay in regulation with a much lower supply voltage  $V_{IN}$ . This leads to a lower effective dropout voltage.

Given an output voltage, the choice of the switching frequency affects the allowed input voltage range, solution size and efficiency. The maximum operation supply voltage can be found by:

$$V_{IN\_MAX} = \frac{V_{OUT}}{\left(f_{SW} \times T_{ON\_MIN}\right)}$$

(5)

At lower supply voltage, the switching frequency decreases once  $T_{OFF\_MIN}$  is tripped. The minimum  $V_{IN}$  without frequency foldback can be approximated by:

FXAS

STRUMENTS

www.tij.co.jp

(6)

$$V_{\text{IN}_{\text{MIN}}} = \frac{V_{\text{OUT}}}{\left(1 - f_{\text{SW}} \times T_{\text{OFF}_{\text{MIN}}}\right)}$$

Taking considerations of power losses in the system with heavy load operation,  $V_{IN\_MAX}$  is higher than the result calculated in  $\neq 5$ . With frequency foldback,  $V_{IN\_MIN}$  is lowered by decreased  $f_{SW}$ .

図 8-8. Frequency Foldback at Dropout (V<sub>OUT</sub> = 5 V, f<sub>SW</sub> = 400 kHz)

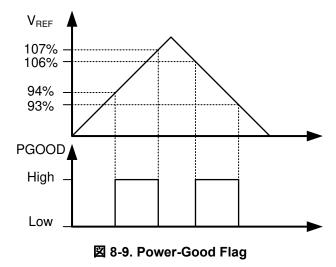

### 8.3.7 Power Good (PGOOD)

The power-good version of LMR23630 has a built in power-good flag shown on PGOOD pin to indicate whether the output voltage is within its regulation level. The PGOOD signal can be used for start-up sequencing of multiple rails or fault protection. The PGOOD pin is an open-drain output that requires a pullup resistor to an appropriate DC voltage. Voltage detected by the PGOOD pin must never exceed 15 V, and limit the maximum current into this pin to 1 mA. A typical range of pullup resistor value is 10 k $\Omega$  to 100 k $\Omega$ .

When the FB voltage is within the power-good band, +6% above and -6% below the internal reference voltage  $V_{REF}$  typically, the PGOOD switch is turned off, and the PGOOD voltage is as high as the pulled-up voltage. When the FB voltage is outside of the tolerance band, +7% above or -7% below  $V_{REF}$  typically, the PGOOD switch is turned on, and the PGOOD pin voltage is pulled low to indicate power bad. A glitch filter prevents false flag operation for short excursions in the output voltage, such as during line and load transients. The values for the various filter and delay times can be found in  $\frac{1}{2}\sqrt{2}\sqrt{2}\sqrt{7.6}$ . Power-good operation can best be understood by reference to  $\boxed{8}$  8-9.

#### 8.3.8 Internal Compensation and C<sub>FF</sub>

The LMR23630 is internally compensated as shown in 272328.2. The internal compensation is designed so that the loop response is stable over the entire operating frequency and output voltage range. Depending on the output voltage, the compensation loop phase margin can be low with all ceramic capacitors. TI recommends an external feed-forward capacitor C<sub>FF</sub> be placed in parallel with the top resistor divider R<sub>FBT</sub> for optimum transient performance.

#### **図** 8-10. Feed-forward Capacitor for Loop Compensation

The feed-forward capacitor  $C_{FF}$  in parallel with  $R_{FBT}$  places an additional zero before the crossover frequency of the control loop to boost phase margin. The zero frequency can be found by:

$$f_{Z_{CFF}} = \frac{1}{\left(2\pi \times C_{FF} \times R_{FBT}\right)}$$

(7)

An additional pole is also introduced with C<sub>FF</sub> at the frequency of:

$$f_{P_{CFF}} = \frac{1}{\left(2\pi \times C_{FF} \times R_{FBT} / / R_{FBB}\right)}$$

(8)

The zero  $f_{Z\_CFF}$  adds phase boost at the crossover frequency and improves transient response. The pole  $f_{P-CFF}$  helps maintaining proper gain margin at frequency beyond the crossover.  $\pm 9-1$  lists the combination of  $C_{OUT}$ ,  $C_{FF}$  and  $R_{FBT}$  for typical applications, designs with similar  $C_{OUT}$  but  $R_{FBT}$  other than recommended value, adjust  $C_{FF}$  such that ( $C_{FF} \times R_{FBT}$ ) is unchanged and adjust  $R_{FBB}$  such that ( $R_{FBT} / R_{FBB}$ ) is unchanged.

Designs with different combinations of output capacitors need different  $C_{FF}$ . Different types of capacitors have different equivalent series resistance (ESR). Ceramic capacitors have the smallest ESR and need the most CFF. Electrolytic capacitors have much larger ESR than ceramic, and the ESR zero frequency location would be low enough to boost the phase up around the crossover frequency. Designs that use mostly electrolytic capacitors at the output may not need any CFF. The location of this ESR zero frequency can be calculated with Equation 9:

$$f_{Z\_ESR} = \frac{1}{(2\pi \times C_{OUT} \times ESR)}$$

(9)

The  $C_{FF}$  creates a time constant with  $R_{FBT}$  that couples in the attenuate output voltage ripple to the FB node. If the  $C_{FF}$  value is too large, it can couple too much ripple to the FB and affect  $V_{OUT}$  regulation. Therefore, calculate  $C_{FF}$  based on output capacitors used in the system. At cold temperatures, the value of  $C_{FF}$  might change based on the tolerance of the chosen component. This may reduce its impedance and ease noise coupling on the FB node. To avoid this, more capacitance can be added to the output or the value of  $C_{FF}$  can be reduced.

#### 8.3.9 Bootstrap Voltage (BOOT)

The LMR23630 provides an integrated bootstrap voltage regulator. A small capacitor between the BOOT and SW pins provides the gate drive voltage for the high-side MOSFET. The BOOT capacitor is refreshed when the high-side MOSFET is off and the low-side switch conducts. The recommended value of the BOOT capacitor is

0.1 µF to 0.47 µF. TI recommends a ceramic capacitor with an X7R or X5R grade dielectric with a voltage rating of 16 V or higherfor stable performance over temperature and voltage.

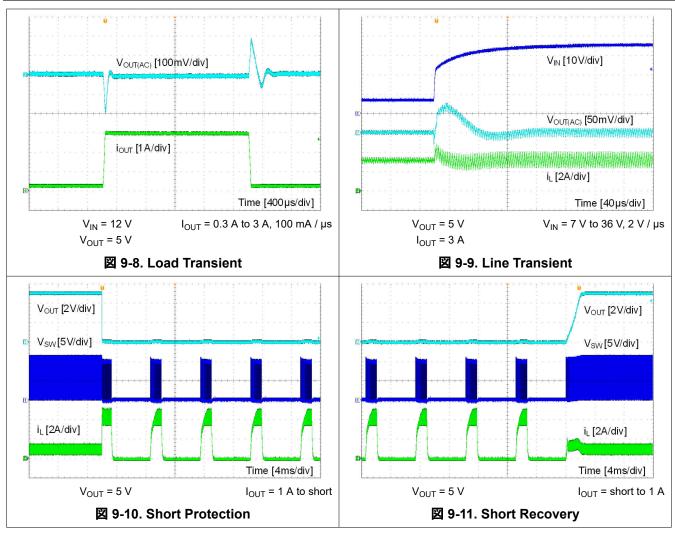

#### 8.3.10 Overcurrent and Short-Circuit Protection

The LMR23630 is protected from over-current conditions by cycle-by-cycle current limit on both the peak and valley of the inductor current. Hiccup mode will be activated if a fault condition persists to prevent over-heating.

High-side MOSFET overcurrent protection is implemented by the nature of the peak-current-mode control. The HS switch current is sensed when the HS is turned on after a set blanking time. The HS switch current is compared to the output of the error amplifier (EA) minus slope compensation every switching cycle. See the  $\frac{1}{2}$   $\frac{1}{2}$  8.2 for more details. The peak current of HS switch is limited by a clamped maximum peak current threshold I<sub>HS\_LIMIT</sub> which is constant. Thus, the peak current limit of the high-side switch is not affected by the slope compensation and remains constant over the full duty cycle range.

The current going through LS MOSFET is also sensed and monitored. When the LS switch turns on, the inductor current begins to ramp down. The LS switch is not turned OFF at the end of a switching cycle if its current is above the LS current limit  $I_{LS\_LIMIT}$ . The LS switch is kept ON so that inductor current keeps ramping down, until the inductor current ramps below the LS current limit  $I_{LS\_LIMIT}$ . The LS switch is somewhat different than the more typical peak current limit and results in Equation 10 for the maximum load current.

$$I_{OUT\_MAX} = I_{LS\_LIMIT} + \frac{(V_{IN} - V_{OUT})}{2 \times f_{SW} \times L} \times \frac{V_{OUT}}{V_{IN}}$$

(10)

If the current of the LS switch is higher than the LS current limit for 64 consecutive cycles, hiccup current protection mode is activated. In hiccup mode, the regulator is shut down and kept off for 5 ms typically before the LMR23630 tries to start again. If overcurrent or short-circuit fault condition still exist, hiccup will repeat until the fault condition is removed. Hiccup mode reduces power dissipation under severe overcurrent conditions, prevents over-heating and potential damage to the device.

For FPWM version, the inductor current is allowed to go negative. If this current exceed  $I_{L_NEG}$ , the LS switch is turned off until the next clock cycle. This is used to protect the LS switch from excessive negative current.

#### 8.3.11 Thermal Shutdown

The LMR23630 provides an internal thermal shutdown to protect the device when the junction temperature exceeds 170°C (typical). The device is turned off when thermal shutdown activates. Once the die temperature falls below 155°C (typical), the device reinitiates the power-up sequence controlled by the internal soft-start circuitry.

### 8.4 Device Functional Modes

#### 8.4.1 Shutdown Mode

The EN pin provides electrical ON and OFF control for the LMR23630. When  $V_{EN}$  is below 1 V (typical), the device is in shutdown mode. The LMR23630 also employs VIN and VCC UVLO protection. If  $V_{IN}$  or  $V_{CC}$  voltage is below their respective UVLO level, the regulator is turned off.

#### 8.4.2 Active Mode

The LMR23630 is in active mode when  $V_{EN}$  is above the precision enable threshold,  $V_{IN}$  and  $V_{CC}$  are above their respective UVLO level. The simplest way to enable the LMR23630 is to connect the EN pin to VIN pin. This allows self startup when the input voltage is in the operating range 4 V to 36 V. See  $t/2y_{2} \times 8.3.5$  and  $t/2y_{2} \times 8.3.4$  for details on setting these operating levels.

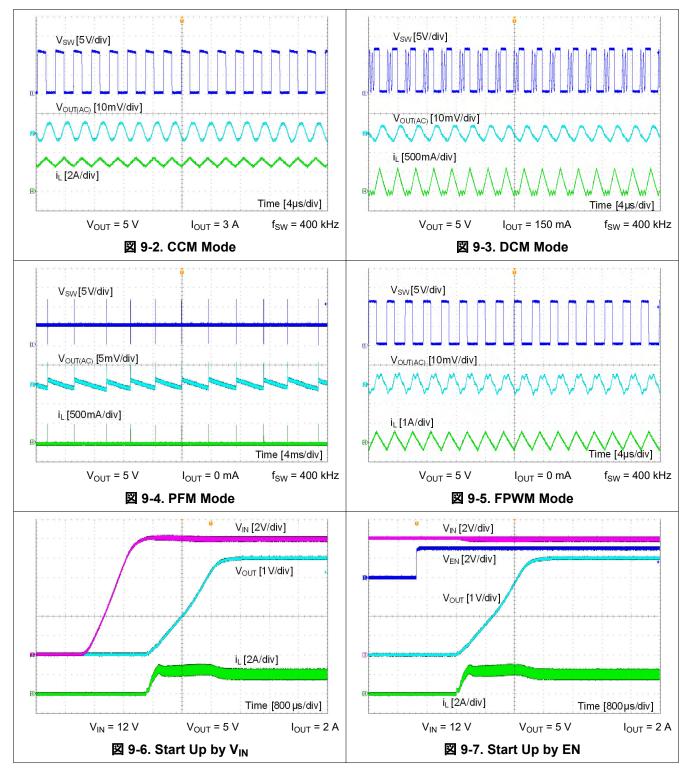

In active mode, depending on the load current, the LMR23630 is in one of four modes:

- 1. Continuous conduction mode (CCM) with fixed switching frequency when load current is above half of the peak-to-peak inductor current ripple (for both PFM and FPWM options).

- 2. Discontinuous conduction mode (DCM) with fixed switching frequency when load current is lower than half of the peak-to-peak inductor current ripple in CCM operation (only for PFM option).

- 3. Pulse frequency modulation mode (PFM) when switching frequency is decreased at very light load (only for PFM option).

- 4. Forced pulse width modulation mode (FPWM) with fixed switching frequency even at light load (only for FPWM option).

#### 8.4.3 CCM Mode

CCM operation is employed in the LMR23630 when the load current is higher than half of the peak-to-peak inductor current. In CCM operation, the frequency of operation is fixed, output voltage ripple is at a minimum in this mode, and the maximum output current of 3 A can be supplied by the LMR23630.

#### 8.4.4 Light Load Operation (PFM Version)

For PFM version, when the load current is lower than half of the peak-to-peak inductor current in CCM, the LMR23630 operates in DCM, also known as diode emulation mode (DEM). In DCM, the LS switch is turned off when the inductor current drops to  $I_{L_{ZC}}$  (-40 mA typical). Both switching losses and conduction losses are reduced in DCM, compared to forced PWM operation at light load.

At even lighter current loads, PFM is activated to maintain high efficiency operation. When either the minimum HS switch ON-time ( $t_{ON\_MIN}$ ) or the minimum peak inductor current  $I_{PEAK\_MIN}$  (300 mA typ) is reached, the switching frequency decreases to maintain regulation. In PFM, switching frequency is decreased by the control loop when load current reduces to maintain output voltage regulation. Switching loss is further reduced in PFM operation due to less frequent switching actions. The external clock synchronizing is not valid when the LMR23630 device enters into PFM mode.

#### 8.4.5 Light Load Operation (FPWM Version)

For FPWM version, LMR23630 is locked in PWM mode at full load range. This operation is maintained, even at no-load, by allowing the inductor current to reverse its normal direction. This mode trades off reduced light load efficiency for low output voltage ripple, tight output voltage regulation, and constant switching frequency. In this mode, a negative current limit of  $I_{L_NEG}$  is imposed to prevent damage to the regulators low side FET. When in FPWM mode the converter synchronizes to any valid clock signal on the EN/SYNC input.

## 9 Application and Implementation

#### Note

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 9.1 Application Information

The LMR23630 is a step-down DC-to-DC regulator. It is typically used to convert a higher DC voltage to a lower DC voltage with a maximum output current of 3 A. The following design procedure can be used to select components for the LMR23630. Alternately, the WEBENCH<sup>®</sup> software may be used to generate complete designs. When generating a design, the WEBENCH<sup>®</sup> software utilizes iterative design procedure and accesses comprehensive databases of components. See www.ti.com for more details.

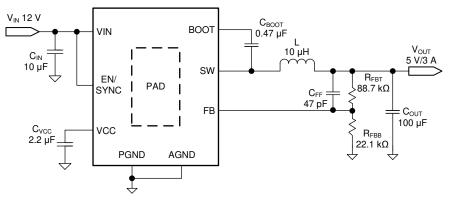

#### 9.2 Typical Applications

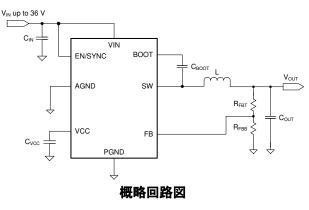

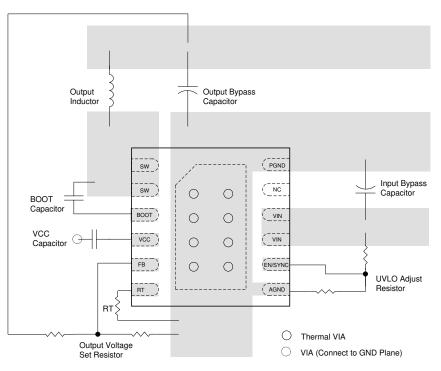

The LMR23630 only requires a few external components to convert from a wide voltage-range supply to a fixed output voltage.  $\boxtimes$  9-1 shows a basic schematic.

図 9-1. LM23630 Application Circuit

The external components must fulfill the needs of the application, but also the stability criteria of the device control loop.  $\frac{1}{2}$  9-1 can be used to simplify the output filter component selection.

Turnia al Malura a

| f <sub>SW</sub> (kHz) | V <sub>OUT</sub> (V) | L (μH) <sup>(2)</sup> | C <sub>OUT</sub> (μF) <sup>(3)</sup> | C <sub>FF</sub> (pF) | R <sub>FBT</sub> (kΩ) <sup>(4) (5)</sup> |

|-----------------------|----------------------|-----------------------|--------------------------------------|----------------------|------------------------------------------|

|                       | 3.3                  | 15                    | 300                                  | 150                  | 51                                       |

| 200                   | 5                    | 18                    | 200                                  | 100                  | 88.7                                     |

| 200                   | 12                   | 33                    | 100                                  | See <sup>(1)</sup>   | 243                                      |

|                       | 24                   | 33                    | 47                                   | See <sup>(1)</sup>   | 510                                      |

|                       | 3.3                  | 6.8                   | 150                                  | 75                   | 51                                       |

| 400                   | 5                    | 10                    | 100                                  | 47                   | 88.7                                     |

| 400                   | 12                   | 15                    | 68                                   | See <sup>(1)</sup>   | 243                                      |

|                       | 24                   | 15                    | 47                                   | See <sup>(1)</sup>   | 510                                      |

| 1000                  | 3.3                  | 3.3                   | 68                                   | 39                   | 51                                       |

| 1000                  | 5                    | 4.7                   | 47                                   | 25                   | 88.7                                     |

| 2200                  | 3.3                  | 2.2                   | 47                                   | 33                   | 51                                       |

| 2200                  | 5                    | 2.2                   | 33                                   | 18                   | 88.7                                     |

(1) High ESR  $C_{OUT}$  gives enough phase boost and  $C_{FF}$  not needed.

- (2) Inductance value is calculated based on  $V_{IN}$  = 36 V.

- (3) All the C<sub>OUT</sub> values are after derating. Add more when using ceramic capacitors.

- (4)  $R_{FBT} = 0 \Omega$  for  $V_{OUT} = 1 V$ .  $R_{FBB} = 22.1 k\Omega$  for all other  $V_{OUT}$  setting.

- (5) For designs with R<sub>FBT</sub> other than recommended value, please adjust C<sub>FF</sub> such that (C<sub>FF</sub> × R<sub>FBT</sub>) is unchanged and adjust R<sub>FBB</sub> such that (R<sub>FBT</sub> / R<sub>FBB</sub>) is unchanged.

#### 9.2.1 Design Requirements

Detailed design procedure is described based on a design example. For this design example, use the parameters listed in  $\frac{1}{5}$  9-2 as the input parameters.

| DESIGN PARAMETER                    | EXAMPLE VALUE                        |

|-------------------------------------|--------------------------------------|

| Input voltage, V <sub>IN</sub>      | 12 V typical, range from 8 V to 28 V |

| Output voltage, V <sub>OUT</sub>    | 5 V                                  |

| Maximum output current IO_MAX       | 3 A                                  |

| Transient response 0.2 A to 2.5 A   | 5%                                   |

| Output voltage ripple               | 50 mV                                |

| Input voltage ripple                | 400 mV                               |

| Switching frequency f <sub>SW</sub> | 400 kHz                              |

#### 表 9-2. Design Example Parameters

#### 9.2.2 Detailed Design Procedure

#### 9.2.2.1 Custom Design With WEBENCH® Tools

Click here to create a custom design using the LMR23625 device with the WEBENCH® Power Designer.

- 1. Start by entering the input voltage (V<sub>IN</sub>), output voltage (V<sub>OUT</sub>), and output current (I<sub>OUT</sub>) requirements.

- 2. Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

- 3. Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time pricing and component availability.

In most cases, these actions are available:

- · Run electrical simulations to see important waveforms and circuit performance

- Run thermal simulations to understand board thermal performance

- · Export customized schematic and layout into popular CAD formats

- Print PDF reports for the design, and share the design with colleagues

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

#### 9.2.2.2 Output Voltage Setpoint

The output voltage of LMR23630 is externally adjustable using a resistor divider network. The divider network is comprised of top feedback resistor  $R_{FBT}$  and bottom feedback resistor  $R_{FBB}$ . Equation 11 is used to determine the output voltage:

$$R_{FBT} = \frac{V_{OUT} - V_{REF}}{V_{REF}} \times R_{FBB}$$

(11)

Choose the value of  $R_{FBB}$  to be 22.1 k $\Omega$ . With the desired output voltage set to 5 V and the  $V_{REF}$  = 1 V, the  $R_{FBB}$  value can then be calculated using Equation 11. The formula yields to a value 88.7 k $\Omega$ .

#### 9.2.2.3 Switching Frequency

The default switching frequency of the LMR23630 is 400 kHz. For other switching frequency, the device must be synchronized to an external clock, see  $\frac{1}{2}\sqrt{3} \times 8.3.4$  for more details.

#### 9.2.2.4 Inductor Selection

The most critical parameters for the inductor are the inductance, saturation current, and the rated current. The inductance is based on the desired peak-to-peak ripple current  $\Delta i_L$ . Because the ripple current increases with the input voltage, the maximum input voltage is always used to calculate the minimum inductance  $L_{MIN}$ . Use Equation 12 to calculate the minimum value of the output inductor.  $K_{IND}$  is a coefficient that represents the amount of inductor ripple current relative to the maximum output current of the device. A reasonable value of  $K_{IND}$  should be 20% to 40%. During an instantaneous short or overcurrent operation event, the RMS and peak inductor current can be high. The inductor current rating should be higher than the current limit of the device.

$$\Delta i_{L} = \frac{V_{OUT} \times (V_{IN} MAX - V_{OUT})}{V_{IN} MAX \times L \times f_{SW}}$$

(12)

$$L_{MIN} = \frac{V_{IN}MAX - V_{OUT}}{I_{OUT} \times K_{IND}} \times \frac{V_{OUT}}{V_{IN}MAX \times f_{SW}}$$

(13)

In general, it is preferable to choose lower inductance in switching power supplies, because it usually corresponds to faster transient response, smaller DCR, and reduced size for more compact designs. However, inductance that is too low can generate an inductor current ripple that is too high so that overcurrent protection at the full load could be falsely triggered. It also generates more conduction loss and inductor core loss. Larger inductor current ripple also implies larger output voltage ripple with same output capacitors. With peak current mode control, TI does not recommend having an inductor current ripple that is too small. A larger peak-current ripple improves the comparator signal-to-noise ratio.

For this design example, choose  $K_{IND} = 0.4$ , the minimum inductor value is calculated to be 8.56  $\mu$ H. Choose the nearest standard 8.2  $\mu$ H ferrite inductor with a capability of 4-A RMS current and 6-A saturation current.

#### 9.2.2.5 Output Capacitor Selection

Choose the output capacitor(s), C<sub>OUT</sub>, with care because it directly affects the steady-state output-voltage ripple, loop stability, and the voltage over/undershoot during load-current transients.

The output ripple is essentially composed of two parts. One is caused by the inductor current ripple going through the equivalent series resistance (ESR) of the output capacitors:

$$\Delta V_{OUT\_ESR} = \Delta i_{L} \times ESR = K_{IND} \times I_{OUT} \times ESR$$

<sup>(14)</sup>

The other is caused by the inductor current ripple charging and discharging the output capacitors:

$$\Delta V_{OUT_{C}} = \frac{\Delta i_{L}}{(8 \times f_{SW} \times C_{OUT})} = \frac{K_{IND} \times I_{OUT}}{(8 \times f_{SW} \times C_{OUT})}$$

(15)

The two components in the voltage ripple are not in phase, so the actual peak-to-peak ripple is smaller than the sum of two peaks.

Output capacitance is usually limited by transient performance specifications if the system requires tight voltage regulation with presence of large current steps and fast slew rate. When a fast large load increase happens, output capacitors provide the required charge before the inductor current can slew up to the appropriate level. The control loop of the regulator usually needs four or more clock cycles to respond to the output voltage droop. The output capacitance must be large enough to supply the current difference for four clock cycles to maintain the output voltage within the specified range. Equation 17 shows the minimum output capacitance needed for specified output undershoot. When a sudden large load decrease happens, the output capacitors absorb energy stored in the inductor. which results in an output voltage overshoot. Equation 14 calculates the minimum capacitance required to keep the voltage overshoot within a specified range.

(16)

(17)

$$C_{OUT} > \frac{4 \times (I_{OH} - I_{OL})}{f_{SW} \times V_{US}}$$

$$C_{OUT} > \frac{I_{OH}^2 - I_{OL}^2}{\left(V_{OUT} + V_{OS}\right)^2 - V_{OUT}^2} \times L$$

where

- I<sub>OL</sub> = Low level output current during load transient

- I<sub>OH</sub> = High level output current during load transient

- V<sub>US</sub> = Target output voltage undershoot

- V<sub>OS</sub> = Target output voltage overshoot

For this design example, the target output ripple is 50 mV. Presuppose  $\Delta V_{OUT_ESR} = \Delta V_{OUT_C} = 50$  mV, and chose K<sub>IND</sub> = 0.4. Equation 16 yields ESR no larger than 41.7 m $\Omega$  and Equation 17 yields C<sub>OUT</sub> no smaller than 7.5 µF. For the target over/undershoot range of this design,  $V_{US} = V_{OS} = 5\% \times V_{OUT} = 250$  mV. The C<sub>OUT</sub> can be calculated to be no smaller than 108 µF and 28.5 µF by Equation 15 and Equation 17, respectively. Consider of derating, one 47-µF, 16-V and one 100-µF, 10-V ceramic capacitor with 5-m $\Omega$  ESR are used in parallel.

#### 9.2.2.6 Feed-Forward Capacitor

The LMR23630 is internally compensated. Depending on the V<sub>OUT</sub> and frequency  $f_{SW}$ , if the output capacitor C<sub>OUT</sub> is dominated by low-ESR (ceramic types) capacitors, it could result in low phase margin. To improve the phase boost an external feed-forward capacitor C<sub>FF</sub> can be added in parallel with R<sub>FBT</sub>. C<sub>FF</sub> is chosen such that phase margin is boosted at the crossover frequency without C<sub>FF</sub>. A simple estimation for the crossover frequency ( $f_X$ ) without C<sub>FF</sub> is shown in Equation 18, assuming C<sub>OUT</sub> has very small ESR, and C<sub>OUT</sub> value is after derating.

$$f_{X} = \frac{8.32}{V_{OUT} \times C_{OUT}}$$

(18)

Equation 19 for  $C_{FF}$  was tested:

$$C_{FF} = \frac{1}{4\pi \times f_X \times R_{FBT}}$$

(19)

For designs with higher ESR,  $C_{FF}$  is not needed when  $C_{OUT}$  has very high ESR and  $C_{FF}$  calculated from Equation 19 must reduced with medium ESR.  $\ge 9-1$  can be used as a quick starting point.

For the application in this design example, a 47-pF, 50-V, COG capacitor is selected.

#### 9.2.2.7 Input Capacitor Selection

The LMR23630 device requires high-frequency input decoupling capacitor(s) and a bulk input capacitor, depending on the application. The typical recommended value for the high-frequency decoupling capacitor is 4.7  $\mu$ F to 10  $\mu$ F. TI recommends a high-quality ceramic capacitor type X5R or X7R with sufficiency voltage rating. To compensate the derating of ceramic capacitors, a voltage rating twice the maximum input voltage is recommended. Additionally, some bulk capacitance can be required, especially if the LMR23630 circuit is not located within approximately 5 cm from the input voltage source. This capacitor is used to provide damping to the voltage spike due to the lead inductance of the cable or the trace. For this design, two 4.7- $\mu$ F, 50-V, X7R ceramic capacitors are used. A 0.1- $\mu$ F for high-frequency filtering and place it as close as possible to the device pins.

## 9.2.2.8 Bootstrap Capacitor Selection

Every LMR23630 design requires a bootstrap capacitor ( $C_{BOOT}$ ). TI recommends a capacitor of 0.47  $\mu$ F, ated 16 V or higher. The bootstrap capacitor is located between the SW pin and the BOOT pin. The bootstrap capacitor must be a high-quality ceramic type with an X7R or X5R grade dielectric for temperature stability.

#### 9.2.2.9 VCC Capacitor Selection

The VCC pin is the output of an internal LDO for LMR23630. To insure stability of the device, place a minimum of 2.2-µF, 16V, X7R capacitor from this pin to ground.

#### 9.2.2.10 Undervoltage Lockout Setpoint

The system undervoltage lockout (UVLO) is adjusted using the external voltage divider network of  $R_{ENT}$  and  $R_{ENB}$ . The UVLO has two thresholds, one for power up when the input voltage is rising and one for power down or brown outs when the input voltage is falling. The following equation can be used to determine the V<sub>IN</sub> UVLO level.

$$V_{\text{IN}_{\text{RISING}}} = V_{\text{ENH}} \times \frac{R_{\text{ENT}} + R_{\text{ENB}}}{R_{\text{ENB}}}$$

(20)

The EN rising threshold (V<sub>ENH</sub>) for LMR23630 is set to be 1.55 V (typical). Choose the value of R<sub>ENB</sub> to be 287 k $\Omega$  to minimize input current from the supply. If the desired V<sub>IN</sub> UVLO level is at 6 V, then the value of R<sub>ENT</sub> can be calculated using Equation 21:

$$R_{ENT} = \left(\frac{V_{IN}RISING}{V_{ENH}} - 1\right) \times R_{ENB}$$

(21)

Equation 21 yields a value of 820 k $\Omega$ . The resulting falling UVLO threshold, equals 4.4 V, can be calculated by Equation 22, where EN hysteresis (V<sub>EN HYS</sub>) is 0.4 V (typical).

$$V_{\text{IN}_{\text{FALLING}}} = \left(V_{\text{ENH}} - V_{\text{EN}_{\text{HYS}}}\right) \times \frac{R_{\text{ENT}} + R_{\text{ENB}}}{R_{\text{ENB}}}$$

(22)

### 9.2.3 Application Curves

Unless otherwise specified the following conditions apply:  $V_{IN}$  = 12 V,  $f_{SW}$  = 400 kHz, L = 8.2 µH,  $C_{OUT}$  = 150 µF,  $T_A$  = 25 °C.

## **10 Power Supply Recommendations**

The LMR23630 is designed to operate from an input voltage supply range between 4.5 V and 36 V for the HSOIC package and 4 V to 36 V for the WSON package. This input supply must be able to withstand the maximum input current and maintain a stable voltage. The resistance of the input supply rail must be low enough that an input current transient does not cause a high enough drop at the LMR23630 supply voltage that can cause a false UVLO fault triggering and system reset. If the input supply is located more than a few inches from the LMR23630, additional bulk capacitance may be required in addition to the ceramic input capacitors. The amount of bulk capacitance is not critical, but a 47-µF or 100-µF electrolytic capacitor is a typical choice.

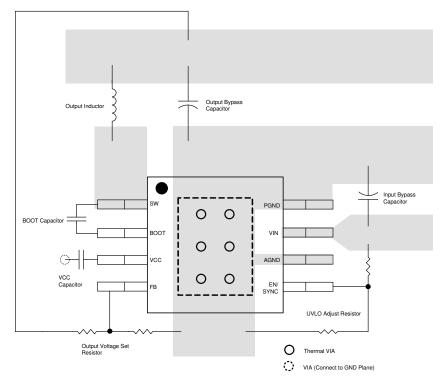

## 11 Layout

## **11.1 Layout Guidelines**

Layout is a critical portion of good power supply design. The following guidelines will help users design a PCB with the best power conversion performance, thermal performance, and minimized generation of unwanted EMI.

- The input bypass capacitor C<sub>IN</sub> must be placed as close as possible to the VIN and PGND pins. Grounding for both the input and output capacitors should consist of localized top side planes that connect to the PGND pin and PAD.

- 2. Place bypass capacitors for V<sub>CC</sub> close to the VCC pin and ground the bypass capacitor to device ground.

- Minimize trace length to the FB pin net. Both feedback resistors, R<sub>FBT</sub> and R<sub>FBB</sub> should be located close to the FB pin. Place C<sub>FF</sub> directly in parallel with R<sub>FBT</sub>. If V<sub>OUT</sub> accuracy at the load is important, make sure V<sub>OUT</sub> sense is made at the load. Route V<sub>OUT</sub> sense path away from noisy nodes and preferably through a layer on the other side of a shielded layer.