**DRV8213** JAJSOH4 - AUGUST 2023

# DRV8213 電流センス、電流レギュレーション、ストール検出機能を内蔵した 4A ブラシ付き DC モーター・ドライバ

# 1 特長

Texas

INSTRUMENTS

- N チャネル、H ブリッジ、ブラシ付き DC モーター・ドラ イバ

- 動作電源電圧範囲:1.65V~11V

- 240mΩ の R<sub>DS(on)</sub> (ハイサイド+ローサイド)

- 高い出力電流能力:4A (ピーク)

- PWM 制御インターフェイス、最大 100kHz のスイッチ ング

- 1.8V、3.3V、5Vのロジック入力電圧をサポート

- 電流センスおよび電流レギュレーション機能を内蔵

- アナログ電流センス出力 (IPROPI)

- ゲイン選択 (GAINSEL) 機能:

- 最小 10mA までの高精度電流センス

- さまざまな電流範囲に合わせて最適化された R<sub>DS(on)</sub> および過電流制限

- 設定可能な突入時間 (RTE パッケージのみ)

- 内蔵チャージ・ポンプ

- 低消費電力のスリープ・モードによる長いバッテリ寿命 - 60nA 未満の最大スリープ電流

- 小さいパッケージ占有面積

- 保護機能内蔵

- VM 低電圧誤動作防止 (UVLO)

- 自動リトライ過電流保護 (OCP)

- サーマル・シャットダウン (TSD)

- ストール検出 (RTE パッケージのみ)

# 2 アプリケーション

- ブラシ付き DC モーター、ソレノイド、リレー駆動

- 水道およびガス・メーター

- 電子スマート・ロック

- 電子 / ロボット玩具

- 輸液ポンプおよびその他のポータブル医療機器 •

- 電動歯ブラシ

- 美容と化粧

- 携帯プリンタ

- POS (販売時点情報管理) デバイス

- その他のバッテリ駆動 DC モーター・アプリケーション

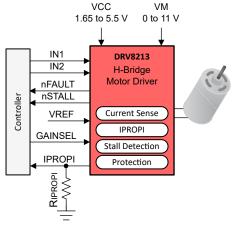

# 3 概要

DRV8213 は、N チャネル H ブリッジ、チャージ・ポンプ、 電流センス出力、電流レギュレーション、保護回路を備え た統合型モーター・ドライバです。3段のチャージ・ポンプ により、最低 1.65V で動作し、1.8V の電源レールとバッテ リの低電圧に対応できます。チャージ・ポンプにはすべて のコンデンサが内蔵されており、100%のデューティ・サイ クル動作が可能です。

内部カレント・ミラーは、電流センスとレギュレーションを実 装しています。そのため、大電力シャント抵抗を使う必要 がなく、基板面積を節約しシステム・コストを低減できま す。IPROPI 電流センス出力を使うと、マイコンはモーター のストールまたは負荷条件の変化を検出できます。ゲイン 選択 (GAINSEL) 機能により、平均モーター電流 10mA までの高精度の電流センスが可能です。 VREF ピンを使う ことで、起動および高負荷イベント中もマイコンを使わずに モーター電流をレギュレーションできます。 RTE パッケー ジは、センサレス・モーター・ストール検出とマイコンへのレ ポートをサポートしています。

低消費電力スリープ・モードは、内部回路の多くをシャット ダウンすることで非常に小さい静止電流を実現します。低 電圧誤動作防止、過電流、過熱に対する内部保護機能を 備えています。

#### 制品情報(1)

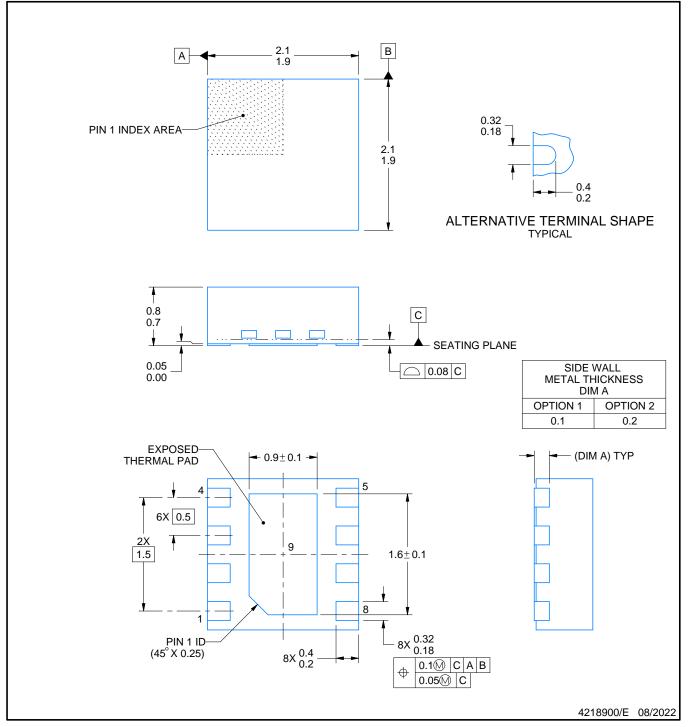

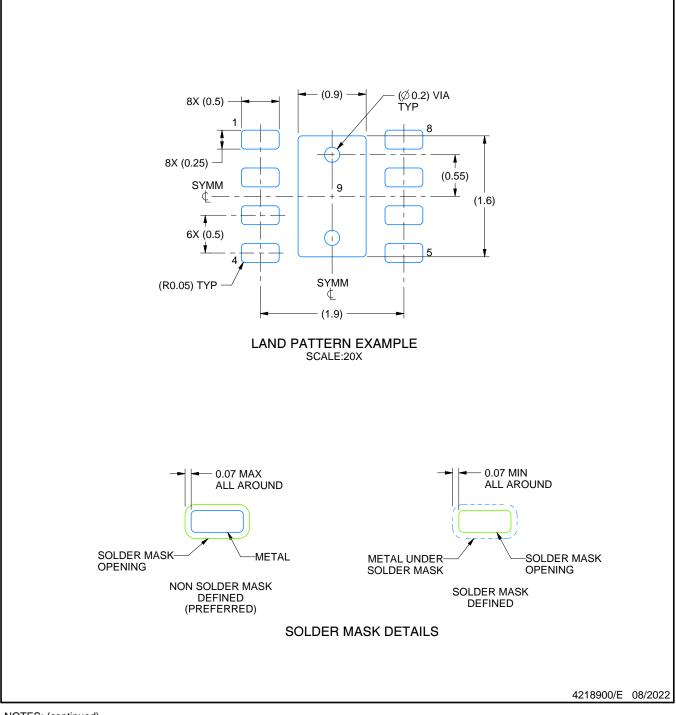

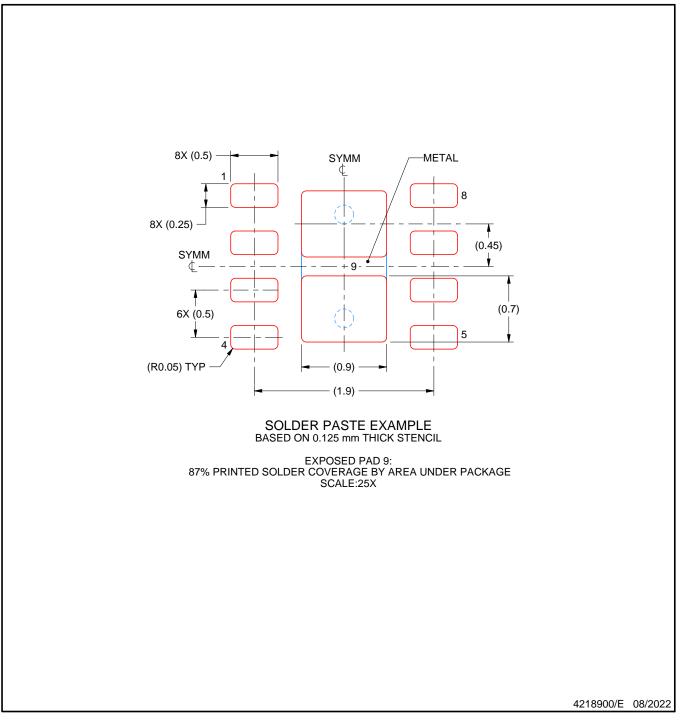

| 部品番号       | パッケージ     | 本体サイズ (公称)      |

|------------|-----------|-----------------|

| DRV8213DSG | WSON (8)  | 2.00mm × 2.00mm |

| DRV8213RTE | WQFN (16) | 3.00mm × 3.00mm |

利用可能なすべてのパッケージについては、データシートの末尾 (1)にある注文情報を参照してください。

概略回路図 (RTE パッケージ)

# **Table of Contents**

| 2 アプリケーション                                                                                                                                                                                                                                                                          | 1          | 1   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|

| 4 Revision History       2         5 Device Comparison       3         6 Pin Configuration and Functions       3         7 Specifications       5         7.1 Absolute Maximum Ratings       5         7.2 ESD Ratings       5         7.3 Recommended Operating Conditions       5 | 1          | 2   |

| 5 Device Comparison       3         6 Pin Configuration and Functions       3         7 Specifications       5         7.1 Absolute Maximum Ratings       5         7.2 ESD Ratings       5         7.3 Recommended Operating Conditions       5                                    | 1          | 3 : |

| 6 Pin Configuration and Functions.       3         7 Specifications.       5         7.1 Absolute Maximum Ratings.       5         7.2 ESD Ratings.       5         7.3 Recommended Operating Conditions.       5                                                                   | 2          | 4   |

| 7 Specifications.       5         7.1 Absolute Maximum Ratings.       5         7.2 ESD Ratings.       5         7.3 Recommended Operating Conditions.       5                                                                                                                      | 3          | 5   |

| 7.1 Absolute Maximum Ratings                                                                                                                                                                                                                                                        |            |     |

| 7.2 ESD Ratings5<br>7.3 Recommended Operating Conditions5                                                                                                                                                                                                                           |            |     |

| 7.3 Recommended Operating Conditions5                                                                                                                                                                                                                                               |            |     |

| 7.3 Recommended Operating Conditions5                                                                                                                                                                                                                                               |            |     |

|                                                                                                                                                                                                                                                                                     | onditions5 |     |

| 7.4 Thermal Information6                                                                                                                                                                                                                                                            | 6          |     |

| 7.5 Electrical Characteristics6                                                                                                                                                                                                                                                     |            |     |

| 7.6 Timing Diagrams9                                                                                                                                                                                                                                                                |            |     |

| 7.7 Typical Operating Characteristics9                                                                                                                                                                                                                                              |            |     |

| 8 Detailed Description11                                                                                                                                                                                                                                                            |            |     |

| 8.1 Overview                                                                                                                                                                                                                                                                        |            |     |

| 8.2 Functional Block Diagram12                                                                                                                                                                                                                                                      |            |     |

| 8.3 External Components13                                                                                                                                                                                                                                                           |            |     |

| 8.4 Feature Description                              | 14                |

|------------------------------------------------------|-------------------|

| 8.5 Device Functional Modes                          | 23                |

| 8.6 Pin Diagrams                                     |                   |

| 9 Application and Implementation                     |                   |

| 9.1 Application Information                          | 26                |

| 9.2 Typical Application                              | 26                |

| 10 Power Supply Recommendations                      |                   |

| 10.1 Bulk Capacitance                                |                   |

| 11 Layout                                            | 40                |

| 11.1 Layout Guidelines                               |                   |

| 12 Device and Documentation Support                  | 41                |

| 12.1 Documentation Support                           |                   |

| 12.2 Receiving Notification of Documentation Updates | s <mark>41</mark> |

| 12.3 Community Resources                             | 41                |

| 12.4 Trademarks                                      |                   |

| 13 Mechanical, Packaging, and Orderable              |                   |

| Information                                          | 41                |

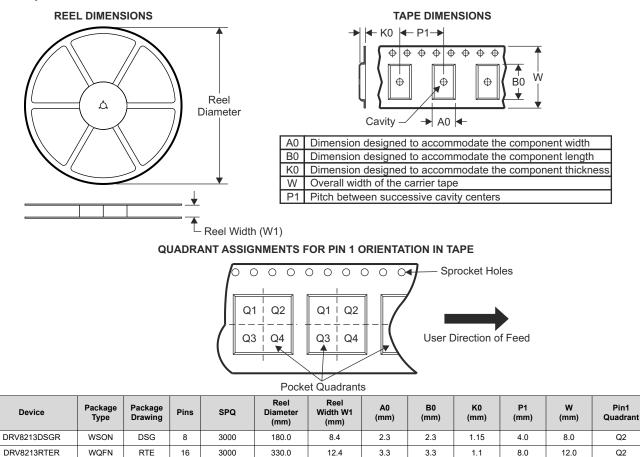

| 13.1 Tape and Reel Information                       |                   |

| •                                                    |                   |

4 Revision History 資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| DATE        | REVISION | NOTES           |

|-------------|----------|-----------------|

| August 2023 | *        | Initial Release |

# **5 Device Comparison**

| Part<br>Number | Package | Supply (VM,<br>Volts) | R <sub>DS(on)</sub> (mΩ) | Current<br>Regulation | Current Sense<br>Output Stall Detection |     | Package Size |

|----------------|---------|-----------------------|--------------------------|-----------------------|-----------------------------------------|-----|--------------|

| DRV8213        | RTE     | 1.65 to 11            | 240                      | Yes                   | Yes                                     | Yes | 3 mm x 3 mm  |

| DRV8213        | DSG     | 1.65 to 11            | 240                      | Yes                   | Yes                                     | No  | 2 mm x 2 mm  |

| DRV8212/P      | DSG     | 1.65 to 11            | 280                      | No                    | No                                      | No  | 2 mm x 2 mm  |

| DRV8210/P      | DSG     | 1.65 to 11            | 1000                     | No                    | No                                      | No  | 2 mm x 2 mm  |

| DRV8837        | DSG     | 0 to 11               | 280                      | No                    | No                                      | No  | 2 mm x 2 mm  |

| DRV8837C       | DSG     | 0 to 11               | 1000                     | No                    | No                                      | No  | 2 mm x 2 mm  |

表 5-1. Device Comparison Table

# **6** Pin Configuration and Functions

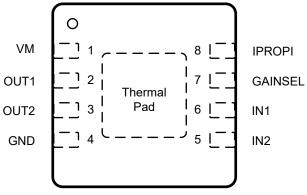

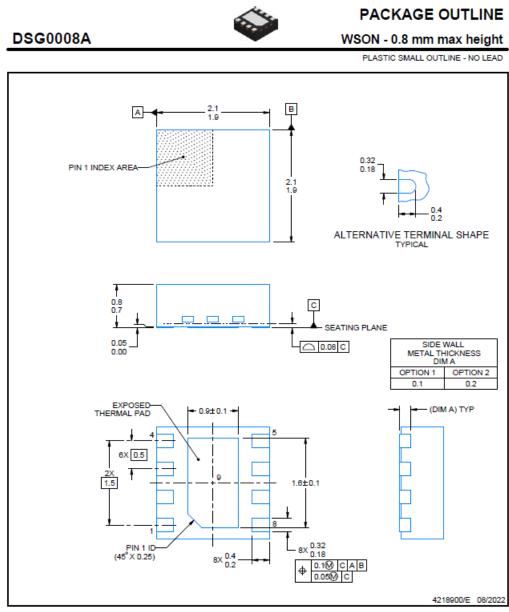

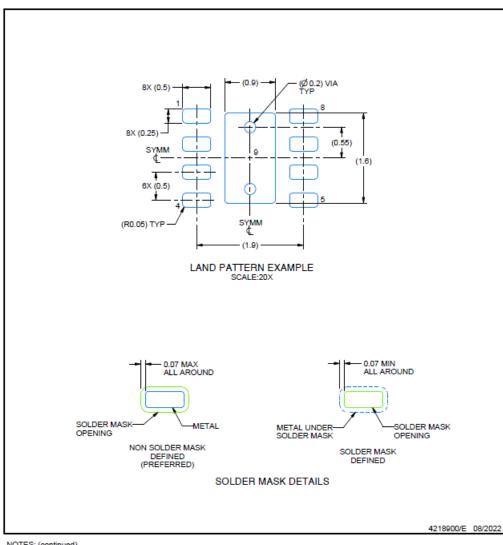

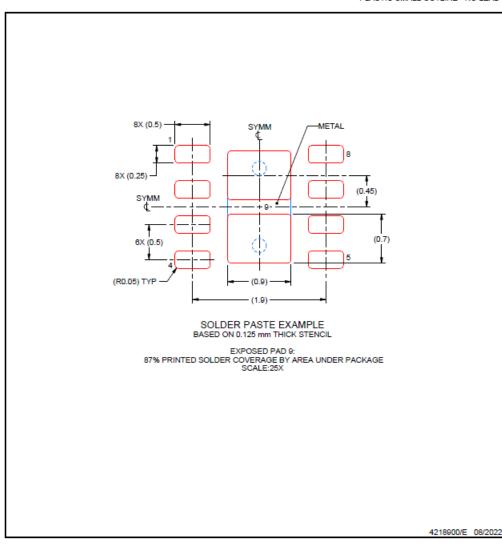

図 6-1. DSG Package (WSON) Top View

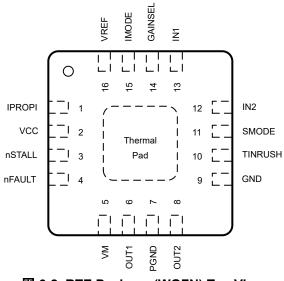

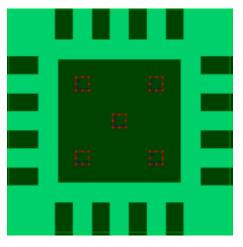

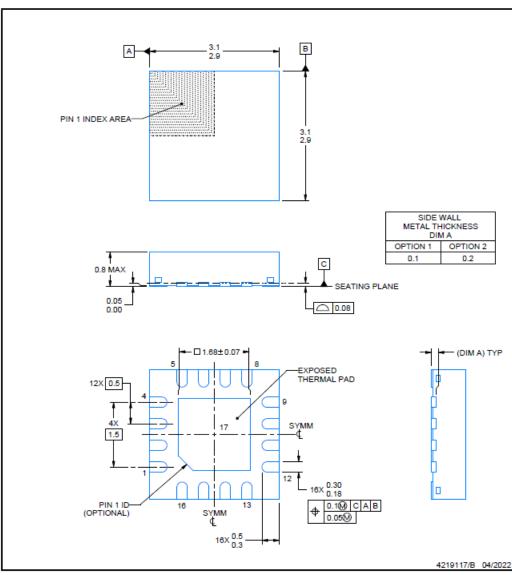

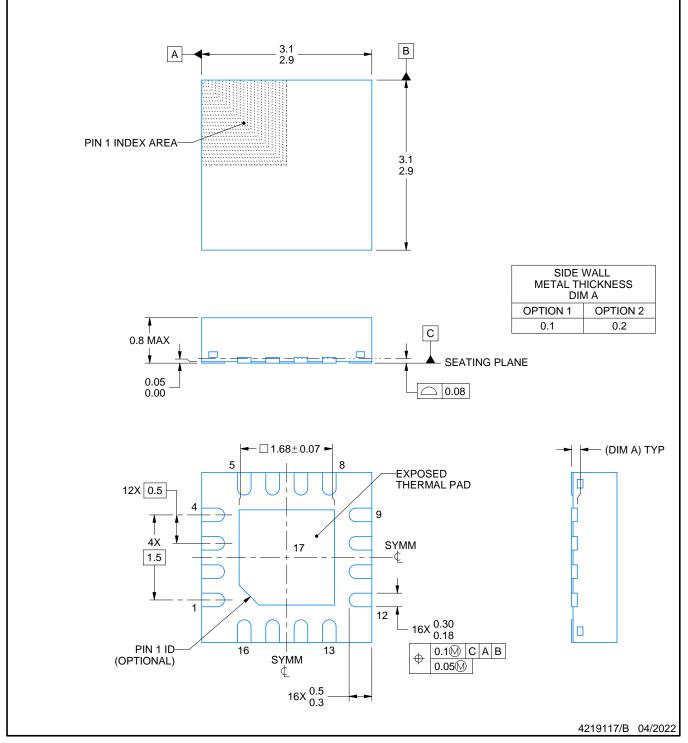

図 6-2. RTE Package (WQFN) Top View

#### 表 6-1. Pin Functions

|                                                                                                                                                                                                                                  | PIN |     |                                                                              |                                                                                                                                                                                                                                                                                   | TVDE | DESCRIPTION |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------|--|--|

| NAME                                                                                                                                                                                                                             | DSG | RTE | ITFE                                                                         | DESCRIPTION                                                                                                                                                                                                                                                                       |      |             |  |  |

| NAME         DSG         RTE           GND         4         9         PW           IMODE         —         15         1           IN1         6         13         1           IN2         5         12         1               |     | PWR | Device ground. Connect to system ground.                                     |                                                                                                                                                                                                                                                                                   |      |             |  |  |

| NAME         DSG         RTE         TYPE           GND         4         9         PWR           IMODE         —         15         1           IN1         6         13         1           IN2         5         12         1 |     | I   | Current regulation mode configuration. Tri-level input. See 表 8-4.           |                                                                                                                                                                                                                                                                                   |      |             |  |  |

| IN1                                                                                                                                                                                                                              | 6   | 13  | I                                                                            | Controls the H-bridge output. Has internal pulldown. Logic input. See 表 8-2.                                                                                                                                                                                                      |      |             |  |  |

| NAME         DSG         RTE           GND         4         9           IMODE         —         15           IN1         6         13           IN2         5         12                                                        |     | I   | Controls the H-bridge output. Has internal pulldown. Logic input. See 表 8-2. |                                                                                                                                                                                                                                                                                   |      |             |  |  |

| IPROPI                                                                                                                                                                                                                           | 8   | 1   | PWR                                                                          | Analog current output proportional to load current. See セクション 8.4.2.1.                                                                                                                                                                                                            |      |             |  |  |

| nFAULT                                                                                                                                                                                                                           | _   | 4   | OD                                                                           | Fault indicator output. Pulled low during a fault condition. Connect an external pullup resistor for open-drain operation. Connect to nSTALL pin to reduce number of external components. See セクション 8.4.4.                                                                        |      |             |  |  |

| nSTALL                                                                                                                                                                                                                           | _   | 3   | OD                                                                           | Stall detection enable and stall indicator output. Pulled low during a stall condition.<br>Connect an external pullup resistor for open-drain operation. Connect to nFAULT pi<br>reduce number of external components. Connect to GND to disable stall detection.<br>セクション 8.4.3. |      |             |  |  |

| OUT1                                                                                                                                                                                                                             | 2   | 6   | 0                                                                            | H-bridge output. Connect directly to the motor or other inductive load.                                                                                                                                                                                                           |      |             |  |  |

| OUT2                                                                                                                                                                                                                             | 3   | 8   | 0                                                                            | H-bridge output. Connect directly to the motor or other inductive load.                                                                                                                                                                                                           |      |             |  |  |

| PGND                                                                                                                                                                                                                             | —   | 7   | PWR                                                                          | Device power ground. Connect to system ground.                                                                                                                                                                                                                                    |      |             |  |  |

| SMODE                                                                                                                                                                                                                            | _   | 11  | I                                                                            | Stall detection response configuration. Tri-level input. See 表 8-6.                                                                                                                                                                                                               |      |             |  |  |

| TINRUSH                                                                                                                                                                                                                          | _   | 10  | 0                                                                            | Sets timing for stall detection to ignore motor inrush current. Connect to a ceramic capacitor to system ground. See セクション 8.4.3.                                                                                                                                                 |      |             |  |  |

| vcc                                                                                                                                                                                                                              | _   | 2   | PWR                                                                          | Logic power supply. Bypass this pin to the GND pin with a 0.1- $\mu$ F ceramic capacitor rated for VCC.                                                                                                                                                                           |      |             |  |  |

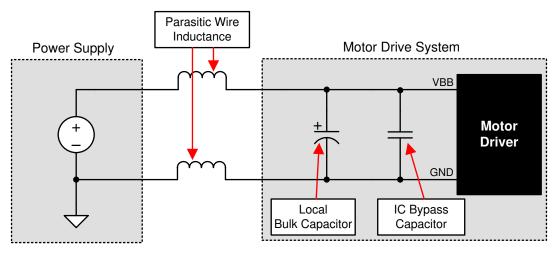

| VM                                                                                                                                                                                                                               | 1   | 5   | PWR                                                                          | Motor power supply. Bypass this pin to the GND pin with a 0.1- $\mu$ F ceramic capacitor as well as sufficient bulk capacitance rated for VM.                                                                                                                                     |      |             |  |  |

| VREF                                                                                                                                                                                                                             | _   | 16  | I                                                                            | Analog input to set current regulation and stall detection level. For the DSG package, VREF is internally fixed at 510 mV. For information on current regulation, see セクション 8.4.2.2. For more information on stall detection, see セクション 8.4.3.                                    |      |             |  |  |

| GAINSEL                                                                                                                                                                                                                          | 7   | 14  | I                                                                            | Configures IPROPI gain factor depeding on the output current range. Tri-level input.                                                                                                                                                                                              |      |             |  |  |

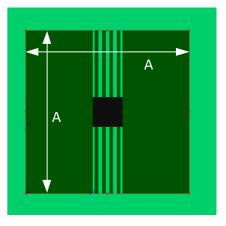

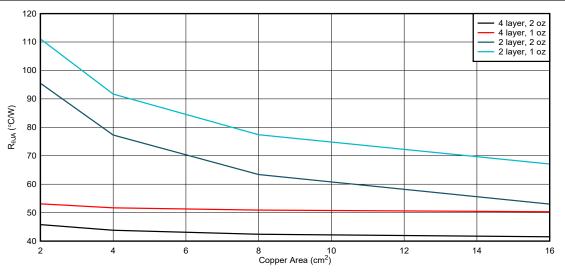

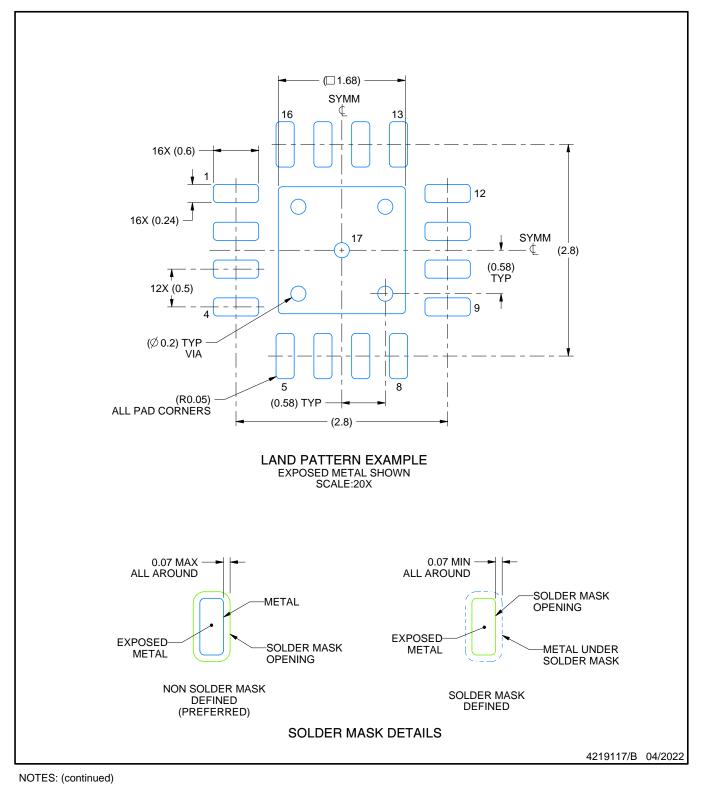

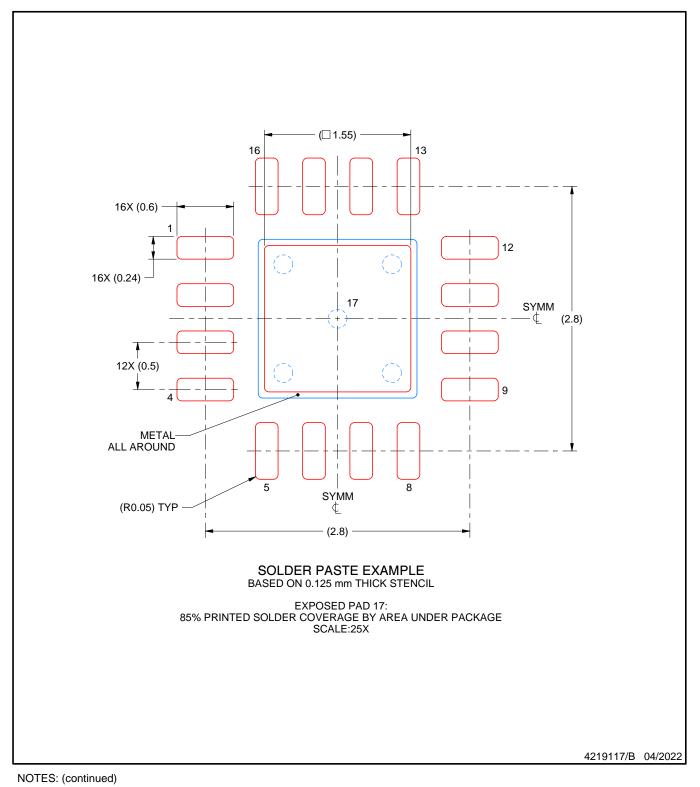

| PAD                                                                                                                                                                                                                              | _   | _   | —                                                                            | Thermal pad. Connect to board ground. For good thermal dissipation, use large ground planes on multiple layers, and multiple nearby vias connecting those planes.                                                                                                                 |      |             |  |  |

# **7** Specifications

#### 7.1 Absolute Maximum Ratings

over operating temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                          |                                         | MIN                   | MAX                              | UNIT |

|----------------------------------------------------------|-----------------------------------------|-----------------------|----------------------------------|------|

| Power supply pin voltage                                 | VM                                      | -0.5                  | 12                               | V    |

| Logic power supply pin voltage                           | VCC                                     | -0.5                  | 5.75                             | V    |

| Power supply transient voltage ramp                      | VM, VCC                                 | 0                     | 2                                | V/µs |

| Voltage difference between ground pins                   | GND, PGND                               | -0.6                  | 0.6                              | V    |

| Logic pin voltage                                        | IN1, IN2, GAINSEL, nSLEEP, IMODE, SMODE | -0.3                  | 5.75                             | V    |

| Open-drain output pin voltage                            | nFAULT, nSTALL                          | -0.3                  | 5.75                             | V    |

| Timing capacitor current output pin voltage              | TINRUSH                                 | -0.3                  | V <sub>VCC</sub>                 | V    |

| Proportional current output pin voltage, VM $\ge$ 5.45 V | - IPROPI                                | -0.3                  | 5.75                             | V    |

| Proportional current output pin voltage, VM $< 5.45$ V   |                                         | -0.3                  | V <sub>VM</sub> + 0.3            | V    |

| Reference input pin voltage                              | VREF                                    | 0.3                   | 5.75                             | V    |

| Output pin voltage                                       | OUTx                                    | -V <sub>SD</sub>      | V <sub>VM</sub> +V <sub>SD</sub> | V    |

| Output current                                           | OUTx                                    | Internally<br>Limited | Internally<br>Limited            | А    |

| Ambient temperature, T <sub>A</sub>                      |                                         | -40                   | 125                              | °C   |

| Junction temperature, T <sub>J</sub>                     |                                         | -40                   | 150                              | °C   |

| Storage temperature, T <sub>stg</sub>                    |                                         | -65                   | 150                              | °C   |

(1) Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|                    |               |                                                                                | VALUE | UNIT |

|--------------------|---------------|--------------------------------------------------------------------------------|-------|------|

|                    | Electrostatic | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 | V    |

| V <sub>(ESD)</sub> | discharge     | Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | v    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Pins listed as ± 2000 V may actually have higher performance.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Pins listed as ± 500 V may actually have higher performance.

#### 7.3 Recommended Operating Conditions

over operating temperature range (unless otherwise noted)

|                                 |                              |                                         | MIN  | NOM | MAX | UNIT |

|---------------------------------|------------------------------|-----------------------------------------|------|-----|-----|------|

| V <sub>VM</sub>                 | Power supply voltage, DSG    | VM                                      | 1.65 |     | 11  | V    |

| V <sub>VM</sub>                 | Power supply voltage, RTE    | VM                                      | 0    |     | 11  | V    |

| V <sub>VCC</sub>                | Power supply voltage, RTE    | VCC                                     | 1.65 |     | 5.5 | V    |

| V <sub>IN</sub>                 | Logic input voltage          | IN1, IN2, nSLEEP, IMODE, SMODE, GAINSEL | 0    |     | 5.5 | V    |

| f <sub>PWM</sub>                | PWM frequency                | IN1, IN2                                | 0    |     | 100 | kHz  |

| V <sub>OD</sub>                 | Open drain pullup voltage    | nFAULT, nSTALL                          | 0    |     | 5.5 | V    |

| I <sub>OD</sub>                 | Open drain output current    | nFAULT, nSTALL                          | 0    |     | 5   | mA   |

| I <sub>OUT</sub> <sup>(1)</sup> | Peak output current          | OUTx                                    | 0    |     | 4   | А    |

| I <sub>IPROPI</sub>             | Current sense output current | IPROPI                                  | 0    |     | 1   | mA   |

over operating temperature range (unless otherwise noted)

|                   |                                 |      | MIN | NOM MAX                                 | UNIT |

|-------------------|---------------------------------|------|-----|-----------------------------------------|------|

| V <sub>VREF</sub> | Current limit reference voltage | VREF | 0   | min (3.3,<br>V <sub>VM</sub> -<br>1.25) | V    |

| T <sub>A</sub>    | Operating ambient temperature   |      | -40 | 125                                     | °C   |

| TJ                | Operating junction temperature  |      | -40 | 150                                     | °C   |

(1) Power dissipation and thermal limits must be observed

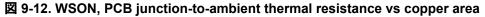

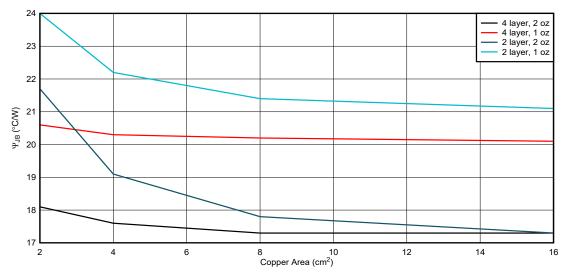

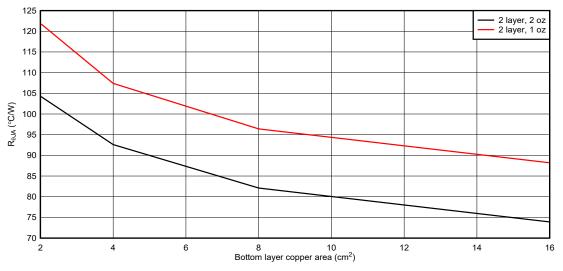

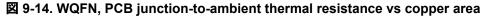

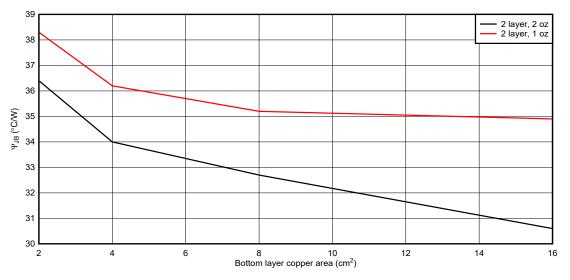

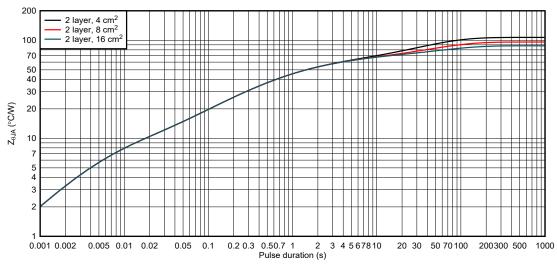

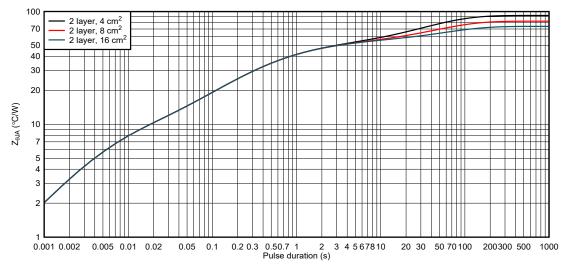

## 7.4 Thermal Information

|                       |                                              | DEVICE     | DEVICE     |      |

|-----------------------|----------------------------------------------|------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | DSG (WSON) | RTE (WQFN) | UNIT |

|                       |                                              | 8 PINS     | 16 PINS    |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 65.9       | 50.7       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 75.2       | 52.0       | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 28.7       | 25.5       | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 2.0        | 1.8        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 28.7       | 25.4       | °C/W |

| $R_{\theta JC(bot)}$  | Junction-to-case (bottom) thermal resistance | 12.0       | 11.2       | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### 7.5 Electrical Characteristics

DSG: 1.65 V  $\leq$  V<sub>VM</sub>  $\leq$  11 V, RTE: 0 V  $\leq$  V<sub>VM</sub>  $\leq$  11 V and 1.65 V  $\leq$  V<sub>VCC</sub>  $\leq$  5.5 V, -40°C  $\leq$  T<sub>J</sub>  $\leq$  150°C (unless otherwise noted). Typical values are at T<sub>J</sub> = 27°C, V<sub>VM</sub> = 5 V, V<sub>VCC</sub> = 3.3 V.

| <u></u>                | PARAMETER                       | TEST CONDITIONS                                                                                                                                                                                                                    | MIN  | TYP  | MAX  | UNIT |

|------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| POWER SU               | PPLIES, DSG (VM)                |                                                                                                                                                                                                                                    |      |      | I    |      |

| I <sub>VMQ</sub>       | VM sleep mode current           | IN1 = IN2 = 0 V, after waiting $t_{AUTOSLEEP}$ ,<br>V <sub>VM</sub> = 5 V, T <sub>J</sub> = 27°C                                                                                                                                   |      | 20   | 60   | nA   |

| I <sub>VM</sub>        | VM active mode current          | IN1 = 3.3 V, IN2 = 0 V                                                                                                                                                                                                             |      | 1.2  | 1.9  | mA   |

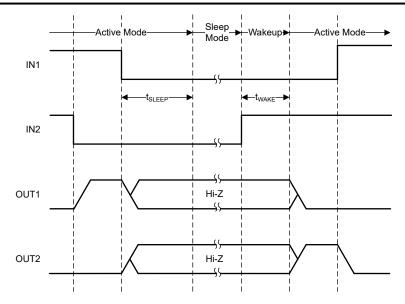

| t <sub>WAKE</sub>      | Turnon time                     | Sleep mode to active mode delay                                                                                                                                                                                                    |      |      | 250  | μs   |

| t <sub>AUTOSLEEP</sub> | Autosleep turnoff time          | Active mode to autosleep mode delay                                                                                                                                                                                                | 0.7  | 1    | 1.3  | ms   |

| f <sub>VCP</sub>       | Charge pump switching frequency |                                                                                                                                                                                                                                    |      | 6000 |      | kHz  |

| POWER SU               | PPLIES, RTE (VM, VCC)           | · · ·                                                                                                                                                                                                                              |      |      |      |      |

| I <sub>VMQ</sub>       | VM sleep mode current           | IN1 = IN2 = 0 V, after waiting $t_{AUTOSLEEP}$ ,<br>V <sub>VM</sub> = 5 V, V <sub>VCC</sub> = 3.3 V, T <sub>J</sub> = 27°C                                                                                                         |      | 10   | 20   | nA   |

| I <sub>VM</sub>        | VM active mode current          | IN1 = 3.3 V, IN2 = 0 V, V <sub>VM</sub> = 5 V, V <sub>VCC</sub> =<br>3.3 V                                                                                                                                                         |      | 0.83 | 1    | mA   |

| I <sub>VCCQ</sub>      | VCC sleep mode current          | $\label{eq:IN1} \begin{array}{l} \text{IN1 = IN2 = 0 V, after waiting } t_{\text{AUTOSLEEP}}, \\ \text{V}_{\text{VM}} = 5 \text{ V}, \text{V}_{\text{VCC}} = 3.3 \text{ V}, \text{ T}_{\text{J}} = 27^{\circ}\text{C} \end{array}$ |      | 6    | 12   | nA   |

| I <sub>VCC</sub>       | VCC active mode current         | IN1 = 3.3 V, IN2 = 0 V, V <sub>VM</sub> = 5 V, V <sub>VCC</sub> = 3.3 V                                                                                                                                                            |      | 0.46 | 0.6  | mA   |

| t <sub>WAKE</sub>      | Turnon time                     | Sleep mode to active mode delay                                                                                                                                                                                                    |      |      | 250  | μs   |

| t <sub>AUTOSLEEP</sub> | Autosleep turnoff time          | Active mode to autosleep mode delay                                                                                                                                                                                                | 0.75 | 0.9  | 1.05 | ms   |

| LOGIC-LEV              | EL INPUTS (IN1, IN2)            |                                                                                                                                                                                                                                    |      |      |      |      |

| V <sub>IL</sub>        | Input logic low voltage         |                                                                                                                                                                                                                                    | 0    |      | 0.4  | V    |

| V <sub>IH</sub>        | Input logic high voltage        |                                                                                                                                                                                                                                    | 1.45 |      | 5.5  | V    |

| V <sub>HYS</sub>       | Input hysteresis                |                                                                                                                                                                                                                                    | 40   |      |      | mV   |

| IIL                    | Input logic low current         | V <sub>1</sub> = 0 V                                                                                                                                                                                                               | -1   |      | 1    | μA   |

DSG: 1.65 V  $\leq$  V<sub>VM</sub>  $\leq$  11 V, RTE: 0 V  $\leq$  V<sub>VM</sub>  $\leq$  11 V and 1.65 V  $\leq$  V<sub>VCC</sub>  $\leq$  5.5 V, -40°C  $\leq$  T<sub>J</sub>  $\leq$  150°C (unless otherwise noted). Typical values are at T<sub>J</sub> = 27°C, V<sub>VM</sub> = 5 V, V<sub>VCC</sub> = 3.3 V.

|                         | PARAMETER                                    | TEST CONDITIONS                                                                                                                                                                                                | MIN  | TYP  | MAX  | UNIT |

|-------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| L                       | Input logic high current                     | V <sub>INx</sub> = 5 V                                                                                                                                                                                         | 15   |      | 35   | μA   |

| IH                      |                                              | V <sub>nSTALL</sub> = VCC                                                                                                                                                                                      |      |      | 40   | nA   |

| ۲ <sub>PD</sub>         | Input pulldown resistance, INx               |                                                                                                                                                                                                                |      | 200  |      | kΩ   |

| DEGLITCH                | Input logic deglitch, INx                    |                                                                                                                                                                                                                |      | 50   |      | ns   |

| TRI-LEVEL               | INPUTS (IMODE, SMODE)                        | · · ·                                                                                                                                                                                                          |      |      |      |      |

| V <sub>THYS</sub>       | Tri-level input logic low voltage            |                                                                                                                                                                                                                | 0    |      | 0.4  | V    |

| TIL                     | Tri-level input Hi-Z voltage                 |                                                                                                                                                                                                                | 0.75 |      | 1.05 | V    |

| TIZ                     | Tri-level input logic high voltage           |                                                                                                                                                                                                                | 1.45 |      | 5.5  | V    |

| R <sub>TPD</sub>        | Tri-level pulldown resistance                | to GND                                                                                                                                                                                                         |      | 83   |      | kΩ   |

| TPU                     | Tri-level pullup current                     | to VCC                                                                                                                                                                                                         |      | 10.5 |      | μA   |

| OPEN-DRA                | IN OUTPUTS (nFAULT, nSTALL)                  |                                                                                                                                                                                                                |      |      |      |      |

| V <sub>OL</sub>         | Output logic low voltage                     | I <sub>OD</sub> = 5 mA                                                                                                                                                                                         |      |      | 0.4  | V    |

| oz                      | Output logic high current                    | V <sub>OD</sub> = VCC                                                                                                                                                                                          | -1   |      | 1    | μA   |

|                         | ITPUTS (OUTx)                                |                                                                                                                                                                                                                |      |      |      |      |

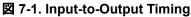

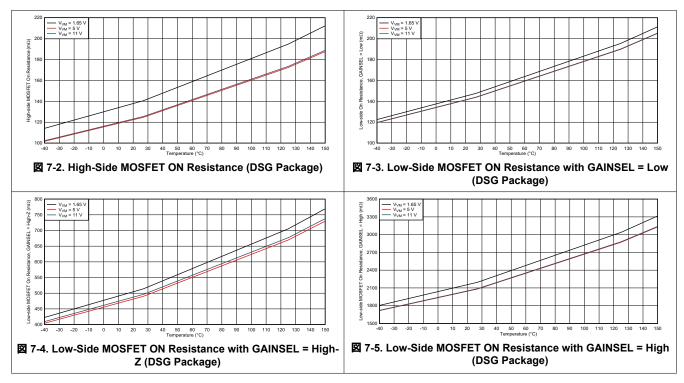

| R <sub>DS(ON)_HS</sub>  | High-side MOSFET on resistance               | I <sub>OUTx</sub> = 1 A                                                                                                                                                                                        |      | 120  | 280  | mΩ   |

| R <sub>DS(ON)</sub> _LS | Low-side MOSFET on resistance, 350mA to 2A   | GAINSEL = Low                                                                                                                                                                                                  |      | 120  | 260  | mΩ   |

| R <sub>DS(ON)_LS</sub>  | Low-side MOSFET on resistance, 60mA to 350mA | GAINSEL = High-Z                                                                                                                                                                                               |      | 460  | 900  | mΩ   |

| R <sub>DS(ON)_LS</sub>  | Low-side MOSFET on resistance, 10mA to 60mA  | GAINSEL = High                                                                                                                                                                                                 |      | 2100 | 4000 | mΩ   |

| V <sub>SD</sub>         | Body diode forward voltage                   | I <sub>OUTx</sub> = -1 A                                                                                                                                                                                       |      | 0.9  |      | V    |

| RISE                    | Output rise time                             | $V_{OUTx}$ rising from 10% to 90% of $V_{VM}$                                                                                                                                                                  |      | 70   |      | ns   |

| FALL                    | Output fall time                             | $V_{OUTx}$ falling from 90% to 10% of $V_{VM}$                                                                                                                                                                 |      | 40   |      | ns   |

| PDR                     | Input high to output high propagation delay  | Input to OUTx                                                                                                                                                                                                  |      | 450  |      | ns   |

| PDF                     | Input low to output low propagation delay    | Input to OUTx                                                                                                                                                                                                  |      | 450  |      | ns   |

|                         | Output dead time                             |                                                                                                                                                                                                                |      | 500  |      | ns   |

|                         | SENSE AND REGULATION (IPROPI, VRE            | F)                                                                                                                                                                                                             |      |      |      |      |

| V <sub>REF_INT</sub>    | Internal reference voltage                   | SMODE = Open for RTE package and for DSG package                                                                                                                                                               | 470  | 510  | 550  | mV   |

| A <sub>IPROPI H</sub>   | Current scaling factor                       | GAINSEL = Low                                                                                                                                                                                                  |      | 205  |      | µA/A |

|                         | Current scaling factor                       | GAINSEL = High-Z                                                                                                                                                                                               |      | 1050 |      | μΑ/Α |

| AIPROPI L               | Current scaling factor                       | GAINSEL = High                                                                                                                                                                                                 |      | 4900 |      | μΑ/Α |

| A <sub>ERR_H</sub>      | Current mirror total error, 350 mA to 2 A    | GAINSEL = Low, $V_{IPROPI} \le min(VM-1.25)$<br>V, 3.3 V), 3.3 V $\le V_{VM} \le 11$ V                                                                                                                         | -6   |      | 6    | %    |

| A <sub>ERR_H</sub>      | Current mirror total error, 350 mA to 2 A    | GAINSEL = Low, $V_{IPROPI} \le min(VM-1.25)$<br>V, 3.3 V), 1.65 V $\le V_{VM} \le 3.3$ V                                                                                                                       | -6   |      | 6    | %    |

|                         | Current mirror total error, 60 mA to 350     | $ \begin{array}{l} \text{GAINSEL} = \text{High-Z}, \ \text{V}_{\text{IPROPI}} \leq \\ \text{min}(\text{VM-1.25 V}, 3.3 \text{ V}), \ 3.3 \text{ V} \leq \text{V}_{\text{VM}} \leq 11 \\ \text{V} \end{array} $ | -6   |      | 6    | %    |

| A <sub>ERR_M</sub>      | mA                                           | GAINSEL = High-Z, V <sub>IPROPI</sub> ≤<br>min(VM-1.25 V, 3.3 V), 1.65 V ≤ V <sub>VM</sub> ≤<br>3.3 V                                                                                                          | -6   |      | 6    | %    |

| ۸                       | Current mirror total error, 10 mA to 60      | $ \begin{array}{l} \mbox{GAINSEL = High, V_{IPROPI} \leq min(VM-1.25 \\ \mbox{V, 3.3 V}, 3.3 V \leq V_{VM} \leq 11 \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ $                                                         | -6   |      | 6    | %    |

| A <sub>ERR_L</sub>      | mA                                           |                                                                                                                                                                                                                | -6   |      | 6    | %    |

DSG: 1.65 V  $\leq$  V<sub>VM</sub>  $\leq$  11 V, RTE: 0 V  $\leq$  V<sub>VM</sub>  $\leq$  11 V and 1.65 V  $\leq$  V<sub>VCC</sub>  $\leq$  5.5 V, -40°C  $\leq$  T<sub>J</sub>  $\leq$  150°C (unless otherwise noted). Typical values are at T<sub>J</sub> = 27°C, V<sub>VM</sub> = 5 V, V<sub>VCC</sub> = 3.3 V.

|                           | PARAMETER                                                    | TEST CONDITIONS                                                                                        | MIN  | TYP | MAX  | UNIT |

|---------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------|-----|------|------|

| t <sub>OFF</sub>          | Current regulation off time                                  |                                                                                                        |      | 20  |      | μs   |

| t <sub>BLANK</sub>        | Current regulation blanking time                             |                                                                                                        |      | 1.8 |      | μs   |

| t <sub>DELAY</sub>        | Current sense delay time                                     |                                                                                                        |      | 1.5 |      | μs   |

| t <sub>DEG</sub>          | Current regulation and stall detection deglitch time         |                                                                                                        |      | 2   |      | μs   |

| HARDWARE                  | STALL DETECTION (TINRUSH)                                    |                                                                                                        |      |     |      |      |

| V <sub>TINRUSH_trip</sub> | Threshold voltage for setting t <sub>INRUSH</sub> timing     |                                                                                                        | 0.97 | 1   | 1.03 | V    |

| I <sub>TINRUSH</sub>      | Current sourced out of the TINRUSH pin                       | Inputs transition to a state other than<br>IN1=IN2=0, V <sub>TINRUSH</sub> < V <sub>TINRUSH_trip</sub> | 8    | 10  | 12   | μA   |

| t <sub>discharge</sub>    | TINRUSH capacitor discharge time                             | $0.8 \text{ nF} \le C_{\text{TINRUSH}} \le 0.8 \mu\text{F}$                                            |      |     | 100  | μs   |

| t <sub>STALL_RETRY</sub>  | IN1/IN2 = 0/0 duration to recover from<br>Stall (retry type) |                                                                                                        | 350  |     | 900  | μs   |

| PROTECTIO                 | N CIRCUITS                                                   | ·                                                                                                      |      |     |      |      |

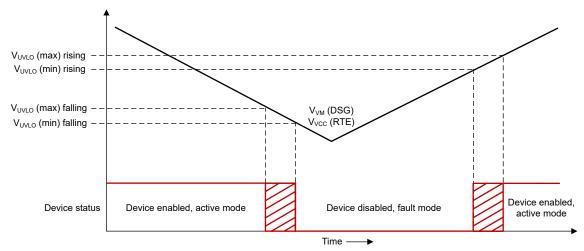

| \/                        | VM supply undervoltage lockout (UVLO),                       | Supply rising                                                                                          |      |     | 1.65 | V    |

| V <sub>UVLO_VM</sub>      | DSG                                                          | Supply falling                                                                                         | 1.30 |     |      | V    |

| Vinne vice                | VCC supply undervoltage lockout                              | Supply rising                                                                                          |      |     | 1.65 | V    |

| V <sub>UVLO_VCC</sub>     | (UVLO), RTE                                                  | Supply falling                                                                                         | 1.30 |     |      | V    |

| V <sub>UVLO_HYS</sub>     | Supply UVLO hysteresis                                       | Rising to falling threshold                                                                            |      | 150 |      | mV   |

| t <sub>UVLO</sub>         | Supply undervoltage deglitch time                            | $V_{\text{VM}}$ falling (DSG) or $V_{\text{VCC}}$ falling (RTE) to OUTx disabled                       |      | 10  |      | μs   |

| I <sub>OCP</sub>          | Overcurrent protection trip point, 350mA to 2A               |                                                                                                        | 4    |     |      | А    |

| I <sub>OCP</sub>          | Overcurrent protection trip point, 60mA to 350mA             |                                                                                                        | 0.8  |     |      | А    |

| I <sub>OCP</sub>          | Overcurrent protection trip point, 10mA to 60mA              |                                                                                                        | 0.16 |     |      | А    |

| t <sub>OCP</sub>          | Overcurrent protection deglitch time                         |                                                                                                        |      | 4.2 |      | μs   |

| t <sub>RETRY</sub>        | Fault retry time                                             |                                                                                                        |      | 1.5 |      | ms   |

| T <sub>TSD</sub>          | Thermal shutdown temperature                                 |                                                                                                        | 165  | 175 | 185  | °C   |

| T <sub>HYS</sub>          | Thermal shutdown hysteresis                                  |                                                                                                        |      | 17  |      | °C   |

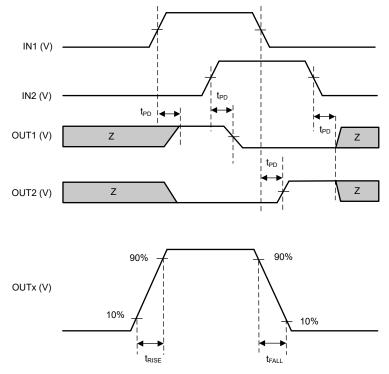

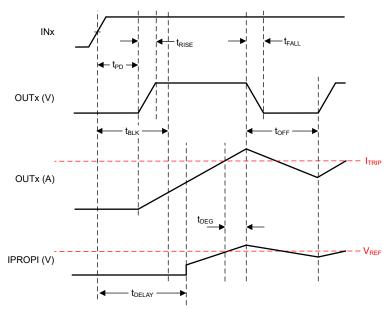

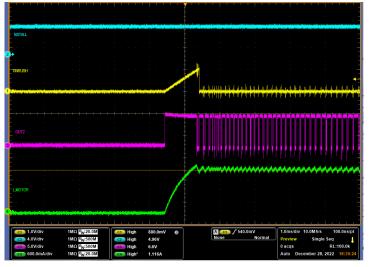

## 7.6 Timing Diagrams

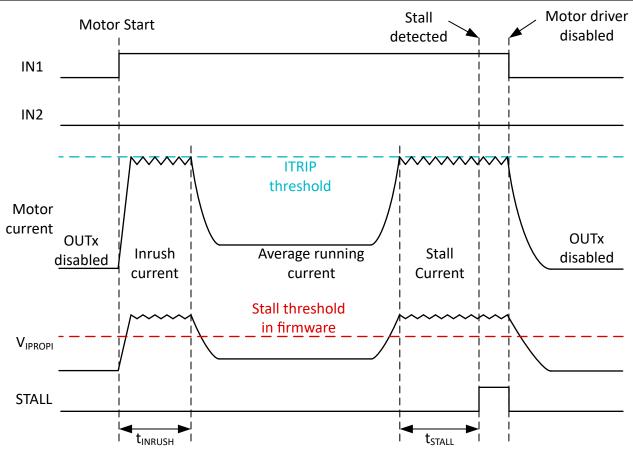

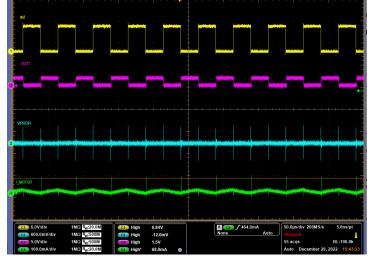

# 7.7 Typical Operating Characteristics

# 7.7 Typical Operating Characteristics (continued)

# 8 Detailed Description

#### 8.1 Overview

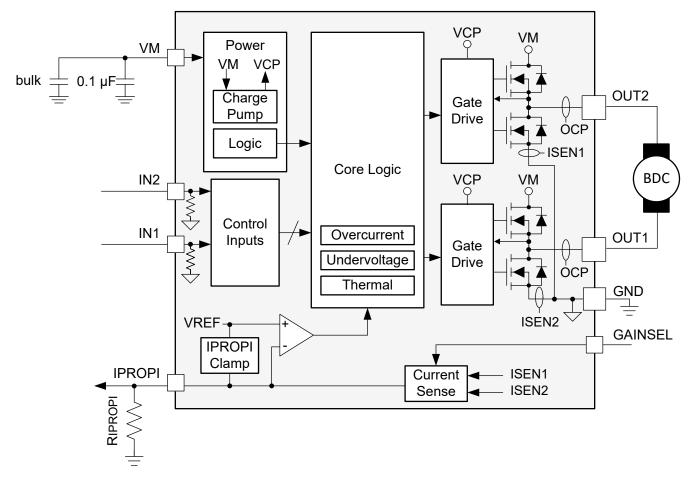

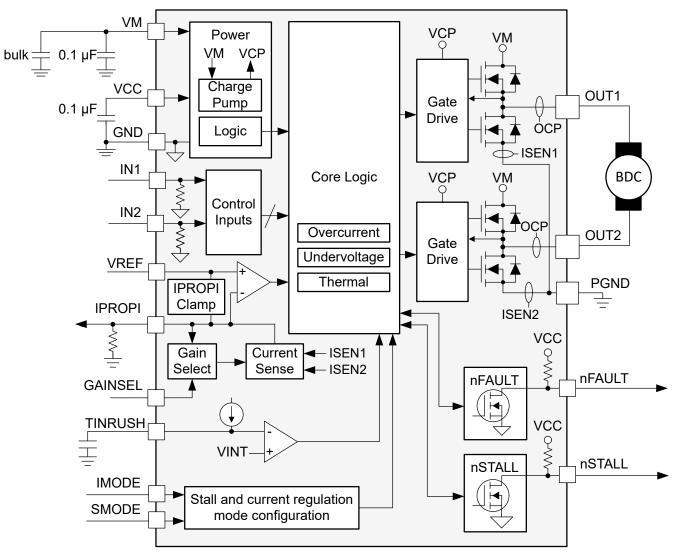

DRV8213 is a full-bridge driver with integrated current sense, current regulation, and current sense output. To reduce area and external components on a printed circuit board, the device integrates a charge pump regulator and capacitors. In the WQFN (RTE) package, the separate full-bridge (VM) and logic (VCC) supplies allow the full-bridge supply voltage to drop to 0 V without significant impact to  $R_{DS(ON)}$  and without triggering UVLO as long as the VCC supply is stable. In the WSON (DSG) package, a single power input (VM) serves as both device power and the full-bridge supply for small design size. An auto-sleep mode reduces microcontroller GPIO connections by eliminating a disable/sleep pin and automatically putting the device into a low-power sleep mode when the PWM inputs remain low for t<sub>AUTOSLEEP</sub>.

The DRV8213 uses a standard 2-pin (IN1/IN2) PWM interface. The IN1/IN2 pins control the full bridge, which consists of four N-channel MOSFETs that have a typical  $R_{DS(ON)}$  of 240 m $\Omega$  (including one high-side and one low-side FET). Motor speed can be controlled with pulse-width modulation (PWM), at frequencies between 0 to 100 kHz.

The integrated current regulation feature limits motor current to a predefined maximum based on the VREF and IPROPI settings. The IPROPI signal can provide current feedback to a microcontroller during both the drive and brake/slow-decay states of the H-bridge.

The gain select (GAINSEL) feature allows high accuracy current sensing down to 10 mA average motor current. The  $R_{DS(ON)}$  of the low-side MOSFET and the overcurrent protection limit changes according to the GAINSEL setting, thereby leading to optimized answers for different applications and different values of motor current.

In the WQFN package (RTE), the DRV8213 has additional pins to configure a hardware stall detection feature based on the IPROPI current sensing signal.

The integrated protection features protect the device in the case of a system fault. These include undervoltage lockout (UVLO), overcurrent protection (OCP), and overtemperature shutdown (TSD).

### 8.2 Functional Block Diagram

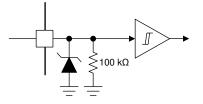

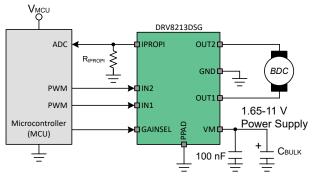

#### 図 8-1. DRV8213 in WSON (DSG) package with single supply pin

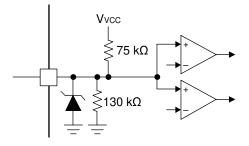

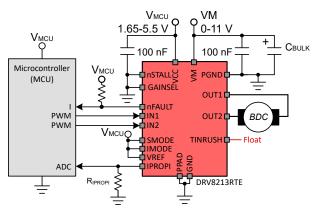

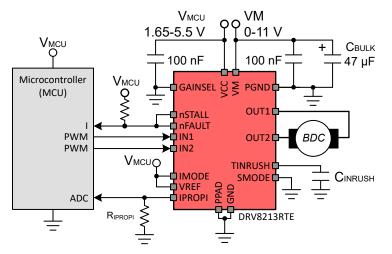

#### 図 8-2. DRV8213 in WQFN (RTE) package with stall detection and dual supply pins

### 8.3 External Components

$\pm$  8-1 lists the recommended external components for the device.

表 8-1. Recommended external components

| COMPONENT           | PIN 1   | PIN 2  | RECOMMENDED                                                        |

|---------------------|---------|--------|--------------------------------------------------------------------|

| C <sub>VM1</sub>    | VM      | GND    | 0.1-µF, low ESR ceramic capacitor, VM-rated                        |

| C <sub>VM2</sub>    | VM      | GND    | セクション 10.1, VM-rated                                               |

| C <sub>VCC</sub>    | VCC     | GND    | 0.1-µF, low ESR ceramic capacitor, VM-rated                        |

| R <sub>IPROPI</sub> | IPROPI  | GND    | Resistor from IPROPI pin to GND, sets the current regulation level |

| C <sub>INRUSH</sub> | TINRUSH | GND    | Sets the inrush current blanking time                              |

| R <sub>nFAULT</sub> | VCC     | nFAULT | 10 κΩ                                                              |

| R <sub>nSTALL</sub> | VCC     | nSTALL | 10 κΩ                                                              |

# 8.4 Feature Description

vм

└ <u></u>

Forward

# 8.4.1 Bridge Control

The DRV8213 output consists of four N-channel MOSFETs designed to drive high current. These outputs are controlled by the two PWM inputs IN1 and IN2 as listed in  $\frac{1}{2}$  8-2.

| IN1 | IN2 | OUT1   | OUT2   | DESCRIPTION                                                                      |

|-----|-----|--------|--------|----------------------------------------------------------------------------------|

| 0   | 0   | High-Z | High-Z | Coast; H-bridge disabled to High-Z (sleep entered after t <sub>AUTOSLEEP</sub> ) |

| 0   | 1   | L      | Н      | Reverse (Current OUT2 $\rightarrow$ OUT1)                                        |

| 1   | 0   | Н      | L      | Forward (Current OUT1 $\rightarrow$ OUT2)                                        |

| 1   | 1   | L      | L      | Brake; low-side slow decay                                                       |

表 8-2. H-Bridge Control

The inputs can be set to static voltages for 100% duty cycle drive, or they can be pulse-width modulated (PWM) for variable motor speed. When using PWM, switching between driving and braking typically works best. For example, to drive a motor forward with 50% of the maximum RPM, IN1 = 1 and IN2 = 0 during the driving period, and IN1 = 1 and IN2 = 1 during the other period. Alternatively, the coast mode (IN1 = 0, IN2 = 0) for *fast current decay* is also available. 🛛 8-3 shows how the motor current flows through the H-bridge. The input pins can be powered before VM or VCC are applied.

VM

Reverse

#

When an output changes from driving high to driving low, or driving low to driving high, dead time is automatically inserted to prevent shoot-through. The  $t_{DEAD}$  time is the time in the middle when the output is High-Z. If the output pin is measured during  $t_{DEAD}$ , the voltage depends on the direction of current. If the current is leaving the pin, the voltage is a diode drop below ground. If the current is entering the pin, the voltage is a diode drop above VM. This diode is the body diode of the high-side or low-side FET.

The propagation delay time  $(t_{PD})$  is measured as the time between an input edge to output change. This time accounts for input deglitch time and other internal logic propagation delays. The input deglitch time prevents noise on the input pins from affecting the output state. Additional output slew delay timing accounts for FET turn on or turn off times ( $t_{RISE}$  and  $t_{FALL}$ ).

Copyright © 2023 Texas Instruments Incorporated

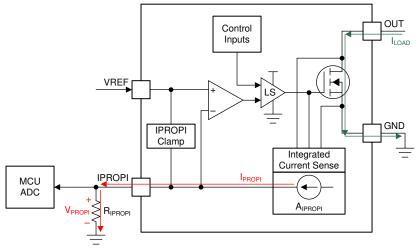

#### 8.4.2 Current Sense and Regulation (IPROPI)

The DRV8213 device integrates current sensing, regulation, and current sense feedback. The internal current mirror allows the device to sense the output current without an external sense resistor or sense circuitry, thereby reducing system size, cost, and complexity. The current regulation feature allows for the device to limit the output current in the case of motor stall or high torque events and give detailed feedback to the controller about the load current using the IPROPI output. 🛛 8-4 shows the IPROPI timings specified in the Electrical Characteristics table.

#### 8.4.2.1 Current Sensing and Current Mirror Gain Selection

The IPROPI pin outputs an analog current proportional to the current flowing through the low-side power MOSFETs in the H-bridge and scaled by the current mirror gain ( $A_{IPROPI}$ ). The IPROPI output current can be calculated by  $\overrightarrow{\pi}$  1. The I<sub>LSx</sub> in  $\overrightarrow{\pi}$  1 is only valid when the current flows from drain to source in the low-side MOSFET. If current flows from source to drain or through the body diode, the value of I<sub>LSx</sub> for that channel is zero. For instance, if the bridge is in the brake, slow-decay state, then the current out of IPROPI is only proportional to the current in one of the low-side MOSFETs.

$$I_{PROPI}$$

( $\mu A$ ) = ( $I_{LS1}$  +  $I_{LS2}$ ) (A) x A<sub>IPROPI</sub> ( $\mu A/A$ )

(1)

The  $A_{ERR}$  parameter in the Electrical Characteristics table is the error associated with the  $A_{IPROPI}$  gain.  $A_{ERR}$  indicates the combined effect of offset error added to the  $I_{OUT}$  current and gain error.

Depending on the application, high accuracy current sense output is required down to 10 mA current. The GAINSEL feature allows optimizing the design for different end applications by reducing OCP limit and increasing current mirror gain at lower motor currents. The current mirror gain  $A_{IPROPI}$  depends on the GAINSEL pin setting, as shown in  $\gtrsim 8-3$ .

| GAINSEL | A <sub>IPROPI</sub> | Recommended Current Range | Low-side FET R <sub>DS(ON)</sub> | Minimum OCP Limit |  |  |  |

|---------|---------------------|---------------------------|----------------------------------|-------------------|--|--|--|

| Low     | 205 µA/A            | 350 mA to 2 A             | 120 mΩ                           | 4 A               |  |  |  |

| High-Z  | 1050 µA/A           | 60 mA to 350 mA           | 460 mΩ                           | 800 mA            |  |  |  |

| High    | 4900 µA/A           | 10 mA to 60 mA            | 2100 mΩ                          | 160 mA            |  |  |  |

| 表 8-3. GAINSEL Settir | ١g |

|-----------------------|----|

|-----------------------|----|

The motor current is measured by an internal current mirror architecture on the low-side FETs which removes the need for an external power sense resistor as shown in  $\boxtimes$  8-5. The current mirror architecture senses motor winding current in both the drive and brake low-side slow-decay periods, therefore allowing continuous current monitoring in typical bidirectional brushed DC motor applications. In coast mode, the current is freewheeling and cannot be sensed because the current flows from source to drain. However, the current can be sampled by briefly reenabling the driver in either drive or slow-decay modes and measuring the current before switching back to coast mode again.

Copyright © 2017, Texas Instruments Incorporated

#### **8-5.** Integrated Current Sensing

The IPROPI pin is connected to an external resistor ( $R_{IPROPI}$ ) to ground to generate a proportional voltage ( $V_{IPROPI}$ ) on the IPROPI pin with the  $I_{IPROPI}$  analog current output. This allows for the load current to be measured as the voltage drop across the  $R_{IPROPI}$  resistor with a standard analog to digital converter (ADC). The  $R_{IPROPI}$  resistor can be sized based on the expected load current in the application so that the full range of the controller ADC is utilized.

Additionally, the DRV8213 device implements an internal IPROPI voltage clamp circuit to limit  $V_{IPROPI}$  with respect to  $V_{VREF}$  on the VREF pin and protect the external ADC in case of output overcurrent or unexpected high current events. For the DSG package,  $V_{VREF}$  is set at 510 mV internally. TI recommends designing for at least 1.25 V of headroom between  $V_{VM}$  and the maximum  $V_{IPROPI}$  voltage to be measured by the ADC,  $V_{IPROPI}$  MAX. This maintains good accuracy across the range of VIPROPI voltages measured by the ADC. For instance, if  $V_{VM}$  is 4.55 V to 11 V,  $V_{IPROPI}_{MAX}$  can be as high as 3.3 V. However, if  $V_{VM}$  is 3.3 V, then VIPROPI has good accuracy up to 2.05 V.

The corresponding IPROPI voltage to the output current can be calculated by  $\pm 2$ .

$$V_{IPROPI}(V) = I_{PROPI}(A) \times R_{IPROPI}(\Omega)$$

(2)

The IPROPI output bandwidth is limited by the sense delay time ( $t_{DELAY}$ ) of the internal current sensing circuit. This time is the delay from the low-side MOSFET enable command (from the INx pins) to the IPROPI output being ready.

If the device is alternating between drive and slow-decay (brake) in an H-bridge PWM pattern then the low-side MOSFET sensing the current is continuously on and the sense delay time has no impact to the IPROPI output. If a command on the INx pins disables the low-side MOSFETs (according to the logic tables in  $2923 \times 8.4.1$ ), the IPROPI output disables with the input logic signal. Although the low-side MOSFETs still conduct current as the MOSFETs disable according to the device slew rate (noted in the Electrical Characteristics table by t<sub>RISE</sub> time), IPROPI does not represent the current in the low-side MOSFETs during this turnoff time.

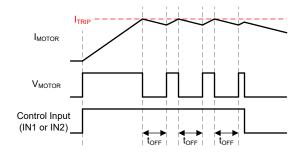

#### 8.4.2.2 Current Regulation

The DRV8213 device integrates current regulation using a fixed off-time current chopping scheme, as shown in  $\boxtimes$  8-6. This allows the device to limit the output current in case of motor stall, high torque, or other high current load events without involvement from the external controller.

図 8-6. Off-Time Current-Regulation

The current chopping threshold ( $I_{TRIP}$ ) is set through a combination of the VREF voltage ( $V_{VREF}$ ) and IPROPI output resistor ( $R_{IPROPI}$ ). This is done by comparing the voltage drop across the external  $R_{IPROPI}$  resistor to  $V_{VREF}$  with an internal comparator.

$$I_{\text{TRIP}}(A) \times A_{\text{IPROPI}}(\mu A/A) = V_{\text{VREF}}(V) / R_{\text{IPROPI}}(\Omega)$$

(3)

For example, if  $V_{VREF}$  = 3.3 V,  $R_{IPROPI}$  = 8.06 k $\Omega$ , and  $A_{IPROPI}$  = 205  $\mu$ A/A, then  $I_{TRIP}$  will be approximately 2 A.

$V_{VREF}$  must be lower than  $V_{VM}$  by at least 1.25 V. The maximum recommended value of  $V_{VREF}$  is 3.3 V.

As mentioned before, for DSG package,  $V_{VREF}$  is internally fixed at 510 mV. For RTE package as well, if SMODE is left OPEN,  $V_{VREF}$  is internally fixed at 510 mV.

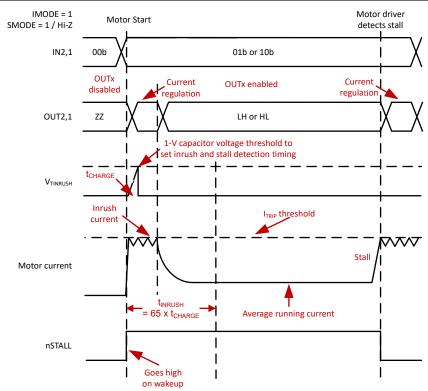

The fixed off-time current chopping scheme supports up to 100% duty cycle current regulation since the H-bridge automatically enables after the  $t_{OFF}$  period and does not require a new control input edge on the INx pins to reset the outputs. When the motor current exceeds the  $I_{TRIP}$  threshold, the outputs will enter a current chopping mode with a fixed off time ( $t_{OFF}$ ). During  $t_{OFF}$ , the H-bridge enters a brake/low-side slow decay state (both low-side MOSFETs ON) for  $t_{OFF}$  duration after  $I_{OUT}$  exceeds  $I_{TRIP}$ . After  $t_{OFF}$ , the outputs re-enable according to the control inputs if  $I_{OUT}$  is less than  $I_{TRIP}$ . If  $I_{OUT}$  is still greater than  $I_{TRIP}$ , the H-bridge enters another period of brake/low-side slow decay for  $t_{OFF}$  after a drive time of  $t_{BLANK}$ . If the state of the INx control pins changes during the  $t_{OFF}$  time, the remainder of the  $t_{OFF}$  time is ignored, and the outputs will again follow the inputs.

The  $I_{TRIP}$  comparator has both a blanking time ( $t_{BLK}$ ) and a deglitch time ( $t_{DEG}$ ). The internal blanking time helps to prevent voltage and current transients during output switching from effecting the current regulation. These transients may be caused by a capacitor inside the motor or on the connections to the motor terminals. The internal deglitch time ensures that transient conditions do not prematurely trigger the current regulation. In certain cases where the transient conditions are longer than the deglitch time, placing a 10-nF capacitor on the IPROPI pin, close to the device, will help filter the transients on IPROPI output so current regulation does not prematurely trigger. The capacitor value can be adjusted as needed, however large capacitor values may slow down the response time of the current regulation circuitry.

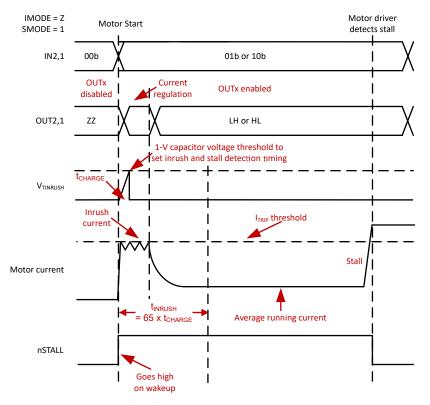

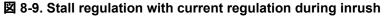

The IMODE pin determines the behavior of current regulation in the motor driver. When IMODE is logic low (IMODE = 0), current regulation is disabled. When IMODE is floating (IMODE =Z), the device only performs current regulation during the  $t_{INRUSH}$  time when stall detection is enabled. This functionality relates to the hardware stall detection feature described in  $\forall 2 \neq 2 \neq 8.4.3$ . When IMODE is logic high (IMODE = 1), current regulation is enabled at all times.  $\frac{1}{2} \times 8.4$  summarizes the IMODE pin settings.

| IMODE | nSTALL | Description                       |

|-------|--------|-----------------------------------|

| Low   | Х      | No current regulation at any time |

| 表 8-4. IMODE configuration (continued) |      |                                                    |  |  |

|----------------------------------------|------|----------------------------------------------------|--|--|

| IMODE nSTALL                           |      | Description                                        |  |  |

| High-Z                                 | Low  | Current regulation at all times                    |  |  |

| High-Z                                 | High | Current regulation during t <sub>INRUSH</sub> only |  |  |

| High                                   | Х    | Current regulation at all times                    |  |  |

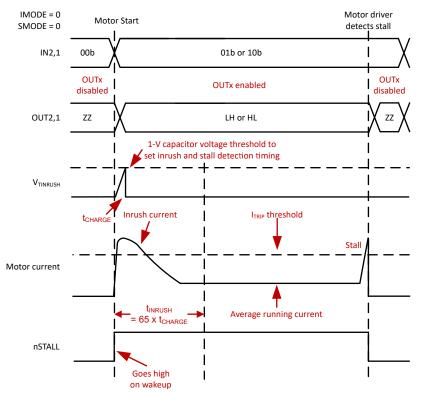

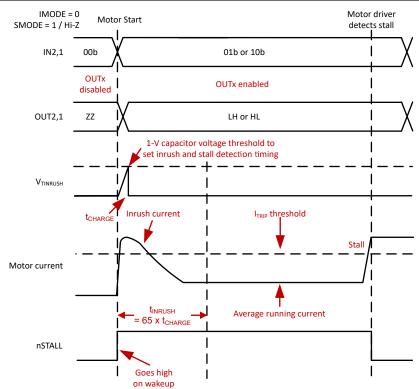

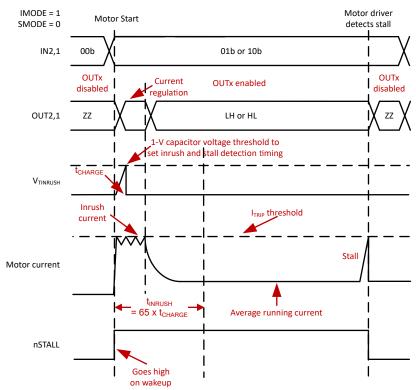

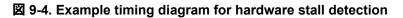

#### 8.4.3 Hardware Stall Detection

The DRV8213 integrates a hardware stall detection feature available in the RTE package variant. The principle of the stall detection scheme relies on the fact that motor current increases during stall conditions. The DRV8213 compares the voltage on the IPROPI pin to the voltage on the VREF pin (or 510 mV as applicable) to determine whether a stall condition has occurred. The following paragraphs describe how to configure the device pins for the desired stall detection response. For information on implementing stall detection in the DSG package variant, see  $t = 292 \times 9.2.1.3.1.2$ .

The nSTALL output is pulled low when stall is detected. The nSTALL pin status is latched at power-up. It requires a pull-up resistor to VCC and pulls low when a stall condition occurs. This pin can be connected to the nFAULT pin so both pins share the same pullup resistor. Combining nFAULT and nSTALL signals reduces board area needed by external components and number of input pins on the controller to detect fault and stall conditions. By having separate pullup resistors for the nSTALL and nFAULT, the microcontroller can detect a device fault separate from a stall condition using two input pins. Connecting nSTALL directly to GND disables stall detection.  $\frac{1}{5}$  8-5 summarizes the nSTALL pin settings.

| 表 8-5. nSTALL configu | ration |

|-----------------------|--------|

|-----------------------|--------|

| nSTALL                  | Description                                                                                                                             |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

|                         | Stall detection disabled. Float TINRUSH. If IMODE = High-Z, current regulation will occur at all times when $V_{IPROPI} \ge V_{VREF}$ . |

| Pull-up resistor to VCC | Stall detection enabled. Pin pulls low to indicate a stall.                                                                             |

The **IPROPI** pin provides the current sense signal for the hardware stall detection feature. The **VREF** pin sets the I<sub>TRIP</sub> current level at which a stall condition is detected. For DSG package, or RTE package and SMODE = High-Z, V<sub>VREF</sub> is internally fixed at 510 mV. When V<sub>IPROPI</sub>  $\ge$  V<sub>VREF</sub>, then I<sub>OUT</sub>  $\ge$  I<sub>TRIP</sub>, and the device will detect a stall condition if the t<sub>INRUSH</sub> time has passed. The IPROPI and VREF pins are also responsible for current regulation, as described in  $2723 \times 8.4.2$ .

The **TINRUSH** pin sets the amount of time that the stall detection scheme will ignore the inrush current during motor startup ( $t_{INRUSH}$ ). When the input pins transition from the state IN1 = IN2 = logic low to any other logic combination, the TINRUSH pin sources 10 µA of current into the capacitor ( $C_{INRUSH}$ ) connected from TINRUSH pin to ground. Once the voltage of the TINRUSH pin exceeds 1 V, the device discharges the capacitor in less than 100 µs. The capacitor charging time is internally multiplied by 65 to determine the  $t_{INRUSH}$  time. After  $t_{INRUSH}$  time expires, the DRV8213 indicates a stall condition the next time  $V_{IPROPI}$  is greater than or equal to  $V_{VREF}$ .

The following conditions cause the stall detection scheme to ignore the inrush current for t<sub>INRUSH</sub> time -

- Power-up of the DRV8213

- Recovering from faults

- After device exits from sleep mode

- After recovering from stall, as explained in 表 8-6

Use the following formula to select the CINRUSH capacitor -

$t_{INRUSH} = 6.5 \times 10^6 \times C_{INRUSH}$

The **SMODE** pin sets the device's response to a stall condition. The device decides that a stall condition has occurred when  $V_{IPROPI}$  is greater than or equal to  $V_{VREF}$  and the  $t_{INRUSH}$  time has elapsed. When SMODE = logic low, the outputs disable, and the nSTALL pin latches low. When SMODE = logic high, the nSTALL pin still latches low, but the outputs continue to drive current into the motor. When SMODE = Hi-z, the device uses

internal V<sub>VREF</sub> (510 mV) for stall detection, the nSTALL pin still latches low, but the outputs continue to drive current into the motor.  $\frac{1}{2}$  8-6 summarizes the SMODE pin settings.

| SMODE | Description                                                                                                                              | Recovery from Stall Condition                                                                                                                                                                                                                                      |

|-------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | Latched disable with indication: the OUTx pins disable and the nSTALL pin pulls low.                                                     | To recover from this condition, device needs to enter sleep mode. nSTALL will go high after IN1 and IN2 are both low for $t_{\text{SLEEP}}$ . After waking up from sleep mode, the stall detection scheme ignores the inrush current for $t_{\text{INRUSH}}$ time. |