BQ41790

# BQ41Z90 高集積 3~16 セル バッテリ残量計、IT-DZT アルゴリズムおよび ECC 認証機能付き

# 1 特長

- 3~16 直列セル アプリケーション向け、高集積バッテ リパック マネージャ

- 超低消費電力の 32 ビット RISC CPU

- 80V の耐性で、最大 16 個の直列セルを ADC 測

- ダイナミック Z-Track™ 残量測定アルゴリズムを搭 載した高精度 SoC と SoH

- 証明書ベースのセキュリティ保護されたフラッシュメ

- 2 つの独立した ADC を持つ高精度アナログ フロント

- 高精度の 18 ビット統合型、デルタ シグマ クーロン

- 入力変換とマルチプレクサを搭載した、高精度の 16 ビット デルタ シグマ

- 電流と電圧の同時サンプリングに対応

- 最大8個の外部サーミスタ測定と1つの内部温度 センサをサポート

- 高速なターンオン時間とターンオフ時間を持つ強力な ハイサイド NMOS FET 駆動

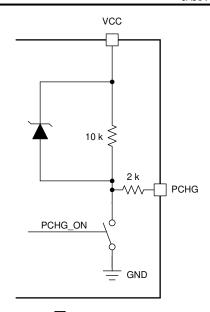

- 事前充電および事前放電 NMOS FET ドライバ向けの チャージ ポンプ サポート

- 個別のチャージャとシステムポートが付属している、取 り外し可能なバッテリの並列構成をサポート

- セルあたりのバイパスが最大 50mA のセル バランシン グをサポート

- 診断用の寿命データモニタとレコーダ

- 複数のホスト通信をサポート:

- I<sup>2</sup>C (最大 1MHz)

- SMBus 3.2 (最大 1MHz)

- 低静止電流動作のための複数の電力モード

- SHA-1、SHA-2、または EC-KCDSA 認証による堅牢 なバッテリ パックのセキュリティ

# 2 アプリケーション

- バッテリ バックアップ ユニット (BBU)

- 電動自転車/電動スクーター/軽電気自動車 (LEV)

- ハンドヘルド掃除機およびロボット掃除機

- 園芸用ロボットおよび電動工具

- ・ドローン

- 医療およびテスト用機器

- その他の産業用バッテリパック

## 3 概要

テキサス・インスツルメンツの BQ41Z90 は、リチウムイオ ン、LiFeP4、NiMH、およびリチウムポリマ バッテリ パック の 3~16 直列セルのためにフラッシュ プログラマブルな CPU、安全保護、楕円曲線暗号化 (ECC) 認証機能を提 供する、統合型のバッテリ パック ベースのバッテリ パック マネージャソリューションです。

BQ41Z90 バッテリ パック マネージャは SMBus v3.2 また は I<sup>2</sup>C 互換の インターフェイスで通信を行い、超低消費 電力かつ高速の32ビットプロセッサ、高精度アナログ測 定機能、内蔵フラッシュ メモリ、ペリフェラル IO アレイ、 NMOS 保護 FET 駆動、SHA-1、SHA-2、EC-KCDSA 認証レスポンダを組み合わせた、完全な高性能バッテリ管 理ソリューションです。

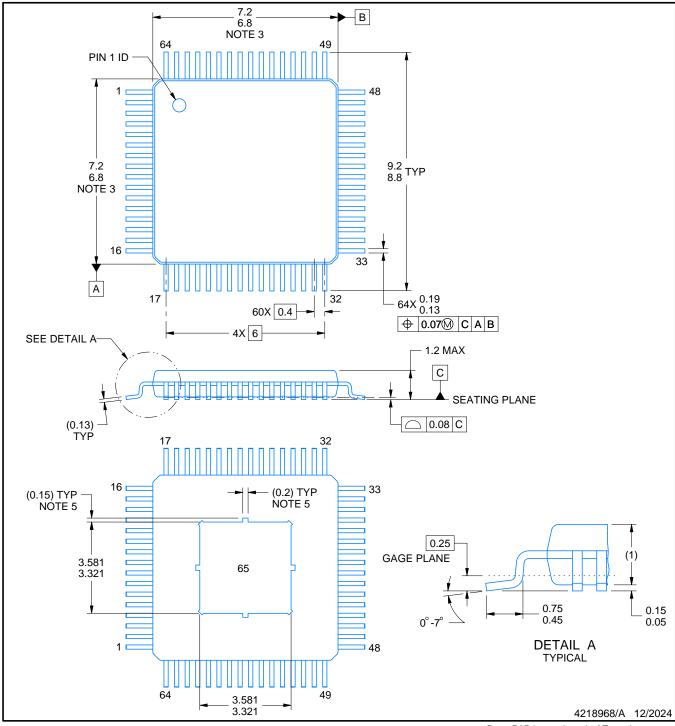

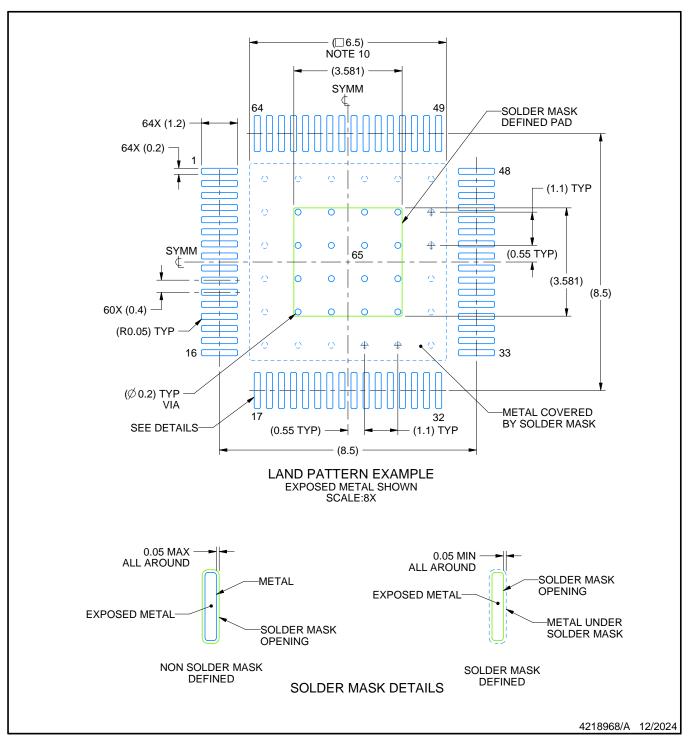

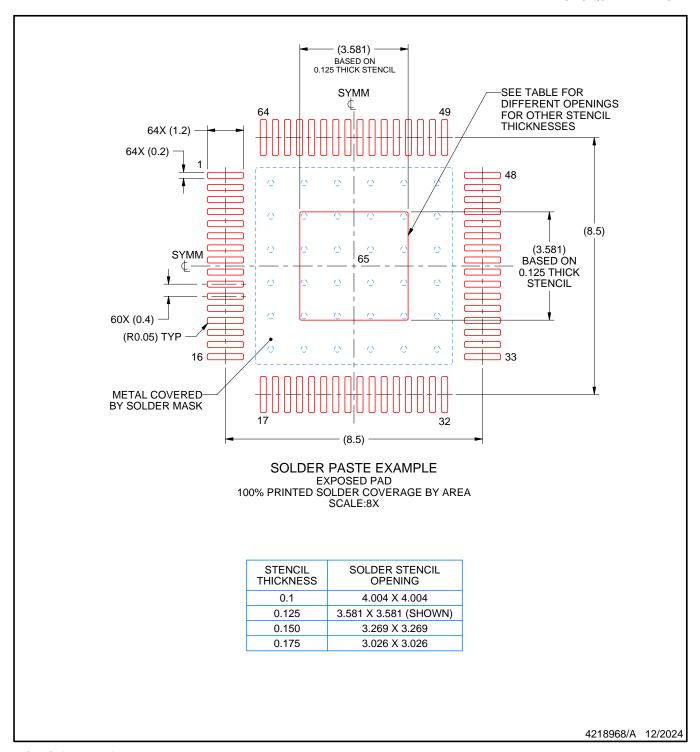

### パッケージ情報

| 部品番号        | パッケージ <sup>(1)</sup> | 本体サイズ (公称)      |  |  |  |

|-------------|----------------------|-----------------|--|--|--|

| BQ41Z90 RSN | PVP (64)             | 7.00mm × 7.00mm |  |  |  |

詳細については、Mechanical, Packaging, and Orderable Information を参照してください。

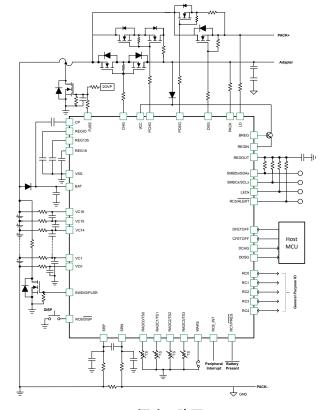

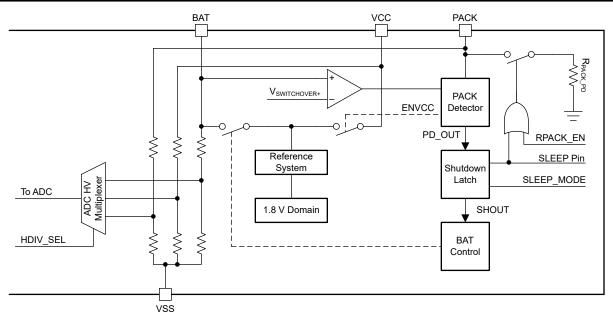

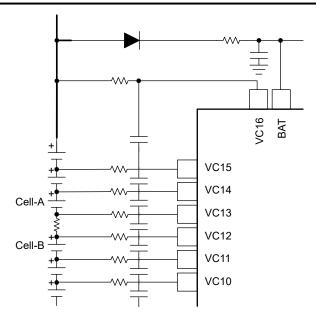

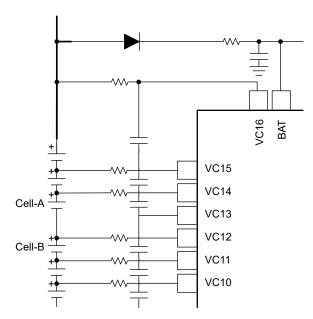

概略回路図

# **Table of Contents**

| <b>1</b> 特長 1                                | 6.17 F              |

|----------------------------------------------|---------------------|

| <b>2</b> アプリケーション1                           | 6.18 F              |

| 3 概要1                                        | 6.19 Ir             |

| 4 Pin Configuration and Functions:           | 6.20 I <sup>2</sup> |

| 5 Pin Equivalent Diagrams                    | 7 Detaile           |

| 6 Specifications10                           | 7.1 Ov              |

| 6.1 Absolute Maximum Ratings10               | 7.2 Fu              |

| 6.2 ESD Ratings11                            | 7.3 Fe              |

| 6.3 Recommended Operating Conditions11       | 8 Applic            |

| 6.4 Thermal Information12                    | 8.1 Ap              |

| 6.5 Supply Current12                         | 8.2 Ty              |

| 6.6 Power Selector                           | 9 Power             |

| 6.7 Current Wake Detector                    | 10 Device           |

| 6.8 General Purpose Input-Outputs13          | 10.1 <del>サ</del>   |

| 6.9 Aux REGOUT LDO                           | 10.2 D              |

| 6.10 LD Pin                                  | 10.3 ⅓              |

| 6.11 Shelf Timer                             | 10.4 🕏              |

| 6.12 Cell Balancing                          | 10.5 T              |

| 6.13 Comparator-Based Detections (SCOMP)17   | 10.6 郬              |

| 6.14 SCOMP Timing Requirements17             | 10.7 月              |

| 6.15 SCD Comparator                          | 11 Revis            |

| 6.16 High-side NFET Drivers (CHG and DSG and | 12 Mech             |

| PCHG and PDSG)18                             | Inform              |

| •                                            |                     |

| 6.17 FUSE Pin                           | 19              |

|-----------------------------------------|-----------------|

| 6.18 Flash Memory                       | 19              |

| 6.19 Interface I/O                      | 20              |

| 6.20 I <sup>2</sup> C Interface Timing  |                 |

| 7 Detailed Description                  | 23              |

| 7.1 Overview                            | <mark>23</mark> |

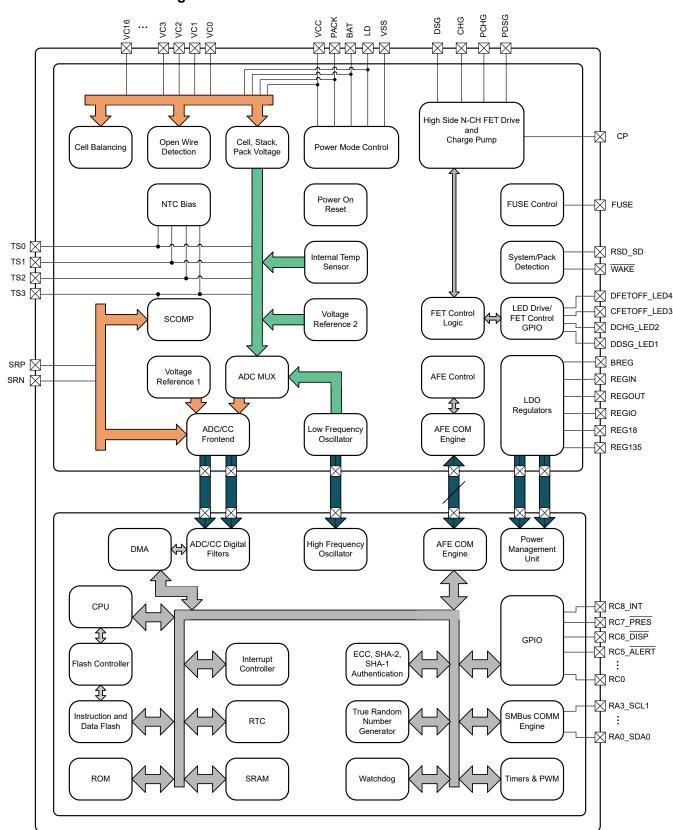

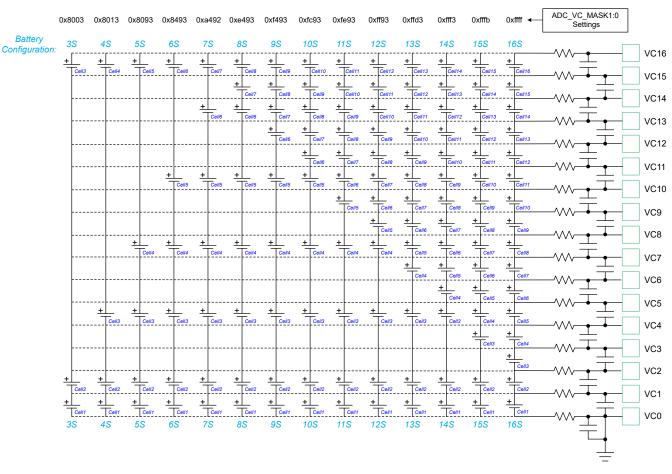

| 7.2 Functional Block Diagram            | <mark>24</mark> |

| 7.3 Feature Description                 | 25              |

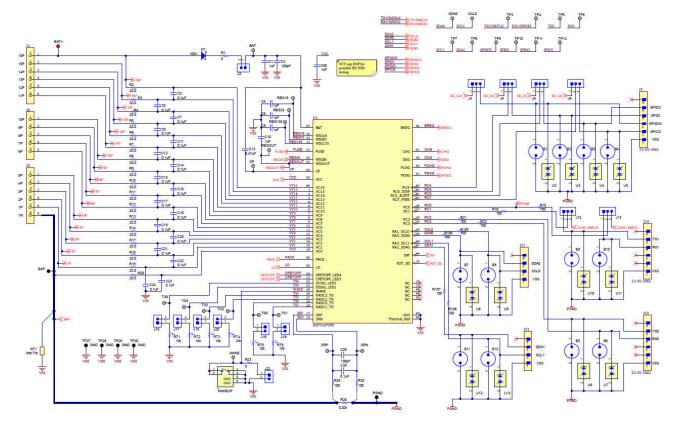

| 8 Application and Implementation        | 43              |

| 8.1 Application Information             | 43              |

| 8.2 Typical Applications                | 44              |

| 9 Power Supply Recommendations          | 46              |

| 10 Device and Documentation Support     | 46              |

| 10.1 サード・パーティ製品に関する免責事項                 | 46              |

| 10.2 Documentation Support              | 46              |

| 10.3ドキュメントの更新通知を受け取る方法                  | 46              |

| 10.4 サポート・リソース                          | 46              |

| 10.5 Trademarks                         | 46              |

| 10.6 静電気放電に関する注意事項                      | 47              |

| 10.7 用語集                                | 47              |

| 11 Revision History                     |                 |

| 12 Mechanical, Packaging, and Orderable |                 |

| Information                             | 10              |

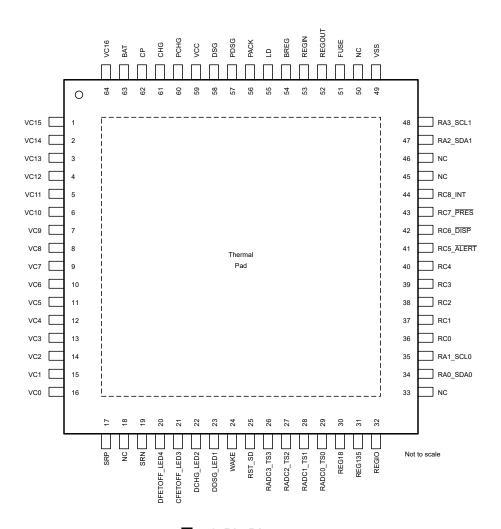

# 4 Pin Configuration and Functions:

図 4-1. Pin Diagram

表 4-1. Pin Functions

| PIN    |     | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                               |

|--------|-----|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO. | ITPE                | DESCRIPTION                                                                                                                                                                                                                               |

| VC15 1 |     | Al                  | Sense voltage input pin for the fifteenth cell from the bottom of the stack, balance current input for the fifteenth cell from the bottom of the stack, and return balance current for the sixteenth cell from the bottom of the stack    |

| VC14   | 2   | Al                  | Sense voltage input pin for the fourteenth cell from the bottom of the stack, balance current input for the fourteenth cell from the bottom of the stack, and return balance current for the fifteenth cell from the bottom of the stack  |

| VC13 3 |     | AI                  | Sense voltage input pin for the thirteenth cell from the bottom of the stack, balance current input for the thirteenth cell from the bottom of the stack, and return balance current for the fourteenth cell from the bottom of the stack |

| VC12   | 4   | Al                  | Sense voltage input pin for the twelveth cell from the bottom of the stack, balance current input for the twelveth cell from the bottom of the stack, and return balance current for the thirteenth cell from the bottom of the stack     |

| VC11   | 5   | Al                  | Sense voltage input pin for the eleventh cell from the bottom of the stack, balance current input for the eleventh cell from the bottom of the stack, and return balance current for the twelfth cell from the bottom of the stack        |

# 表 4-1. Pin Functions (続き)

| PIN          | 1                                                 | TYPE(1) | DESCRIPTION                                                                                                                                                                                                                                      |  |  |

|--------------|---------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME         | NO.                                               | TYPE    | DESCRIPTION                                                                                                                                                                                                                                      |  |  |

| VC10         | 6                                                 | Al      | Sense voltage input pin for the tenth cell from the bottom of the stack, balance current input for the tenth cell from the bottom of the stack, and return balance current for the eleventh cell from the bottom of the stack                    |  |  |

| VC9          | 7                                                 | Al      | Sense voltage input pin for the ninth cell from the bottom of the stack, balance current input for the ninth cell from the bottom of the stack, and return balance current for the tenth cell from the bottom of the stack                       |  |  |

| VC8          | 8                                                 | Al      | Sense voltage input pin for the eighth cell from the bottom of the stack, balance current input for the eighth cell from the bottom of the stack, and return balance current for the ninth cell from the bottom of the stack                     |  |  |

| VC7          | 9                                                 | Al      | Sense voltage input pin for the seventh cell from the bottom of the stack, balance current input for the seventh cell from the bottom of the stack, and return balance current for the eighth cell from the bottom of the stack                  |  |  |

| VC6          | 10                                                | Al      | Sense voltage input pin for the sixth cell from the bottom of the stack, balance current input for the sixth cell from the bottom of the stack, and return balance current for the seventh cell from the bottom of the stack                     |  |  |

| VC5          | 11                                                | Al      | Sense voltage input pin for the fifth cell from the bottom of the stack, balance current input for the fifth cell from the bottom of the stack, and return balance current for the sixth cell from the bottom of the stack                       |  |  |

| VC4          | 12                                                | Al      | Sense voltage input pin for the fourth cell from the bottom of the stack, balance current input for the fourth cell from the bottom of the stack, and return balance current for the fifth cell from the bottom of the stack                     |  |  |

| VC3          | 13                                                | Al      | Sense voltage input pin for the third cell from the bottom of the stack, balance current input for the third cell from the bottom of the stack, and return balance current for the fourth cell from the bottom of the stack                      |  |  |

| VC2          | 14                                                | Al      | Sense voltage input pin for the second cell from the bottom of the stack, balance current input for the second cell from the bottom of the stack, and return balance current for the third cell from the bottom of the stack                     |  |  |

| VC1          | 15                                                | Al      | Sense voltage input pin for the first cell from the bottom of the stack, balance current input for the first cell from the bottom of the stack, and return balance current for the second cell from the bottom of the stack                      |  |  |

| VC0          | 16                                                | Al      | Sense voltage input pin for the negative terminal of the first cell from the bottom of the stack, and return balance current for the first cell from the bottom of the stack                                                                     |  |  |

| SRP          | 17                                                | Al      | Analog input pin connected to the internal coulomb counter peripheral for integrating a small voltage between SRP and SRN, where SRP is the top of the sense resistor. A charging current generates a positive voltage at SRP relative to SRN    |  |  |

| NC           | 18                                                | NC      | This pin is not connected to silicon                                                                                                                                                                                                             |  |  |

| SRN          | 19                                                | Al      | Analog input pin connected to the internal coulomb counter peripheral for integrating a small voltage between SRP and SRN, where SRN is the bottom of the sense resistor. A charging current generates a positive voltage at SRP relative to SRN |  |  |

| DFETOFF_LED4 | 20                                                | I/O     | DFETOFF input to keep the DFET off as long as this pin is asserted, or LED4 open drain output pin with current sink.                                                                                                                             |  |  |

| CFETOFF_LED3 | 21                                                | I/O     | CFETOFF input to keep the CFET off as long as this pin is asserted, or LED3 open drain output pin with current sink,                                                                                                                             |  |  |

| DCHG_LED2    | 22                                                | 0       | DCHG output to indicate protection faults which should cause CFET to be off, or LED2 open drain output pin with current sink.                                                                                                                    |  |  |

| DDSG_LED1    | 23                                                | 0       | DDSG output to indicate protection faults which should cause DFET to be off, or LED1 open drain output pin with current sink.                                                                                                                    |  |  |

| WAKE         | 24                                                | Al      | Push-down button input to wake up the device from Shutdown or Hibernate mode.                                                                                                                                                                    |  |  |

| RST_SD       | 25                                                | Al      | Input pin for reset or shutdown                                                                                                                                                                                                                  |  |  |

| RADC3_TS3    | TS3 26 AI General-purpose ADC or thermistor input |         |                                                                                                                                                                                                                                                  |  |  |

| RADC2_TS2    | 27                                                | Al      | General-purpose ADC or thermistor input                                                                                                                                                                                                          |  |  |

| RADC1_TS1    | 28                                                | Al      | General-purpose ADC or thermistor input                                                                                                                                                                                                          |  |  |

| RADC0_TS0    | 29                                                | Al      | General-purpose ADC or thermistor input                                                                                                                                                                                                          |  |  |

4

English Data Sheet: SLUSFQ1

# 表 4-1. Pin Functions (続き)

| PI        | 教 4-1. PIII FUNCTIONS (税さ) |                     |                                                                                                                                                            |  |  |  |

|-----------|----------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME      | NO.                        | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                |  |  |  |

| REG18     | 30                         | PO                  | Internal 1.8V LDO Output Cap Connection (only for internal use)                                                                                            |  |  |  |

| REG135    | 31                         | PO                  | Internal 1.35V LDO Output Cap Connection (only for internal use)                                                                                           |  |  |  |

| REGIO     | 32                         | PI                  | Internal 3.3V/1.8V LDO Output Cap Connection (only for internal use)                                                                                       |  |  |  |

| NC        | 33                         | NC                  | This pin is not connected to silicon                                                                                                                       |  |  |  |

| RA0_SDA0  | 34                         | I/O                 | General-purpose input with or without INT, or multifunction open-drain output, can be configured as SDA, SCL, SMBD, or SMBC                                |  |  |  |

| RA1_SCL0  | 35                         | I/O                 | General-purpose input with or without INT, or multifunction open-drain output, can be configured as SDA, SCL, SMBD, or SMBC                                |  |  |  |

| RC0       | 36                         | I/O                 | General-purpose digital input with or without INT, or multifunction push-pull output.                                                                      |  |  |  |

| RC1       | 37                         | I/O                 | General-purpose digital input with or without INT, or multifunction push-pull output.                                                                      |  |  |  |

| RC2       | 38                         | I/O                 | General-purpose digital input with or without INT, or multifunction push-pull output.                                                                      |  |  |  |

| RC3       | 39                         | I/O                 | General-purpose digital input with or without INT, or multifunction push-pull output.                                                                      |  |  |  |

| RC4       | 40                         | I/O                 | General-purpose digital input with or without INT, or multifunction push-pull output.                                                                      |  |  |  |

| RC5_ALERT | 41                         | I/O                 | General-purpose digital input with or without INT, or multifunction push-pull output.  Defaults to ALERT output to signal general fault detection.         |  |  |  |

| RC6_DISP  | 42                         | I/O                 | General-purpose digital input with or without INT, or multifunction push-pull output.  Defaults to DISPbottom control output signal.                       |  |  |  |

| RC7_PRES  | 43                         | I/O                 | General-purpose digital input with or without INT, or multifunction push-pull output.  Defaults to PRES for battery presence input signal.                 |  |  |  |

| RC8_INT   | 44                         | I/O                 | General-purpose digital input with or without INT, or multifunction push-pull output                                                                       |  |  |  |

| NC        | 45                         | NC                  | This pin is not connected to silicon                                                                                                                       |  |  |  |

| NC        | 46                         | NC                  | This pin is not connected to silicon                                                                                                                       |  |  |  |

| RA2_SDA1  | 47                         | Ю                   | General-purpose input or multifunction open-drain output, can be configured as SDA, SCL, SMBD, or SMBC                                                     |  |  |  |

| RA3_SCL1  | 48                         | Ю                   | General-purpose input or multifunction open-drain output, can be configured as SDA, SCL, SMBD, or SMBC                                                     |  |  |  |

| VSS       | 49                         | Р                   | Device ground                                                                                                                                              |  |  |  |

| NC        | 50                         | NC                  | This pin is not connected to silicon                                                                                                                       |  |  |  |

| FUSE      | 51                         | IO,A                | Fuse sense and drive                                                                                                                                       |  |  |  |

| REGOUT    | 52                         | AO                  | External LDO output, which can be programmed for 2 V, 2.5 V, 3.0 V, 3.3 V, or 5.0 V                                                                        |  |  |  |

| REGIN     | 53                         | Al                  | Input pin for external LDO REGOUT                                                                                                                          |  |  |  |

| BREG      | 54                         | AO                  | Base control signal for external regulatory transistor                                                                                                     |  |  |  |

| LD        | 55                         | Al                  | Load detect pin                                                                                                                                            |  |  |  |

| PACK      | 56                         | Al                  | Pack sense input pin                                                                                                                                       |  |  |  |

| PDSG      | 57                         | AO                  | Pre-discharge control pin                                                                                                                                  |  |  |  |

| DSG       | 58                         | AO                  | Discharge control pin                                                                                                                                      |  |  |  |

| VCC       | 59                         | Р                   | Secondary power supply input                                                                                                                               |  |  |  |

| PCHG      | 60                         | AO                  | Pre-charge control pin                                                                                                                                     |  |  |  |

| CHG       | 61                         | AO                  | Charge control pin                                                                                                                                         |  |  |  |

| СР        | 62                         | AO                  | Charge pump capacitor                                                                                                                                      |  |  |  |

| BAT       | 63                         | Р                   | Primary power supply input from battery                                                                                                                    |  |  |  |

| VC16      | 64                         | Al                  | Sense voltage input pin for the sixteenth cell from the bottom of the stack, and balance current input for the sixteenth cell from the bottom of the stack |  |  |  |

<sup>(1)</sup> I = Input, O = Output, I/O = Input or Output, AI = Analog Input, AO = Analog Output, G = Ground, P = Power.

# **5 Pin Equivalent Diagrams**

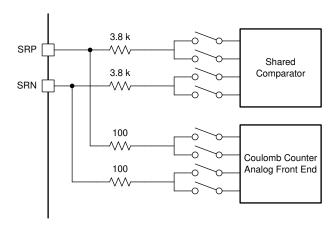

図 5-1. SRx Pins

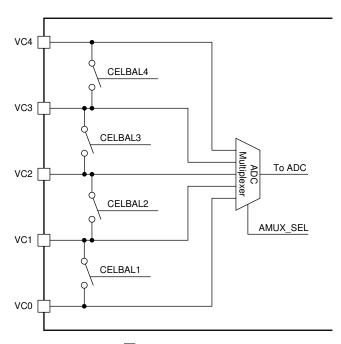

図 5-2. VCx Pins

図 5-3. Power Supply Pins

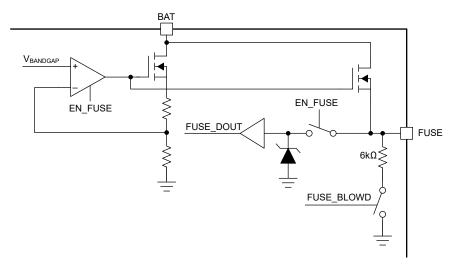

図 5-4. Fuse Pin

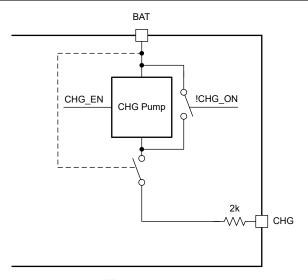

図 5-5. CHG Pin

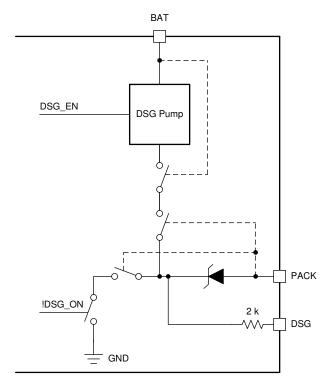

図 5-6. DSG Pin

図 5-7. PCHG Pin

# 6 Specifications

# **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1)

|                      | PARAMETER                                            | PINS                                                                                  | MIN                                                          | MAX                                                 | UNIT |

|----------------------|------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------|------|

| V <sub>DD</sub>      | Supply voltage range                                 | BAT, VCC                                                                              | VSS-0.3                                                      | VSS+85                                              | V    |

|                      |                                                      | PACK, LD                                                                              | VSS-0.3                                                      | VSS+85                                              | V    |

|                      |                                                      | FUSE <sup>(2)</sup>                                                                   | VSS-0.3                                                      | minimum<br>of VSS+20<br>or<br>V <sub>BAT</sub> +0.3 | V    |

|                      |                                                      | REGIN                                                                                 | VSS-0.3                                                      | minimum<br>of VSS+6<br>or<br>V <sub>BREG</sub> +0.3 | V    |

|                      |                                                      | RAx (SDL0, SCLK0, SDL1, SCLK1)                                                        | VSS-0.3                                                      | VSS+6                                               | V    |

| $V_{IN}$             | Voltage on Input pins                                | RADCx, TSx, LEDx, DFETOFF, CFETOFF, WAKE, RST_SD                                      | VSS-0.3                                                      | VSS+3.6                                             | V    |

|                      |                                                      | RCx                                                                                   | VSS-0.3                                                      | VSS+3.6                                             | V    |

|                      |                                                      | SRP, SRN                                                                              | VSS-0.3                                                      | V <sub>REG18</sub> + 0.3                            | V    |

|                      |                                                      | VC1, VC2, VC3, VC4, VC5, VC6, VC7, VC8, VC9, VC10, VC11, VC12, VC13, VC14, VC15, VC16 | maximum<br>of VSS-0.3<br>and VC0-<br>0.3                     | VSS+85                                              | V    |

|                      |                                                      | VC0                                                                                   | VSS-0.3                                                      | VSS+6                                               | V    |

|                      |                                                      | СР                                                                                    | V <sub>BAT</sub> -0.3                                        | minimum<br>of VSS+85<br>or<br>VBAT+15               | V    |

|                      |                                                      | CHG, DSG                                                                              | VSS-0.3                                                      | VSS+85                                              | V    |

| V <sub>OUT</sub>     | Voltage on Output pins                               | PCHG, PDSG                                                                            | maximum<br>of V <sub>BAT</sub> –10<br>or V <sub>LD</sub> –10 | VSS+85                                              | V    |

|                      |                                                      | REG135                                                                                | VSS-0.3                                                      | VSS+1.45                                            | V    |

|                      |                                                      | REG18                                                                                 | VSS-0.3                                                      | VSS+2                                               | V    |

|                      |                                                      | REGIO                                                                                 | VSS-0.3                                                      | VSS+3.5                                             | V    |

|                      |                                                      | REGOUT                                                                                | VSS-0.3                                                      | VSS+5.5                                             | V    |

| I <sub>BALANCE</sub> | Maximum cell balancing current through a single cell | VC0 - VC16                                                                            |                                                              | 100                                                 | mA   |

| I <sub>SS</sub>      | Maximum VSS current                                  |                                                                                       |                                                              | 75                                                  | mA   |

| T <sub>J</sub>       | Junction temperature (operational)                   |                                                                                       | -40                                                          | 125                                                 | °C   |

| T <sub>STG</sub>     | Storage temperature                                  |                                                                                       | -55                                                          | 150                                                 | °C   |

|                      |                                                      | I .                                                                                   |                                                              |                                                     |      |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

(2) The current allowed to flow into the FUSE pin must be limited (such as by using external series resistance) to 2 mA or less.

# 6.2 ESD Ratings

|                  |                         |                                                                                     | VALUE | UNIT |

|------------------|-------------------------|-------------------------------------------------------------------------------------|-------|------|

| V                | Electrostatio discharge | Human body model (HBM), per ANSI/<br>ESDA/JEDEC JS-001, all pins <sup>(1)</sup>     | ±1000 | V    |

| V <sub>ESD</sub> | Electrostatic discharge | Charged device model (CDM), per ANSI/<br>ESDA/JEDEC JS-002, all pins <sup>(2)</sup> | ±500  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **6.3 Recommended Operating Conditions**

Typical values stated where  $T_A$  = 25°C and  $V_{BAT}$  = 59.2 V, min/max values stated where  $T_A$  = -40°C to 105°C and  $V_{BAT}$  = 5 V to 80 V (unless otherwise noted)<sup>(1)</sup>

| `                      | PARAMETER                     | TEST CONDITIONS                            | MIN                       | NOM MAX                  | UNIT |

|------------------------|-------------------------------|--------------------------------------------|---------------------------|--------------------------|------|

| $V_{DD}$               | Supply voltage                | BAT pin, I <sub>REG18</sub> ≤ 22mA         | V <sub>SWITCHOVE</sub> R- | 80                       | V    |

|                        |                               | VCC pin                                    | 5                         | 80                       | V    |

|                        |                               | PACK, LD                                   | 0                         | 80                       | V    |

|                        |                               | RAx (SDL0, SCLK0, SDL1, SCLK1)             | 0                         | 5.5                      | V    |

|                        |                               | RCx                                        | 0                         | $V_{REGIO}$              | V    |

|                        |                               | RADCx, TSx, LEDx, DFETOFF, CFETOFF, RST_SD | 0                         | V <sub>REG18</sub> + 0.3 | V    |

|                        |                               | SRP, SRN pins                              | -0.25                     | 0.5                      | V    |

|                        |                               | VC16                                       | VC <sub>15</sub> -0.2     | VC <sub>15</sub> +5      | V    |

|                        |                               | VC15                                       | VC <sub>14</sub> -0.2     | VC <sub>14</sub> +5      | V    |

|                        |                               | VC14                                       | VC <sub>13</sub> -0.2     | VC <sub>13</sub> +5      | V    |

|                        |                               | VC13                                       | VC <sub>12</sub> -0.2     | VC <sub>12</sub> +5      | V    |

|                        |                               | VC12                                       | VC <sub>11</sub> -0.2     | VC <sub>11</sub> +5      | V    |

| V <sub>IN</sub>        | Input voltage range           | VC11                                       | VC <sub>10</sub> 02       | VC <sub>10</sub> +5      | V    |

|                        |                               | VC10                                       | VC <sub>9</sub> 02        | VC <sub>9</sub> +5       | V    |

|                        |                               | VC9                                        | VC <sub>8</sub> -0.2      | VC <sub>8</sub> +5       | V    |

|                        |                               | VC8                                        | VC <sub>7</sub> -0.2      | VC <sub>7</sub> +5       | V    |

|                        |                               | VC7                                        | VC <sub>6</sub> -0.2      | VC <sub>6</sub> +5       | V    |

|                        |                               | VC6                                        | VC <sub>5</sub> -0.2      | VC <sub>5</sub> +5       | V    |

|                        |                               | VC5                                        | VC <sub>4</sub> -0.2      | VC <sub>4</sub> +5       | V    |

|                        |                               | VC4                                        | VC <sub>3</sub> -0.2      | VC <sub>3</sub> +5       | V    |

|                        |                               | VC3                                        | VC <sub>2</sub> -0.2      | VC <sub>2</sub> +5       | V    |

|                        |                               | VC2                                        | VC <sub>1</sub> -0.2      | VC <sub>1</sub> +5       | V    |

|                        |                               | VC1                                        | VC <sub>0</sub> 02        | VC <sub>0</sub> +5       | V    |

|                        |                               | VC0                                        | -0.2                      | 0.5                      | V    |

| V <sub>OUT</sub>       | Output voltage range          | CHG, DSG, PCHG, PDSG                       | 0                         | 80                       | V    |

| V <sub>OUT</sub>       | Output voltage range          | FUSE                                       | 0                         | 28                       | V    |

| C <sub>BAT</sub> (1)   | BAT external capacitor        | Derated to 2.2V, 100V capacitor            | 0.47                      | 1                        | μF   |

| C <sub>VCC</sub> (1)   | VCC external capacitor        | Derated to 2.2V, 100V capacitor            | 0.1                       | 0.47                     | μF   |

| C <sub>REGIO</sub> (1  | REGIO exteranl capacitor      | Derated to 3.3 V, 10V capacitor            | 0.47                      | 1 2.2                    | μF   |

| C <sub>REG18</sub> (1) | REG18 external capacitor      | Derated to 1.8 V, 10V capacitor            | 0.47                      | 1 2.2                    | μF   |

| C <sub>REG135</sub> (  | 1) REG135 external capacitor  | Derated to 1.35 V, 10V capacitor           | 0.47                      | 1 2.2                    | μF   |

| Ср                     | Charge pump capacitor         | Derated to 2.2V, 100V capacitor            | 100                       | 470 2200                 | nF   |

| CC                     | External cell input capacitor | Derated to 2.2V, 100V capacitor            |                           | 100                      | nF   |

Typical values stated where  $T_A = 25^{\circ}\text{C}$  and  $V_{BAT} = 59.2 \text{ V}$ , min/max values stated where  $T_A = -40^{\circ}\text{C}$  to  $105^{\circ}\text{C}$  and  $V_{BAT} = 5 \text{ V}$  to 80 V (unless otherwise noted)<sup>(1)</sup>

| PARAMETER                      |                                          | TEST CONDITIONS                        | MIN | NOM | MAX | UNIT |

|--------------------------------|------------------------------------------|----------------------------------------|-----|-----|-----|------|

| R <sub>C</sub>                 | External cell measurement input resistor |                                        | 20  |     | 100 | Ω    |

| R <sub>PACK</sub> (1)          | PACK series external resistor            | For lowest Startup voltage             | 2   | 10  | 12  | kΩ   |

| I <sub>SS</sub> <sup>(1)</sup> | Maximum current through Vss pin          | Includes LDOs, GPIO and Cell balancing |     |     | 200 | mA   |

| T <sub>A</sub> (2)             | Operating free-air temperature           |                                        | -40 |     | 105 | °C   |

- Specified by design. Not production tested.

- (2) Additional cooling strategies may be necessary to keep junction temperature at recommended limits.

## **6.4 Thermal Information**

Typical values stated where  $T_A = 25^{\circ}\text{C}$  and  $V_{BAT} = 59.2 \text{ V}$ , min/max values stated where  $T_A = -40^{\circ}\text{C}$  to 105°C and  $V_{BAT} = 5 \text{ V}$  to 80 V (unless otherwise noted)

|                        | THERMAL METRIC(1)                            | PVP (QFP) | UNIT |

|------------------------|----------------------------------------------|-----------|------|

|                        | THERWIAL METRIC                              | 64 Pins   | ONII |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 29.4      | °C/W |

| R <sub>0JC(top)</sub>  | Junction-to-case (top) thermal resistance    | 16.7      | °C/W |

| R <sub>eJB</sub>       | Junction-to-board thermal resistance         | 12.6      | °C/W |

| $\Psi_{JT}$            | Junction-to-top characterization parameter   | 12.5      | °C/W |

| $\Psi_{JB}$            | Junction-to-board characterization parameter | 0.9       | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 2.3       | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

# 6.5 Supply Current

Typical values stated where  $T_A = 25^{\circ}C$  and  $V_{BAT} = 59.2$  V, min/max values stated where  $T_A = -40^{\circ}C$  to  $105^{\circ}C$  and  $V_{BAT} = 5$  V to 80 V (unless otherwise noted)

|                         | PARAMETER       | TEST CONDITIONS                                                                                                                  | MIN | TYP | MAX | UNIT |

|-------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| I <sub>ACTIVE</sub> (1) | ACTIVE mode     | CPU active, ADC and CC On, Protections On, CHG and DSG FETs On, No Communication                                                 |     | 500 |     | μА   |

| I <sub>SLEEP</sub> (2)  | SLEEP mode      | CPU halted, ADC and CC On, Protections On, CHG and DSG FETs On, RAM in retension, No Flash read/write/erase, No Communication    |     | 250 |     | μΑ   |

| I <sub>DEEPSLEEP</sub>  | DEEP SLEEP mode | CPU halted, ADC and CC Off, Protections Off, CHG and DSG FETs Off, RAM in retension, No Flash read/write/erase, No Communication |     | 80  |     | μΑ   |

| I <sub>HIBERNATE</sub>  | HIBERNATE mode  | Everything powered OFF execpt PACK and WAKE detection functions                                                                  |     | 30  |     | μА   |

| I <sub>SHELF</sub>      | SHELF mode      | Everything powered OFF except PACK detection function and Low Power Timer                                                        |     | 3   | 5   | μА   |

| I <sub>SHUT</sub>       | SHUTDOWN mode   | Everything powered OFF except PACK detection function. External Pullup on GPIO pins not powered                                  |     | 0.6 | 2   | μΑ   |

- (1) Assuming device is running typical firmware settings under ACTIVE mode, which manages CPU and ADC/CC duty cycle to <4%

- (2) Assuming device is running typical firmware settings under SLEEP mode, which manages CPU and CC duty cycle to <1%

#### 6.6 Power Selector

Typical values stated where  $T_A = 25^{\circ}C$  and  $V_{BAT} = 59.2$  V, min/max values stated where  $T_A = -40^{\circ}C$  to  $105^{\circ}C$  and  $V_{BAT} = 5$  V to 80 V (unless otherwise noted)

| PARAMETER      | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|----------------|-----------------|-----|-----|-----|------|

| Power Selector |                 |     |     |     |      |

Copyright © 2025 Texas Instruments Incorporated English Data Sheet: SLUSFQ1

|                                     | PARAMETER                                                                                       | TEST CONDITIONS                                                | MIN  | TYP  | MAX  | UNIT |

|-------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------|------|------|------|

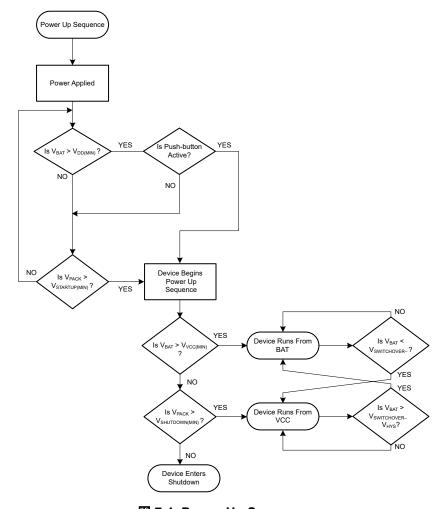

| V <sub>STARTUP</sub>                | Startup Voltage at PACK                                                                         | V <sub>PACK</sub> > V <sub>STARTUP</sub> for 1 ms              | 3.5  | 4.5  | 5.5  | V    |

| V <sub>SWITCHOVER</sub> -           | BAT to VCC switchover voltage                                                                   | V <sub>BAT</sub> < V <sub>SWITCHOVER</sub> -                   | 4.9  | 4.95 | 5.05 | V    |

| V <sub>SWITCHOVER</sub>             | VCC to BAT switchover voltage                                                                   | V <sub>BAT</sub> > V <sub>SWITCHOVER-</sub> + V <sub>HYS</sub> | 5.85 | 6.1  | 6.5  | V    |

| V <sub>HYS</sub>                    | Switchover hysteresis voltage                                                                   | V <sub>SWITCHOVER+</sub> - V <sub>SWITCHOVER-</sub>            |      | 1.02 |      | V    |

| T <sub>SD_ALERT+</sub>              | Thermal shutdown alert temperature rising                                                       |                                                                |      | 120  | 135  | °C   |

| T <sub>SD_ALERT</sub>               | Thermal shutdown alert temperature falling                                                      | Exit from RESET, REG135 enabled                                | 100  | 102  |      | °C   |

| T <sub>SD+</sub>                    | Thermal shutdown temperature rising                                                             |                                                                |      | 140  | 148  | °C   |

| T <sub>SD-</sub>                    | Thermal shutdown temperature falling                                                            | REG18 Enabled                                                  | 122  | 130  |      | °C   |

| 1                                   | Input laglage gurrent                                                                           | BAT pin, BAT = 0 V, VCC = 60 V,<br>PACK = 60 V                 |      |      | 1    | μΑ   |

| I <sub>LKG</sub>                    | Input leakage current                                                                           | PACK pin, BAT = 60V, VCC = 0 V,<br>PACK = 0 V                  |      |      | 1    | μΑ   |

| R <sub>PACK_PD</sub>                | Internal pulldown resistance                                                                    | PACK pin                                                       | 30   | 40   | 50   | kΩ   |

| Power On Re                         | set                                                                                             |                                                                |      |      |      |      |

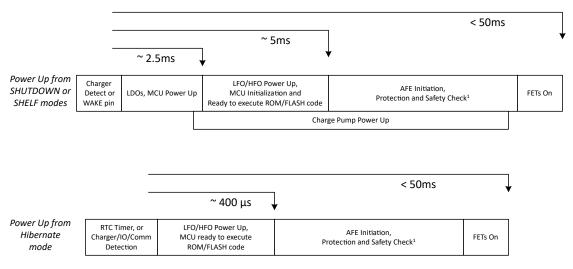

| t <sub>RST_POR</sub> (1)            | Power on reset time: From application of valid input voltage to release of POR for the MCU      |                                                                |      | 2.5  | 4.0  | ms   |

| t <sub>RST_ROM</sub> <sup>(1)</sup> | Power on reset time: From application of valid input voltage to CPU ready to execute ROM code   |                                                                |      | 5    | 10   | ms   |

| t <sub>RST_EXE</sub> (1)            | Power on reset time: From application of valid input voltage to CPU ready to execute flash code | Not including CRC of flash array performed by ROM              |      | 5    | 10   | ms   |

|                                     |                                                                                                 |                                                                |      |      |      |      |

<sup>(1)</sup> Specified by design. Not production tested.

### **6.7 Current Wake Detector**

Typical values stated where  $T_A$  = 25°C and  $V_{BAT}$  = 59.2 V, min/max values stated where  $T_A$  = -40°C to 105°C and  $V_{BAT}$  = 5 V to 80 V (unless otherwise noted)

|                                              | PARAMETER                      | TEST CONDITIONS                                                                | MIN TYP                         | MAX | UNIT |

|----------------------------------------------|--------------------------------|--------------------------------------------------------------------------------|---------------------------------|-----|------|

| V <sub>WAKE_THR</sub>                        | Wakeup voltage threshold       | Nominal settings, threshold based on V <sub>SRP</sub> - V <sub>SRN</sub>       | ±0.5 to<br>±7.5 in<br>0.5 steps |     | mV   |

| V <sub>WAKE_THR_E</sub><br>RR <sup>(1)</sup> | Wakeup voltage threshold error | T <sub>A</sub> = 25°C, V <sub>WAKE</sub> = V <sub>SRP</sub> – V <sub>SRN</sub> | -350                            | 350 | μV   |

<sup>(1)</sup> Specified by design. Not production tested.

# **6.8 General Purpose Input-Outputs**

Typical values stated where  $T_A = 25^{\circ}C$  and  $V_{BAT} = 59.2$  V, min/max values stated where  $T_A = -40^{\circ}C$  to 85°C and  $V_{BAT} = 5$  V to 80 V (unless otherwise noted)

| ·                              | PARAMETER                  | TEST CONDITIONS               | MIN                         | TYP MAX             | UNIT |

|--------------------------------|----------------------------|-------------------------------|-----------------------------|---------------------|------|

| Low Volta                      | age GPIO (RA and RC Ports) |                               |                             |                     |      |

| V <sub>IN</sub>                | Input voltage range        | RA03 (SDA0, SCL0, SDA1, SCL1) | -0.2                        | 5.5                 | V    |

| V <sub>IN</sub>                | Input voltage range        | RC08                          | -0.2                        | V <sub>REG3.3</sub> | V    |

| V <sub>IH</sub> (2)            | High-level input voltage   | RA03 (SDA0, SCL0, SDA1, SCL1) | 0.7 x<br>V <sub>REGIO</sub> |                     | V    |

| V <sub>IH</sub> <sup>(2)</sup> | High-level input voltage   | RC08                          | 0.7 x<br>V <sub>REGIO</sub> |                     | V    |

DVANCE INFORMATION

|                                 | PARAMETER                            | TEST CONDITIONS                                                                                           | MIN                         | TYP | MAX                         | UNIT |

|---------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------|-----|-----------------------------|------|

| V <sub>IL</sub> (2)             | Low-level input voltage              | RA03 (SDA0, SCL0, SDA1, SCL1)                                                                             |                             |     | 0.3 x<br>V <sub>REGIO</sub> | V    |

| V <sub>IL</sub> (2)             | Low-level input voltage              | RC08                                                                                                      |                             |     | 0.3 x<br>V <sub>REGIO</sub> | V    |

| V <sub>IOHYS</sub> (1)          | Hysteresis of Input                  | RA03, RC08                                                                                                | 75                          |     |                             | mV   |

| V <sub>OH</sub> <sup>(2)</sup>  | Output voltage high                  | RC08 : I <sub>OH</sub> = -450 μA                                                                          | 0.7*V <sub>REGI</sub>       |     |                             | V    |

| V <sub>OL</sub>                 | Output voltage low                   | RA03 (SDA0, SCL0, SDA1, SCL1):<br>I <sub>OH</sub> = 3mA                                                   |                             |     | 0.35                        | V    |

| V <sub>OL</sub>                 | Output voltage low                   | RC08 : I <sub>OH</sub> = 1mA                                                                              |                             |     | 0.35                        | V    |

| t <sub>PWMRISE</sub>            | PWM Output Rise Time                 | RC0, RC1: C <sub>L</sub> = 100 pF, Q <sub>tot</sub> = 1 nC,<br>0% to 90% of Gate Drive,<br>PWM_SYNC = 1   |                             |     | 6                           | μs   |

| t <sub>PWMFALL</sub>            | PWM Output Fall Time                 | RC0, RC1: C <sub>L</sub> = 100 pF, Q <sub>tot</sub> = 1 nC,<br>100% to 10% of Gate Drive,<br>PWM_SYNC = 1 |                             |     | 6                           | μs   |

| R <sub>BUSPD</sub>              | Internal weak pull down resistance   | RA03, Always ON                                                                                           | 3.2                         | 4   | 4.8                         | МΩ   |

| R <sub>WKPD</sub>               | Internal pull down resistance        | RA03 (SDA0, SCL0, SDA1, SCL1)                                                                             | 35                          | 40  | 50                          | kΩ   |

| R <sub>WKPD</sub>               | Internal pull down resistance        | RC08                                                                                                      | 15                          | 20  | 30                          | kΩ   |

| R <sub>WKPU</sub>               | Internal pull up resistance          | RC08                                                                                                      | 180                         | 100 | 120                         | kΩ   |

| C <sub>I</sub> <sup>(1)</sup>   | Input capacitance                    | RA03 (SDA0, SCL0, SDA1, SCL1)                                                                             |                             | 1.8 |                             | pF   |

| C <sub>I</sub> (1)              | Input capacitance                    | RC08                                                                                                      |                             | 1.5 |                             | pF   |

| I <sub>lkg</sub> <sup>(1)</sup> | Input leakage current                | RA03, including always on R <sub>BUSPD</sub> pulldown                                                     |                             | 0.5 | 2                           | μA   |

| I <sub>lkg</sub> (1)            | Input leakage current                | RC08                                                                                                      |                             | 1   | 2                           | μΑ   |

| GPIO with A                     | ADC Inputs (RADC Port)               |                                                                                                           |                             |     |                             |      |

|                                 |                                      | RADCx/TS: When used as ADC input, Internal Reference (V <sub>REF1</sub> )                                 | -0.2                        |     | 1                           | V    |

| V                               | Input voltage range                  | RADCx/TS: When used as ADC input, External Reference (V <sub>REG18</sub> )                                | -0.2                        |     | 0.8 x<br>V <sub>REG18</sub> | V    |

| V <sub>IN</sub>                 | Imput voitage range                  | RADCx/TS without weak pull-up, where n = 0 to 8                                                           | -0.2                        |     | 5.5                         | V    |

|                                 |                                      | RADCx/TS with weak pull-up where n = 0 to 8                                                               | -0.2                        |     | V <sub>REGIO</sub>          | V    |

| V <sub>IH</sub> <sup>(2)</sup>  | High-level input voltage             | RADCx/TS                                                                                                  | 0.7 x<br>V <sub>REGIO</sub> |     |                             | V    |

| V <sub>IL</sub> (2)             | Low-level input voltage              | RADCx/TS0                                                                                                 |                             |     | 0.3 x<br>V <sub>REGIO</sub> | V    |

| V <sub>IOHYS</sub> (1)          | Hysteresis of Input                  | RADCx/TS                                                                                                  | 75                          |     |                             | mV   |

| V <sub>OH</sub> <sup>(2)</sup>  | Output voltage high                  | RADCx/TS: I <sub>OH</sub> = -1 mA                                                                         | 0.7*V <sub>REGI</sub>       |     |                             | V    |

| V <sub>OL</sub> <sup>(2)</sup>  | Output voltage low                   | RADCx/TS: I <sub>OL</sub> = 3mA                                                                           |                             |     | 0.3 x<br>V <sub>REGIO</sub> | V    |

| R <sub>WKPD</sub>               | Internal weak pull down resistance   | RADC08                                                                                                    | 0.8                         | 1   | 1.2                         | МΩ   |

| R <sub>WKPU</sub>               | Internal weak pull up resistance     | RADC08                                                                                                    | 0.8                         | 1   | 1.2                         | ΜΩ   |

| C <sub>I</sub> <sup>(1)</sup>   | Input capacitance                    | RADC08                                                                                                    |                             | 2   |                             | pF   |

| I <sub>lkg</sub> (1)            | Input leakage current                | RADC08                                                                                                    |                             | 1   | 5                           | μA   |

| Low Voltag                      | e GPIO with Current Sinks (RL/LED Po | orts)                                                                                                     |                             | ,   | 1                           |      |

| V <sub>IN</sub>                 | Input voltage range                  | Without weak pull up                                                                                      | -0.2                        |     | 5.5                         | V    |

|                                | PARAMETER                          | TEST CONDITIONS         | MIN                   | TYP | MAX                         | UNIT |

|--------------------------------|------------------------------------|-------------------------|-----------------------|-----|-----------------------------|------|

| V <sub>IN</sub> (2)            | Input voltage range                | With weak pull up       | -0.2                  |     | V <sub>REGIO</sub>          | V    |

| V <sub>IH</sub> <sup>(2)</sup> | High-level input voltage           |                         | 0.7*V <sub>REGI</sub> |     |                             | V    |

| V <sub>IL</sub> (2)            | Low-level input voltage            |                         |                       |     | 0.3 x<br>V <sub>REGIO</sub> | V    |

| V <sub>IOHYS</sub> (1)         | Hysteresis of Input                |                         | 75                    |     |                             | mV   |

| V <sub>OH</sub> <sup>(2)</sup> | Output voltage high                | I <sub>OH</sub> = -1 mA | 0.7*V <sub>REGI</sub> |     |                             | V    |

| I <sub>OL</sub>                | Sink current                       | V <sub>OL</sub> = 1 V   | 3.5                   | 5   | 6.5                         | mA   |

| R <sub>WKPD</sub>              | Internal weak pull down resistance |                         | 0.8                   | 1   | 1.2                         | ΜΩ   |

| R <sub>WKPU</sub>              | Internal weak pull up resistance   |                         | 0.8                   | 1   | 1.2                         | ΜΩ   |

| C <sub>I</sub> (1)             | Input capacitance                  |                         |                       | 5   |                             | pF   |

| I <sub>lkg</sub> (1)           | Input leakage current              |                         |                       | 1   | 2                           | μΑ   |

- (1) Specified by design. Not production tested.

- (2) V<sub>REGIO</sub> can be 1.8V or 3.3V depending on OTP configuration.

### 6.9 Aux REGOUT LDO

Typical values stated where  $T_A = 25^{\circ}C$  and  $V_{BAT} = 59.2$  V, min/max values stated where  $T_A = -40^{\circ}C$  to  $105^{\circ}C$  and  $V_{BAT} = 5$  V to 80 V (unless otherwise noted)

|                                    | PARAMETER                                                                | TEST CONDITIONS                                                                                                                                                                                                                                                                  | MIN  | TYP   | MAX | UNIT |

|------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-----|------|

| V <sub>BAT_REGO</sub>              |                                                                          | V <sub>BAT</sub> ≥ 7.5 V                                                                                                                                                                                                                                                         |      | 7.5   | 8.5 | V    |

| V <sub>REGOUT_3</sub> .            | Regulator voltage ( programmed to 3.3V setting)                          | VREGIN≥ 4.2 V, I <sub>REG</sub> = 0 mA to 100 mA                                                                                                                                                                                                                                 | 3    | 3.3   | 3.6 | V    |

| V <sub>REGOUT_5</sub> .            | Regulator voltage (programmed to 5.0V setting)                           | V <sub>BREG</sub> ≥5.8V, I <sub>REG</sub> = 0 mA to 100 mA                                                                                                                                                                                                                       | 4.5  | 5     | 5.5 | V    |

| Δ<br>V <sub>REGOUT(TE</sub><br>MP) | Temp regulation                                                          | $\begin{array}{l} \Delta V_{REGOUT} \text{ vs } (V_{REGOUT} \text{ at } 25^{\circ}\text{C}, \\ I_{REGOUT} = 20 \text{ mA}, V_{REGIN} = 5.5 \text{ V}, \\ V_{REGOUT} \text{set to nominal } 3.3 \text{ V setting)} \end{array}$                                                   | -1.5 | ±0.25 | 1.5 | %    |

| Δ<br>V <sub>REGOUT(LI</sub><br>NE) | Line regulation                                                          | $\begin{array}{l} \Delta V_{REGOUT} \text{ vs } (V_{REGOUT} \text{ at } 25^{\circ}\text{C}, \\ V_{REGIN} = 5.5 \text{ V, } I_{REGOUT} = 20 \text{ mA, as} \\ V_{REGIN} \text{ varies from 5 V to 6 V, } V_{REGOUT} \\ \text{set to nominal } 3.3 \text{ V setting)} \end{array}$ | -1   |       | 1   | %    |

| Δ<br>V <sub>REGOUTLO</sub><br>AD   | Load regulation                                                          | I <sub>REGOUT</sub> = 1 to 5 mA                                                                                                                                                                                                                                                  | -2.6 |       | 2.6 | %    |

| Δ<br>V <sub>REGOUTLO</sub><br>AD   | Load regulation                                                          | I <sub>REGOUT</sub> = 1 to 100 mA                                                                                                                                                                                                                                                | -5   |       | 5   | %    |

| I <sub>sc</sub>                    | Regulator short-circuit current limit with external BJT                  | V <sub>REGOUT</sub> = 0 V                                                                                                                                                                                                                                                        | 101  |       | 230 | mA   |

| C <sub>EXT_REGIN</sub>             | External capacitor REGIN to VSS <sup>(1)</sup>                           |                                                                                                                                                                                                                                                                                  |      | 0.02  |     | μF   |

| C <sub>EXT</sub>                   | External capacitor REGOUT to VSS <sup>(1)</sup>                          |                                                                                                                                                                                                                                                                                  | 1    |       |     | μF   |

| $\Delta V_{O(TEMP)}$               | Regulator output over temperature                                        | $\Delta V_{REGIN}$ vs $V_{REGIN}$ at 25°C, $I_{REGIN}$ = 50 mA, $V_{BAT}$ > 8.5 V                                                                                                                                                                                                |      | ±1    |     | %    |

| I <sub>Max</sub>                   | Maximum current driven out from BREG without external BJT <sup>(1)</sup> | Under short circuit conditions (V <sub>BREG</sub> = 0 V)                                                                                                                                                                                                                         | 2    | 3     | 4   | mA   |

(1) Specified by design

#### 6.10 LD Pin

Typical values stated where  $T_A = 25^{\circ}C$  and  $V_{BAT} = 59.2$  V, min/max values stated where  $T_A = -40^{\circ}C$  to  $105^{\circ}C$  and  $V_{BAT} = 5$  V to 80 V (unless otherwise noted)

|                       | PARAMETER                                                                          | TEST CONDITIONS                               | MIN  | TYP | MAX  | UNIT |

|-----------------------|------------------------------------------------------------------------------------|-----------------------------------------------|------|-----|------|------|

| C <sub>IN</sub>       | Input capacitance                                                                  |                                               |      | 5   |      | pF   |

| RLD                   | LD pin serial resistor resistance                                                  |                                               | 2    | 10  |      | kΩ   |

| I <sub>(PULLUP)</sub> | Internal pullup current from BAT pin to LD pin, used for load detect functionality | V <sub>BAT</sub> ≥ 8 V, V <sub>LD</sub> = VSS | 1.75 | 3   | 4.05 | mA   |

### 6.11 Shelf Timer

Typical values stated where  $T_A$  = 25°C and  $V_{BAT}$  = 59.2 V, min/max values stated where  $T_A$  = -40°C to 105°C and  $V_{BAT}$  = 5 V to 80 V (unless otherwise noted)

|                                 | PARAMETER                                                                                                    | TEST CONDITIONS | MIN | TYP | MAX  | UNIT |

|---------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------|-----|-----|------|------|

| Low Frequen                     | cy Oscillator                                                                                                |                 |     |     |      |      |

| F <sub>OSC_SHUTDO</sub><br>WN   | Oscilator Operating Frequency in Shutdown Mode                                                               |                 |     | 2   |      | kHz  |

| T <sub>WAKEUP_DEL</sub>         | Preloaded Wake up Delay Time<br>( Selectable options: 33s, 66s, 131s,<br>262s, 524s, 1048s, 2097s and 4194s) |                 | 33  |     | 4194 | S    |

| F <sub>LOSC_DRIFT</sub> (1) (2) | Frequency Drift after Trim at Room<br>Temp                                                                   | 25°C            | -5  |     | 5    | %    |

| F <sub>LOSC_DRIFT</sub>         | Frequency Drift after Trim Across                                                                            | -25°C to 65°C   | -8  |     | 8    | %    |

| (1) (2) -                       | Temp                                                                                                         | -40°C to 85°C   | -10 |     | 10   | %    |

- (1) Specified by Design. Not production tested.

- (2) The frequency drift is included and measured from the trimmed frequency at T<sub>A</sub> = 25°C, with the minimum and maximum based on characterization, actual value stored in OTP.

### 6.12 Cell Balancing

Typical values stated where  $T_A = 25^{\circ}C$  and  $V_{BAT} = 59.2$  V, min/max values stated where  $T_A = -40^{\circ}C$  to  $105^{\circ}C$  and  $V_{BAT} = 5$  V to 80 V (unless otherwise noted)

|                   | PARAMETER | TEST CONDITIONS                                                                                           | MIN | TYP | MAX | UNIT |

|-------------------|-----------|-----------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| R <sub>(CB)</sub> |           | $R_{DS(ON)}$ for internal FET switch at $V_{VC(n)}$ - $V_{VC(n-1)}$ = 1.5V, 1 ≤ n ≥ 16, $V_{BAT}$ ≥ 4.7 V | 15  | 28  | 46  | Ω    |

- (1) Operation with V<sub>BAT</sub> up to 80 V is supported when the charge pump is not in operation. Whenever the charge pump is in operation (in 5.5 V or 11 V mode), the maximum voltage on V<sub>BAT</sub> should be reduced to ensure the voltage on CP1, CHG, and DSG does not exceed their maximum specified voltage.

- (2) Cell balancing must be controlled to limit the current based on the absolute maximum allowed current, and to avoid exceeding the recommended device operating temperature. This can be accomplished by appropriate sizing of the offchip cell input resistors and limiting the number of cells that can be balanced simultaneously.

Copyright © 2025 Texas Instruments Incorporated

English Data Sheet: SLUSFQ1

# **6.13 Comparator-Based Detections (SCOMP)**

Typical values stated where  $T_A$  = 25°C and  $V_{BAT}$  = 59.2 V, min/max values stated where  $T_A$  = -40°C to 105°C and  $V_{BAT}$  = 5 V to 80 V (unless otherwise noted)

|                                | PARAMETER                                                      | TEST CONDITIONS                                                                                      | MIN TYP          | MAX  | UNIT |

|--------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------|------|------|

|                                |                                                                | OT_SEL = 0x07 to 0x7F                                                                                | 893 to<br>108000 |      | Ω    |

|                                |                                                                | OT_SEL = 0x15 (35°C)                                                                                 | 7200             |      | Ω    |

|                                |                                                                | OT_SEL = 0x18 (40°C)                                                                                 | 6000             |      | Ω    |

|                                |                                                                | OT_SEL = 0x1c (45°C)                                                                                 | 4909             |      | Ω    |

|                                |                                                                | OT_SEL = 0x20 (50°C)                                                                                 | 4154             |      | Ω    |

|                                |                                                                | OT_SEL = 0x24 (55°C)                                                                                 | 3600             |      | Ω    |

|                                |                                                                | OT_SEL = 0x2a (60°C)                                                                                 | 3000             |      | Ω    |

| R <sub>OT</sub> <sup>(1)</sup> | Overtemperature detection resistance threshold                 | OT_SEL = 0x30 (65°C)                                                                                 | 2571             |      | Ω    |

|                                | resistance infeshold                                           | OT_SEL = 0x36 (70°C)                                                                                 | 2250             |      | Ω    |

|                                |                                                                | OT_SEL = 0x3e (75°C)                                                                                 | 1929             |      | Ω    |

|                                |                                                                | OT_SEL = 0x47 (80°C)                                                                                 | 1662             |      | Ω    |

|                                |                                                                | OT_SEL = 0x50 (85°C)                                                                                 | 1459             |      | Ω    |

|                                |                                                                | OT_SEL = 0x5c (90°C)                                                                                 | 1256             |      | Ω    |

|                                |                                                                | OT_SEL = 0x68 (95°C)                                                                                 | 1102             |      | Ω    |

|                                |                                                                | OT_SEL = 0x75 (100°C)                                                                                | 973              |      | Ω    |

|                                |                                                                | OT_SEL = 0x7f (105°C)                                                                                | 893              |      | Ω    |