# ACD354x Single Channel 14-bit 250MSPS and 500MSPS Analog-to-Digital Converter (ADC)

#### 1 Features

- 14-bit, single channel 250 and 500MSPS ADC

- Noise spectral density: -158.5dBFS/Hz

- Thermal Noise: 74.5dBFS

- Single core (non-interleaved) ADC architecture

- Power consumption:

- 435mW (500MSPS)

- 369mW (250MSPS)

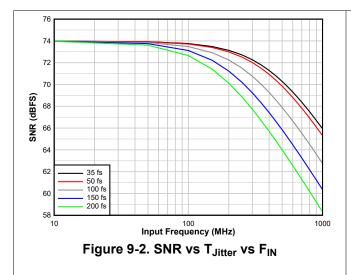

- Aperture jitter: 75fs

- Buffered analog inputs

- Programmable 100 and 200Ω termination

- Input fullscale: 2Vpp

- Full power input bandwidth (-3dB): 1.4GHz

- Spectral performance ( $f_{IN} = 70MHz$ , -1dBFS):

- SNR: 73.8dBFS

- SFDR HD2,3: 82dBc

- SFDR worst spur: 94dBFS

- Digital down-converters (DDCs)

- Up to four independent DDC

- Complex and real decimation

- Decimation: 2x, 4x to 32768x decimation

- 48-bit NCO phase coherent frequency hopping

- DDR/Serial LVDS interface

- 16-bit Parallel SDR, DDR LVDS for DDC bypass

- Serial LVDS for decimation

- 32-bit output option for high decimation

#### 2 Applications

- Software defined radio

- Spectrum analyzer

- Radar

- Spectroscopy

- Power amplifier linearization

- Communications infrastructure

### 3 Description

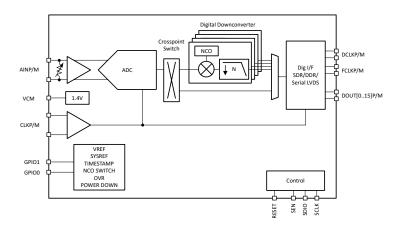

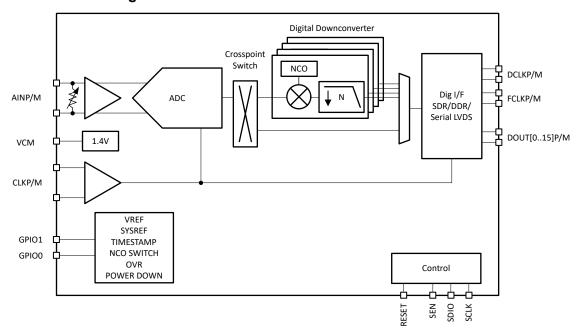

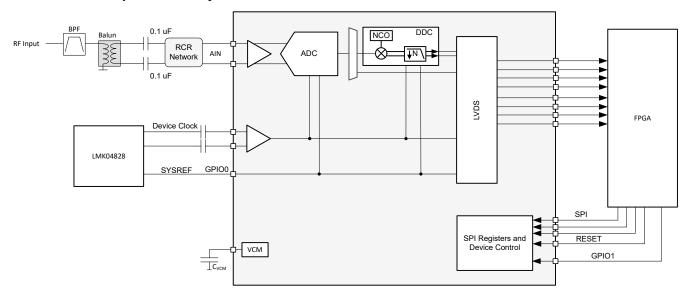

The ADC3548 and ADC3549 (ADC354x) is a 14bit, 250 and 500MSPS, single channel analog to digital converter (ADC). The device is designed for high signal-to-noise ratio (SNR) and delivers a noise spectral density as low as -158.5dBFS/Hz.

The power efficient ADC architecture consumes 435mW at 500MSPS and provides power scaling with lower sampling rates (369mW at 250MSPS).

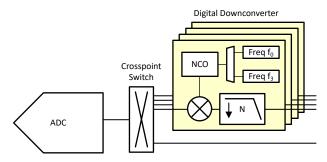

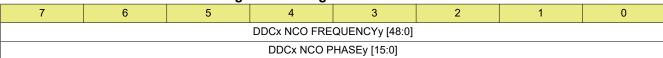

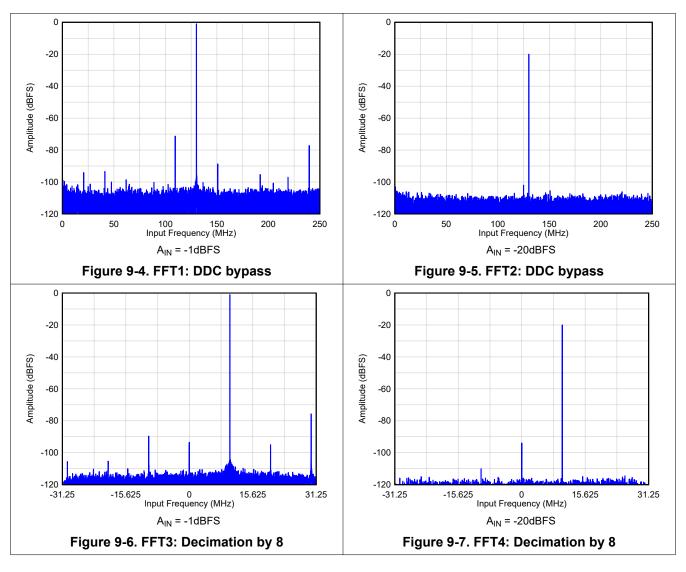

The ADC354x includes a quad band digital downconverter (DDC) supporting wide band decimation by 2 to narrow band decimation by 32768. The DDC uses a 48-bit NCO which supports phase coherent and phase continuous frequency hopping.

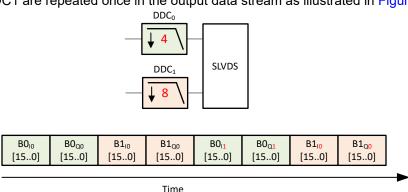

The ADC354x is outfitted with a flexible LVDS interface. In decimation bypass mode, the device uses a 14-bit wide parallel SDR or DDR LVDS interface. When using decimation, the output data is transmitted using a serial LVDS interface reducing the number of lanes needed as decimation increases. For high decimation rates, the output resolution can be increased to 32-bit.

#### **Device Information**

| PART NUMBER | PACKAGE(!) | MAXIMUM<br>SAMPLING RATE |

|-------------|------------|--------------------------|

| ADC3549     | 64 QFN     | 500MSPS                  |

| ADC3548     | 64 QFN     | 250MSPS                  |

For more information, see Section 12.

**Block Diagram**

# **Table of Contents**

| 1 Features1                                         | 8.1 Overview                                         | . 24 |

|-----------------------------------------------------|------------------------------------------------------|------|

| 2 Applications1                                     | 8.2 Functional Block Diagram                         | .24  |

| 3 Description1                                      | 8.3 Feature Description                              | .2   |

| 4 Device Comparison2                                | 8.4 Device Functional Modes                          | .48  |

| 5 Pin Configuration and Functions3                  | 8.5 Programming                                      | 49   |

| 6 Specifications5                                   | 9 Application and Implementation                     |      |

| 6.1 Absolute Maximum Ratings5                       | 9.1 Application Information                          | 6    |

| 6.2 ESD Ratings5                                    | 9.2 Typical Application                              | 6    |

| 6.3 Recommended Operating Conditions5               | 9.3 Power Supply Recommendations                     | .72  |

| 6.4 Thermal Information6                            | 9.4 Layout                                           | . 73 |

| 6.5 Electrical Characteristics - Power Consumption6 | 10 Device and Documentation Support                  | .74  |

| 6.6 Electrical Characteristics - DC Specifications6 | 10.1 Documentation Support                           | .74  |

| 6.7 Electrical Characteristics - AC Specifications  | 10.2 Receiving Notification of Documentation Updates | .74  |

| (ADC3548 - 250 MSPS)8                               | 10.3 Support Resources                               | .74  |

| 6.8 Electrical Characteristics - AC Specifications  | 10.4 Trademarks                                      | .74  |

| (ADC3549 - 500 MSPS)9                               | 10.5 Electrostatic Discharge Caution                 | .74  |

| 6.9 Timing Requirements10                           | 10.6 Glossary                                        |      |

| 6.10 Typical Characteristics - ADC3548 (250MSPS)11  | 11 Revision History                                  | 74   |

| 6.11 Typical Characteristics - ADC3549 (500MSPS)16  | 12 Mechanical, Packaging, and Orderable              |      |

| 7 Parameter Measurement Information22               | Information                                          | .74  |

| 8 Detailed Description24                            |                                                      |      |

|                                                     |                                                      |      |

# **4 Device Comparison**

# **Table 4-1. Device Comparison Table**

| in zone companion in and |                                                                                       |                                                                                                                                                                                                                                                                                 |  |  |  |  |

|--------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Maximum Sampling Rate    | Resolution                                                                            | No. of Channels                                                                                                                                                                                                                                                                 |  |  |  |  |

| 500MSPS                  | 16 bit                                                                                | 2                                                                                                                                                                                                                                                                               |  |  |  |  |

| 250MSPS                  | 16 bit                                                                                | 2                                                                                                                                                                                                                                                                               |  |  |  |  |

| 500MSPS                  | 16 bit                                                                                | 1                                                                                                                                                                                                                                                                               |  |  |  |  |

| 250MSPS                  | 16 bit                                                                                | 1                                                                                                                                                                                                                                                                               |  |  |  |  |

| 500MSPS                  | 14 bit                                                                                | 2                                                                                                                                                                                                                                                                               |  |  |  |  |

| 250MSPS                  | 14 bit                                                                                | 2                                                                                                                                                                                                                                                                               |  |  |  |  |

| 500MSPS                  | 14 bit                                                                                | 1                                                                                                                                                                                                                                                                               |  |  |  |  |

| 250MSPS                  | 14 bit                                                                                | 1                                                                                                                                                                                                                                                                               |  |  |  |  |

|                          | Maximum Sampling Rate 500MSPS 250MSPS 500MSPS 250MSPS 500MSPS 500MSPS 250MSPS 500MSPS | Maximum Sampling Rate         Resolution           500MSPS         16 bit           250MSPS         16 bit           500MSPS         16 bit           250MSPS         16 bit           500MSPS         14 bit           250MSPS         14 bit           500MSPS         14 bit |  |  |  |  |

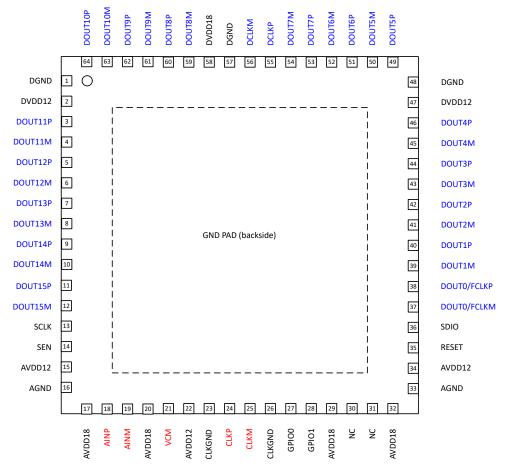

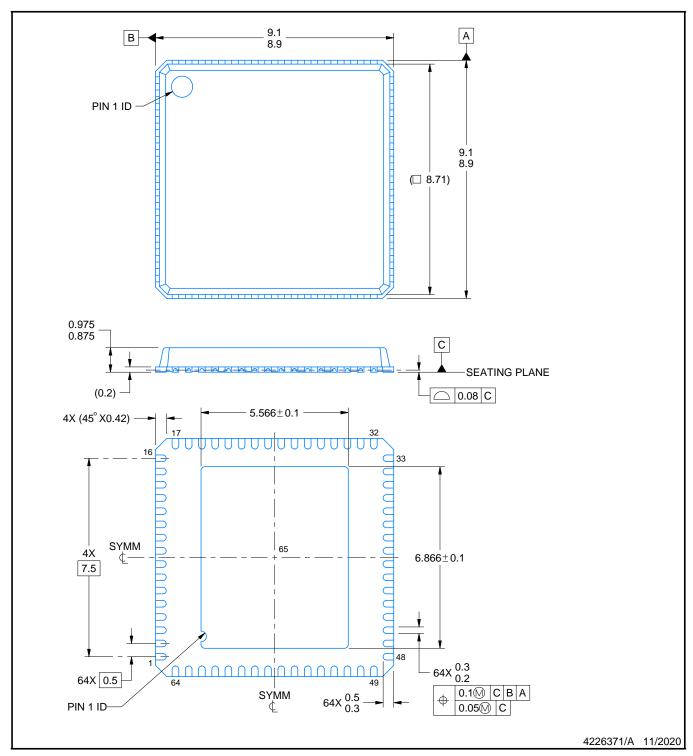

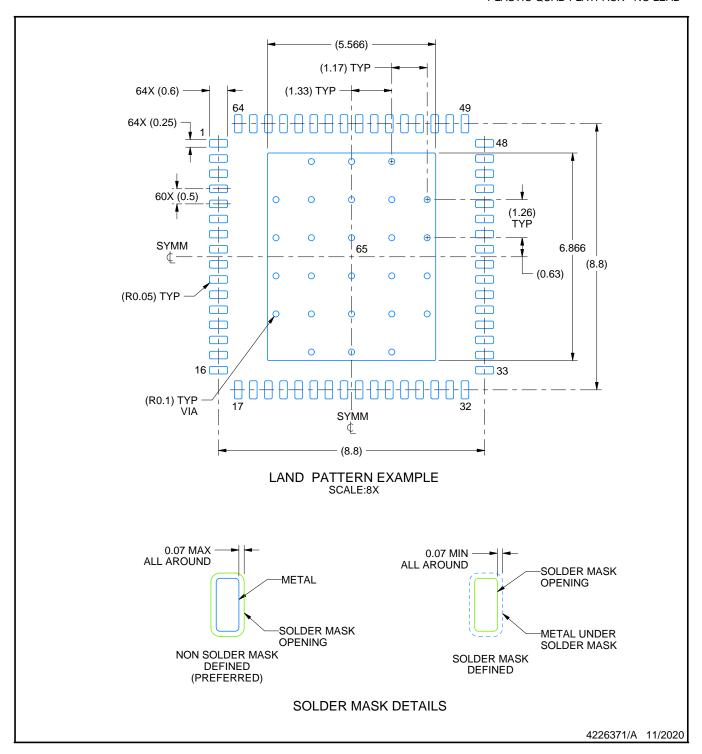

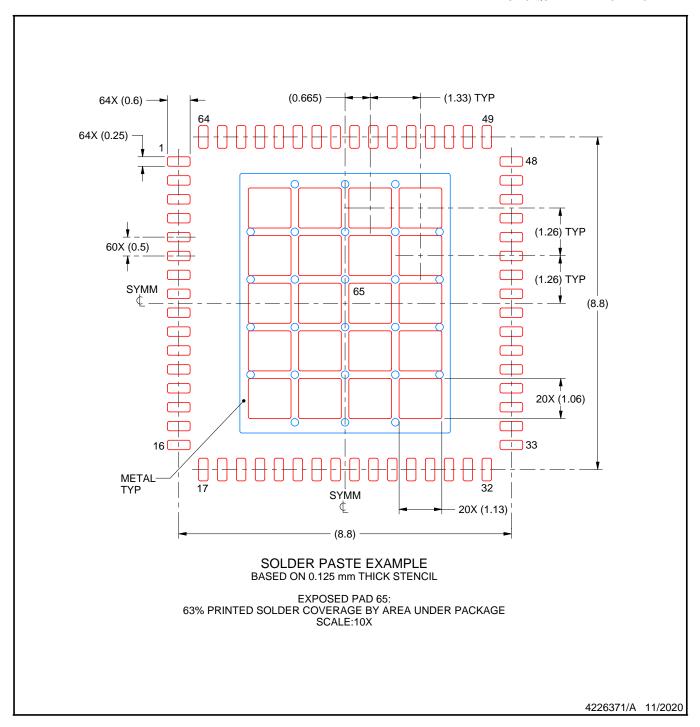

# **5 Pin Configuration and Functions**

Figure 5-1. RTD Package, 64 Pin VQFNP (Top View)

**Table 5-1. Pin Functions**

| PIN         |                   | TYPE(1) | DESCRIPTION                                                                                                                                                      |

|-------------|-------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | NO.               | ITPE    | DESCRIPTION                                                                                                                                                      |

| AGND        | 16, 33            | I       | Analog ground, 0V                                                                                                                                                |

| AINM        | 19                | I       | Channel A differential signal input, negative connection. The differential input has programmable internal termination (100 or $200\Omega$ ) and is self biased. |

| AINP        | 18                | I       | Channel A differential signal input, positive connection.                                                                                                        |

| AVDD12      | 15, 22,<br>34     | I       | Analog 1.2V supply                                                                                                                                               |

| AVDD18      | 17, 20,<br>29, 32 | I       | Analog 1.8V supply                                                                                                                                               |

| CLKGND      | 23, 26            | I       | Clock ground, 0V                                                                                                                                                 |

| CLKP        | 24                | I       | Device sampling clock differential input. AC coupling and terminating the clock signal externally                                                                |

| CLKM        | 25                | I       | for best AC performance is recommended. The differential input is self biased to the input common-mode voltage (0.75V).                                          |

| DCLKP       | 55                | 0       | Differential LVDS data hit alook quitaut                                                                                                                         |

| DCLKM       | 56                | 0       | Differential LVDS data bit clock output.                                                                                                                         |

| DGND        | 1, 48, 57         | I       | Digital ground, 0V                                                                                                                                               |

| DOUT0/FCLKM | 37                | 0       | Differential LVDS data bit output lane 0. In decimation mode this pin turns to the differential SLVDS                                                            |

| DOUT0/FCLKP | 38                | 0       | frame clock output, replacing the LSB.                                                                                                                           |

## Table 5-1. Pin Functions (continued)

| PIN            | 1     |                     | Table 5-1. Pin Functions (continued)                                                                                  |  |

|----------------|-------|---------------------|-----------------------------------------------------------------------------------------------------------------------|--|

|                |       | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                           |  |

| NAME<br>DOUT1M | NO.   | 0                   |                                                                                                                       |  |

|                | 39    | 0                   | Differential LVDS data bit output lane 1. Can be left floating and powered down via SPI if not used.                  |  |

| DOUT1P         | 40    | 0                   |                                                                                                                       |  |

| DOUT2M         | 41    | 0                   | Differential LVDS data bit output lane 2. Can be left floating and powered down via SPI if not used.                  |  |

| DOUT2P         | 42    | 0                   |                                                                                                                       |  |

| DOUT3M         | 43    | 0                   | Differential LVDS data bit output lane 3. Can be left floating and powered down via SPI if not used.                  |  |

| DOUT3P         | 44    | 0                   |                                                                                                                       |  |

| DOUT4M         | 45    | 0                   | Differential LVDS data bit output lane 4. Can be left floating and powered down via SPI if not used.                  |  |

| DOUT4P         | 46    | 0                   |                                                                                                                       |  |

| DOUT5P         | 49    | 0                   | Differential LVDS data bit output lane 5. Can be left floating and powered down via SPI if not used.                  |  |

| DOUT5M         | 50    | 0                   |                                                                                                                       |  |

| DOUT6P         | 51    | 0                   | Differential LVDS data bit output lane 6. Can be left floating and powered down via SPI if not used.                  |  |

| DOUT6M         | 52    | 0                   | Differential EVDE data by output falle 6. Gail be for floating and powered down via of 11 flot about.                 |  |

| DOUT7P         | 53    | 0                   | Differential LVDS data bit output lane 7. Can be left floating and powered down via SPI if not used.                  |  |

| DOUT7M         | 54    | 0                   | Tollielential EVDS data bit output lane 7. Can be left hoating and powered down via SFT in hot used.                  |  |

| DOUT8M         | 59    | 0                   | Differential LVDS data hit output land 9. Can be left floating and neuronal days via SDI if not used                  |  |

| DOUT8P         | 60    | 0                   | Differential LVDS data bit output lane 8. Can be left floating and powered down via SPI if not used.                  |  |

| DOUT9M         | 61    | 0                   | Differential LV/DC data bit autout land 0. Comba laft flaction and reviewed device via CDI if not used                |  |

| DOUT9P         | 62    | 0                   | <ul> <li>Differential LVDS data bit output lane 9. Can be left floating and powered down via SPI if not us</li> </ul> |  |

| DOUT10M        | 63    | 0                   | Differential LVDS data bit output lane 10. Can be left floating and powered down via SPI if no                        |  |

| DOUT10P        | 64    | 0                   | - Differential LVDS data bit output lane 10. Can be left floating and powered down via SPI if not used.               |  |

| DOUT11P        | 3     | 0                   |                                                                                                                       |  |

| DOUT11M        | 4     | 0                   | Differential LVDS data bit output lane 11. Can be left floating and powered down via SPI if not used.                 |  |

| DOUT12P        | 5     | 0                   |                                                                                                                       |  |

| DOUT12M        | 6     | 0                   | Differential LVDS data bit output lane 12. Can be left floating and powered down via SPI if not used.                 |  |

| DOUT13P        | 7     | 0                   |                                                                                                                       |  |

| DOUT13M        | 8     | 0                   | Differential LVDS data bit output lane 13. Can be left floating and powered down via SPI if not used.                 |  |

| DOUT14P        | 9     | 0                   |                                                                                                                       |  |

| DOUT14M        | 10    | 0                   | Differential LVDS data bit output lane 14. Can be left floating and powered down via SPI if not used.                 |  |

| DOUT15P        | 11    | 0                   | Differential LVDS data bit output lane 15 (MSB). Can be left floating and powered down via SPI if                     |  |

| DOUT15M        | 12    | 0                   | not used.                                                                                                             |  |

| DVDD12         | 2, 47 | ı                   | Digital 1.2V supply                                                                                                   |  |

| DVDD18         | 58    | ı                   | Digital 1.8V supply                                                                                                   |  |

| GPIO0          | 27    | I/O                 | Synchronization or control input or status output. Can be left floating if not used.                                  |  |

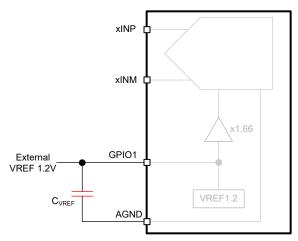

| GPIO1          | 28    | I/O                 | Control input or status output or external voltage reference (1.2V). Can be left floating if not used.                |  |

| NC             | 30,31 | -                   | Do not connect                                                                                                        |  |

| RESET          | 35    | I                   | Hardware reset. Active high. This pin has an internal 21kΩ pull-up resistor to DGND.                                  |  |

| SCLK           | 13    | I                   | Serial interface clock for the serial interface programming. This pin has an internal 21kΩ pull-up resistor to DGND.  |  |

| SDIO           | 36    | I/O                 | Serial interface data input/output. This pin has an internal 21kΩ pull-up resistor to DGND.                           |  |

| SEN            | 14    | ı                   | Serial interface chip select. This pin has an internal 21kΩ pull-up resistor to DVDD18.                               |  |

| VCM            | 21    | 0                   | Common mode voltage output (1.4V)                                                                                     |  |

|                |       |                     | - Common made carbar (1.17)                                                                                           |  |

<sup>(1)</sup> I = Input, O = Output, I/O = Input or Output, G = Ground, P = Power.

# **6 Specifications**

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

| PARAMETER                             | TEST CONDITIONS                     | MIN  | MAX          | UNIT |

|---------------------------------------|-------------------------------------|------|--------------|------|

| Supply voltage range, AVDD18          |                                     | -0.3 | 2.1          | V    |

| Supply voltage range, AVDD12          |                                     | -0.3 | 1.4          | V    |

| Supply voltage range, DVDD18          |                                     | -0.3 | 2.1          | V    |

| Supply voltage range, DVDD12          |                                     | -0.3 | 1.4          | V    |

|                                       | AINP/M                              | -0.3 | 2.1          | V    |

| Voltage applied to input pins         | CLKP/M                              | -0.3 | 1.4          | V    |

|                                       | GPIO0/1, RESET, SCLK, SEN, SDIO     | -0.3 | DVDD18 + 0.2 | V    |

| Peak RF input power (AINP/M)          | Differential 100 Ω termination      |      | 10           | dBm  |

| unction temperature, T <sub>J</sub>   |                                     |      | 125          | °C   |

| Storage temperature, T <sub>stg</sub> | orage temperature, T <sub>stg</sub> |      |              | C    |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |                         |                                                                       | VALUE | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | 1500  | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | 750   | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                |                                | MIN  | NOM | MAX                | UNIT |

|----------------|--------------------------------|------|-----|--------------------|------|

| AVDD18         | 1.8 V analog supply            | 1.75 | 1.8 | 1.85               |      |

| AVDD12         | 1.2 V analog supply            | 1.15 | 1.2 | 1.225              | V    |

| DVDD18         | 1.8 V digital supply           | 1.75 | 1.8 | 1.85               | V    |

| DVDD12         | 1.2 V digital supply           | 1.15 | 1.2 | 1.225              |      |

| T <sub>A</sub> | Operating free-air temperature | -40  |     | 105                | °C   |

| T <sub>J</sub> | Operating junction temperature |      |     | 115 <sup>(1)</sup> | C    |

(1) Prolonged use above this junction temperature may increase the device failure-in-time (FIT) rate.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### **6.4 Thermal Information**

|                       |                                              | ADC3548/49 |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC(1)                            | RTD (QFN)  | UNIT |

|                       |                                              | 64 Pins    |      |

| R <sub>OJA</sub>      | Junction-to-ambient thermal resistance       | 22.3       | °C/W |

| R <sub>OJC(top)</sub> | Junction-to-case (top) thermal resistance    | 11.4       | °C/W |

| R <sub>OJB</sub>      | Junction-to-board thermal resistance         | 7.4        | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.1        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 7.3        | °C/W |

| R <sub>OJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.1        | °C/W |

<sup>(1)</sup> For more information about thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

## 6.5 Electrical Characteristics - Power Consumption

Maximum and minimum values are specified over the operating free-air temperature range and nominal supply voltages. Typical values are specified at  $T_A$  = 25°C, ADC sampling rate = 500 MSPS, DDC Bypass mode, 50% clock duty cycle, nominal supply voltages and -1-dBFS differential input, unless otherwise noted

|                     | PARAMETER                            | TEST CONDITIONS   | MIN | TYP | MAX | UNIT |

|---------------------|--------------------------------------|-------------------|-----|-----|-----|------|

| ADC3548 -           | - 250 MSPS                           |                   |     |     |     |      |

| I <sub>AVDD18</sub> | Supply current, 1.8 V analog supply  | DDR LVDS          |     | 60  | 85  | mA   |

| I <sub>AVDD12</sub> | Supply current, 1.2 V analog supply  | DDR LVDS          |     | 45  | 90  | mA   |

| I <sub>DVDD18</sub> | Supply current, 1.8 V digital supply | DDR LVDS          |     | 75  | 105 | mA   |

| I <sub>DVDD12</sub> | Supply current, 1.2 V digital supply | DDR LVDS          |     | 60  | 126 | mA   |

| P <sub>DIS</sub>    | Power dissipation                    | DDR LVDS          |     | 369 |     | mW   |

| ADC3549 -           | - 500 MSPS                           | -                 |     |     | ,   |      |

| I <sub>AVDD18</sub> | Supply current, 1.8 V analog supply  | DDR LVDS          |     | 66  | 85  | mA   |

| I <sub>AVDD12</sub> | Supply current, 1.2 V analog supply  | DDR LVDS          |     | 65  | 115 | mA   |

| I <sub>DVDD18</sub> | Supply current, 1.8 V digital supply | DDR LVDS          |     | 76  | 105 | mA   |

| I <sub>DVDD12</sub> | Supply current, 1.2 V digital supply | DDR LVDS          |     | 85  | 155 | mA   |

| P <sub>DIS</sub>    | Power dissipation                    | DDR LVDS          |     | 435 |     | mW   |

| POWER D             | OWN MODES                            |                   | -   |     | ,   |      |

| P <sub>DIS</sub>    | Power down mode power consumption    | Global power down |     | 31  |     | mW   |

### 6.6 Electrical Characteristics - DC Specifications

Maximum and minimum values are specified over the operating free-air temperature range and nominal supply voltages. Typical values are specified at  $T_A$  = 25°C, ADC sampling rate = 500 MSPS, DDC Bypass mode, 50% clock duty cycle, nominal supply voltages and -1-dBFS differential input, internal reference, unless otherwise noted

|                       | PARAMETER                    | TEST CONDITIONS          | MIN   | TYP    | MAX | UNIT    |

|-----------------------|------------------------------|--------------------------|-------|--------|-----|---------|

| DC ACCURA             | CY                           |                          |       |        |     |         |

| No missing co         | odes                         |                          | 14    |        |     | bits    |

| ADC3548: 25           | 0 MSPS (INTERNAL REFERENCE)  |                          |       | -      |     |         |

| DNL                   | Differential nonlinearity    | F <sub>IN</sub> = 70 MHz | -0.95 | ± 0.15 |     | LSB     |

| INL                   | Integral nonlinearity        | F <sub>IN</sub> = 70 MHz |       | ± 0.5  |     | LSB     |

| V <sub>OS_ERR</sub>   | Offset error                 |                          |       | 2.5    |     | LSB     |

| V <sub>OS_DRIFT</sub> | Offset drift over temprature |                          |       | 2.5    |     | LSB     |

| GAIN <sub>ERR</sub>   | Gain error                   | External Reference       |       | ± 1    |     | %FSR    |

| GAINERR               | Gain end                     | Internal Reference       |       | ± 3    |     | /01-GIX |

| GAIN <sub>DRIFT</sub> | Gain drift over temperature  | External Reference       |       | ± 0.5  |     | %FSR    |

| OAIINDRIFT            | Gain drift over temperature  | Internal Reference       |       | ± 1    |     | 701 GIX |

Submit Document Feedback

Copyright © 2025 Texas Instruments Incorporated

Maximum and minimum values are specified over the operating free-air temperature range and nominal supply voltages. Typical values are specified at  $T_A$  = 25°C, ADC sampling rate = 500 MSPS, DDC Bypass mode, 50% clock duty cycle, nominal supply voltages and -1-dBFS differential input, internal reference, unless otherwise noted

|                            | PARAMETER                             | TEST CONDITIONS             | MIN             | TYP      | MAX   | UNIT  |

|----------------------------|---------------------------------------|-----------------------------|-----------------|----------|-------|-------|

| ADC3549: 5                 | 00 MSPS (INTERNAL REFERENCE)          |                             |                 |          |       |       |

| DNL                        | Differential nonlinearity             | F <sub>IN</sub> = 70 MHz    | -0.95           | ± 0.15   |       | LSB   |

| INL                        | Integral nonlinearity                 | F <sub>IN</sub> = 70 MHz    |                 | ± 0.5    |       | LSB   |

| V <sub>OS_ERR</sub>        | Offset error                          |                             |                 | 2.5      |       | LSB   |

| V <sub>OS_DRIFT</sub>      | Offset drift over temprature          |                             |                 | 2.5      |       | LSB   |

| CAIN                       | Gain error                            | External Reference          |                 | ± 1      |       | %FSR  |

| GAIN <sub>ERR</sub>        | Gain enoi                             | Internal Reference          |                 | ± 3      |       | 70F3K |

| CAIN                       | Cain drift over temperature           | External Reference          |                 | ± 0.5    |       | %FSR  |

| GAIN <sub>DRIFT</sub>      | Gain drift over temperature           | Internal Reference          |                 | ± 1      |       | 70F3K |

| ADC ANALO                  | OG INPUTS (AINP/M)                    |                             |                 |          |       |       |

| FS                         | Input full scale                      | Differential                |                 | 2.0      |       | Vpp   |

| V <sub>ICM</sub>           | Input common model voltage            |                             | 1.3             | 1.4      | 1.5   | V     |

| Z <sub>IN</sub>            | Differential input impedance          | Differential at 100 MHz     |                 | 100      |       | Ω     |

| V <sub>CM</sub>            | Output common mode voltage            |                             |                 | 1.4      |       | V     |

| BW                         | Analog Input Bandwidth (-3dB)         |                             |                 | 1.4      |       | GHz   |

| CLOCK INP                  | UT (CLKP/M)                           |                             |                 |          |       |       |

| In most of a difference on |                                       | ADC3549                     | 125             |          | 500   | MHz   |

| Input clock fr             | equency                               | ADC3548                     | 125             |          | 250   | MHz   |

| $V_{ID}$                   | Differential input voltage            |                             | 0.5             | 2        | 2.4   | Vpp   |

| V <sub>ICM</sub>           | Input common mode voltage             |                             |                 | 0.75     |       | V     |

| Z <sub>IN</sub>            | Differential input impedance          | Differential at 500 MHz     |                 | 5        |       | kΩ    |

| Clock duty c               | ycle                                  |                             | 35              | 50       | 65    | %     |

| EXTERNAL                   | REFERENCE INPUT (GPIO1)               |                             |                 |          |       |       |

| VREF                       | External voltage reference            |                             | 1.175           | 1.2      | 1.225 | V     |

| I <sub>VREF</sub>          | Input current, external voltage refer | ence input                  |                 | 10       |       | uA    |

| DIGITAL INF                | PUTS (GPIO0, GPIO1, RESET, SCLK       | , SEN, SDIO)                |                 |          | '     |       |

| V <sub>IH</sub>            | High level input voltage              |                             | 1.4             | 1.8      |       | V     |

| V <sub>IL</sub>            | Low level input voltage               |                             |                 | 0        | 0.4   | V     |

| I <sub>IH</sub>            | High level input current              |                             |                 | 90       | 150   | uA    |

| I <sub>IL</sub>            | Low level input current               |                             | -150            | -90      |       | uA    |

| Cı                         | Input capacitance                     |                             |                 | 1.5      |       | pF    |

| DIGITAL OU                 | TPUTS (GPIO0, GPIO1, SDIO)            |                             |                 |          |       |       |

| V <sub>OH</sub>            | High level output voltage             | I <sub>LOAD</sub> = -400 uA | AVDD18<br>- 0.1 | AVDD18   |       | V     |

| V <sub>OL</sub>            | Low level output voltage              | I <sub>LOAD</sub> = 400 uA  |                 |          | 0.1   | V     |

| LVDS/SLVD                  | S INTERFACE (DOUT[015]P/M, DC         | LKP/M)                      | l .             |          | Į.    |       |

| Output data                | format (default)                      |                             | 2s c            | omplemen | it    |       |

| V <sub>OD</sub>            | Differential output voltage           | differential peak-peak      | 500             | 700      | 850   | mVpp  |

| V <sub>OCM</sub>           | Output common mode voltage            |                             | 0.96            | 1.02     | 1.08  | V     |

## 6.7 Electrical Characteristics - AC Specifications (ADC3548 - 250 MSPS)

Maximum and minimum values are specified over the operating free-air temperature range and nominal supply voltages. Typical values are specified at  $T_A$  = 25°C, ADC sampling rate = 250 MSPS, DDC Bypass mode, 50% clock duty cycle, nominal supply voltages and -1-dBFS differential input, internal reference, unless otherwise noted

|           | PARAMETER                                        | TEST CONDITIONS                                                               | MIN <sup>(1)</sup> | TYP MAX | UNIT    |

|-----------|--------------------------------------------------|-------------------------------------------------------------------------------|--------------------|---------|---------|

| AC ACCURA | ACY                                              |                                                                               |                    |         |         |

| NSD       | Noise Spectral Density                           | f <sub>IN</sub> = 100 MHz, A <sub>IN</sub> = -20 dBFS                         | _                  | 155.5   | dBFS/Hz |

| NF        | Noise Figure                                     | f <sub>IN</sub> = 100 MHz, A <sub>IN</sub> = -20 dBFS                         |                    | 25.5    | dB      |

|           |                                                  | f <sub>IN</sub> = 10 MHz                                                      |                    | 74.0    |         |

|           |                                                  | f <sub>IN</sub> = 70 MHz                                                      | 70                 | 73.8    |         |

| SNR       | Signal to noise ratio                            | f <sub>IN</sub> = 170 MHz                                                     |                    | 73.2    | dBFS    |

|           |                                                  | f <sub>IN</sub> = 300 MHz                                                     |                    | 71.6    |         |

|           |                                                  | f <sub>IN</sub> = 450 MHz                                                     |                    | 69.6    |         |

|           |                                                  | f <sub>IN</sub> = 10 MHz                                                      | ,                  | 72.1    |         |

|           |                                                  | f <sub>IN</sub> = 70 MHz                                                      |                    | 71.9    |         |

| SINAD     | Signal to noise and distortion ratio             | f <sub>IN</sub> = 170 MHz                                                     |                    | 71.3    | dBFS    |

|           |                                                  | f <sub>IN</sub> = 300 MHz                                                     |                    | 69.7    |         |

|           |                                                  | f <sub>IN</sub> = 450 MHz                                                     |                    | 67.8    |         |

|           |                                                  | f <sub>IN</sub> = 10 MHz                                                      |                    | 11.7    |         |

|           |                                                  | f <sub>IN</sub> = 70 MHz                                                      |                    | 11.7    |         |

| ENOB      | Effective number of bits                         | f <sub>IN</sub> = 170 MHz                                                     |                    | 11.6    | Bits    |

|           |                                                  | f <sub>IN</sub> = 300 MHz                                                     |                    | 11.3    |         |

|           |                                                  | f <sub>IN</sub> = 450 MHz                                                     |                    | 11.0    |         |

|           | Total Harmonic Distortion (First five harmonics) | f <sub>IN</sub> = 10 MHz                                                      |                    | 77      |         |

|           |                                                  | f <sub>IN</sub> = 70 MHz                                                      |                    | 80      | dBc     |

| THD       |                                                  | f <sub>IN</sub> = 170 MHz                                                     |                    | 75      |         |

|           |                                                  | f <sub>IN</sub> = 300 MHz                                                     |                    | 71      |         |

|           |                                                  | f <sub>IN</sub> = 450 MHz                                                     |                    | 65      |         |

|           |                                                  | f <sub>IN</sub> = 10 MHz                                                      |                    | 79      |         |

|           |                                                  | f <sub>IN</sub> = 70 MHz                                                      | 69                 | 85      |         |

| HD2       | Second Harmonic Distortion                       | f <sub>IN</sub> = 170 MHz                                                     |                    | 78      | dBc     |

|           |                                                  | f <sub>IN</sub> = 300 MHz                                                     |                    | 76      |         |

|           |                                                  | f <sub>IN</sub> = 450 MHz                                                     |                    | 68      |         |

|           |                                                  | f <sub>IN</sub> = 10 MHz                                                      |                    | 83      |         |

|           | Third Harmonic Distortion                        | f <sub>IN</sub> = 70 MHz                                                      | 71                 | 81      |         |

| HD3       |                                                  | f <sub>IN</sub> = 170 MHz                                                     |                    | 81      | dBc     |

|           |                                                  | f <sub>IN</sub> = 300 MHz                                                     |                    | 79      |         |

|           |                                                  | f <sub>IN</sub> = 450 MHz                                                     |                    | 74      |         |

|           |                                                  | f <sub>IN</sub> = 10 MHz                                                      |                    | 96      |         |

|           |                                                  | f <sub>IN</sub> = 70 MHz                                                      |                    | 96      |         |

| Non HD2,3 | Spur free dynamic range (excluding               | f <sub>IN</sub> = 170 MHz                                                     |                    | 95      | dBFS    |

| ,-        | HD2 and HD3)                                     | f <sub>IN</sub> = 300 MHz                                                     |                    | 88      |         |

|           |                                                  | f <sub>IN</sub> = 450 MHz                                                     |                    | 81      |         |

| IMD3      | Two tone inter-modulation distortion             | $f_1 = 100 \text{ MHz}, f_2 = 120 \text{ MHz}, A_{IN} = -7 \text{ dBFS/tone}$ |                    | 83      | dBc     |

<sup>(1)</sup> SNR and HD3 minimum values are specified by ATE; HD2 is specified by bench characterization.

Submit Document Feedback

Copyright © 2025 Texas Instruments Incorporated

## 6.8 Electrical Characteristics - AC Specifications (ADC3549 - 500 MSPS)

Maximum and minimum values are specified over the operating free-air temperature range and nominal supply voltages. Typical values are specified at  $T_A$  = 25°C, ADC sampling rate = 500 MSPS, DDC Bypass mode, 50% clock duty cycle, nominal supply voltages and -1-dBFS differential input, internal reference, unless otherwise noted

|           | PARAMETER                                        | TEST CONDITIONS                                                                    | MIN <sup>(1)</sup> | TYP MAX | UNIT    |

|-----------|--------------------------------------------------|------------------------------------------------------------------------------------|--------------------|---------|---------|

| AC ACCURA | ACY                                              |                                                                                    |                    |         |         |

| NSD       | Noise Spectral Density                           | f <sub>IN</sub> = 100 MHz, A <sub>IN</sub> = -20 dBFS                              |                    | 158.5   | dBFS/Hz |

| NF        | Noise Figure                                     | f <sub>IN</sub> = 100 MHz, A <sub>IN</sub> = -20 dBFS                              |                    | 22.5    | dB      |

|           |                                                  | f <sub>IN</sub> = 10 MHz                                                           |                    | 74.0    |         |

|           |                                                  | f <sub>IN</sub> = 70 MHz                                                           | 70                 | 73.8    |         |

| SNR       | Signal to noise ratio                            | f <sub>IN</sub> = 170 MHz                                                          |                    | 73.2    | dBFS    |

|           |                                                  | f <sub>IN</sub> = 300 MHz                                                          |                    | 71.6    |         |

|           |                                                  | f <sub>IN</sub> = 450 MHz                                                          |                    | 69.6    |         |

|           |                                                  | f <sub>IN</sub> = 10 MHz                                                           |                    | 72.1    |         |

|           |                                                  | f <sub>IN</sub> = 70 MHz                                                           |                    | 71.9    |         |

| SINAD     | Signal to noise and distortion ratio             | f <sub>IN</sub> = 170 MHz                                                          |                    | 71.3    | dBFS    |

|           |                                                  | f <sub>IN</sub> = 300 MHz                                                          |                    | 69.7    |         |

|           |                                                  | f <sub>IN</sub> = 450 MHz                                                          |                    | 67.8    |         |

|           |                                                  | f <sub>IN</sub> = 10 MHz                                                           |                    | 11.7    |         |

|           |                                                  | f <sub>IN</sub> = 70 MHz                                                           |                    | 11.7    |         |

| ENOB      | Effective number of bits                         | f <sub>IN</sub> = 170 MHz                                                          |                    | 11.6    | Bits    |

|           |                                                  | f <sub>IN</sub> = 300 MHz                                                          |                    | 11.3    |         |

|           |                                                  | f <sub>IN</sub> = 450 MHz                                                          |                    | 11.0    |         |

|           | Total Harmonic Distortion (First five harmonics) | f <sub>IN</sub> = 10 MHz                                                           |                    | 74      | dBc     |

|           |                                                  | f <sub>IN</sub> = 70 MHz                                                           |                    | 77      |         |

| THD       |                                                  | f <sub>IN</sub> = 170 MHz                                                          |                    | 74      |         |

|           |                                                  | f <sub>IN</sub> = 300 MHz                                                          |                    | 68      |         |

|           |                                                  | f <sub>IN</sub> = 450 MHz                                                          |                    | 63      |         |

|           |                                                  | f <sub>IN</sub> = 10 MHz                                                           |                    | 76      | dBc     |

|           |                                                  | f <sub>IN</sub> = 70 MHz                                                           | 69                 | 82      |         |

| HD2       | Second Harmonic Distortion                       | f <sub>IN</sub> = 170 MHz                                                          |                    | 77      |         |

|           |                                                  | f <sub>IN</sub> = 300 MHz                                                          |                    | 81      |         |

|           |                                                  | f <sub>IN</sub> = 450 MHz                                                          |                    | 76      |         |

|           |                                                  | f <sub>IN</sub> = 10 MHz                                                           |                    | 88      |         |

|           |                                                  | f <sub>IN</sub> = 70 MHz                                                           | 71                 | 80      |         |

| HD3       | Third Harmonic Distortion                        | f <sub>IN</sub> = 170 MHz                                                          |                    | 83      | dBc     |

|           |                                                  | f <sub>IN</sub> = 300 MHz                                                          |                    | 71      |         |

|           |                                                  | f <sub>IN</sub> = 450 MHz                                                          |                    | 65      |         |

|           |                                                  | f <sub>IN</sub> = 10 MHz                                                           |                    | 94      |         |

|           |                                                  | f <sub>IN</sub> = 70 MHz                                                           |                    | 94      |         |

| Non HD2,3 | Spur free dynamic range (excluding               | f <sub>IN</sub> = 170 MHz                                                          |                    | 90      | dBFS    |

| ,-        | HD2 and HD3)                                     | f <sub>IN</sub> = 300 MHz                                                          |                    | 86      |         |

|           |                                                  | f <sub>IN</sub> = 450 MHz                                                          |                    | 87      |         |

| IMD3      | Two tone inter-modulation distortion             | f <sub>1</sub> = 100 MHz, f <sub>2</sub> = 120 MHz, A <sub>IN</sub> = -7 dBFS/tone |                    | 86      | dBc     |

<sup>(1)</sup> SNR and HD3 minimum values are specified by ATE; HD2 is specified by bench characterization.

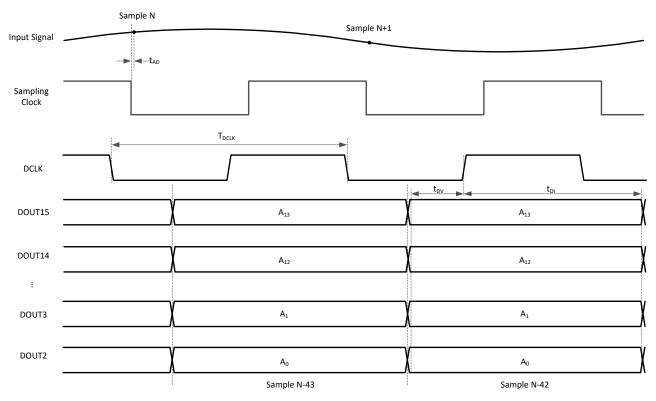

### 6.9 Timing Requirements

Maximum and minimum values are specified over the operating free-air temperature range and nominal supply voltages. Typical values are specified at  $T_A$  = 25°C, ADC sampling rate = 500 MSPS, DDC Bypass mode, 50% clock duty cycle, nominal supply voltages and -1-dBFS differential input, unless otherwise noted

|                        | PARAMETER                                                          | TEST CONDITIONS                                                                                | MIN                        | NOM                        | MAX                      | UNIT                      |  |

|------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------|----------------------------|--------------------------|---------------------------|--|

| ADC TIM                | ING SPECIFICATIONS                                                 |                                                                                                |                            |                            |                          |                           |  |

| T <sub>AD</sub>        | Aperture Delay                                                     |                                                                                                |                            | 200                        |                          | ps                        |  |

| T <sub>A</sub>         | Aperture Jitter                                                    |                                                                                                |                            | 75                         |                          | fs                        |  |

|                        |                                                                    | F <sub>S</sub> = 500 MSPS, Error > 256 codes                                                   |                            | 1E-10                      |                          |                           |  |

| CER                    | Code error rate                                                    | F <sub>S</sub> = 500 MSPS, Error > 512 codes                                                   |                            | 3E-13                      |                          | errors/<br>sample         |  |

|                        |                                                                    | F <sub>S</sub> = 250 MSPS, Error > 256 codes                                                   |                            | 1E-11                      |                          | Sample                    |  |

| Wake up                | time                                                               | time to valid data after coming out of global power down mode (internal voltage reference OFF) |                            | 3                          |                          | ms                        |  |

| LATENC                 | Y: t <sub>PD</sub> + t <sub>ADC</sub> + t <sub>DIG</sub>           |                                                                                                |                            |                            |                          |                           |  |

| t <sub>PD</sub>        | Propagation delay: sampling clock falling edge to DCLK rising edge | Propagation delay: sampling clock falling edge to DCLK rising edge                             | 1.4 +<br>T <sub>S</sub> /4 | 1.7 +<br>T <sub>S</sub> /4 | 2 +<br>T <sub>S</sub> /4 | ns                        |  |

|                        | 1001                                                               | SDR/DDR LVDS, normal mode                                                                      |                            | 38                         |                          | ADC                       |  |

| t <sub>ADC</sub>       | ADC latency                                                        | DDR LVDS, low latency mode                                                                     |                            | 4                          |                          | clock                     |  |

|                        | Time stamp: input to LVDS output                                   | SDR/DDR LVDS                                                                                   |                            | 8                          |                          | cycles                    |  |

|                        |                                                                    | DDC bypass                                                                                     |                            | 5                          |                          | Output<br>clock<br>cycles |  |

|                        |                                                                    | Decimation by 2 (real or complex)                                                              |                            | 24                         |                          |                           |  |

| t <sub>DIG</sub>       | Digital latency: interface and decimation                          | Decimation by 4,8 (real or complex)                                                            |                            | 49                         |                          |                           |  |

|                        |                                                                    | Decimation by 1632768 (real or complex)                                                        |                            | 50                         |                          |                           |  |

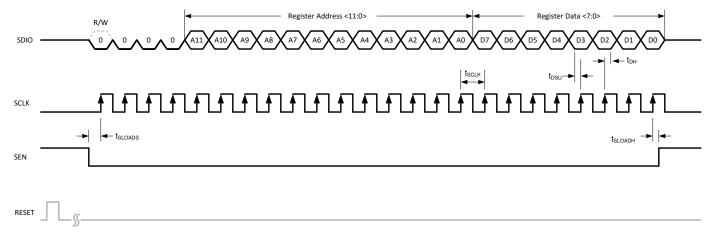

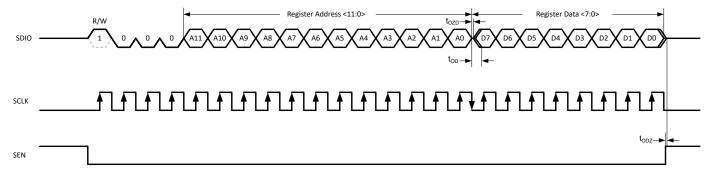

| SERIAL I               | ──<br>PROGRAMMING INTERFACE (SCLK, SEN, SD                         | DIO) - Input                                                                                   |                            |                            |                          |                           |  |

| f <sub>CLK(SCLK)</sub> | Serial clock frequency                                             | •                                                                                              | 1                          |                            | 20                       | MHz                       |  |

| t <sub>SLOADS</sub>    | Setup time from SEN falling edge to SCLK risi                      | 10                                                                                             |                            |                            | ns                       |                           |  |

| t <sub>SLOADH</sub>    | Hold time from SCLK rising edge to SEN rising                      | 10                                                                                             |                            |                            | ns                       |                           |  |

| t <sub>DSU</sub>       | Setup time from SDIO to rising edge of SCLK                        | 10                                                                                             |                            |                            | ns                       |                           |  |

| t <sub>DH</sub>        | Hold time from rising edge of SCLK to SDIO                         | 10                                                                                             |                            |                            | ns                       |                           |  |

|                        | PROGRAMMING INTERFACE (SDIO) - Output                              |                                                                                                |                            |                            |                          |                           |  |

| t <sub>(OZD)</sub>     | SDIO tri-state to driven                                           |                                                                                                |                            |                            | 10                       | ns                        |  |

| t <sub>(ODZ)</sub>     | SDIO data to tri-state                                             |                                                                                                |                            |                            | 14                       | ns                        |  |

| t <sub>(OD)</sub>      | SDIO valid from falling edge of SCLK                               |                                                                                                |                            |                            | 10                       | ns                        |  |

| TIMING:                |                                                                    |                                                                                                |                            | -                          |                          |                           |  |

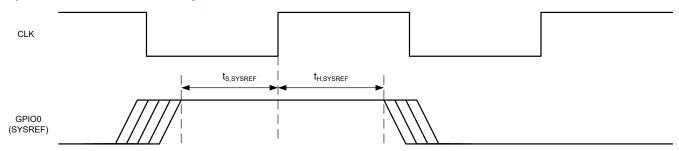

| t <sub>s(SYSREF)</sub> |                                                                    | LKP/M                                                                                          | 100                        |                            |                          | ps                        |  |

| t <sub>h(SYSREF)</sub> |                                                                    |                                                                                                | 100                        |                            |                          | ps                        |  |

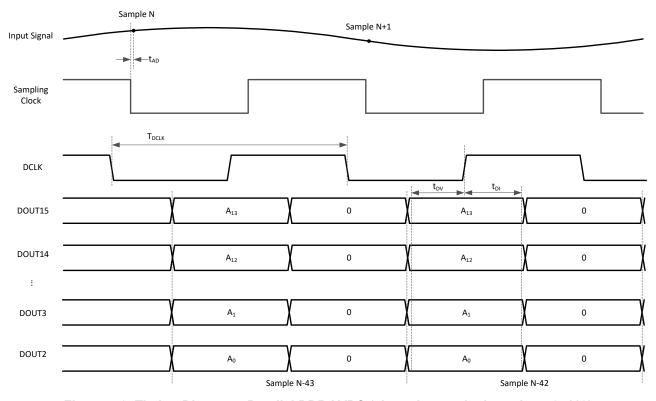

|                        | CE TIMING: SDR LVDS                                                |                                                                                                |                            | -                          |                          |                           |  |

|                        | Time Data Valid: data transition to DCLK                           | F <sub>S</sub> = 500 MSPS                                                                      | 0.465                      | 0.68                       | 0.905                    | ns                        |  |

| $t_{DV}$               | rising edge                                                        | F <sub>S</sub> = 250 MSPS                                                                      | 0.905                      |                            | 1.415                    | ns                        |  |

| t <sub>DI</sub>        |                                                                    | F <sub>S</sub> = 500 MSPS                                                                      | 1.095                      |                            | 1.495                    | ns                        |  |

|                        | Time Data Invalid : DCLK rising edge to data transition            | F <sub>S</sub> = 250 MSPS                                                                      | 2.615                      |                            | 3.015                    | ns                        |  |

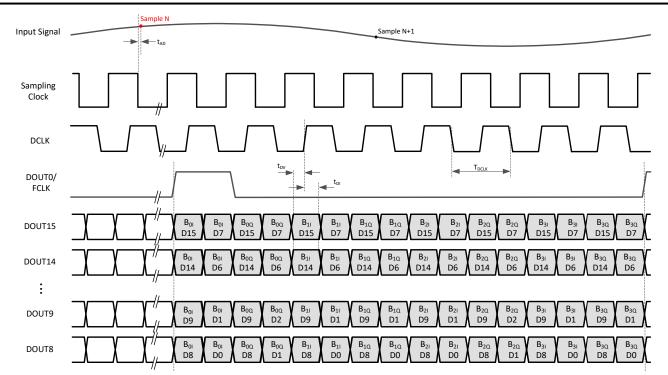

| INTERFA                | LCE TIMING: DDR AND SLVDS                                          | . 5 _555. 5                                                                                    |                            |                            | 5.5.0                    |                           |  |

|                        | T                                                                  | F <sub>S</sub> = 500 MSPS                                                                      | 0.465                      | 0.68                       | 0.905                    | ns                        |  |

| $t_{DV}$               | Time Data Valid: data transition to DCLK transition                | F <sub>S</sub> = 250 MSPS                                                                      | 0.403                      |                            | 1.415                    | ns                        |  |

| -Dv tr                 |                                                                    | 1 5 200 INIOI O                                                                                | 0.900                      | 1.10                       | 1.713                    | 113                       |  |

|                        | Time Data Invalid : DCLK transition to data                        | $F_S = 500 \text{ MSPS}$                                                                       | 0.095                      | ი ვე                       | 0.535                    | ns                        |  |

Submit Document Feedback

Copyright © 2025 Texas Instruments Incorporated

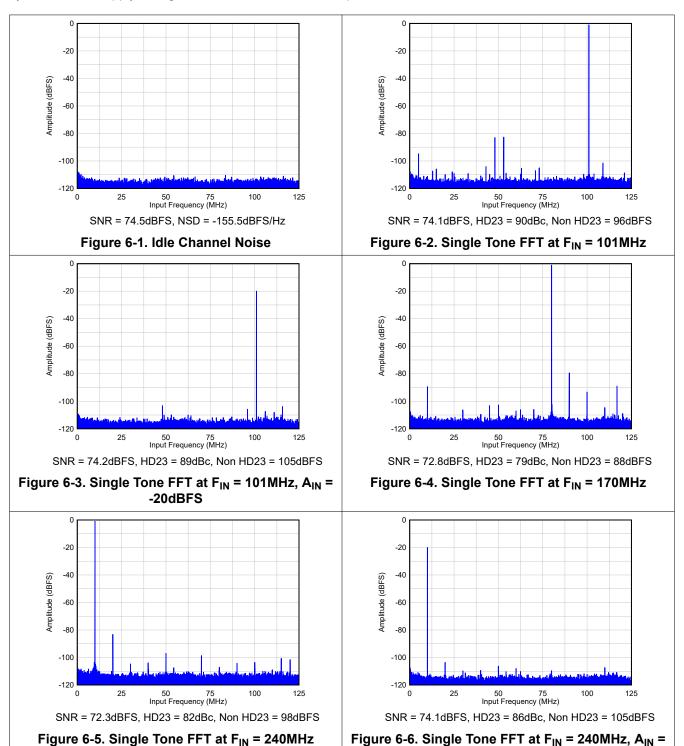

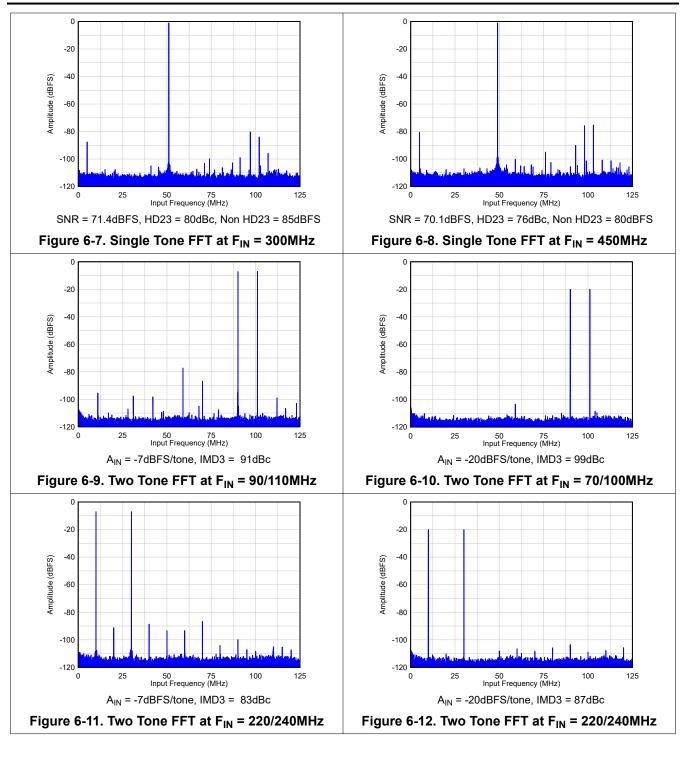

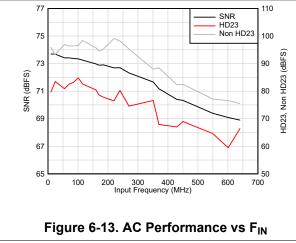

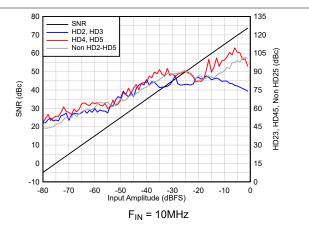

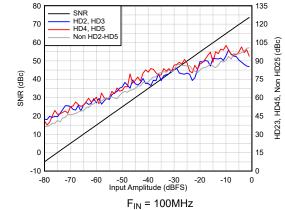

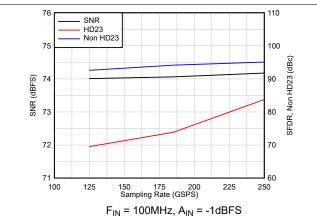

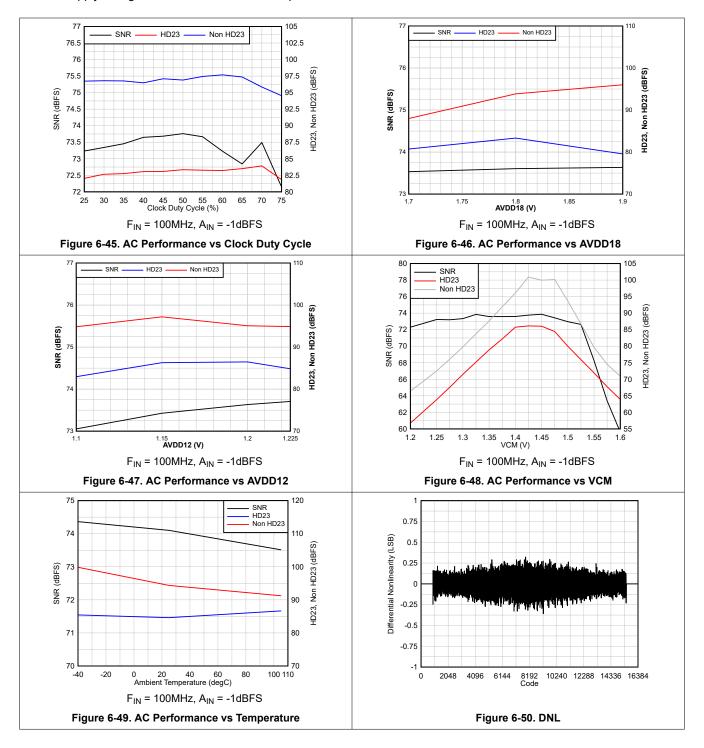

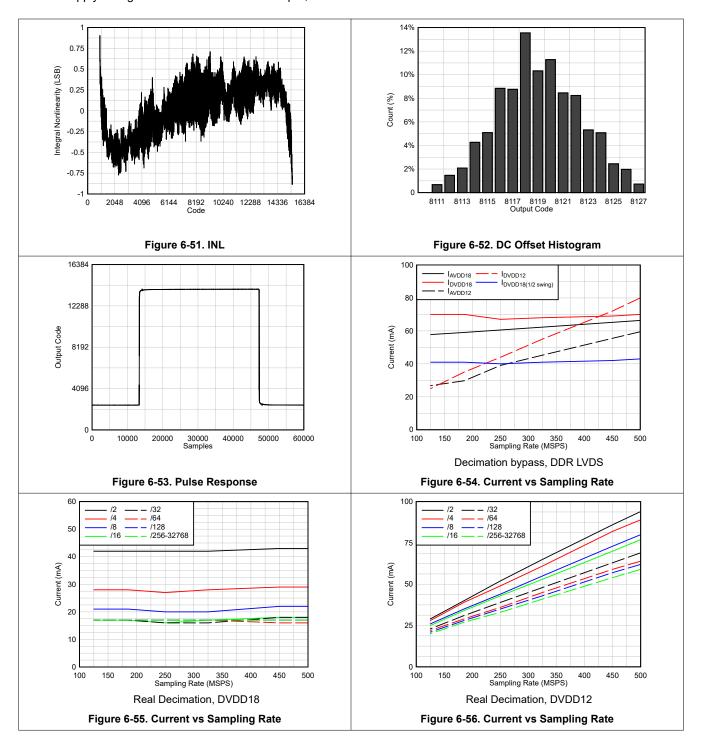

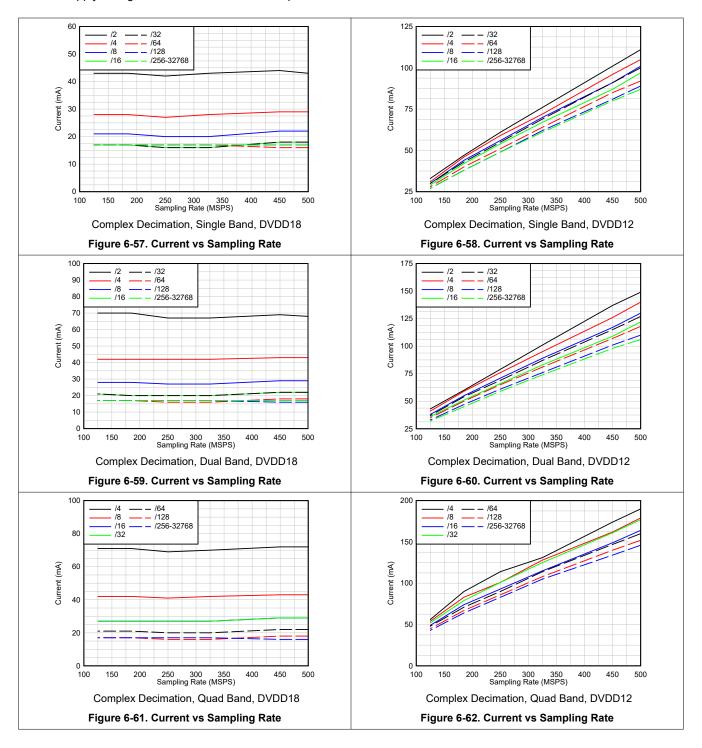

### 6.10 Typical Characteristics - ADC3548 (250MSPS)

Figure 6-14. AC Performance vs A<sub>IN</sub>

Figure 6-15. AC Performance vs AIN

Figure 6-16. AC Performance vs F<sub>S</sub>

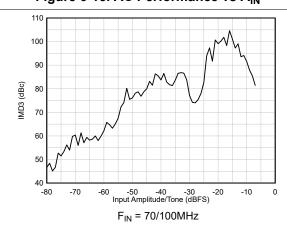

Figure 6-17. IMD3 vs A<sub>IN</sub>

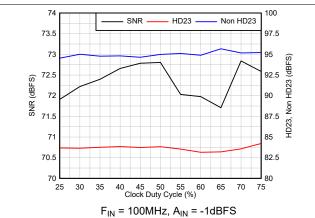

Figure 6-18. AC Performance vs Clock Duty Cycle

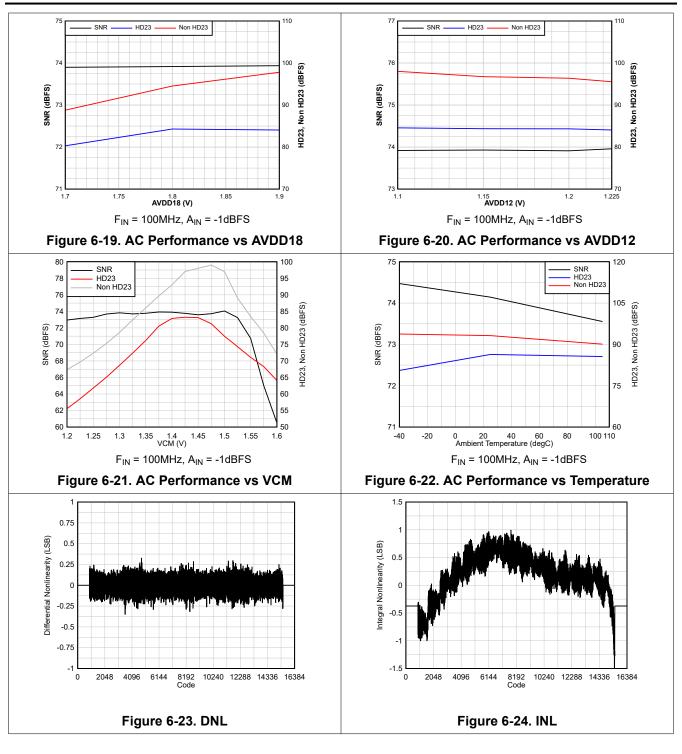

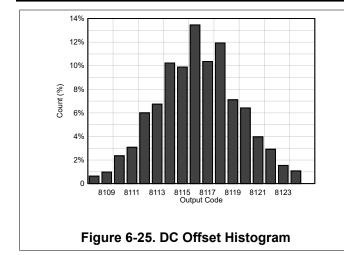

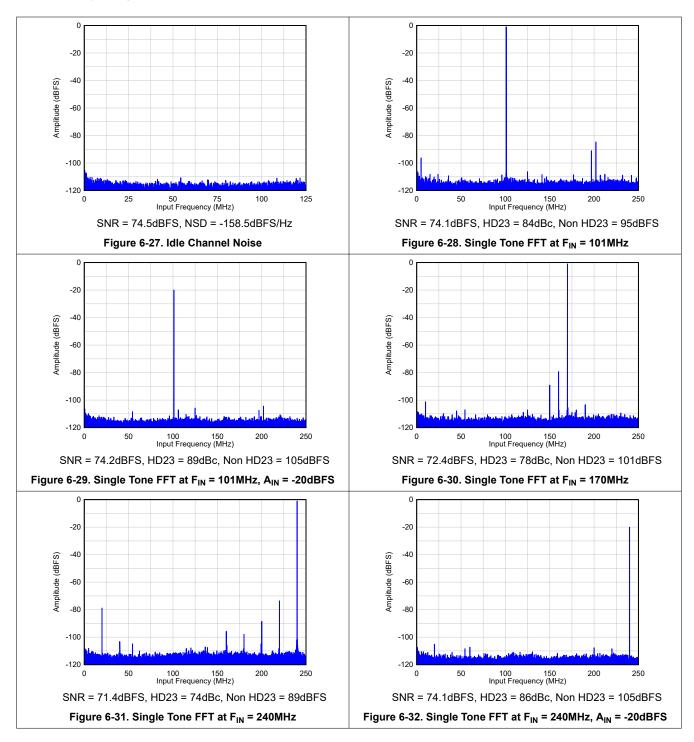

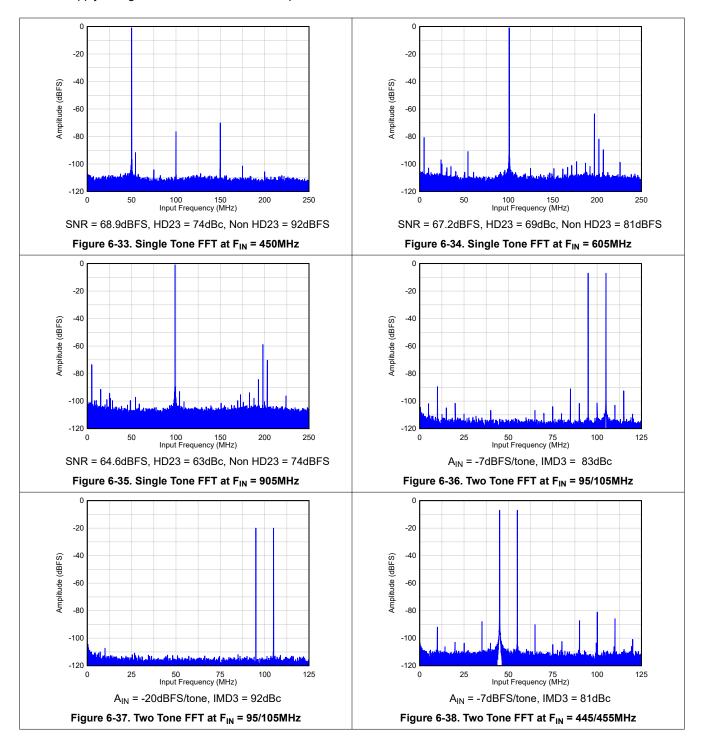

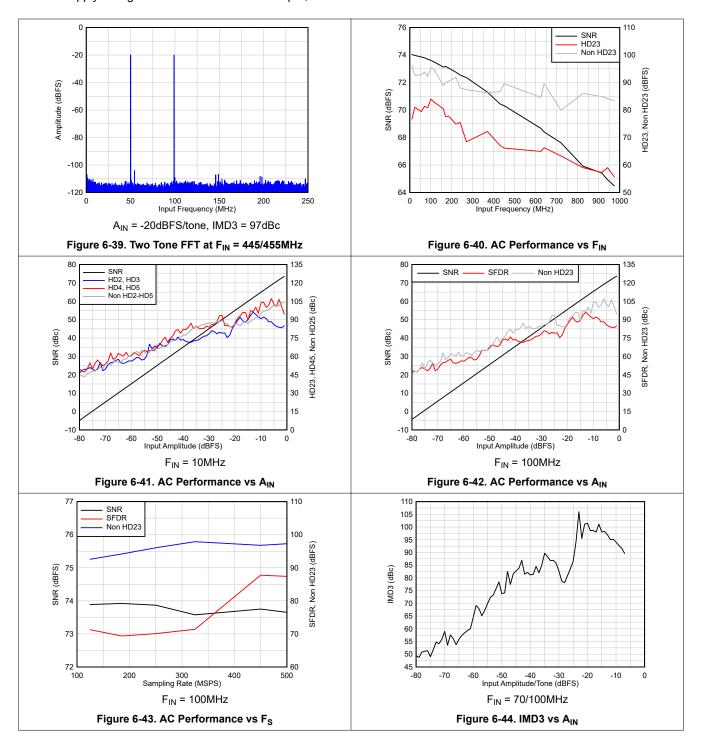

## 6.11 Typical Characteristics - ADC3549 (500MSPS)

Typical values are specified at  $T_A$  = 25°C, ADC sampling rate = 500MSPS, DDC bypass mode, 50% clock duty cycle, nominal supply voltages and -1dBFS differential input, unless otherwise noted

Submit Document Feedback

Copyright © 2025 Texas Instruments Incorporated

## 7 Parameter Measurement Information

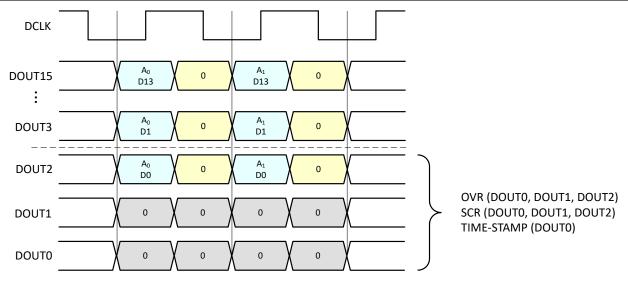

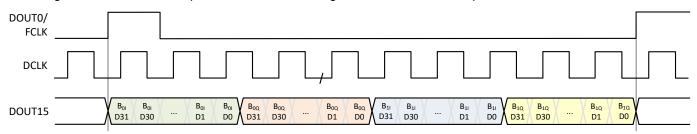

Figure 7-1. Timing Diagram - Parallel SDR LVDS (default)

Figure 7-2. Timing Diagram - Parallel DDR LVDS (via register write in register 0x110)

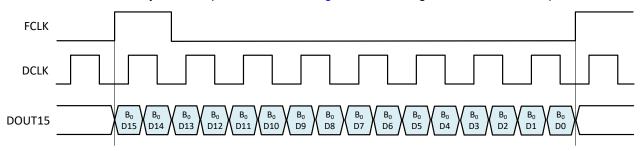

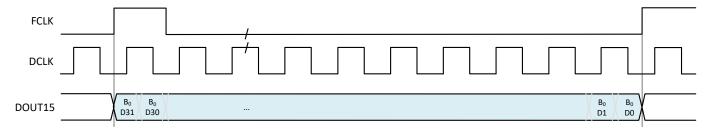

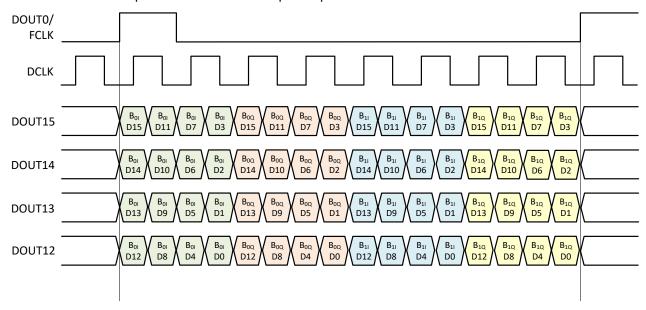

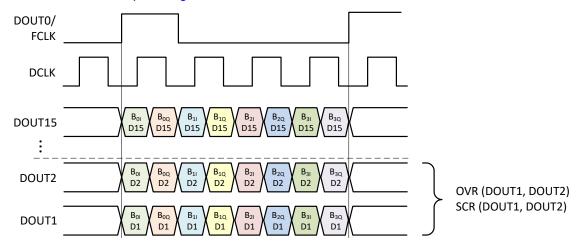

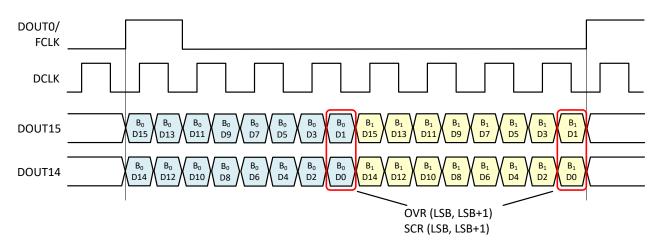

Figure 7-3. Timing Diagram - Serial LVDS (example: quad band, 16-bit, complex decimation by 8)

## 8 Detailed Description

#### 8.1 Overview

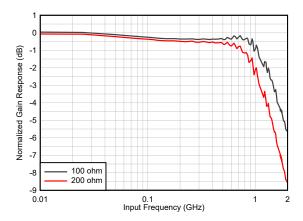

The ADC354x is a 14-bit, 250 to 500MSPS, single channel analog to digital converter (ADC). The device is designed for high signal-to-noise ratio (SNR) and delivers a noise spectral density as low as -158.5dBFS/Hz. The buffered analog inputs support a programmable internal termination impedance of  $100\Omega$  and  $200\Omega$  with a full power input bandwidth of 1.4GHz (-3dB).

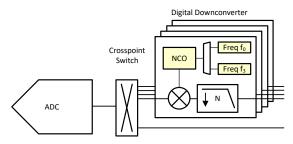

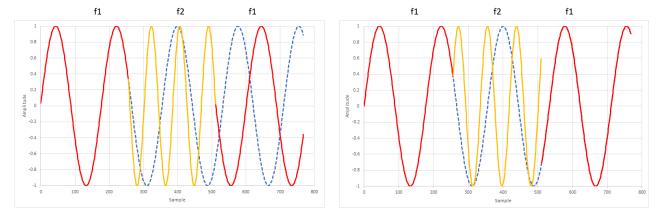

The ADC354x includes a quad band digital down-converter (DDC) supporting wideband decimation by 2 to narrow band decimation by 32768. The DDC uses a 48-bit NCO which supports phase coherent and phase continuous frequency hopping.

The ADC354x is outfitted with a flexible LVDS interface. In decimation bypass mode, the output data is transmitted over 14 LVDS pairs with a SDR or DDR clock. When using real or complex decimation, the output data is transmitted using a serial LVDS interface. Reducing the number of lanes used as decimation increases.

The power efficient ADC architecture consumes 435mW at 500MSPS and provides power scaling with lower sampling rates (369mW at 250MSPS).

#### 8.2 Functional Block Diagram

Figure 8-1. Block Diagram

### 8.3 Feature Description

#### 8.3.1 Analog Inputs

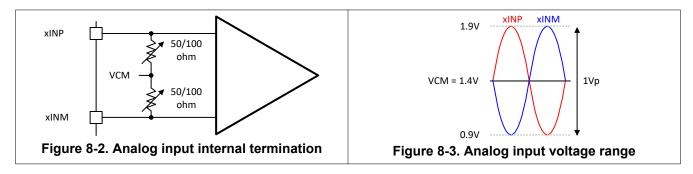

The analog inputs of the ADC354x have internal buffers which isolates the sampling capacitor glitch noise from the external input circuitry. The analog inputs have a differential  $100\Omega$  split termination with internal biasing as shown in Figure 8-2. This can be changed to differential  $200\Omega$  termination via SPI register write.

The input fullscale is 2Vpp and the VCM is 1.4V; thus, the voltage on the analog inputs swing between 0.9V and 1.9V. The ADC inputs are reliably designed to support 1.9V for normal operation.

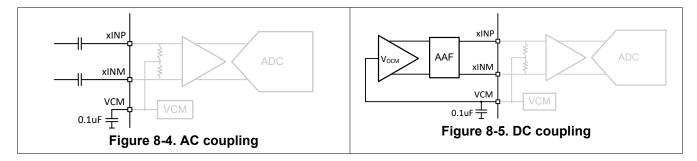

The device supports both AC and DC coupling of the analog inputs as shown in Figure 8-4 and Figure 8-5.

The input bandwidth (-3 dB) for internal  $100\Omega$  and  $200\Omega$  termination are shown in Figure 8-6.

Figure 8-6. Full power input bandwidth for  $100\Omega$  and  $200\Omega$  internal termination

#### 8.3.1.1 Nyquist Zone Selection

The ADC includes a digital error correction which is optimized based on which Nyquist zone the signal of interest is in. For optimum performance the correct input frequency range (register 0x132) and Nyquist zone have to be selected in the SPI register map (register 0x16B). By default the first Nyquist zone is selected.

#### 8.3.1.2 Analog Front End Design

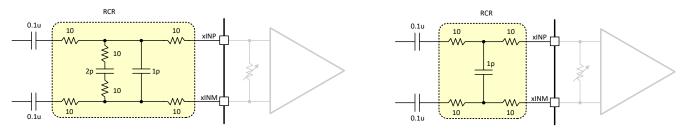

To optimize SNR and HD3 performance of the ADC, the recommendation is to add a RCR circuitry directly in front of the analog input. Figure 8-7 shows the recommended RCR circuitry for input frequencies less and greater than 500MHz (example shows AC coupling but same applies to DC coupling), assuming a  $50\Omega$  source impedance. If the ADC is driven by an external amplifier, the RCR circuitry may not be needed.

Figure 8-7. External RCR for  $F_{IN}$  < 500MHz (left) and  $F_{IN}$  > 500MHz (right)

#### 8.3.2 Sampling Clock

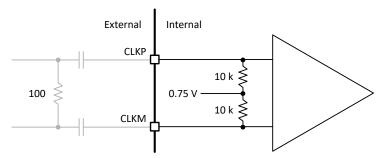

The sampling clock input is designed to be driven differentially with external AC coupling and termination. The ADC provides internal common mode voltage biasing as shown in Figure 8-8.

Figure 8-8. Sampling Clock Input Circuitry

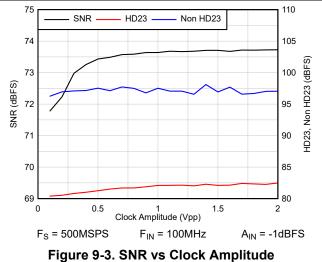

The internal sampling clock path was designed for low residual phase noise contribution. The sampling clock circuitry requires a dedicated, low noise power supply for best phase noise and jitter performance. The internal residual clock phase noise is also sensitive to clock amplitude.

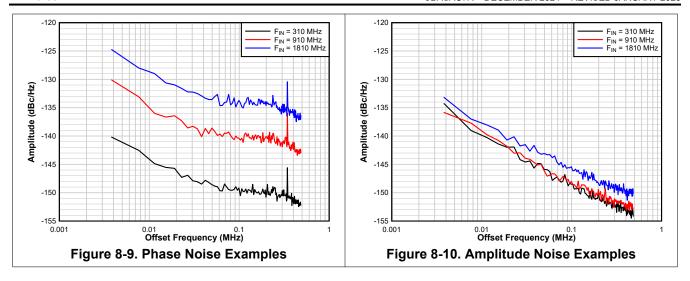

The internal residual clock noise consists of two components - phase noise and amplitude noise as shown in Table 8-1. The phase noise scales with input frequency and sampling rate  $(20*log(f_{IN}/F_S))$  while the amplitude noise does not scale.

| rabio o ni i naco ana / impirtado i toto at oconiniz |                      |                          |  |  |  |  |  |

|------------------------------------------------------|----------------------|--------------------------|--|--|--|--|--|

| Frequency Offset (MHz)                               | Phase Noise (dBc/Hz) | Amplitude Noise (dBc/Hz) |  |  |  |  |  |

| 0.001                                                | -130                 | -129                     |  |  |  |  |  |

| 0.01                                                 | -140                 | -139                     |  |  |  |  |  |

| 0.1                                                  | -150                 | -149                     |  |  |  |  |  |

| 1                                                    | -160                 | -159                     |  |  |  |  |  |

| 3                                                    | -165                 | -164                     |  |  |  |  |  |

| 10                                                   | -165                 | -164                     |  |  |  |  |  |

Table 8-1. Phase and Amplitude Noise at 500MHz

Figure 8-9 and Figure 8-10 show the phase and amplitude noise at three different input frequencies.

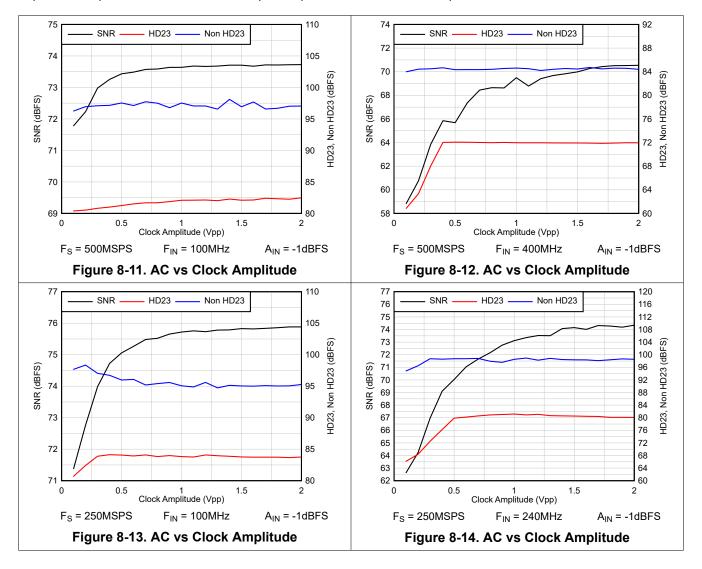

The internal clock noise is also dependent on the external clock amplitude. Figure 8-11 to Figure 8-14 show the expected AC performance for different input frequencies across clock amplitude.

#### 8.3.2.1 Multi-Chip Synchronization

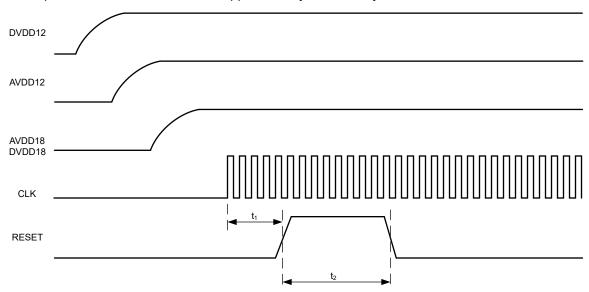

The device provides an option to achieve deterministic latency to ease synchronization across multiple devices, depending on operating mode:

- DDC Bypass mode: The device inherently already has deterministic latency. External multi-chip synchronization is accomplished by matching clock traces across devices. However, the internal RAMP test pattern can be reset using the SYSREF signal.

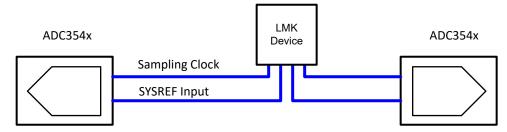

- DDC mode: Internal blocks related to the decimation filter (clock dividers, NCO phase, and so on) are reset to a deterministic state using the SYSREF signal. External multi-chip synchronization is accomplished by matching both clock and SYSREF signal traces (blue lines) across devices as shown in Figure 8-15.

Figure 8-15. Synchronization example of 2 devices

The GPIO0 pin can be configured as a synchronization input. A single pulse can be applied for multi-chip synchronization as shown in Figure 8-16.

Figure 8-16. Timing: external synchronization input

In the SPI register map there are several different synchronization masks available to reset only specific blocks such as the NCO phase.

Table 8-2. Example register writes for external SYSREF config

| ADDR  | DATA | DESCRIPTION                         |

|-------|------|-------------------------------------|

| 0x146 | 0x00 | Configure pin GPIO0 as SYSREF input |

Submit Document Feedback

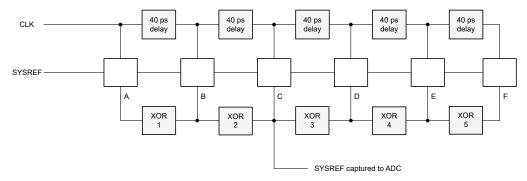

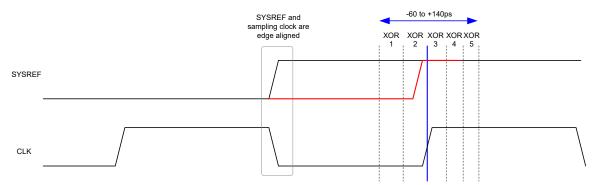

#### 8.3.2.2 SYSREF Monitor

The SYSREF input signal rising edge must be edge aligned with the falling edge of the sampling clock to maximize the setup and hold times. The SYSREF signal is internally sampled on the rising edge of the sampling clock plus 60ps.

The device includes an internal SYSREF monitoring circuitry to detect a possible SYSREF logic level metastability close to the sampling instant of SYSREF which can lead to misalignment across devices. The SYSREF monitoring circuitry provides insights into SYSREF/clock misalignment by detecting whether a SYSREF logic state transition is within -60ps to +140ps of the sampling clock rising edge. This circuitry detects and raises one of the SYSREF XOR flags corresponding to the matching SYSREF window below:

- Window XOR1: SYSREF leading sample clock by 20 to 60ps

- Window XOR2: SYSREF leading sample clock by 20ps to 0ps or SYSREF lagging sample clock by 0 to 20ps

- Window XOR3: SYSREF lagging sample clock by up to 20 to 60ps

- Window XOR4: SYSREF lagging sample clock by 60 to 100ps

- Window XOR5: SYSREF lagging sample clock by 100 to 140ps

The SYSREF monitor registers are updated at every rising edge of SYSREF. The <SYSREF DET> register (D6) is sticky (indicating a SYSREF edge was detected) and needs to be cleared manually.

Figure 8-17. SYSREF Detection Circuitry

The example in Figure 8-18 shows a misaligned SYSREF signal where the SYSREF signal arrives much later than the sampling clock falling edge. In this example, the delayed SYSREF signal transitions between the "B" and "C" flip flop which raises the XOR2 flag. The XOR flags get reported in register 0x140. In this example, Register 0x140 reads back 0x62, as shown in Table 8-3.

Figure 8-18. Detection of SYSREF Transition Within Capture Window

Table 8-3. SYSREF Window Register Example (0x140)

| ADDR  | D7 | D6         | D5        | D4        | D3        | D2        | D1        | D0        |

|-------|----|------------|-----------|-----------|-----------|-----------|-----------|-----------|

| 0x140 | 0  | SYSREF DET | SYSREF OR | SYSREF X5 | SYSREF X4 | SYSREF X3 | SYSREF X2 | SYSREF X1 |

|       | 0  | 1          | 1         | 0         | 0         | 0         | 1         | 0         |

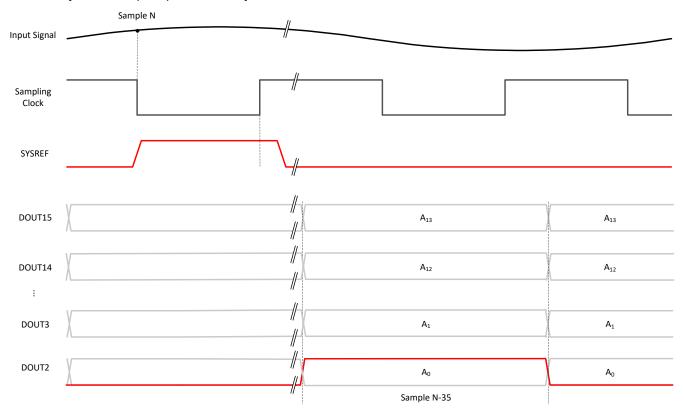

#### 8.3.3 Time-Stamp

The ADC354x includes a time-stamp feature which enables tagging a specific sample on the analog input in DDC bypass mode. When enabling the feature (via SPI write), a logic low-to-high transition on the GPIO/SYSREF pin is registered on the rising edge of the sampling clock. The time stamp signal is output on the lane DOUT2 (LSB) however it is not latency matched with the output data. The time-stamp feature is available with SDR and DDR LVDS.

As shown in Figure 8-19the time stamp signal is indicated 35 clock cycles ahead of the output data:

- Latency output data: 43 clock cycles

- Latency time stamp output: 8 clock cycles

Figure 8-19. Timing Diagram - Time-Stamp Output with SDR LVDS

Table 8-4. Example register writes to enable time stamp on pin GPIO0

| ADDR  | DATA | DESCRIPTION                                   |  |  |  |

|-------|------|-----------------------------------------------|--|--|--|

| 0x146 | 0x00 | Enable SYSREF on pin GPIO0.                   |  |  |  |

| 0x162 | 0xC0 | Enable time stamp function replacing the LSB. |  |  |  |

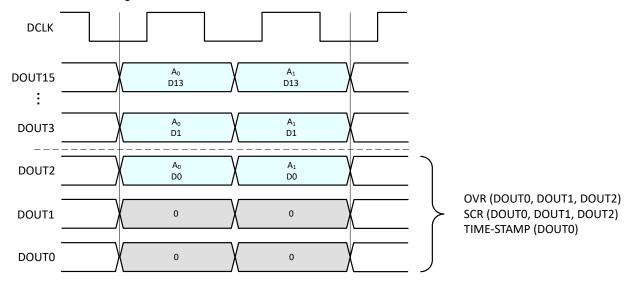

#### 8.3.4 Overrange

The device triggers the overrange indicator when the signal crosses the representable digital range. The overrange output can be configured in registers 0x10A/0x10B. The latency of the OVR indication is equal or less than the data latency.

The OVR can be indicated in two different ways:

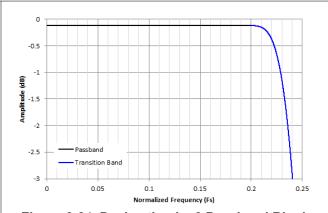

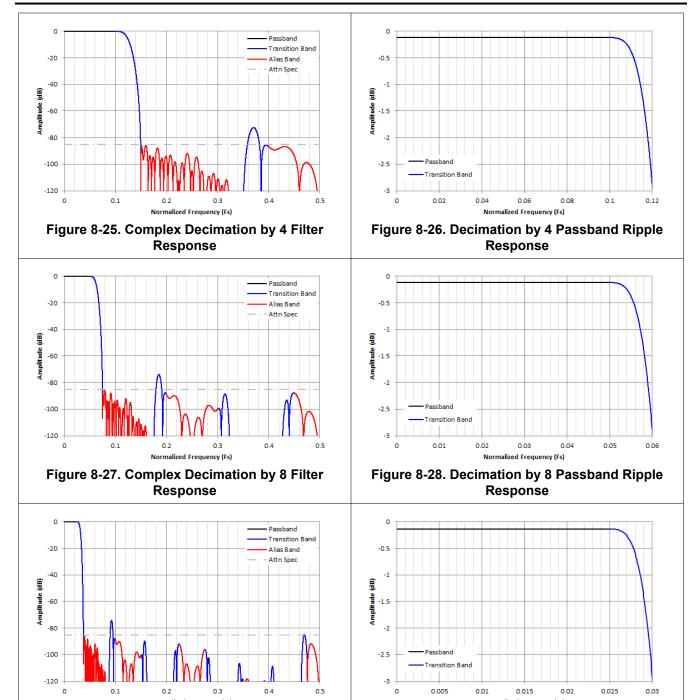

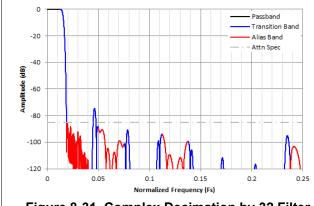

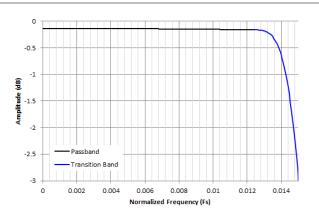

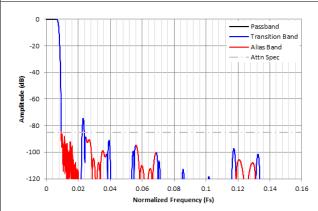

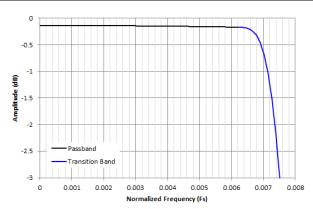

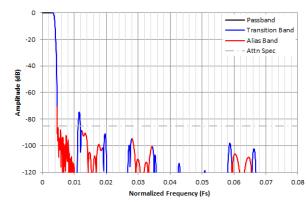

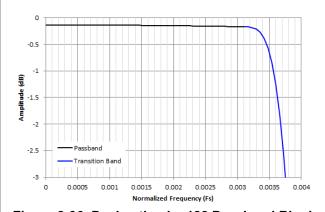

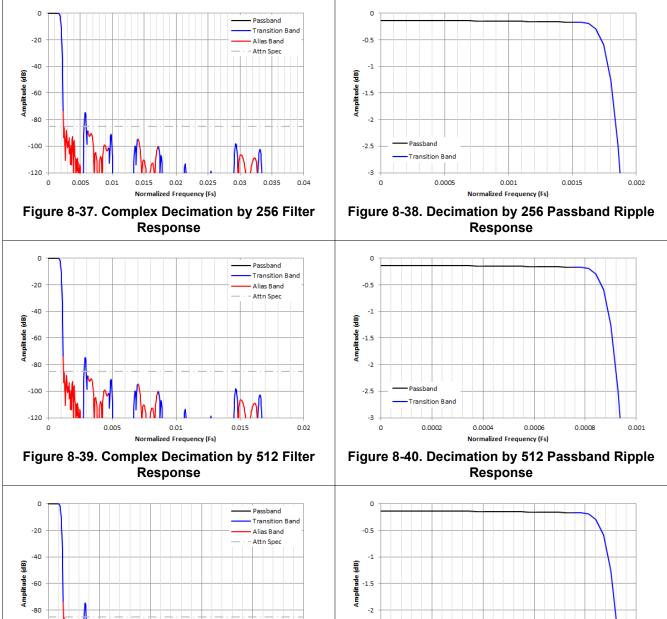

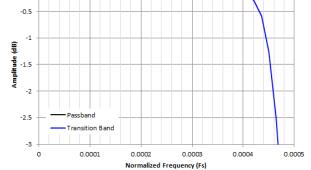

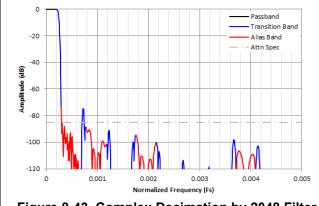

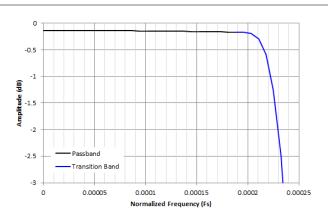

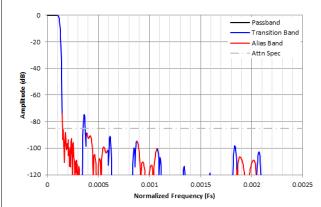

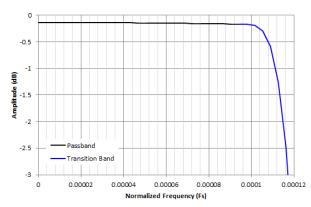

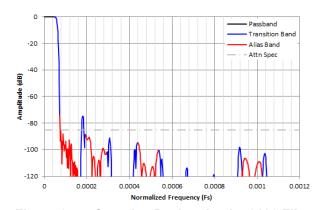

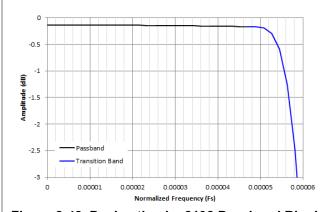

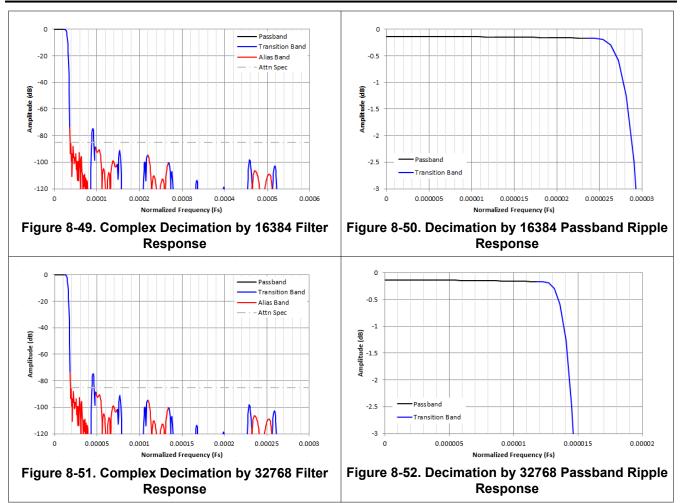

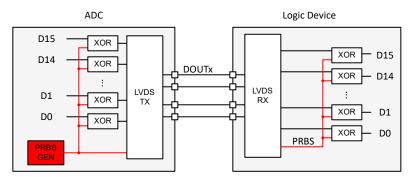

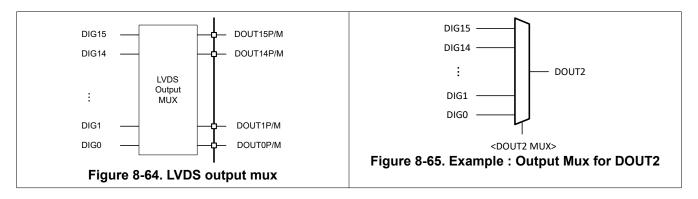

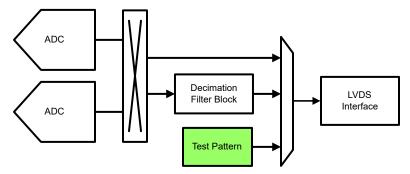

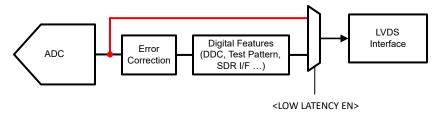

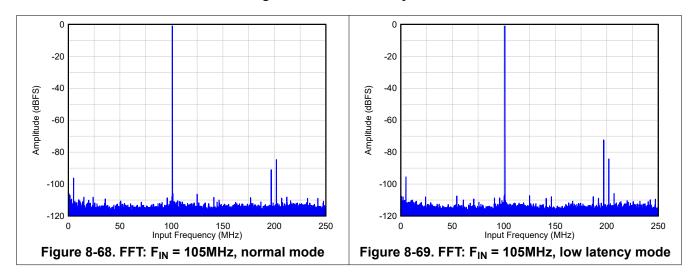

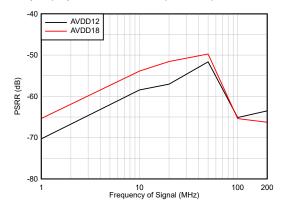

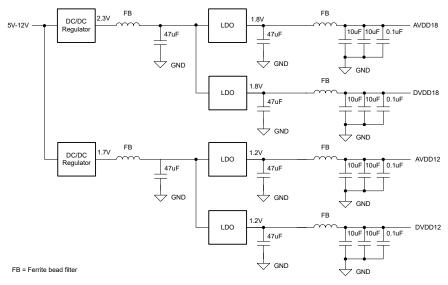

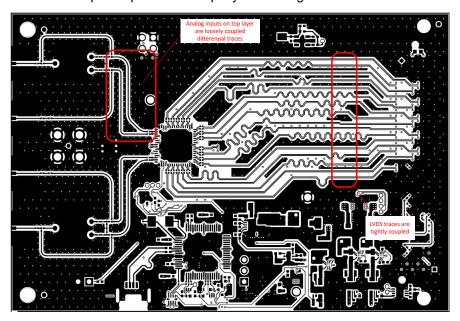

- GPIO pin: can be configured using register 0x146