ADC12D1620QML-SP JAJSDJ8A - APRIL 2017 - REVISED OCTOBER 2021

# ADC12D1620QML-SP 12 ビット、シングルまたはデュアル、3200 または 1600MSPS RF サンプリング A/D コンバータ (ADC)

# 1 特長

- 総照射線量 (TID) 耐性 = 300krad (Si)

- シングル・イベント機能割り込み (SEFI) テスト済み

- シングル・イベント・ラッチアップ耐性:120MeVcm<sup>2</sup>/mg 超

- コールド・スペア対応

- 広い温度範囲:-55℃~+125℃

- 消費電力 = 3.8W または 2.7W (1600 または ٠ 800MHz クロック)

- 3dB 入力帯域幅 = 3GHz

- 低サンプリング・パワー・セービング・モード (LSPSM) により、f<sub>CLK</sub> ≤ 800 MHz について消費電力を低減し性 能を向上

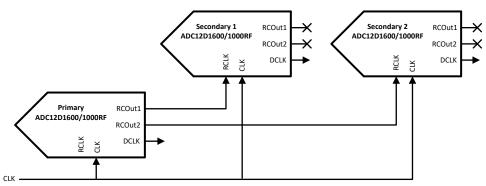

- マルチチップ・システム用の自動同期機能 •

- タイム・スタンプ機能により外部トリガをキャプチャ

- システム・デバッグ用にテスト・パターンを出力

- 1:1 非デマルチプレクス、または 1:2 もしくは 1:4 の並 列デマルチプレクスの LVDS 出力

- 1.9V 単一電源

# 2 アプリケーション

- 直接 RF ダウン変換

- 広帯域衛星通信

- 合成開口レーダーおよび LIDAR

# 3 概要

ADC12D1620QML は、パッケージの再設計により、 ADC12D1600QML と比較して ENOB、SNR、クロストー クが改良されています。前世代の製品と同様に、 ADC12D1620QML は低消費電力、高性能の CMOS A/D コンバータ (ADC) であり、インターリーブ・モードにお いて最高 3.2GSPS のサンプリング・レートと 12 ビットの 分解能で信号をデジタル化します。また、デュアル・チャネ ル ADC として、最高 1.6GSPS のサンプリング・レートで も使用できます。サンプリング・レートが 800MHz 未満の 場合、低サンプリング・パワー・セービング・モード (LSPSM) により、消費電力が 1 チャネルあたり 1.4W 未 満 (標準値) に低減されます。この ADC は、最低で 200MSPS の変換レートをサポートできます。

| 製品情報                |                               |            |  |  |  |  |  |

|---------------------|-------------------------------|------------|--|--|--|--|--|

| 部品番号 <sup>(1)</sup> | グレード                          | パッケージ      |  |  |  |  |  |

| 5962F1220502VXF     | SMD フライト 300 krad(Si)         | CCGA (376) |  |  |  |  |  |

| ADC12D1620CCMLS     | フライト 300 krad(Si)             | CCGA (376) |  |  |  |  |  |

| ADC12D1620CCMPR     | プリフライトのエンジニアリン<br>グ・プロトタイプ    | CCGA (376) |  |  |  |  |  |

| ADC10D1000DAISY     | デイジー・チェーン、メカニ<br>カル・サンプル、ダイなし | CCGA (376) |  |  |  |  |  |

| ADC12D1620LGMLS     | フライト 300 krad(Si)             | CLGA (256) |  |  |  |  |  |

| ADC12D1620LGMPR     | プリフライトのエンジニアリン<br>グ・プロトタイプ    | CLGA (256) |  |  |  |  |  |

| ADC10D1000LDAZ      | デイジー・チェーン、メカニ<br>カル・サンプル、ダイなし | CLGA (256) |  |  |  |  |  |

利用可能なすべてのパッケージについては、このデータシートの (1) 末尾にあるパッケージ注文情報の付録 (POA) を参照してくださ 3

英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、 🐼 www.ti.com で閲覧でき、その内容が常に優先されます。 TI では翻訳の正確性および妥当性につきましては一切保証いたしません。 実際の設計などの前には、必ず 最新版の英語版をご参照くださいますようお願いいたします。

# **Table of Contents**

| 1 特長                                                                                     | 1  |

|------------------------------------------------------------------------------------------|----|

| 2 アプリケーション                                                                               | .1 |

| 3 概要                                                                                     |    |

| 4 Revision History                                                                       |    |

| 5 Pin Configuration and Functions                                                        |    |

| 6 Specifications                                                                         |    |

| 6.1 Absolute Maximum Ratings                                                             | 12 |

| 6.2 ESD Ratings                                                                          | 12 |

| 6.3 Recommended Operating Conditions                                                     | 13 |

| 6.4 Thermal Information                                                                  |    |

| 6.5 Converter Electrical Characteristics: Static                                         |    |

| Converter Characteristics                                                                | 4  |

| 6.6 Converter Electrical Characteristics: Dynamic                                        |    |

| Converter Characteristics                                                                | 15 |

| 6.7 Converter Electrical Characteristics: Analog                                         |    |

| Input/Output and Reference Characteristics                                               | 17 |

| 6.8 Converter Electrical Characteristic: Channel-to-                                     |    |

| Channel Characteristics                                                                  | 8  |

| 6.9 Converter Electrical Characteristics: LVDS CLK                                       |    |

| Input Characteristics                                                                    |    |

| 6.10 Electrical Characteristics: AutoSync Feature                                        | 9  |

| 6.11 Converter Electrical Characteristics: Digital                                       |    |

| Control and Output Pin Characteristics                                                   | 19 |

| 6.12 Converter Electrical Characteristics: Power                                         |    |

| Supply Characteristics                                                                   | 21 |

| 6.13 Converter Electrical Characteristics: AC                                            | 22 |

| Electrical Characteristics                                                               |    |

|                                                                                          |    |

| 6.15 Timing Requirements: Serial Port Interface<br>6.16 Timing Requirements: Calibration |    |

| 6.17 Quality Conformance Inspection                                                      |    |

|                                                                                          | 10 |

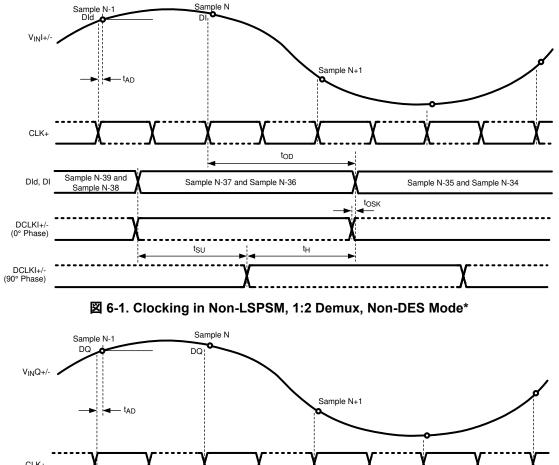

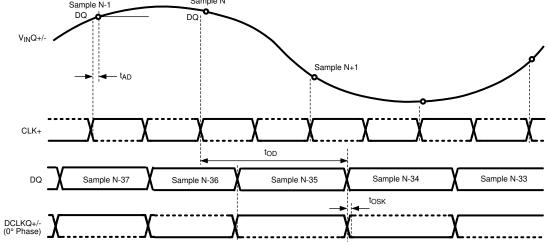

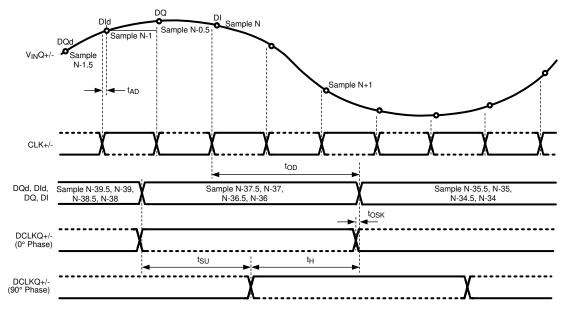

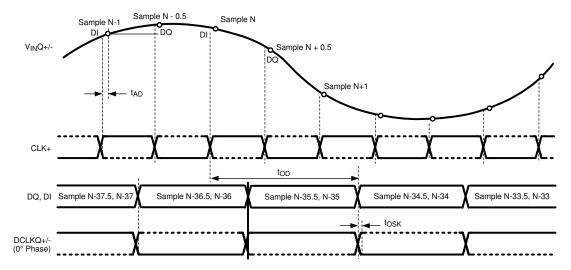

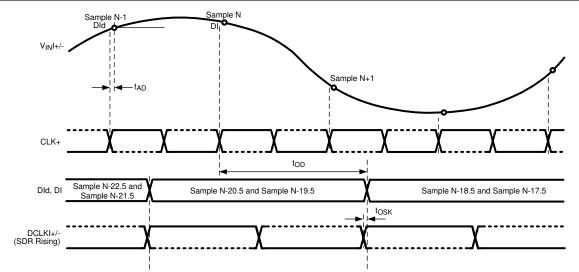

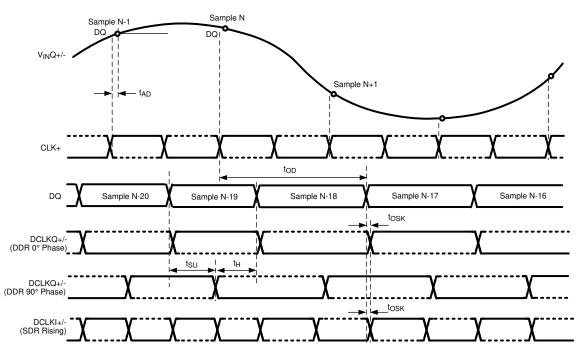

| 6.18 Timing Diagrams                    | <mark>27</mark> |

|-----------------------------------------|-----------------|

| 6.19 Typical Characteristics            | 32              |

| 7 Detailed Description                  |                 |

| 7.1 Overview                            |                 |

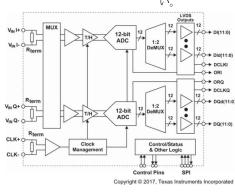

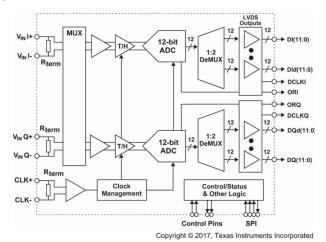

| 7.2 Functional Block Diagram            | 37              |

| 7.3 Feature Description                 |                 |

| 7.4 Device Functional Modes             | 46              |

| 7.5 Programming                         |                 |

| 7.6 Register Maps                       | <mark>52</mark> |

| 8 Application Information Disclaimer    | 59              |

| 8.1 Application Information             | <mark>59</mark> |

| 8.2 Radiation Environments              | 66              |

| 8.3 Cold Sparing                        | 66              |

| 9 Power Supply Recommendations          | 68              |

| 9.1 System Power-On Considerations      | 68              |

| 10 Layout                               |                 |

| 10.1 Layout Guidelines                  | 69              |

| 10.2 Layout Example                     |                 |

| 10.3 Thermal Considerations             | <b>73</b>       |

| 10.4 Board Mounting Recommendation      | 73              |

| 11 Device and Documentation Support     | 75              |

| 11.1 Device Support                     | 75              |

| 11.2ドキュメントの更新通知を受け取る方法                  | 77              |

| 11.3 サポート・リソース                          |                 |

| 11.4 Trademarks                         |                 |

| 11.5 静電気放電に関する注意事項                      |                 |

| 11.6 用語集                                |                 |

| 12 Mechanical, Packaging, and Orderable |                 |

| Information                             | 78              |

| 12.1 Engineering Samples                |                 |

| g                                       |                 |

# **4 Revision History**

| Cł | hanges from Revision * (April 2017) to Revision A (October 2021)                                                 | Page |

|----|------------------------------------------------------------------------------------------------------------------|------|

| •  | 旧式の用語を使用している場合、文書全体にわたってプライマリおよびセカンダリに変更                                                                         | 1    |

| •  | 「 <i>製品情報</i> 」表に <b>5962F1220502VXF</b> を追加                                                                     | 1    |

| •  | Changed VinI+, VinI–, VinQ+, VinQ– voltage MIN value From: -0.15 V To: -0.5 in the Absolute Maximu Ratings table |      |

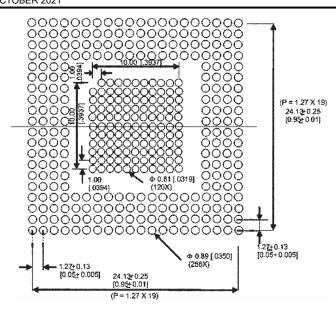

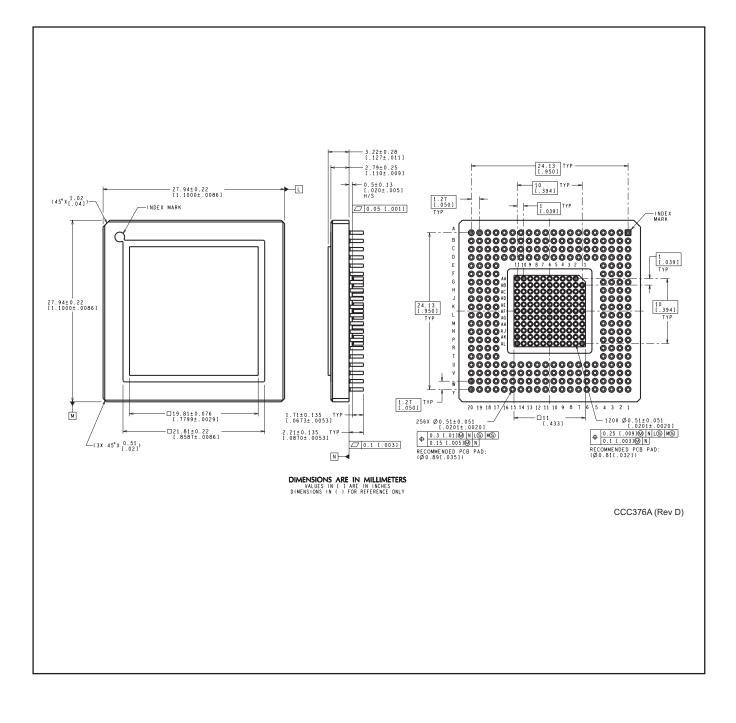

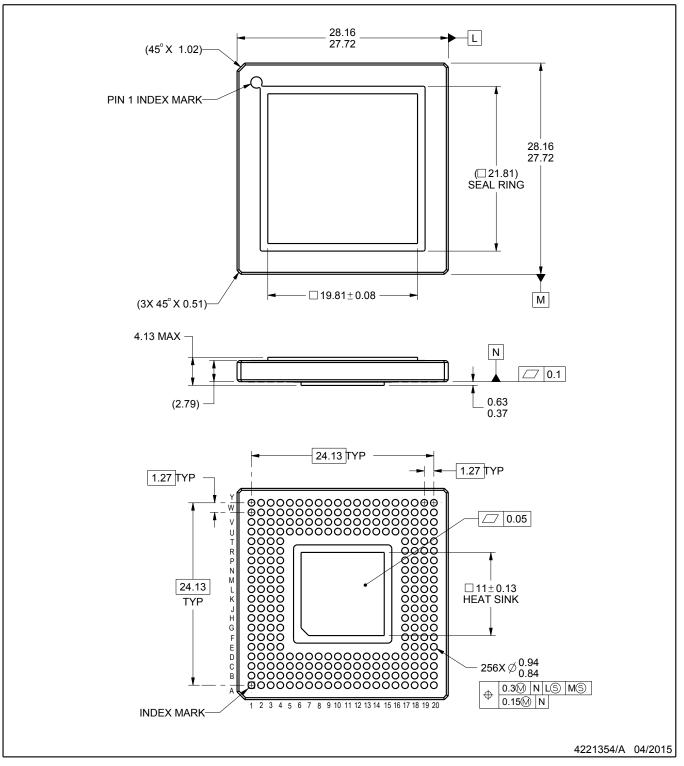

# **5** Pin Configuration and Functions

The center ground pins are for thermal dissipation and must be soldered to a ground plane to ensure rated performance. See *Layout Guidlines* for more information.

|   | 1             | 2             | 3                 | 4                  | 5             | 6                  | 7            | 8            | 9                  | 10                    | 11            | 12        | 13           | 14            | 15           | 16            | 17            | 18           | 19                  | 20          |    |

|---|---------------|---------------|-------------------|--------------------|---------------|--------------------|--------------|--------------|--------------------|-----------------------|---------------|-----------|--------------|---------------|--------------|---------------|---------------|--------------|---------------------|-------------|----|

| Α | GND           | V_A           | SDO               | ТРМ                | NDM           | V_A                | GND          | V_E          | GND_E              | Did0+                 | V_DR          | DId3+     | GND_DR       | DId6+         | V_DR         | DId9+         | GND_DR        | Did 11+      | DId 11-             | GND_DR      | A  |

| в | Vbg           | GND           | ECEb              | SDI                | CalRun        | V_A                | GND          | GND_E        | V_E                | Did0-                 | DId2+         | Did3-     | DId5+        | Did6-         | DId8+        | Did9-         | DId 10+       | D10+         | DI1+                | DI1-        | в  |

| с | Rtrim+        | Vcmo          | Rext+             | SCSb               | SCLK          | GND                | V_A          | V_E          | GND_E              | Did 1+                | Did2-         | DId4+     | Did 5-       | Did7+         | Did8-        | Did 10-       | D10-          | V_DR         | DI2+                | D12-        | с  |

| D | V_A           | Rtrim-        | Rext-             | GND                | GND           | CAL                | Vbiasl       | V_A          | V_A                | Did 1-                | V_DR          | DId4-     | GND_DR       | Did7-         | V_DR         | GND_DR        | V_DR          | DI3+         | D14+                | D14-        | D  |

| Е | V_A           | T diode+      | RSV1              | GND                |               | 1                  | 2            | 3            | 4                  | 5                     | 6             | 7 1       | 8 9          | 10            | 11           |               | GND_DR        | D13-         | D15+                | D15-        | Е  |

| F | A_V           | GND_TC        | T diode-          | RSV2               | АА            |                    | GND          | GND          | GND                | GND G                 | ND G          | ND GI     | ND GN        | D GNE         | GND          |               | GND_DR        | D16+         | D16-                | GND_DR      | F  |

| G | v_тс          | GND_TC        | v_тс              | v_тс               | АВ            | GND                | GND          | GND          | GND (              | GND G                 | ND G          | ND GI     | ND GN        | D GNE         | GND          |               | D17+          | D17-         | D18+                | D18-        | G  |

| н | Vinl+         | v_тс          | GND_TC            | V_A                | AC            | GND                | GND          | GND          | GND (              | GND G                 | ND G          | ND GI     | ND GN        | D GNI         | GND          |               | D19+          | D19-         | DI10+               | DI10-       | н  |

| J | Vinl-         | GND_TC        | v_тс              | Vbiasl             | AD            | GND                | GND          | GND          | GND (              | GND G                 | ND G          | ND GI     | ND GN        | D GNE         | GND          |               | V_DR          | DI11+        | DI 11-              | V_DR        | J  |

| к | GND           | Vbiasl        | ∨_тс              | GND_TC             | AE            | GND                | GND          | GND          | GND (              | GND G                 | ND G          | ND GI     | ND GN        | D GNE         | GND          | _             | ORI+          | ORI-         | DCLKI+              | DCLKI-      | к  |

| L | GND           | VbiasQ        | v_тс              | GND_TC             | AF            | GND                |              |              |                    |                       |               |           | ND GN        |               |              |               | ORQ+          | ORQ-         | DCLKQ+              | DCLKQ-      | L  |

| М | VinQ-         | GND_TC        | v_тс              | VbiasQ             | AG<br>AH      | GND                |              |              |                    |                       |               |           | ND GN        |               |              |               | GND_DR        | DQ 11+       | DQ11-               | GND_DR      | М  |

| N | VinQ+         | v_тс          | GND_TC            | V_A                | AJ            | GND                |              |              |                    |                       | _             |           | ND GN        |               |              |               | DQ9+          | DQ9-         | DQ 10+              | DQ 10-      | N  |

| Ρ | v_тс          | GND_TC        | ∨_тс              | v_тс               | AK            | GND                | GND          | GND          | GND (              | GND G                 | ND G          | ND GI     | ND GN        | D GNI         | ) GND        |               | DQ7+          | DQ7-         | DQ8+                | DQ8-        | Ρ  |

| R | V_A           | GND_TC        | v_тс              | v_тс               | AL            | GND                | GND          | GND          | GND (              | GND G                 | ND G          | ND GI     | ND GN        | D GNE         | GND          |               | V_DR          | DQ6+         | DQ6-                | V_DR        | R  |

| т | V_A           | GND_TC        | GND_TC            | GND                |               |                    |              | ļ            |                    |                       |               |           |              |               |              | _             | V_DR          | DQ3-         | DQ5+                | DQ5-        | т  |

| U | GND_TC        | CLK+          | PDI               | GND                | GND           | RCOut1-            | VbiasQ       | V_A          | V_A                | DQd1-                 | V_DR          | DQd4-     | GND_DR       | DQd7-         | V_DR         | V_DR          | GND_DR        | DQ3+         | DQ4+                | DQ4-        | U  |

| v | CLK-          | DCLK_R<br>ST+ | PDQ               | LSPSM              | DES           | RCOut2+            | RCOut2-      | V_E          | GND_E              | DQd1+                 | DQd2-         | DQd4+     | DQd5-        | DQd7+         | DQd8-        | DQd10-        | DQ0-          | GND_DR       | DQ2+                | DQ2-        | v  |

| w | DCLK_R<br>ST- | GND           | RSV               | DDRPh              | RCLK-         | V_A                | GND          | GND_E        | V_Е                | DQd0-                 | DQd2+         | DQd3-     | DQd5+        | DQd6-         | DQd8+        | DQd9-         | DQd 10+       | DQ0+         | DQ1+                | DQ1-        | w  |

| Y | GND           | V_A           | FSR               | RCLK+              | RCOut1+       | V_A                | GND          | V_E          | GND_E              | DQd0+                 | V_DR          | DQd3+     | GND_DR       | DQd6+         | V_DR         | DQd9+         | GND_DR        | DQd11+       | DQd 11-             | GND_DR      | Y  |

|   | 1<br>The c    | 2<br>enter g  | <b>3</b><br>round | <b>4</b><br>pins a | 5<br>re for t | <b>6</b><br>hermal | 7<br>dissipa | 8<br>ation a | <b>9</b><br>nd mus | <b>10</b><br>st be so | 11<br>oldered | <b>12</b> | 13<br>ground | 14<br>plane t | 15<br>o ensu | 16<br>re rate | 17<br>d perfo | 18<br>ormanc | <b>19</b><br>e. See | 20<br>Layou | ıt |

The center ground pins are for thermal dissipation and must be soldered to a ground plane to ensure rated performance. See *Layout Guidlines* for more information.

🛛 5-1. NAA Package, 376-Pin CCGA and CLGA, Top View

# 表 5-1. Pin Functions: Analog Front-End and Clock Pins

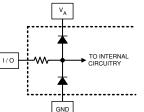

| PIN                                        |                | ТҮРЕ               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | EQUIVALENT CIRCUIT                                      |  |  |

|--------------------------------------------|----------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--|--|

| NAME                                       | NO.            | - TYPE DESCRIPTION |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                         |  |  |

| ANALOG FRONT                               | F-END AND CLOC | K PINS             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                         |  |  |

| CLK+<br>CLK–                               | U2/V1          | 1                  | Differential converter sampling clock. In the non-DES mode, the analog inputs are sampled on the positive transitions of this clock signal. In the DES mode, the selected input is sampled on both transitions of this clock. This clock must be AC-coupled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | VA<br>AGND<br>VA<br>SOK<br>VA<br>SOK<br>VBIAS           |  |  |

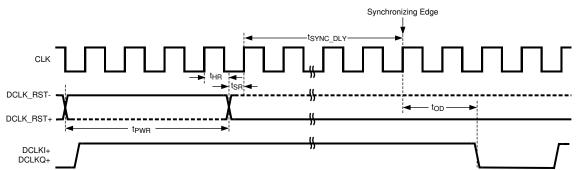

| DCLK_RST+<br>DCLK_RST-                     | V2/W1          | I                  | Differential DCLK reset. A positive pulse on this<br>input is used to reset the DCLKI and DCLKQ outputs<br>of two or more ADC12D1620 devices in order to<br>synchronize them with other ADC12D1620 devices<br>in the system. DCLKI and DCLKQ are always in<br>phase with each other, unless one channel is<br>powered down, and do not require a pulse from<br>DCLK_RST to become synchronized. The pulse<br>applied here must meet timing relationships with<br>respect to the CLK input. Although supported, this<br>feature has been superseded by AutoSync.                                                                                                                                                                                                                                       | VA<br>O<br>AGND<br>VA<br>100<br>VA<br>100<br>VA<br>AGND |  |  |

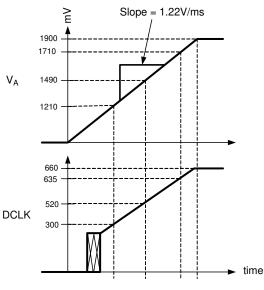

| RCLK+<br>RCLK–                             | Y4/W5          | I                  | Reference clock input. When the AutoSync feature is<br>active, and the ADC12D1620 is in secondary mode,<br>the internal divided clocks are synchronized with<br>respect to this input clock. The delay on this clock<br>may be adjusted when synchronizing multiple ADCs.<br>This feature is available in ECM with the DRC bits of<br>the AutoSync Control Register (Addr: Eh, Bits: 15:7).                                                                                                                                                                                                                                                                                                                                                                                                           | VA<br>AGND<br>VA<br>50k<br>VBIAS                        |  |  |

| RCOut1+,<br>RCOut1–<br>RCOut2+,<br>RCOut2– | Y5/U6<br>V6/V7 | 0                  | Reference clock output 1 and 2. These signals,<br>when enabled, provide a reference clock. The<br>RCOut rates for all of the available modes can be<br>found in $\not{\equiv}$ 7-8; the rates displayed in the table are<br>independent of whether the ADC is in primary or<br>secondary mode. RCOut1 and RCOut2 are used to<br>drive the RCLK of ADC12D1620 to enable automatic<br>synchronization for multiple ADCs (AutoSync<br>feature). The impedance of each trace from RCOut1<br>and RCOut2 to the RCLK of ADC12D1620 should<br>be 100- $\Omega$ differential. Having two clock outputs<br>allows the auto-synchronization to propagate as a<br>binary tree. Use the DOC bit of the AutoSync Control<br>Register (Addr: Eh; Bit: 1) to enable or disable this<br>feature; default is disabled. |                                                         |  |  |

| 表 5-1. Pin Functions: Analog Front-End and Clock Pins (continued) |

|-------------------------------------------------------------------|

|-------------------------------------------------------------------|

| P                  | PIN   |      |                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                    |  |  |

|--------------------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|

| NAME               | NO.   | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                             | EQUIVALENT CIRCUIT                                 |  |  |

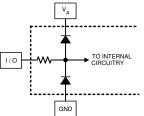

| Rext+<br>Rext–     | C3/D3 | I/O  | External reference resistor terminals. Connect a 3.3- $k\Omega$ , ±0.1% resistor between Rext+, Rext–. The Rext resistor is used as a reference to trim internal circuits that affect the linearity of the converter; the value and precision of this resistor must not be compromised.                                                                                                                                 | VA<br>GND<br>V                                     |  |  |

| Rtrim+<br>Rtrim–   | C1/D2 | I/O  | Input termination trim resistor terminals. Connect a 3.3-k $\Omega$ , ±0.1%resistor between Rtrim+/ Rtrim–. The Rtrim resistor is used to establish the calibrated 100- $\Omega$ input impedance of Vinl, VinQ, and CLK. These impedances may be fine-tuned by varying the value of the resistor by a corresponding percentage; however, the tuning range and performance is not tested for such an alternative values. | VA<br>GND<br>VA                                    |  |  |

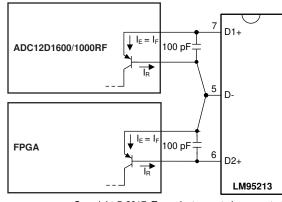

| Tdiode+<br>Tdiode– | E2/F3 | 0    | Temperature sensor diode positive (anode) and<br>negative (cathode) terminals. This set of pins is used<br>for die temperature measurements. It has not been<br>fully characterized.                                                                                                                                                                                                                                    | Tdiode_P                                           |  |  |

| V <sub>BG</sub>    | B1    | I/O  | Bandgap voltage output or LVDS common-mode<br>voltage select. This pin provides a buffered version<br>of the bandgap output voltage; it is capable of<br>sourcing/sinking 100 µA and driving a load of up to<br>80 pF. Alternately, this pin may be used to select the<br>LVDS digital output common-mode voltage. If tied to<br>logic-high, the 1.2-V LVDS common-mode voltage is<br>selected; 0.8 V is the default.   |                                                    |  |  |

| V <sub>CMO</sub>   | C2    | I/O  | Common-mode voltage. This pin is the common-<br>mode output in DC-coupling mode and also serves<br>as the AC-coupling mode select pin. When DC-<br>coupling is used at the analog inputs, the voltage<br>output at this pin is required to be the common-mode<br>input voltage at VIN+ and VIN When AC-coupling<br>is used, this pin must be grounded. This pin is<br>capable of sourcing or sinking 100 µA.            | VA<br>200k<br>VCMO<br>Enable AC<br>Coupling<br>GND |  |  |

| PII                          |                | TYPE |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                               |  |  |

|------------------------------|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--|--|

| NAME                         | NAME NO.       |      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | EQUIVALENT CIRCUIT                            |  |  |

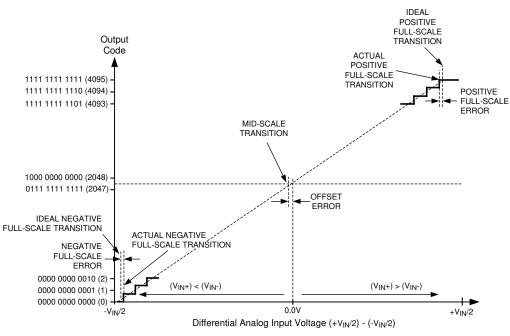

| Vinl+, Vinl–<br>VinQ+, VinQ– | H1/J1<br>N1/M1 | 1    | Differential signal I and Q inputs. In the non-dual<br>edge sampling (non-DES) mode, each I and Q input<br>is sampled and converted by its respective channel<br>with each positive transition of the CLK input. In non-<br>ECM (non-extended control mode) and DES mode,<br>both channels sample the I input. In Extended<br>Control mode (ECM), the Q input may optionally be<br>selected for conversion in DES mode by the DEQ Bit<br>of the Configuration Register (Addr: 0h; Bit: 6).<br>Each I- and Q-channel input has an internal common<br>mode bias that is disabled when DC-coupled mode<br>is selected. Both inputs must be either AC- or DC-<br>coupled. The coupling mode is selected by the V <sub>CMO</sub><br>pin.<br>In non-ECM, the full-scale range of these inputs is<br>determined by the FSR pin; both I and Q channels<br>have the same full-scale input range. In ECM, the<br>full-scale input range of the I- and Q-channel<br>Full-Scale Range Adjust Registers (Addr: 3h and<br>Addr: Bh, respectively). The high and low full-scale<br>input range setting in non-ECM corresponds to the<br>mid and minimum full-scale input range in ECM.<br>The input offset may also be adjusted in ECM with<br>the I- and Q-channel Offset Adjust Registers (Addr:<br>2h and Addr: Ah, respectively). | VA<br>AGND<br>VCMO<br>Control from VA<br>AGND |  |  |

| CONTROL AND S                | TATUS PINS     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                               |  |  |

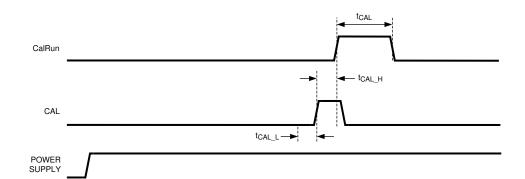

| CAL                          | D6             | 1    | Calibration cycle initiate. The user can command the device to execute a self-calibration cycle by holding this input high for a minimum of $t_{CAL\_H}$ after having held it low for a minimum of $t_{CAL\_L}$ . This pin is active in both ECM and non-ECM. In ECM, this pin is logically OR'd with the CAL Bit of the Configuration Register (Addr: 0h, Bit 15). Therefore, both the pin and bit must be set low and then either can be set high to execute an on-command calibration. TI recommends holding the CAL pin high during normal usage to reduce the chance that an SEU causes a calibration cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | GND                                           |  |  |

| CalRun                       | В5             | 0    | Calibration running indication. This output is logic-<br>high while the calibration sequence is executing;<br>otherwise, this output is logic-low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                               |  |  |

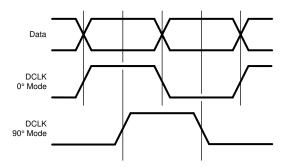

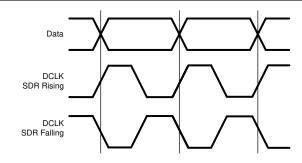

#### PIN TYPE EQUIVALENT CIRCUIT DESCRIPTION NAME NO. DDR phase select. In DDR, when this input is logiclow, it selects the 0° data-to-DCLK phase relationship. When this input is logic-high, it selects the 90° data-to-DCLK phase relationship; that is, the DCLK transition indicates the middle of the valid data outputs. In SDR, when this input is logic-low, the output transitions on the rising edge of DCLK. When this input is logic-high, output transition is on the falling DDRPh W4 Т edge of DCLK. This pin only has an effect when the chip is in 1:2 demuxed mode; that is, the NDM pin is set to logic-GND low. In ECM, this input is ignored and the DDR phase is selected through the Control Register by the DPS bit (Addr: 0h, Bit 14); the default is 0° mode. Dual edge sampling (DES) mode select. In the nonextended control mode (Non-ECM), when this input is set to logic-high, the DES mode of operation is selected; this means that the VinI input is sampled by both channels in a time-interleaved manner and the VinQ input is ignored. When this input is set to logic-low, the device is in DES V5 Т non-DES mode; that is, I and Q channels operate independently. In the extended control mode (ECM), this input is ignored and DES mode selection is controlled through the DES bit of the Configuration GND Register (Addr: 0h; Bit: 7); default is non-DES mode operation. Extended control enable. Extended feature control through the SPI interface is enabled and the device is in ECM when this signal is asserted (logic-low). Please reference $\pm$ 7-1 for information on the behavior of the control pins when the extended ECE B3 Т feature control is enabled. When this signal is de-asserted (logic-high), the SPI interface is disabled, all SPI registers are reset to their default values, and all available settings are GND controlled with the control pins. Full-scale input range select. In non-ECM, when this input is set to logic-low or logic-high, the full-scale differential input range for both I- and Q-channel inputs is set to the lower or higher FSR value, respectively. In the ECM, this input is ignored and the full-scale range of the I- and Q-channelinputs is FSR Y3 Т independently determined by the setting of the I- and Q-channel Full-Scale Range Adjust Registers (Addr: 3h and Addr: Bh, respectively). Note that the high (lower) FSR value in non-ECM corresponds to the GND mid (min) available selection in ECM; the FSR range in ECM is greater.

| PIN        |          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | · · ·              |  |  |

|------------|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|--|

| NAME       | NO.      | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | EQUIVALENT CIRCUIT |  |  |

| LSPSM      | ∨4       | I    | Low-sampling power-saving mode (LSPSM) select.<br>In LSPSM, the power consumption is reduced by<br>approximately 20%, and some improvement in<br>performance may be seen. The output is in SDR in<br>1:2 demux mode and DDR in 1:1 non-demux mode.<br>DDR is not available in 1:2 demux mode in LSPSM.<br>The maximum sampling rate in LSPSM in non-DES<br>mode is 800 MSPS. When this input is logic-high,<br>the device is in LSPSM and when this input is logic-<br>low, the device is in normal mode or non-LSPSM.                                        | GND VA             |  |  |

| NDM        | A5       | I    | Non-demuxed mode select. Setting this input to<br>logic-high causes the digital output bus to be in the<br>1:1 non-demuxed mode. Setting this input to logic-<br>low causes the digital output bus to be in the 1:2<br>demuxed mode. This feature is pin-controlled only<br>and remains active during both ECM and non-ECM.                                                                                                                                                                                                                                   | GND                |  |  |

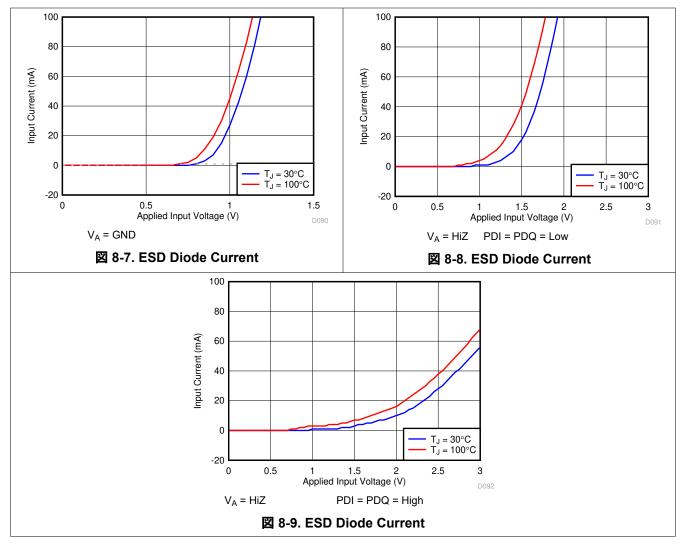

| PDI<br>PDQ | U3<br>V3 | I    | Power down I and Q channels. Setting either input to<br>logic-high powers down the respective I or Q<br>channel. Setting either input to logic-low brings the<br>respective I or Q channel to a operational state after<br>a finite time delay. This pin is active in both ECM and<br>non-ECM. In ECM, each pin is logically OR'd with its<br>respective bit. Therefore, either this pin or the PDI<br>and PDQ bits in the Configuration Register (Addr:<br><b>0h</b> ; Bit: 11 and Bit: 10, respectively) can be used to<br>power down the I and Q channels. |                    |  |  |

| RSV        | W3       | _    | Reserved. This pin is used for internal purposes and must be connected to GND through a $100-k\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                               | NONE               |  |  |

| RSV1       | E3       |      | Decouple this pin with a 100-nF capacitor with a low resistance, low inductance path to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | NONE               |  |  |

| RSV2       | F4       |      | Decouple this pin with a 100-nF capacitor with a low resistance, low inductance path to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | NONE               |  |  |

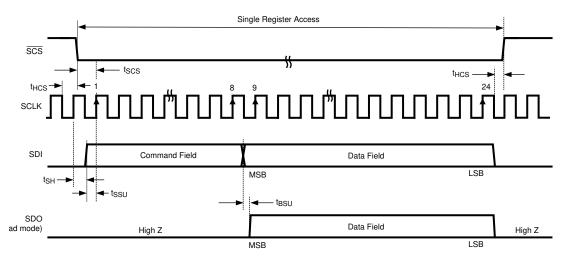

| SCLK       | C5       | I    | Serial clock. In ECM, serial data is shifted into and<br>out of the device synchronously to this clock signal.<br>This clock may be disabled and held logic-low, as<br>long as timing specifications are not violated when<br>the clock is enabled or disabled.                                                                                                                                                                                                                                                                                               | GND VA             |  |  |

| SCS        | C4       | I    | Serial chip select. In ECM, when this signal is<br>asserted (logic-low), SCLK is used to clock in serial<br>data that is present on SDI and to source serial data<br>on SDO. When this signal is de-asserted (logic-<br>high), SDI is ignored and SDO is tri-state.                                                                                                                                                                                                                                                                                           |                    |  |  |

|                   | 表 5-1. Pin Functions: Analog Front-End and Clock Pins (continued)                             |      |                                                                                                                                                                                                                                                                                                                   |                      |  |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|--|--|

| PI<br>NAME        | N NO.                                                                                         | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                       | EQUIVALENT CIRCUIT   |  |  |  |  |  |

| SDI               | B4                                                                                            | 1    | Serial data-in. In ECM, serial data is shifted into the device on this pin while SCS signal is asserted (logic-low).                                                                                                                                                                                              | VA<br>TIOD KC<br>GND |  |  |  |  |  |

| SDO               | A3                                                                                            | 0    | Serial data-out. In ECM, serial data is shifted out of<br>the device on this pin while SCS signal is asserted<br>(logic-low). This output is tri-state when SCS is de-<br>asserted (logic-high).                                                                                                                  |                      |  |  |  |  |  |

| ТРМ               | A4                                                                                            | I    | Test pattern mode select. With this input at logic-<br>high, the device continuously outputs a fixed,<br>repetitive test pattern at the digital outputs. In ECM,<br>this input is ignored, and the test pattern mode can<br>only be activated through the Control Register by the<br>TPM bit (Addr: 0h, Bit: 12). | VA<br>GND            |  |  |  |  |  |

| POWER AND GR      | OUND PINS                                                                                     |      |                                                                                                                                                                                                                                                                                                                   |                      |  |  |  |  |  |

| GND               | A1, A7, B2, B7,<br>C6, D4, D5, E4,<br>K1, L1, T4, U4,<br>U5, W2, W7,<br>Y1, Y7,<br>AA2:AL11   | Ρ    | Analog ground return                                                                                                                                                                                                                                                                                              | NONE                 |  |  |  |  |  |

| GND <sub>DR</sub> | A13, A17, A20,<br>D13, D16, E17,<br>F17, F20, M17,<br>M20, U13, U17,<br>V18, Y13, Y17,<br>Y20 | Ρ    | Ground return for the output drivers                                                                                                                                                                                                                                                                              | NONE                 |  |  |  |  |  |

| GND <sub>E</sub>  | A9, B8, C9, V9,<br>W8, Y9                                                                     | Р    | Ground return for the digital encoder                                                                                                                                                                                                                                                                             | NONE                 |  |  |  |  |  |

| GND <sub>TC</sub> | F2, G2, H3, J2,<br>K4, L4, M2, N3,<br>P2, R2, T2, T3,<br>U1                                   | Ρ    | Ground return for the track-and-hold and clock circuitry                                                                                                                                                                                                                                                          | NONE                 |  |  |  |  |  |

| V <sub>A</sub>    | A2, A6, B6, C7,<br>D1, D8, D9, E1,<br>F1, H4, N4, R1,<br>T1, U8, U9, W6,<br>Y2, Y6            | Ρ    | Analog power supply. This supply is tied to the ESD ring; therefore, it must be powered up before or with any other supply.                                                                                                                                                                                       | NONE                 |  |  |  |  |  |

| Vbiasl            | D7, J4, K2                                                                                    | Ρ    | Bias voltage I channel. This is an externally<br>decoupled bias voltage for the I channel. Each pin<br>must individually be decoupled with a 100-nF<br>capacitor through a low resistance, low inductance<br>path to GND.                                                                                         | NONE                 |  |  |  |  |  |

| PI                                                                                                                                                                                                                                                                                                                    | 表 5-1. Pin Functions: Analog Front-End and Clock Pins (continued)                                                                                                                                                                                                    |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|--|--|

| NAME                                                                                                                                                                                                                                                                                                                  | NO.                                                                                                                                                                                                                                                                  | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | EQUIVALENT CIRCUIT |  |  |  |

| VbiasQ                                                                                                                                                                                                                                                                                                                | L2, M4, U7                                                                                                                                                                                                                                                           | Р    | Bias voltage Q channel. This is an externally<br>decoupled bias voltage for the Q channel. Each pin<br>must individually be decoupled with a 100-nF<br>capacitor through a low resistance, low inductance<br>path to GND.                                                                                                                                                                                                                                                                                                                                                                                                  | NONE               |  |  |  |

| V <sub>DR</sub>                                                                                                                                                                                                                                                                                                       | A11, A15, C18,<br>D11, D15, D17,<br>J17, J20, R17,<br>R20, T17, U11,<br>U15, U16, Y11,<br>Y15                                                                                                                                                                        | Р    | Power supply for the output drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | NONE               |  |  |  |

| V <sub>E</sub>                                                                                                                                                                                                                                                                                                        | A8, B9, C8, V8,<br>W9, Y8                                                                                                                                                                                                                                            | Р    | Power supply for the digital encoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | NONE               |  |  |  |

| V <sub>TC</sub>                                                                                                                                                                                                                                                                                                       | G1, G3, G4,<br>H2, J3, K3, L3,<br>M3, N2, P1, P3,<br>P4, R3, R4                                                                                                                                                                                                      | Р    | Power supply for the track-and-hold and clock circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | NONE               |  |  |  |

| HIGH-SPEED DIG                                                                                                                                                                                                                                                                                                        | ITAL OUTPUT PI                                                                                                                                                                                                                                                       | NS   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |  |  |  |

| DCLKI+,<br>DCLKI–<br>DCLKQ+,<br>DCLKQ–                                                                                                                                                                                                                                                                                | K19/K20<br>L19/L20                                                                                                                                                                                                                                                   | 0    | Data clock output for the I- and Q-channel data bus.<br>These differential clock outputs are used to latch the<br>output data and, if used, terminate with a 100- $\Omega$<br>differential resistor placed as closely as possible to<br>the differential receiver. Delayed and non-delayed<br>data outputs are supplied synchronously to this<br>signal. The DCLK rates for all of the available modes<br>can be found in $\gtrsim$ 7-8. DCLKI and DCLKQ are<br>always in phase with each other, unless one channel<br>is powered down, and do not require a pulse from<br>DCLK_RST to become synchronized.                |                    |  |  |  |

| DI11+, DI11-<br>DI10+, DI10-<br>DI9+, DI9-<br>DI8+, DI8-<br>DI7+, DI7-<br>DI6+, DI6-<br>DI5+, DI5-<br>DI4+, DI4-<br>DI3+, DI3-<br>DI2+, DI2-<br>DI1+, DI1-<br>DQ10+, DQ1-<br>DQ9+, DQ9-<br>DQ8+, DQ8-<br>DQ7+, DQ7-<br>DQ6+, DQ6-<br>DQ5+, DQ5-<br>DQ4+, DQ4-<br>DQ3+, DQ3-<br>DQ2+, DQ2-<br>DQ1+, DQ1-<br>DQ0+, DQ0- | J18/J19<br>H19/H20<br>H17/H18<br>G19/G20<br>G17/G18<br>F18/F19<br>E19/E20<br>D19/D20<br>D18/E18<br>C19/C20<br>B19/B20<br>B18/C17<br>M18/M19<br>N19/N20<br>N17/N18<br>P19/P20<br>P17/P18<br>R18/R19<br>T19/T20<br>U19/U20<br>U18/T18<br>V19/V20<br>W19/W20<br>W18/V17 | 0    | I- and Q-channel digital data outputs. In non-demux<br>mode, this LVDS data is transmitted at the sampling<br>clock rate. In demux mode, these outputs provide $\frac{1}{2}$<br>the data at $\frac{1}{2}$ the sampling clock rate, synchronized<br>with the delayed data; that is, the other $\frac{1}{2}$ of the data<br>which was sampled one clock cycle earlier.<br>Compared with the DId and DQd outputs, these<br>outputs represent the later time samples. If used,<br>terminate each of these outputs with a 100- $\Omega$<br>differential resistor placed as closely as possible to<br>the differential receiver. |                    |  |  |  |

| 表 5-1. Pin Functions: Analog Front-End and Clock Pins (continued) PIN PIN                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                             |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                    |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                                                                                                                                                                                                                                                           | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | EQUIVALENT CIRCUIT                                                 |  |  |

| NAME           Dld11+, Dld11-           Dld10+, Dld9-           Dld8+, Dld8-           Dld7+, Dld7-           Dld6+, Dld6-           Dld5+, Dld5-           Dld4+, Dld4-           Dld3+, Dld3-           Dld2+, Dld2-           Dld1+, Dld1-           Dld0+, Dld0-           .           DQd11+, DQd10-           DQd10+, DQd9-           DQd8+, DQd8-           DQd7+, DQd7-           DQd6+, DQd5-           DQd4+, DQd4-           DQd3+, DQd3-           DQd2+, DQ42-           DQd1+, DQd1- | NO.<br>A18/A19<br>B17/C16<br>A16/B16<br>B15/C15<br>C14/D14<br>A14/B14<br>B13/C13<br>C12/D12<br>A12/B12<br>B11/C11<br>C10/D10<br>A10/B10<br>Y18/Y19<br>W17/V16<br>Y16/W16<br>W15/V15<br>V14/U14<br>Y14/W14<br>W13/V13<br>V12/U12<br>Y12/W12<br>W11/V11<br>V10/U10<br>Y10/W10 | O    | Delayed I- and Q-channel digital data outputs. In<br>non-demux mode, these outputs are tri-state. In<br>demux mode, these outputs provide $\frac{1}{2}$ the data at $\frac{1}{2}$<br>the sampling clock rate, synchronized with the non-<br>delayed data; that is, the other $\frac{1}{2}$ of the data which<br>was sampled one clock cycle later. Compared with<br>the DI and DQ outputs, these outputs represent the<br>earlier time samples. If used, terminate each of<br>these outputs with a 100- $\Omega$ differential resistor<br>placed as closely as possible to the differential<br>receiver. | VDR<br>VDR<br>VDR<br>VDR<br>VDR<br>VDR<br>VDR<br>VDR<br>VDR<br>VDR |  |  |

| ORI+,<br>ORI-<br>ORQ+,<br>ORQ-                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | K17/K18<br>L17/L18                                                                                                                                                                                                                                                          | ο    | Out-of-range output for the I and Q channel. This differential output is asserted logic-high while the over- or under-range condition exists; that is, the differential signal at each respective analog input exceeds the full-scale value. Each OR result refers to the current data, with which it is clocked out. If used, terminate each of these outputs with a 100- $\Omega$ differential resistor placed as closely as possible to the differential receiver.                                                                                                                                    |                                                                    |  |  |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1) (1) (2)</sup>

|                                                                                       | MIN   | MAX  | UNIT |

|---------------------------------------------------------------------------------------|-------|------|------|

| Supply voltage (V <sub>A</sub> , V <sub>TC</sub> , V <sub>DR</sub> , V <sub>E</sub> ) |       | 2.2  | V    |

| Supply difference – max(V <sub>A /TC /DR /E</sub> ) – min(V <sub>A /TC /DR /E</sub> ) | 0     | 100  | mV   |

| Voltage on any input pin (except VinI+, VinI–, VinQ+, VinQ–)                          | -0.15 | 2.35 | V    |

| VinI+, VinI–, VinQ+, VinQ– voltage (maintaining common mode) <sup>(3)</sup>           | -0.5  | 2.5  | V    |

| Input current at VinI+, VinI–, VinQ+, VinQ– <sup>(3)</sup>                            |       | ±50  | mA   |

| Ground difference – max(GND <sub>TC /DR /E</sub> ) – min(GND <sub>TC /DR /E</sub> )   | 0     | 100  | mV   |

| Input current at any pin <sup>(4)</sup>                                               |       | ±50  | mA   |

| Power dissipation at $T_A \le 125^{\circ}C^{(4)}$                                     |       | 4.4  | W    |

| Storage temperature, T <sub>stg</sub>                                                 | -65   | 150  | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are measured with respect to GND = GND<sub>DR</sub> = GND<sub>E</sub> = GND<sub>TC</sub> = 0 V, unless otherwise specified.

(3) Verified during product qualification high-temperature lifetime testing (HTOL) at  $T_J = 150^{\circ}$ C for 1000 hours continuous operation with  $V_A = V_D = 2.2$  V.

(4) When the input voltage at any pin exceeds the power supply limits, the current at that pin must be limited to 50 mA. In addition, overvoltage at a pin must adhere to maximum voltage limits. Simultaneous overvoltage at multiple pins requires adherence to the maximum package power dissipation limits, which are calculated using the JEDEC JESD51-7 thermal model. Higher dissipation may be possible based on customer-specific thermal situations and specified thermal package resistances from junction to case.

#### 6.2 ESD Ratings

|                    |                         |                                                                   | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body Model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±2500 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                                          |                                                 | MIN                    | MAX                    | UNIT      |  |

|--------------------------------------------------------------------------|-------------------------------------------------|------------------------|------------------------|-----------|--|

| Case temperature                                                         |                                                 | -55                    | 125                    | °C        |  |

| Supply voltage (V <sub>A</sub> , V <sub>TC</sub> , V <sub>E</sub> )      |                                                 | 1.8                    | 2                      | V         |  |

| Voltage on any input pin (except VinI+, VinI–, VinQ+                     | , VinQ–)                                        | -0.15                  | 2.15                   | V         |  |

| Driver supply voltage (V <sub>DR</sub> )                                 |                                                 | 1.8                    | V <sub>A</sub>         | V         |  |

| VinI+, VinI–, VinQ+, VinQ– voltage <sup>(2)</sup>                        | DC-coupled                                      | -0.4                   | 2.4                    | V         |  |

|                                                                          | DC-coupled at 100% duty cycle                   |                        | 1                      |           |  |

| VinI+, VinI–, VinQ+, VinQ– differential voltage <sup>(3)</sup>           | DC-coupled at 20% duty cycle                    |                        | 2                      | V         |  |

|                                                                          | DC-coupled at 10% duty cycle                    |                        | 2.8                    |           |  |

| VinI+, VinI–, VinQ+, VinQ– current <sup>(2)</sup>                        | AC-coupled                                      | -50                    | 50                     | mA        |  |

| Vinl+ Vinl VinO+ VinO nowor                                              | Maintaining common-mode voltage,<br>AC-coupled  |                        | 15.3                   |           |  |

| VinI+, VinI–, VinQ+, VinQ– power                                         | Not maintaining common-mode voltage, AC-coupled |                        | 17.1                   | dBm       |  |

| Ground difference - max(GND <sub>TC/DR/E</sub> ) - min(GND <sub>TC</sub> | :/DR/E)                                         |                        | 0                      | V         |  |

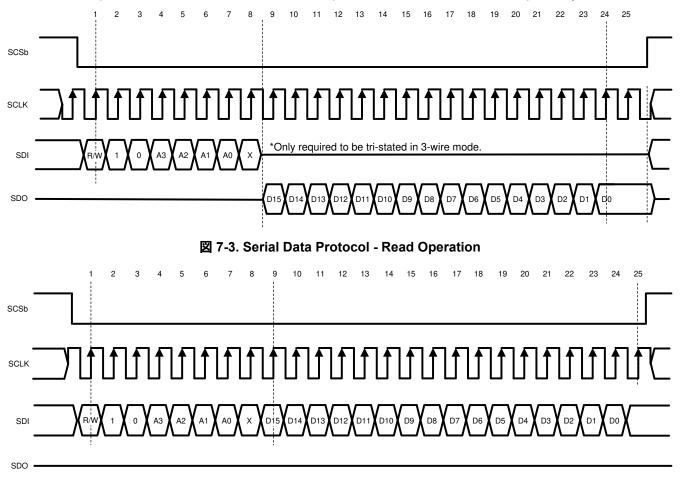

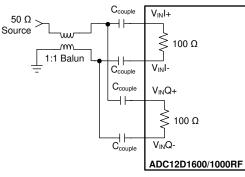

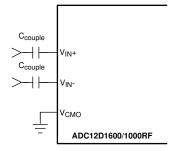

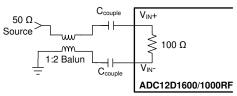

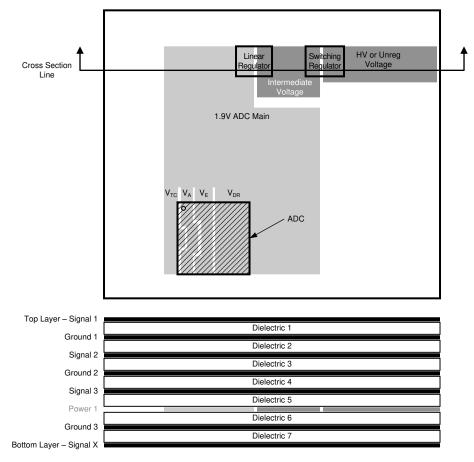

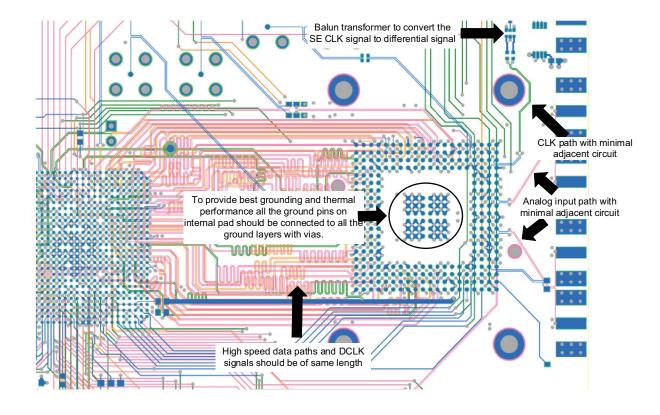

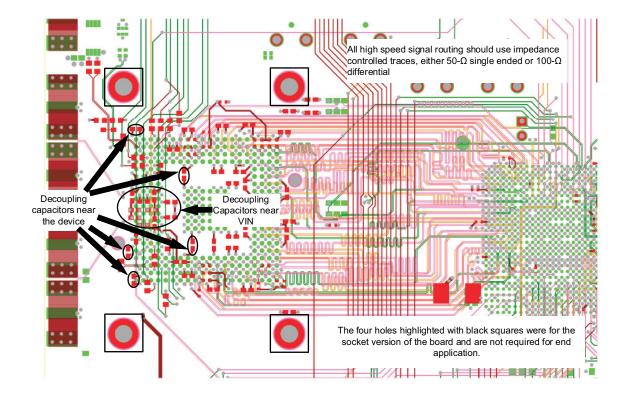

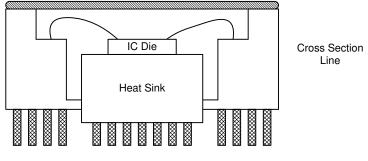

| Input current at any pin except VinI+, VinI-, VinQ+, o                   | or VinQ- <sup>(4)</sup>                         |                        | ±50                    | mA        |  |