SPRAD57 August 2022 AM67 , AM67A , AM68 , AM68A , AM69 , AM69A , DRA829J , DRA829J-Q1 , DRA829V , DRA829V-Q1 , TDA4AEN-Q1 , TDA4AH-Q1 , TDA4AL-Q1 , TDA4AP-Q1 , TDA4VE-Q1 , TDA4VEN-Q1 , TDA4VH-Q1 , TDA4VL-Q1 , TDA4VM , TDA4VM-Q1 , TDA4VP-Q1

Abstract

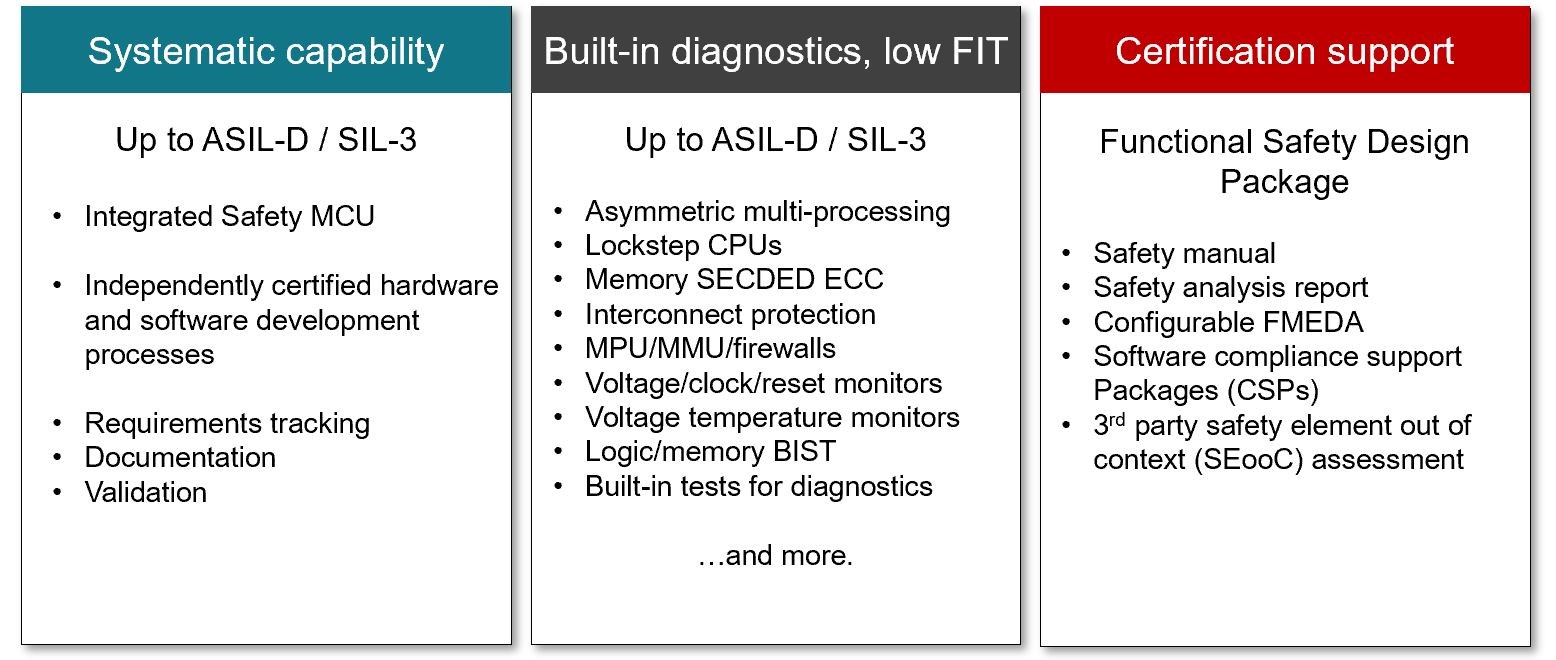

In this document, we will introduce Jacinto 7 safety fundamentals and the collateral TI provides for customers' functional safety implementation.

Jacinto SoCs are developed as a functional Safety Element Out of Context (SEooC) via ISO26262/IEC61508 processes to achieve ASIL-D/SIL-3 systematic fault integrity and includes hardware diagnostics to achieve up ASIL-D/SIL-3 random fault integrity. The device has gone through safety assessment by a certified third party (TUV-SUD) and a certificate will be provided.